Analog I/O: AD-Wandlung, Stand 22.05.2007

Werbung

Embedded Systemarchitekturen und Echtzeitbetriebssysteme

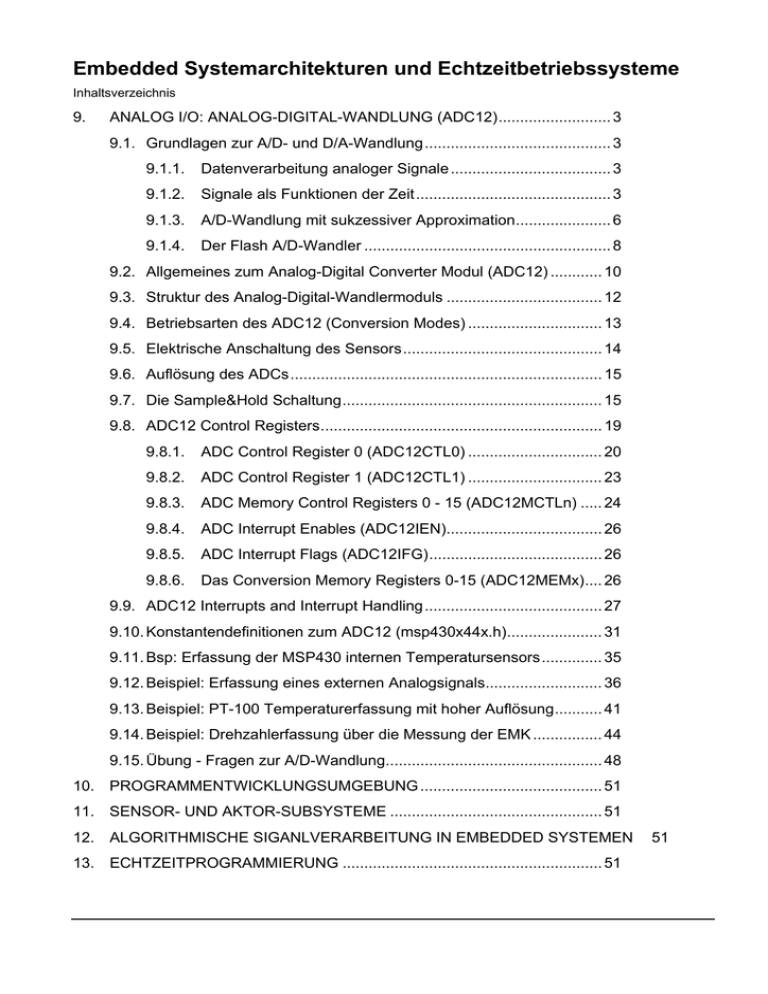

Inhaltsverzeichnis

9.

ANALOG I/O: ANALOG-DIGITAL-WANDLUNG (ADC12).......................... 3

9.1. Grundlagen zur A/D- und D/A-Wandlung........................................... 3

9.1.1.

Datenverarbeitung analoger Signale ..................................... 3

9.1.2.

Signale als Funktionen der Zeit ............................................. 3

9.1.3.

A/D-Wandlung mit sukzessiver Approximation...................... 6

9.1.4.

Der Flash A/D-Wandler ......................................................... 8

9.2. Allgemeines zum Analog-Digital Converter Modul (ADC12) ............ 10

9.3. Struktur des Analog-Digital-Wandlermoduls .................................... 12

9.4. Betriebsarten des ADC12 (Conversion Modes) ............................... 13

9.5. Elektrische Anschaltung des Sensors.............................................. 14

9.6. Auflösung des ADCs........................................................................ 15

9.7. Die Sample&Hold Schaltung............................................................ 15

9.8. ADC12 Control Registers................................................................. 19

9.8.1.

ADC Control Register 0 (ADC12CTL0) ............................... 20

9.8.2.

ADC Control Register 1 (ADC12CTL1) ............................... 23

9.8.3.

ADC Memory Control Registers 0 - 15 (ADC12MCTLn) ..... 24

9.8.4.

ADC Interrupt Enables (ADC12IEN).................................... 26

9.8.5.

ADC Interrupt Flags (ADC12IFG)........................................ 26

9.8.6.

Das Conversion Memory Registers 0-15 (ADC12MEMx).... 26

9.9. ADC12 Interrupts and Interrupt Handling......................................... 27

9.10. Konstantendefinitionen zum ADC12 (msp430x44x.h)...................... 31

9.11. Bsp: Erfassung der MSP430 internen Temperatursensors.............. 35

9.12. Beispiel: Erfassung eines externen Analogsignals........................... 36

9.13. Beispiel: PT-100 Temperaturerfassung mit hoher Auflösung........... 41

9.14. Beispiel: Drehzahlerfassung über die Messung der EMK ................ 44

9.15. Übung - Fragen zur A/D-Wandlung.................................................. 48

10. PROGRAMMENTWICKLUNGSUMGEBUNG .......................................... 51

11. SENSOR- UND AKTOR-SUBSYSTEME ................................................. 51

12. ALGORITHMISCHE SIGANLVERARBEITUNG IN EMBEDDED SYSTEMEN

13. ECHTZEITPROGRAMMIERUNG ............................................................ 51

51

9.

ANALOG I/O: ANALOG-DIGITAL-WANDLUNG (ADC12)

Gliederung

- Was bedeutet AD-Wandlung

- ggf. AD-Wandlertypen

- Sample & Hold Schaltung, DarstellungSample&Hold-Signals (S/-H Signal)

- Berechnung der Impedanz

- Berechnung des Digitalwertes als Fkt von (Vin, Vref+, Vref-)

Hardware

- Beschaltung des AD-Wandlers

- V+Ref, V-Ref, Vss, Vcc

- Hardware Register

Literatur und Weblinks

http://www.embeddedrelated.com/usenet/embedded/keyword/MSP430.php

http://www.mikrocontroller.net/articles/MSP430_Codebeispiele

http://www.atwillys.de/imp/prj/index.htm

comp.arch.embedded -> Newsgroup

www.embedded.com -> Embedded Systems Programming is a good

magazine for picking up tips and ideas. It is a free monthly magazine.

9.1. Grundlagen zur A/D- und D/A-Wandlung

9.1.1.

Datenverarbeitung analoger Signale

Bild: Computing network manipulates digital data

9.1.2.

Signale als Funktionen der Zeit

3

Durch die Quantisierung wird die unendliche Menge im Wertevorrat eines analogen

Signales auf eine (meist) endliche Menge des wertdiskreten (und zeitdiskreten) Signales abgebildet. Quantisierungsfehler

u(t)

analoges Signal

wert- und zeitkontinuierlich

t

Quantisierung

Abtastung

u(n T)

uq(t)

t

wertdiskret

zeitkontinuierlich

t

wertkontinuierlich

zeitdiskret

Quantisierung

Abtastung

uq(n T)

werte- und

zeitdiskret

t

Bild: Abtastung und Quantisierung analoger Signale

Die Aufgabe der Analog/Digitalwandlung besteht darin, einen vorgegebenen Spannungsbereich Umin ≤ U < Umax auf den Bereich der n-Bit Dualzahlen 0 ≤ N ≤ 2n-1 linear

abzubilden.

Der Spannungsbereich Umin bis Umax wird hierzu in 2n gleiche Spannungsschritte der

Höhe

ULSB = (Umax - Umin) ) / 2n unterteilt.

4

Umax und Umin entsprechen dabei der oberen und der unteren analogen Referenzspannung des A/D-Wandlers. ULSB steht für den kleinsten Spannungsschritt

Es ergibt sich dann für das digitale Äquivalent Z der A/D-Wandlung:

Z = (UsIN - Umin) ) / ULSB

mit UsIN = Eingangsspannung am A/D-Wandler

Beispiel:

The next figure shows the digital codes generated by a 4-bit analog-to-digital converter

which has 16 codes of four bits each that are generated as an analog signal increases

from 0 to 15/16 of full scale.

As the signal increases 1/16 of full scale, the code changes by a digital bit. As the analog signal varies in amplitude with time, the digital code generated by the ADC changes

to represent the amplitude of the analog signal at the time the signal was sampled. This

is demonstrated by superimposing the analog signal onto the ADC transfer curve shown

in the next figure. The points of sampling are shown and numbered from 1 through 16

and correspond to the sampling points.

1

2

3

4

5

6 789

10 11 12

13

14

15

16

Bild: AC-Signal überlagert mit den ADC-Quantisierungsstufen

5

The digital codes generated at each sampling point are also listed in this figure. The

digital code generated at a particular sample is the code nearest the amplitude just exceeded by the signal but not large enough to generate the next code step. These codes

from the sampling points appear in sequence at the output of the ADC to describe the

analog signal.

9.1.3.

A/D-Wandlung mit sukzessiver Approximation

Bild: A/D-Wandler nach dem sukzessiven Approximationsverfahren

Das Verfahren wir im folgenden an einem 8-Bit A/D-Wanlder erläutert.

Zu Beginn einer Wanldung steht das Approximationsregister auf 00h. Mit jedem Taktimpuls des A/D-Wandler wird ein Bit des Registers, beginnend mit dem höchstwertigen

Bit, auf 1 gesetzt. Der nachgeschaltete D/A-Wandler erzeugt nun die zu dem aktuellen

Approximationsregister äquivalente analoge Spannung UN(NADC), die mittels des Komparators mit der Eingangsspannung UHold verglichen wird. Ist UN(NADC) > UHold, so wird

noch innerhalb der Dauer des Taktimpulses das zuletzt veränderte Bit im Approximationsregister wieder auf 0 zurück gesetzt.

Dieses Verfahren wird mit den nächsten Bit des Approximationsregisters fortgesetzt, bis

auch das niederwertigste Bit (LSB) ermittelt wurde. Das Ende der sukzessiven Wandlung wird per EOC (End of conversion)-Flag im Statusregister des A/D-Wandlers angezeit und ggf. per Interrupt der CPU signalisiert.

In jedem Taktintervall wird ein Bit des Approximationsregisters ermittlet und der Spaltenvektor nähert sich so dem digitalen Endwert 65h an.

6

Bild: Bildung des Digitalwertes NADC nach dem Verfahren der sukzessiven Approximation

D/A-Wandlung

Die Wandlung von digitalen zu analogen Werten kann sehr einfach mittels eines sog.

R/2R-Widerstandsnetzwerk realisiert werden. Wie die Bezeichnung impliziert, werden

nur R- und 2R-Wiederstände verwendet.

Das nachstehende Bild zeigt die interne Schaltung des 4-Bit D/A-Wandlers. Das Widerstandsnetzwerk erzeugt aus einer Referenzspannung UREF+ Teilspannungen im Verhältnis der Wertigkeit der Binärziffern No, N1, N2 und N3. Der Operationsverstärker kumuliert die Teilspannungen zu der Ausgangsspannung UsIN.

UsIN = (N3 x UREF+/1) + (N2 x UREF+/2) + (N1 x UREF+/4) + (N0 x UREF+/8)

Genau genommen trägt jeder mit „1“ geschaltete Zweig zum Ausgangsstrom Ik bei.

Durch Zuschaltung (=“1“) und Abschaltung (=“0“) der einzelnen Zweige summieren sich

die gewichteten Ströme zum Ausgangsstrom Ik.

Ik = (N3 x UREF+/2R) + (N2 x UREF+/4R) + (N1 x UREF+/8R) + (N0 x UREF+/16R)

7

Der Operationsverstärker arbeitet als Nullfolger und dient der Lastentkopplung. Er erzeugt eine dem Strom Ik proportionale Ausgangsspannung.

U = -R x Ik

Wird Ik eingesetzt erhält man nach der Vereinfachung den Zusammenhang

U = -[ (N3 x 23) + (N2 x 22) + (N1 x 21) + (N0 x 20) ] / [UREF+ / 24]

somit

U = -N x UREF+ / 24 = -N x ULSB

UREF+/2

UREF+

IREF+ = UREF+ / R

UREF+

=

2R

2R

MSB

N3

UREF+/8

UREF+/4

R

R

0

mit ULSB = UREF+ / 2n mit n = 4 (im Bsp.)

R

2R

2R

2R

LSB

N2

1

0

N1

1

0

N0

1

0

1

- R * Ik

Ik

+

Binärwert: 00102

ca. 0V

R

-

UsIN

Bild: Realisierung eines D/A-Wandlers mit einem R/2R Widerstandsnetzwerk

9.1.4.

Der Flash A/D-Wandler

The highest speed conversions are made with flash ADCs. The high speed is made

possible by the use of simultaneous comparisons of the analog input voltage to references generated from a resistor string. A block diagram of a flash ADC is shown in the

next figure.

For an n-bit flash converter, there are 2n – 1 reference voltages and 2n – 1 comparators

required. Thus, for an 8-bit flash converter, 255 comparators are required, and for a 10bit flash converter, 1023 comparators are required. A high price is paid for the speed

advantage-high power, large silicon area for the ICs, and high cost contribute to the

price that must be paid.

8

The conversion process is rather simple. The reference voltages are connected to the

minus input of each comparator and are separated in value by one LSB.

The analog input voltage is connected to the plus input of each comparator. A simultaneous comparison is made at each comparator. If the input analog voltage on the plus

input is less than the reference voltage on the minus input, the output of the comparator

is a 0.

The comparator output will be a 1 if the input analog voltage is greater than the reference voltage. Each comparator output is presented to the decoder at the same time and

the decoder’s output is stored as an n-bit wide code in a latch. All the inputs of the input

analog voltage that are greater than their respective resistor-string reference voltages

will have comparator outputs of a 1; all the inputs that are less than their respective resistor-string reference voltage will have comparator outputs that are 0. The resultant

digital code into the decoder results in the equivalent binary output code, for a given nbit code, that represents the value of the input analog voltage.

Bild: Blockdiagramm eines Flash A/D-Wandlers

9

9.2. Allgemeines zum Analog-Digital Converter Modul (ADC12)

Das Analog Digital Converter Modul (ADC12) erlaubt schnelle 12-Bit analog-zu-digital

Wandlungen.

Das ADC-Modul besitzt

eine 12-bit SAR core

einen Eigangs-Kanalmultiplexer (sample select control)

Sample & Hold Schaltung

Interne Spannungsreferenzen (1,5 und 2,5V)

Einen 16 Word conversion-and-control buffer, allows up to 16 independent ADC

samples to be converted and stored without any CPU intervention.

ADC12 features include:

Greater than 200 ksps (kilo samples per second) maximum conversion rate

Monotonic 12-bit converter with no missing codes

Sample-and-hold with programmable sampling periods controlled by software or timers.

Conversion initiation by software, Timer_A, or Timer_B

Software selectable on-chip reference voltage generation (1.5 V or 2.5 V)

Software selectable internal or external reference

Eight individually configurable external input channels (twelve on MSP430FG43x devices)

Conversion channels for internal temperature sensor, AVCC, and external references

Independent channel-selectable reference sources for both positive and negative

references

Selectable conversion clock source

Single-channel, repeat-single-channel, sequence, and repeat-sequence conversion

modes

ADC core and reference voltage can be powered down separately Interrupt vector

register for fast decoding of 18 ADC interrupts

16 conversion-result storage registers

10

Bild: MSP430x44x functional block diagrams

Bild: Pin Layout des MSP430x449 (top view)

11

9.3. Struktur des Analog-Digital-Wandlermoduls

Most MSP430 devices offer a precision analog-to-digital converter. There are various flavors of converter available. We will describe the most common, the ADC12. If your device

offers a different unit, it is very similar to the 12-bit version described here, and the relevant

differences and detail are available in the user’s guide.

Bild: ADC12 Blockdiagramm

It is important to note that the ADC is by far the most complex of the peripherals available

for the MSP430. My intent here is to cover the high points of its use, but my description is

by no means complete. If you intend to use the ADC, first become intimate with the contents of the user’s guide. I only hope to give the reader a feel for the capabilities and limitations of the peripheral.

12

Bild: Strukturbild des AD-Wanders

The ADC12 is a single 12-bit analog-to-digital converter, with a built-in sample-and-hold

circuit. The front end consists of a multiplexer circuit, allowing the developer to select one

of eight external pins, or one of four internal sources, for the signal to convert. The most

interesting of these is an internal temperature diode, which allows the ADC to provide a

rough idea of operating temperature. The temperature diode varies by device, and the details are in the datasheet. It is considerably less accurate than a true external temperature

sensor, but it can be a useful low-cost alternative in some applications.

9.4. Betriebsarten des ADC12 (Conversion Modes)

There are four conversion modes, reflecting the permutations of single and multiple conversions and one-time and repeated conversions. Specifically, they are:

Single channel one-shot.

This is the true single conversion, with the result being stored in one of the

ADCMEM registers.

Single channel repeated.

As the name would suggest, this mode repetitively performs conversion until

stopped, storing the result in the same ADCMEM register. In this mode, the typical

method is to loop process when the BUSY flag clears.

Multiple channels, single sequence.

In this method, the ADC performs multiple conversions, looping through a specified

number of ADCMEM registers one time.

13

Multiple channels repeated.

This is identical to the previous case, except the series of conversions is repeated

until stopped.

One of the nice things about these modes is that they are all fire-andforget, meaning that

you can write the code so that the process is initialized, and the code can perform other

processing while the conversion is underway. The biggest limitation is that, in the repeated

modes, the software needs to be ready to read the ADCMEM registers before they are rewritten, or an interrupt will be generated.

Timing for the ADC is performed by the conversion clock. The conversion clock may be

sourced by any of the clocks from the Basic Clock Module, or by a fixed RC oscillator,

which is a dedicated portion of the ADC. This oscillator is very similar to the DCO, with the

same limits of accuracy. It is however, a fixed speed oscillator, running around the max

DCO frequency, which is just shy of 5 MHz (typical). This is nice to have, so that the ADC

can operate while the CPU is in sleep mode. The timer must be initialized in the

ADC12CTL1 register, and the DIV value and clock source must be selected such that the

conversion frequency meets the datasheet spec. The conversion takes thirteen cycles of

the conversion clock source.

9.5. Elektrische Anschaltung des Sensors

Isource = (0.25 x Vref) / Rext

Vref = VSVCC – VAVSS

Rext, external adjust resistor

Power Down bit ACTL12 switches current source off

Control bit ACTL.8 swiches current source on or off

Current source output on A0, A1, A2 and A3

Bild: AD-Converter - Absolute Measurement

14

Bild: AD-Converter - External Sensors R-Type

9.6. Auflösung des ADCs

The ADC core converts an analog input to its 12-bit digital representation and stores the

result in conversion memory. The core uses two programmable/ selectable voltage levels (VR+ and VR−) to define the upper and lower limits of the conversion. The digital

output (NADC) is full scale (0FFFh) when the input signal is equal to or higher than

VR+, and zero when the input signal is equal to or lower than VR−. The input channel

and the reference voltage levels (VR+ and VR−) are defined in the conversion-control

memory.

The conversion formula for the ADC result NADC is:

The ADC12 core is configured by two control registers, ADC12CTL0 and ADC12CTL1.

The core is enabled with the ADC12ON bit. The ADC12 can be turned off when not in

use to save power. With few exceptions the ADC12 control bits can only be modified

when ENC = 0. ENC must be set to 1 before any conversion can take place.

9.7. Die Sample&Hold Schaltung

15

An analog-to-digital conversion is initiated with a rising edge of the sample input signal

SHI. The source for SHI is selected with the SHSx bits and includes the following:

The ADC12SC bit

The Timer_A Output Unit 1

The Timer_B Output Unit 0

The Timer_B Output Unit 1

The polarity of the SHI signal source can be inverted with the ISSH bit. The SAMPCON

signal controls the sample period and start of conversion. When SAMPCON is high,

sampling is active. The high-to-low SAMPCON transition starts the analog-to-digital

conversion, which requires 13 ADC12CLK cycles.

Bild: Sample & Hold Schaltung des ADC12

Legende:

Rs

Impedanz der zu messenden Spannungsquelle (externe Hardware)

Eingangsspannung

UsIN

Ri

Ci

Impedanz des gewählten analogen Eingangs Ax (max. 2 kΩ)

Interne Kapazität des analogen Eingangs Ax ( max. 40 pF)

Two different sample-timing methods are defined by control bit SHP, extended sample

mode and pulse mode.

The analog input signal must be valid and steady during the sampling period in order to

obtain an accurate conversion. It is also desirable not to have any digital activity on any

adjacent channels during the whole conversion period to ensure that errors due to supply glitching, ground bounce, or crosstalk do not corrupt the conversion results.

Bild: Sample and Conversion, Basic Signal Timing

16

Das vorherige und die nachfolgenden Bilder zeigen die Sample und die Umsetzungszeit.

Um dem Kondensator Ci Zeit zu geben, sich soweit aufzuladen, dass die Abweichung

nur noch ½ LSB beträgt, muss die minimale Erfassungszeit tsample-min größer sein als

tsample-min > (Rsmax + Rimax) x Cimax x 9,01

(gültig für ADC12 beim MSP430x449)

Die Erfassungszeit tsample wird durch den A/D-Wandlertakt ADC12CLK und die Steuerbits SHT0.x und SHT1.x im Controlregister ADC12CTL0 bestimmt.

SHT0.x definiert dabei die Erfassungszeit für die Memory Control Bytes 0 bis 7,

SHT1.x definiert die Erfassungszeit für die Memory Control Bytes 8 bis 15.

Die Erfassungszeit tsample ist dann:

tsample = (k x n ) / fADCin

mit

fADCin = ADC12-Taktfrequenz (ACLK, MCLK, SMCLK, interner Oszillator) in Hz

k = Eingangsuntersetzung für fADCin (1, 2, 3, 4, 5, 6, 7, 8)

n = ADC12CLK-Taktzyklen definiert durch SHTx

Bsp.:

Die Messzeit einer einzelnen A/D-Wandlung ist die Summe aus der Erfassungszeit und

der Umwandlungszeit

tmess = tsample + tconvert

tmess = tsample + (k x 13) / fADCin

mit

fADCin = ADC12-Taktfrequenz (ACLK, MCLK, SMCLK, interner Oszillator) in Hz

k = Eingangsuntersetzung für fADCin (1, 2, 3, 4, 5, 6, 7, 8)

Pulse Sample Mode

The pulse sample mode is selected when SHP = 1. The SHI signal is used to trigger the

sampling timer. The SHT0x and SHT1x bits in ADC12CTL0 control the interval of the

17

sampling timer that defines the SAMPCON sample period tsample. The sampling timer

keeps SAMPCON high after synchronization with AD12CLK for a programmed interval

tsample. The total sampling time is tsample plus tsync.

The SHTx bits select the sampling time in 4x multiples of ADC12CLK. SHT0x selects

the sampling time for ADC12MCTL0 to 7 and SHT1x selects the sampling time for

ADC12MCTL8 to 15.

Bild: Pulse Sample Mode

Extended Sample Mode

The extended sample mode is selected when SHP = 0. The SHI signal directly controls

SAMPCON and defines the length of the sample period tsample. When SAMPCON is

high, sampling is active. The high-to-low SAMPCON transition starts the conversion after synchronization with ADC12CLK. See Figure 20−3.

Bild : Extended Sample Mode

18

9.8. ADC12 Control Registers

19

Bild: Übersicht der ADC12 Register

9.8.1.

ADC Control Register 0 (ADC12CTL0)

Address: 0x01A0h

All bits are read/write. Bits 15 through 4 may only be edited when ENC=0.

Bild: Codierung des ADC control register ADC12CTL0

20

SHT1.3, SHT1.2, SHT1.1, SHT1.0 /

SHT1.x determines sample and hold time for ADC8 through ADC15

Sample-and-hold Time1. These bits define the sample timing for conversions

whose results are stored in conversion-memory registers ADC12MEM8 to

ADC12MEM15.

The sample time is a multiple of the ADC12CLK × 4:

SHT0.3, SHT0.2, SHT0.1, SHT0.0: Sample and Hold Time0

and SHT0 determines the sample and hold time for ADC0 through ADC7.

Sample-and-hold Time0. These bits define the sample timing for conversions

whose results are stored in conversion-memory registers ADC12MEM0 to

ADC12MEM7.

The sample time is a multiple of the ADC12CLK × 4:

SHTx.3 SHTx.2 SHTx.1 SHTx.0 -Bits

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

n-Value

1

2

4

8

16

24

32

48

64

96

128

256

256

256

256

256

Table: n-Values for SHT-variable

21

MSC:

Multiple Sample and Convert:

0: The sampling timer requires a rising edge on SHI.

1: SHI triggers the first sample, all subsequent samples are automatic.

2_5V: Internal Reference Voltage level

0: 1.5 VDC

1: 2.5 VDC

REFON: Internal Reference Voltage enable

0: Internal Reference is off

1: Internal Reference is on

ADCON: Analog to Digital Converter ON

0: ADC is off

1: ADC is on

ADCOIE: ADC Overflow Interrupt Enable

Individual enable for the overflow-interrupt vector.

If set, an interrupt is generated on overflow. ADC overflow is defined as the

condition that occurs when a result is written and the previous result has not

been read.

The overflow happens if a conversion result is written into an ADC memory

ADC12MEMx but the previous result was not read. An interrupt service is requested if the overflow vector is generated, the overflow-interrupt-enable flag

ADC12OVIE is set, and the general-interrupt-enable bit GIE is set. There is

no individual interrupt flag. See the ADC12 Interrupt Vector Register

ADC12IV section for more information on ADC12 interrupts.

ADCTIE: ADC Timer Overflow Interrupt Enable

Individual enable for the timer overflow-interrupt vector.

If set, an interrupt is generated on ADC timer overflow. ADC timer overflow is

defined as the condition that occurs when a conversion is attempted before

the previous conversion is attempted.

The timing overflow happens if another sample-and-conversion is requested

while the current conversion is not completed. This is independent of the

conversion modes selected by CONSEQ. If the timing overflow vector is generated and the timing overflow interrupt enable flag ADC12TOVIE and the

general interrupt enable bit GIE are set, an interrupt service is requested.

There is no individual interrupt flag. See the ADC12 Interrupt Vector Register

ADC12IV section for more information on ADC12 interrupts.

ENC:

Enable Conversion

If cleared, no conversion is possible. If set, a conversion is possible. The

ADCMCTL registers cannot be edited unless this bit Is cleared. The typical

process is to set the ADC up, and then bring this bit high.

ADC_SC: ADC Sample and Convert

22

When set, the conversion process automatically begins (if ENC=1). This bit is

automatically reset when the conversion is complete.

9.8.2.

ADC Control Register 1 (ADC12CTL1)

Address: 0x01A2h

All bits except 0 (BUSY) are read/write. Bits 15 through 3 may only be edited when

ENC=0.

Bild: Codierung des ADC control register ADC12CTL1

CSAdd3, CSAdd2, CSAdd2, CSAdd1, CSAdd0: Conversion Start Address

Selects which ADC12MEM register is used for the first conversion in a sequence.

SHS1, SHS0: Source Select for the Sample-Input Signal.

0 0 : Control Bit ADC12SC

0 1 : Timer A.OUT.1

1 0 : Timer_B.OUT.0

1 1 : Timer_B.OUT.1

SHP:

Sampling Signal Select

0:

SAMPCOM is sourced from the sample-input signal.

1:

SAMPCOM is sourced from therising edge of the sampling timer.

ISSH: Invert Sample-Input Signal

0:

The Sample-Input Signal isnormally defined.

1:

The Sample-Input Signal isinverted.

DIV2, DIV1, DIV0: Clock Division Rate

The clock selected by SSEL is divided by DIV+1

SSEL1, SSEL0: Clock Source Select

00: ADC Internal Oscillator

01: ACLK

10: MCLK

11: SMCLK

CONS1, CONS0: Conversion Mode Select

00: Single-Channel, Single Conversion

01: Single Sequence of Channels

23

10: Repeat in a single channel until CONS is changed

11: Repeat in a sequence of channels until CONS is changed.

BUSY: Busy Flag (read-only)

This read-only flag is set while aconversion is underway.

9.8.3.

ADC Memory Control Registers 0 - 15 (ADC12MCTLn)

Addresses: 0x0080h through 0x008F

All bits are read/write.

All bits may only be edited when ENC=0.

Bild: Codierung des ADC control register ADC12MCTLn

EOS : End Of Sequence

This bit indicates when a sequence of conversions is complete.

SREF2, SREF1, SREF0 :

Reference Voltage Select

V+

V0 0 0 : V+ is AVcc,

V- is AVss

0 0 1 : V+ is VREF+,

V- is AVss

0 1 0 : V+ is Ve REF+,

V- is AVss

0 1 1 : V+ is VeREF+,

V- is AVss

1 0 0 : V+ is AVcc,

V- is VREF- / Ve REFV- is VREF- / Ve REF1 0 1 : V+ is VREF+,

1 1 0 : V+ is VeREF+,

V- is VREF- / Ve REF1 1 1 : V+ is VeREF+,

V- is VREF- / VeREFLegende:

DVcc, Vcc

DVss, GND

Avcc

AVss

VeREFVeREF+

VREFVREF+

Positive Versorgungsspannung für Digitalschaltung

Negative Versorgungsspannung für die Digitalschaltung

(digitale Masse)

Analog Voltage Common (Analoge Versorgungsspannung)

Analog Source-Voltage (Analoge Masse)

Negative Referenzspannung von extern

Postitive Referenzspannung von extern

Negative Referenzspannung von extern

Postitive Referenzspannung von extern

24

Bild: Auswahl der Referenzspannungen V+ und V- für ADC12 Core

INCH3, INCH2, INCH1, INCH0: Input Channel Select

0 0 0 0 : Select Channel 0

0 0 0 1 : Select Channel 1

0 0 1 0 : Select Channel 2

0 0 1 1 : Select Channel 3

0 1 0 0 : Select Channel 4

0 1 0 1 : Select Channel 5

0 1 1 0 : Select Channel 6

0 1 1 1 : Select Channel 7

1 0 0 0 : Select Channel 8 = VeREF+

1 0 0 1 : Select Channel 9 = VREF- / VeREF1 0 1 0 : Select Channel 10 = Internal Temperature Diode

1 0 1 1 : Select Channel 11 = (AVcc- AVss)/2

1 1 0 0 : Select Channel 12 = (AVcc- AVss)/2

1 1 0 1 : Select Channel 13 = (AVcc- AVss)/2

1 1 1 0 : Select Channel 15 = (AVcc- AVss)/2

1 1 1 1 : Select Channel 16 = (AVcc- AVss)/2

25

9.8.4.

ADC Interrupt Enables (ADC12IEN)

Address: 0x01A6h

All bits are read/write.

All interrupt flags and interrupt-enable bits are reset during POR.

Bild: ADC12 Interrupt Enable Registers

These are standard interrupt flags and enable bits, with bit 15 of each field corresponding to ADC12MEM15, etc. If the ADCMEM registers are accessed, their corresponding interrupt flags are automatically reset.

ADC12IE.x, bits 0–15 The ADC12IE.x interrupt-enable bit enables or disables the interruptrequest service generated if the corresponding interrupt flag ADC12IFG.x is set.

The range for x is 0 to 15.

9.8.5.

ADC Interrupt Flags (ADC12IFG)

Address: 0x01A4h

All bits are read/write.

All interrupt flags and interrupt-enable bits are reset during POR.

Bild: ADC12 Interrupt Flags

ADC12IFG.x, bits 0–15 The ADC12IFG.x interrupt flag is set if a conversion-result register ADC12MEMx is loaded with the result of a conversion. The range for x is 0 to 15.

The interrupt flags are reset if their corresponding ADC12MEMx conversion-result register is accessed. To enable correct handling of overflow conditions, they are not reset

by accessing the interrupt vector word ADC12IV. The overflow condition exists if another conversion result is written to ADC12MEMx and the corresponding ADC12IFG.x is

not reset.

9.8.6.

Das Conversion Memory Registers 0-15 (ADC12MEMx)

Addresses: 0x0140h-0x0156h

26

All significant bits (11-0) are read/write. Bits 15-12 read as 0.

These 16 registers hold the result of conversions in the bottom 12 bits.

To Reference

ADC12MCTLx4-6

080h

081h

08Eh

08Fh

7

EOS

6

4

SREF

To ADC Core

ADC12MCTLx.0-3

ADC12 Results

ADC12MCTL0

ADC12MCTL1

ADC12MEM0

ADC12MEM1

16 x 8-Bit

ADC Memory

Control

16 * 8-bit

ADC Memory

Control

ADC12MCTL14

ADC12MCTL15

ADC12MEM14

ADC12MEM15

3

0

15

INCH

12

0140h

0142h

015Ch

015Eh

11

0

rw

ADC Memory Control Byte

1

12-Bit Measurement Result

r

ADC Memory Register

9.9. ADC12 Interrupts and Interrupt Handling

The ADC12 has 18 interrupt sources:

ADC12IFG0-ADC12IFG15

ADC12OV, ADC12MEMx overflow

ADC12TOV, ADC12 conversion time overflow

The ADC12IFGx bits are set when their corresponding ADC12MEMx memory register is

loaded with a conversion result. An interrupt request is generated if the corresponding

ADC12IEx bit and the GIE bit are set. The ADC12OV condition occurs when a conversion result is written to any ADC12MEMx before its previous conversion result was

read. The ADC12TOV condition is generated when another sample-and-conversion is

requested before the current conversion is completed.

ADC12 Interrupt Vector Register ADC12IV

The 12-bit ADC has one interrupt vector to assist the handling of the 18 possible interrupt flags. Each of the 18 interrupt flags is prioritized and a unique vector word is generated according to the highest-pending interrupt. The priorities and corresponding vectorword values are shown in Table 17–3.

Overflow flag ADC12OVIFG has the highest priority, followed by timing overflow flag

ADC12TOVIFG, and then by the interrupt flags for each conversion-memory register

ADC12IFG.0 to ADC12IFG.15.

27

The highest-pending interrupt flag generates a number from 0 (no interrupt is pending)

to 36. This encoded number can be added to the program counter to automatically enter

the software routine for handling each specific interrupt.

An interrupt request is immediately generated if an interrupt flag is pending

(ADC12IV≠0), if the corresponding interrupt enable bit (ADC12OVIE, ADC12TOVIE, or

ADC12IE.x) is set, and if the general interrupt enable bit GIE is set. When an interrupt

request is generated, the service is requested by the highest-priority interrupt that is enabled.

It is important to note that ADC12OVIFG and ADC12TOVIFG are reset automatically

when either is the highest pending interrupt and the ADC12IV register is accessed. For

example, if both are pending simultaneously, ADC12OVIFG will be reset automatically

with the first access of ADC12IV, and ADC12TOVIFG will be reset automatically with

the next access to the ADC12IV (assuming ADC12OVIFG was not set again). However,

flags ADC12IFG.x must be reset by software or reset by accessing the corresponding

conversion-memory register ADC12MEMx.

Also note that the flags ADC12OVIFG and ADC12TOVIFG can not be accessed by

software. They are visible only via the interrupt vector word ADC12IV data.

Bild: ADC12IV Interrupt-Vector Values

The ADC12IV, Interrupt Vector Generator

All ADC12 interrupt sources are prioritized and combined to source a single interrupt

vector. The interrupt vector register ADC12IV is used to determine which enabled

ADC12 interrupt source requested an interrupt.

The highest priority enabled ADC12 interrupt generates a number in the ADC12IV register (see register description). This number can be evaluated or added to the program

counter to automatically enter the appropriate software routine. Disabled ADC12 interrupts do not affect the ADC12IV value.

28

Any access, read or write, of the ADC12IV register automatically resets the ADC12OV

condition or the ADC12TOV condition if either was the highest pending interrupt. Neither interrupt condition has an accessible interrupt flag.

The ADC12IFGx flags are not reset by an ADC12IV access. ADC12IFGx bits are reset

automatically by accessing their associated ADC12MEMx register or may be reset with

software.

If another interrupt is pending after servicing of an interrupt, another interrupt is generated. For example, if the ADC12OV and ADC12IFG3 interrupts are pending when the

interrupt service routine accesses the ADC12IV register, the ADC12OV interrupt condition is reset automatically. After the RETI instruction of the interrupt service routine is

executed, the ADC12IFG3 generates another interrupt.

Bild: Auszug aus der Datei msp430x44x.h

;;/**************************************************

;; * Definitions of I/O register description file,

;; * interrupt/exception vectors, interrupt control registers,

;; * I/O register reset values.

;; * Copyright 2001-2003 IAR Systems. All rights reserved.

;; *

;; **************************************************/

;; Memory information ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;

;; Used to define address zones within the MSP430 address space (Memory).

;;

;;

Name

may be almost anything

;;

AdrSpace must be Memory

;;

StartAdr start of memory block

;;

EndAdr

end of memory block

;;

AccType

type of access, read-only (R) or read-write (RW)

;;

[Memory]

;;

Name

AdrSpace

StartAdr

EndAdr

AccType

Memory0 = SFR

Memory

0x0000

0x01FF

RW

Memory1 = RAM

Memory

0x0200

0x09FF

RW

Memory2 = INFO

Memory

0x1000

0x10FF

R

Memory3 = FLASH

Memory

0x1100

0xFFDF

R

29

;;

;; I/O Register description file ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;

[SfrInclude]

File = MSP430F449.sfr

;;

;; Interrupt definitions ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;

[InterruptList]

;

Id

Table Adr

Prio

Enable

Pending

Interrupt0

= BASICTIMER_VECTOR 0x00

2

IE2.BTIE

IFG2.BTIFG

Interrupt1

= PORT2_VECTOR

0x02

2

P2IE.P2IE_0

P2IFG.P2IFG_0

Interrupt2

= PORT2_VECTOR

0x02

2

P2IE.P2IE_1

P2IFG.P2IFG_1

Interrupt3

= PORT2_VECTOR

0x02

2

P2IE.P2IE_2

P2IFG.P2IFG_2

Interrupt4

= PORT2_VECTOR

0x02

2

P2IE.P2IE_3

P2IFG.P2IFG_3

Interrupt5

= PORT2_VECTOR

0x02

2

P2IE.P2IE_4

P2IFG.P2IFG_4

Interrupt6

= PORT2_VECTOR

0x02

2

P2IE.P2IE_5

P2IFG.P2IFG_5

Interrupt7

= PORT2_VECTOR

0x02

2

P2IE.P2IE_6

P2IFG.P2IFG_6

Interrupt8

= PORT2_VECTOR

0x02

2

P2IE.P2IE_7

P2IFG.P2IFG_7

Interrupt9

Interrupt10

= USART1TX_VECTOR

= USART1RX_VECTOR

0x04

0x06

2

2

IE2.UTXIE1

IE2.URXIE1

IFG2.UTXIFG1

IFG2.URXIFG1

Interrupt11

Interrupt12

Interrupt13

Interrupt14

Interrupt15

Interrupt16

Interrupt17

Interrupt18

=

=

=

=

=

=

=

=

PORT1_VECTOR

PORT1_VECTOR

PORT1_VECTOR

PORT1_VECTOR

PORT1_VECTOR

PORT1_VECTOR

PORT1_VECTOR

PORT1_VECTOR

0x08

0x08

0x08

0x08

0x08

0x08

0x08

0x08

2

2

2

2

2

2

2

2

P1IE.P1IE_0

P1IE.P1IE_1

P1IE.P1IE_2

P1IE.P1IE_3

P1IE.P1IE_4

P1IE.P1IE_5

P1IE.P1IE_6

P1IE.P1IE_7

P1IFG.P1IFG_0

P1IFG.P1IFG_1

P1IFG.P1IFG_2

P1IFG.P1IFG_3

P1IFG.P1IFG_4

P1IFG.P1IFG_5

P1IFG.P1IFG_6

P1IFG.P1IFG_7

Interrupt19

Interrupt20

Interrupt21

Interrupt22

=

=

=

=

TIMERA1_VECTOR

TIMERA1_VECTOR

TIMERA1_VECTOR

TIMERA0_VECTOR

0x0A

0x0A

0x0A

0x0C

2

2

2

2

TACCTL1.CCIE

TACCTL2.CCIE

TACTL.TAIE

TACCTL0.CCIE

TACCTL1.CCIFG

TACCTL2.CCIFG

TACTL.TAIFG

TACCTL0.CCIFG

Interrupt23

Interrupt24

Interrupt25

Interrupt26

Interrupt27

=

=

=

=

=

ADC_VECTOR

USART0TX_VECTOR

USART0RX_VECTOR

WDT_VECTOR

COMPARATORA_VECTOR

0x0E

0x10

0x12

0x14

0x16

2

2

2

2

2

ADC12IE

IE1.UTXIE0

IE1.URXIE0

IE1.WDTIE

CACTL1.CAIE

ADC12IFG

IFG1.UTXIFG0

IFG1.URXIFG0

IFG1.WDTIFG

CACTL1.CAIFG

Interrupt28

Interrupt29

Interrupt30

Interrupt31

Interrupt32

Interrupt33

Interrupt34

Interrupt35

=

=

=

=

=

=

=

=

TIMERB1_VECTOR

TIMERB1_VECTOR

TIMERB1_VECTOR

TIMERB1_VECTOR

TIMERB1_VECTOR

TIMERB1_VECTOR

TIMERB1_VECTOR

TIMERB0_VECTOR

0x18

0x18

0x18

0x18

0x18

0x18

0x18

0x1A

2

2

2

2

2

2

2

2

TBCCTL1.CCIE

TBCCTL2.CCIE

TBCCTL3.CCIE

TBCCTL4.CCIE

TBCCTL5.CCIE

TBCCTL6.CCIE

TBCTL.TBIE

TBCCTL0.CCIE

TBCCTL1.CCIFG

TBCCTL2.CCIFG

TBCCTL3.CCIFG

TBCCTL4.CCIFG

TBCCTL5.CCIFG

TBCCTL6.CCIFG

TBCTL.TBIFG

TBCCTL0.CCIFG

0x1C

0x1E

2

1

IE1.OFIE

IFG1.NMIIFG

Interrupt36 = NMI_VECTOR

Interrupt37 = RESET_VECTOR

;; End of file

Bild: Auszug aus der Datei msp430F449.ddf (Device Description File)

30

9.10. Konstantendefinitionen zum ADC12 (msp430x44x.h)

Auszug aus der Datei msp430x44x.h

31

32

33

34

9.11. Bsp: Erfassung der MSP430 internen Temperatursensors

As described previously, the ADC units on many devices include a temperature sensor.

This nice little add-on feature is easy to use and is pretty accurate (typically within a degree or so). Code listing 6.1 provides a C-language module for reading temperature. Several considerations are:

This code is written assuming 3.35 mV/°C, as is the case with the ’149 device. If you

are using a different device, check your datasheet for the correct value.

The conversions from ADC reading to °C and from there to °F are designed to avoid

use of floating-point mathematics. They will result in some additional error. However,

the total error from both conversion and mathematics will still keep you within a degree

or two. If your application requires precise measurement of temperature, consider an

external sensor.

The variable sizing of this function is a bit on the inefficient side. It is overkill to report a

value between –50 and +200 using a signed long, but the conversion to temperature

requires more than 15 bits of precision. In fact, if we turn the function into a signed int, it

should automatically return the bottom 16 bits of the Temperature variable, which will

still give us the correct value. However, various experiences doing things like this have

left me distrustful of microcontroller compilers and their ability to always do what they I

think they ought to.

Bild: Übertragungsfunktion des Temperatursensors

35

//This function returns device temperature, based on an ADC conversion

//The passed parameter acts as a flag. If it is zero, the temperature is

//returned in degrees Fahrenheit. If it is non-zero, it is returned in

//degrees Celsius.

signed long Determine_Temp (unsigned char BooleanFlag)

{

signed long Temperature=25; //Define and initialize working variable

ADC12CTL0 = SHT0_6 + SHT1_6 + REFON + ADC12ON;

// Initialize control register 0.

// Sets up conversion clock, internal reference

ADC12CTL1 = SHP;

// Conversion sample timer signal is

// sourced from the sampling timer

ADC12MCTL0 = INCH_10 + SREF_1;

// Use internal reference with

// respect to ground, Temp sensor

// is on input channel 10.

ADC12CTL0 |= ADC12SC + ENC;

// Enable and start conversion

while (ADC12CTL1 & 0x01);

// Hang in loop until conversion completes.

Temperature = ADC12MEM0 & 0x00000FFF;

Temperature *= 845;

// These steps convert the ADC

// reading to degrees Celsius

Temperature >> = 13;

Temperature -= 278;

if (BooleanFlag)

return Temperature; //Return temperature in degrees Celsius,

// if required

Temperature *=461;

Temperature >.=8;

// Otherwise, convert to Fahrenheit and return

Temperature +=32;

}

return Temperature;

// End Determine Temperature Function

Listing 6.2: Temperature Determination using the ADC-12

9.12. Beispiel: Erfassung eines externen Analogsignals

Beim MSP430 handelt es sich um einen 12-Bit-AD-Wandler (TI-Bezeichnung ADC12).

Er verfügt über 8 Kanäle, die sich an den Pins 2-6 und 59-61 befinden, bzw. an Port 6.0

bis 6.7. Streng genommen gibt es noch 3 weitere Kanäle (8, 9 und 10), die für interne

Messzwecke verwendet werden. Über Kanal 10 kann z. B. der interne Temperatursensor

angespreochen werden; er kann über INCH_10 gewählt und mit 2,5 Volt verglichen werden. Hier soll zunächst Port 6.0 bis 6.7 als Eingänge des AD-Wandlers benutzt werden.

Ein AD-Wandler wandelt analoge, kontinuierliche Spannungen in digitale Äquivalente um.

Die Anwendungsmöglichkeiten des ADC12 sind sehr vielfältig: So könnte man sich z. B.

im allereinfachsten Fall ein Voltmeter bauen.

36

Anschlussschaltung:

Ein 47k-Poti ist über VCC an den AD-Wandler angeschlossen. Die Beschaltung dieses

Potis ist trivial:

Bild: Beschaltung des AD-Wandlereingangs

Das eine Ende an VCC, das andere an GND und den Mittenabgriff an P6.0. Man erkennt,

dass nun also je nach Stellung des Potis irgendeine Spannung zwischen VCC und GND,

also zwischen 0 und 3,3 Volt, an dem AD-Wandler anliegt. Im Rahmen der Aufgabenstellung soll eine LED leuchten, wenn die anliegende Spannung größer als 1,25 Volt ist

Das Programm:

Das Programm beginnt mit dem Einbinden der Header-Datei, der Definition der Prototypen

und dem Abschalten des Watchdogs.

Port 1 werden wegen der LEDs als Ausgänge (Output) beschaltet, Port 6 wieder als Input.

P6SEL weist nun die erste Neuerung auf:

Alle Pins weisen eine Doppelbelegung auf. So kann man die Pins an Port 6 als GPIO (general purpose input/output) und eben auch als Eingänge für die AD-Wandlung benutzen,

die Verwendung als ADC12-Eingänge muss explizit festgelegt werden, und zwar mit

P6SEL=0x01. Die logische "0" kennzeichnet den jeweiligen Pin als GPIO, wohingegen

eine "1" ihm seine Zweitfunktion zuweist. Es sind hier natürlich beliebige Kombinationen

möglich, so würde z.B. ein P6SEL=0xD2 P6.1, P6.4, P6.6 und P6.7 als AD-Wandler-Eingänge benutzen und den Rest (P6.0, P6.2, P6.3 und P6.5) als I/O-Leitungen.

Konfiguration des ADC12:

Zur Steuerung des AD-Wandlers gibt es zwei Register, ADC12CTL0 und ADC12CTL1.

15

8

0

7

ADC12CTL0

REF

ON

SHT1

SHT0

MSC

2_5V

rw-(0)

rw-(0)

rw-(0)

rw-(0) rw-(0)

01A0h

15

8

ADC12

ON

ADC12

OVIE

ADC12

TOVIE

ENC

ADC12

SC

rw-(0)

rw-(0)

rw-(0)

rw-(0)

rw-(0)

7

0

ADC12CTL1

CSStartAdd

SHS

SHP

ISSH

ADC12DIV

ADC12SSEL

CONSEQ

01A2h

rw-(0) rw-(0) rw-(0) rw-(0)

rw-(0) rw-(0) rw-(0)

rw-(0) rw-(0) rw-(0) rw-(0) rw-(0)

rw-(0)

rw-(0)

rw-(0)

ADC12

BUSY

r -(0)

Bild: Steuerregister des AD-Wandlers

Durch Zuweisungen an diese beiden Register kann man alle möglichen Parameter zum

Betrieb des ADC12 einstellen, wie z. B.:

ADC12CTL0 = ADC12ON + SHT0_0 + REFON + REF2_5V;

37

ADC12ON schaltet den ADC12 ein. Wäre ADC12ON nicht gesetzt, wäre der AD-Wandler

komplett ausgeschaltet, was eine etwas geringere Leistungsaufnahme des MSP430 zur

Folge hätte. So läßt sich im Batteriebetrieb Strom sparen.

SHT0_0 bewirkt, dass die Sample-and-Hold-Zeit auf n=1 (und damit also t_sample =

4*ADC12CLK*1), eingestellt wird (siehe Datenblatt). Es solle eine Spannung mit geringer

Dynamik an dem Poti vorausgesetzt werden.

Referenz-Spannung REFON. Der ADC12 benötigt für die Konvertierung eine interne

Ober- und Untergrenze, die sogenannte Referenz-Spannung, damit er weiss, wie er die

Werte dazwischen umwandeln soll. Wählt man z. B. die Untergrenze als 0 Volt und die

Obergrenze als 2,5 Volt, so entspricht eine Spannung von 0 Volt an unserem P6.0 einer

digitalen 000000000000 und 2,5 Volt entprechen 111111111111 (12 Bit).

Für die Referenz-Spannung gibt es prinzipiell zwei verschiedene Wege der Realisierung:

Durch Anlegen einer externen Spannung an einen bestimmten Pin (Nummer 10) oder

durch interne Erzeugung im MSP430. Die interne Erzeugung bietet Referenz-Spannungsquellen von 1,5 und 2,5 Volt. Eine externe Referenz-Spannung wir an Pin 10 angeschlossen. REFON schaltet die interne Referenz-Spannungsquelle ein und schaltet sie mit

REF2_5V auf 2,5 Volt. Wäre REF2_5V nicht gesetzt, würde die Spannungsquelle 1,5 Volt

erzeugen. Der "Arbeitsbereich" ist hierduch etwas eingeschränkt, da alle Spannungen zwischen 2,5 und 3,3 Volt am Poti gleichermaßen zu 111111111111 konvertiert werden.

Die nächste Anweisung ADC12CTL1 = SHP legt fest, dass jegliche Einstellungen zum

Sample-and-Hold-Vorgang automatisch erledigt werden. Der SHP-Modus besagt vereinfacht, dass über einen einzigen Software-Befehl eine AD-Wandlung gestartet werden

kann. Daraufhin wird ein Abtastvorgang ausgelöst (wenige µs lang), gefolgt von der völlig

automatisch eingeleiteten Konvertierung der analogen Spannung in einen digitalen Wert.

Das Ergebnis der Konvertierung wird in ein Register geschrieben, von wo aus es gelesen

und weiter verarbeitet werden kann.

Der nächste Befehl ADC12MCTL0 = SREF_1 + INCH_0 bearbeitet das Kontrollregister

des ersten Ausgaberegisters. Der ADC12 besitzt 16 Register (ADC12MEM0 bis

ADC12MEM15), in denen die Ergebnisse der AD-Wandlung automatisch gespeichert werden. Bei gleichzeitiger Benutzung von 8 AD-Kanälen werden schon 8 Register zur Ablage

der digitalisierten Daten benötigt. Möchte man mehrere Messungen hintereinander durchführen, ohne jedes Mal direkt einen Auslesevorgang starten zu müssen, sieht man, dass

diese 16 Register schon ziemlich sinnvoll sein können.

SREF_1 bewirkt, dass die intern erzeugten 2,5 Volt als Referenz-Spannungsquelle gewählt werden. Durch REFON und REF2_5V wurde die interne Referenz-Spannungsquelle

lediglich eingeschaltet. Wie und wo und ob die Referenz-Spannung benutzt wird, ist aber

noch keinesfalls festgelegt. Das Praktische am ADC12 ist nämlich, dass man für jedes der

16 Register eine eigene Referenz-Spannungsquelle festlegen kann. So kann man ganz

leicht z. B. vier Kanäle mit 2,5 Volt Referenz-Spannung betreiben, zwei mit 1,5 Volt und

zwei mit extern angelegten 3,3 Volt. Die den Registern zugeordneten Kanäle können

ebenfalls frei gewählt werden. Wie man an INCH_0 schon erkennt, ordnen wir

ADC12MEM0 den Kanal 0 (also P6.0, d. h. Pin 59) zu. Zusammengefasst bedeutet das:

Die Spannung an P6.0 wird in einen digitalen Wert mit der Obergrenze 2,5 Volt konvertiert

und anschließend in das Register ADC12MEM0 geschrieben.

38

Der letzte Initialisierungs-Befehl ADC12CTL0 = ADC12CTL0 | ENC ist eine Art zweiter

Schalter. Über ADC12ON wurde der ADC12 schon generell eingeschaltet, über ENC

schalten wir ihn jetzt zum Konvertieren frei. Das hat den Sinn, dass fast alle bisher vorgenommenen Einstellungen nur bei ENC=0 vorgenommen werden können. Durch Setzen

von ENC wir die Konfiguration quasi gültig und geben den ADC12 somit zum Konvertieren

frei.

Das eigentliche Hauptprogramm läuft nun wieder in einer Endlosschleife, welche als erstes

eine AD-Wandlung einleitet; dies geschieht über den Befehl ADC12CTL0 = ADC12CTL0 |

ADC12SC. Nun wird P6.0 für einige Mikrosekunden abgetastet; anschließend wird der

ermittelte Spannungswert konvertiert und das Ergebnis in ADC12MEM0 geschrieben. Anschließend wird geprüft, ob der ermittelte Spannungswert kleiner ist als 0x7FF. Das entspricht 11111111111 (11 Einsen) in binärer Schreibweise, was fast genau die Hälfte von

111111111111 (12 Einsen), dem Maximum des Wertebereiches, entspricht. Ist der Wert

kleiner als 0x7FF (also kleiner als 1,25 Volt), so wird die LED gelöscht, andernfalls wird sie

angeschaltet.

Anschließend ist die Schleife beendet und es wird direkt die nächste Konvertierung mittels

ADC12CTL0 = ADC12CTL0 | DC12SC eingeleitet u.s.w.

Man kann den Wert aus dem ADC12MEM0 ebenso auch auslesen, mit DecToString() oder

IntToString() in einen String umwandeln und über die RS232 Schnittstelle an ein Hyperterminalprogramm ausgeben.

39

Bild: Struktogramm zum Programm

/* ad_code.c */

#include <msp430x14x.h>

void wait(unsigned int i);

// prototypen

int main(void)

{

WDTCTL = WDTPW + WDTHOLD; // watchdog aus

P1DIR=0xFF;

// port 1 = output (3 LEDs)

P6DIR=0x00;

// port 6 = input (4 taster und 1 poti)

P1SEL=0x00;

P6SEL=0x01;

// port 1 komplett als GPIO nutzen

// P6.0 als AD-Wandler benutzen, den Rest als GPIO

P1IE=0x00;

// interrupt abschalten

P1OUT=0x00;

// initial alle LEDs aus

40

ADC12CTL0 = ADC12ON+SHT0_0+REFON+REF2_5V;

// ADC12 anschalten, n=1, referenz auf 2,5V setzen

ADC12CTL1 = SHP;

// SHP benutzen

ADC12MCTL0 = SREF_1+INCH_0; // Vr+=Vref+

ADC12CTL0 |= ENC;

// jetzt anfangen ...

while (1)

{

ADC12CTL0 |= ADC12SC;

wait(10000);

// infinite loop

// konvertierung durchfuehren

if (ADC12MEM0 <= 0x7FF)

{

P1OUT&=~0x01;

// rote LED aus

}

else

{

P1OUT|=0x01;

// rote LED an

}

}

}

void wait(unsigned int i) // delay function

{

unsigned int j;

for (j=0;j<i;j++) ;

}

Programmlisting: Sourcecode zum AD-Wandler

9.13. Beispiel: PT-100 Temperaturerfassung mit hoher Auflösung

Erweiterung der Hardware um einen zusätzlichen Messverstärker

Bei der vorhandenen minimalen externen Beschaltung ist der größte Nachteil die geringe Auflösung, da durch den Konstantstrom von ca. 1mA nur Werte im Bereich von

20mV bis 400mV auftreten(18,5mv bei –200°C; 390,3mV bei +850°C). Da die Referenzspannung für den A/D-Wandler größer als 1,4V(hier ca.1,52V) sein muss wird in

dieser Beschaltung die Wandlerbreite nur um etwa ein viertel ausgenutzt. So ist die

Auflösung von nur ca. 1°C zu erklären.

Eine Verbesserung könnte man erreichen durch:

niedrigere Referenzspannung, z.B. 390mV (bei den eingesetzten Controller leider

nicht möglich U Ref > 1,4V)

einen höheren Messstrom, z.B. 4mA hier würden sich Spannungen von ca. 74mV

bis 1,5V ergeben womit der Wandler viel besser ausgenutzt wäre, jedoch steigt bei

höheren Messstrom die Verlustleistung des Pt100-Elementes was eine Eigenerwärmung zur Folge hat. (bei 4mA Sensorstrom: Verlustleistung 16mal so groß wie

bei 1mA)

41

den Einsatz eines Messverstärkers welcher den Messbereich des Sensors(oder einen beliebigen Messbereich) auf den Eingang des AD-Wandlers abbildet.

Dimensionierung des Messverstärkers

Gewünscht wird nun ein Messbereich von –50°C bis 450°C:

Hierbei ändert sich der Widerstand des Pt100 von 80,31Ω auf 264,18Ω (Entnahme der

Werte aus Tabelle oder Berechnung). Bei einem Sensorstrom von 1mA wäre dies eine

Spannung, die zwischen 80,31mV und 264,18mV liegt. Wird nun ein Wandler verwendet, welcher eine Eingangsspannung von 0 – 2,5V in einen digitalen Wert umsetzt,

muss der Bereich von 80,31mV bis 264,18mV auf den Bereich des AD-Wandlers(0 bis

2.5V) abgebildet werden. Eine Möglichkeit ist, erst das Signal um 80.31mV zur Nulllinie

verschieben, und anschließend das Signal so zu verstärken, das es im gewünschten

Bereich liegt.

Signal

AD-Wandler

u

Signal

u

AD-Wandler

u

2,5 V

Signal

u

AD-Wandler

u

u

2,5 V

2,5 V

264,18 mV

80,31 mV

0V

264,18 – 80,31 mV

183,87 mV

0V

0V

Verstärkung

Bild: Dimensionierung des Messverstärkers

Bei Verwendung von Operationsverstärker erreicht man die Verschiebung des Signals

einfach, durch Verwendung eines Subtrahierers, welchen einmal das Messignal und

zum anderen eine Gleichspannung(hier 80,32mV) zugeführt wird.

Zur Verstärkung des Signals auf die 0...2,5V des Wandlers wird ein nichtinvertierender

Verstärker eingesetzt, der folgende Verstärkung besitzen muss:

Ue = 264,18mV – 80,31mV = 183,87mV

Ua = 2,5V

V =

Ua

2,5V

=

= 13,6

Ue 183,87mV

Aufbau der Schaltung

42

Impedanzwandler

Stromquelle

+5V

2,5V (Vref)

nicht

invertierender

Verstärker

+5V

-5V

AD

o 80,31mV

U1

Subtrahierer

Pt100

Impedanzwandler

Gnd

Sensor

Spannungsteiler

(Spindelpotentiometer)

Bild: Realisierung der Schaltung

Voraussetzung:

- Einsatz rauscharmer Verstärker

- Verstäker mit geringem Offset, sog. Messverstärker (Instrumentation Amplifier)

Die vorhanden Stromquelle wurde ein bischen verbessert, indem ein LM317T Spannungsregler, als Stromregler beschalten, eingesetzt wurde. Der LM317T Regelt zwischen Out und Adj eine Spannung von 1,25V ein, bei einem R1 von 1,25kΩ (realisiert

mit einem 1,1k Ω und ein 220 Ω Spindelpoti) stellt sich so ein Strom von genau 1mA

ein. Der Widerstand R2(68Ω) dient lediglich zur Belastung des Reglers, da dieser erst

ab ca. 10mA ordentlich regelt.

Das Signal vom PT100 wird über einem Impedanzwandler zur Entkoppelung einem

Subtrahierer zugeführt. Die Spannung U1 = 80,31V wird über einem Spannungsteiler

aus R3 und R4 erzeugt welcher zur höheren Genauigkeit von der Referenzspannung

des Controllers versorgt wird.

Vref R3 + R 4

=

U1

R4

Bei Vref = 2,5V und U1 = 80,31mV wurde R3 = 3,3kΩ und R4 = 220Ω Spindelpoti gewählt.

Über einen Impedanzwandler wird auch U1 dem Subtrahierer(R5, R6, R7, R8 = 133kΩ)

zugeführt. Danach wird das Signal dem nichtinvertierenden Verstärker zugeführt, dessen Verstärkung über R9 und R10 eingestellt wird

43

V = 1+

R10

R9

Für eine Verstärkung V = 13,6 wurde R10 = 12,6kΩ(aus 12kΩ und 620Ω) und R9 = 1kΩ

gewählt. R11 beträgt 1kΩ und dient zum Schutz des AD-Wandler Eingang.

Mit dem eingesetzten Messverstärker wird so für den gewählten Messbereich die gesamte Wandlerwortbreite ausgenutzt. Es ergibt sich so eine Auflösung a von:

Messbereich : 500°C (-50°C ...450°C)

Wandlerwortbreite: 12bit

a=

Messbereich

500°

= 12 = 0.12°C

Wandlerwortbreite

2

Man erkennt, dass durch den Einsatz eines einfachen Messverstärkers die Auflösung

stark verbessert werden kann, allerdings ist der Messbereich etwas eingeschränkt worden. Natürlich kann auch ein noch viel schmalerer Messbereich gewählt werden und

man erhält so eine noch höhere Auflösung.

9.14. Beispiel: Drehzahlerfassung über die Messung der EMK

In dieser Diplomarbeit wird eine Drehzahlregelung des Sonnenschutzbehanges ohne

Zuhilfenahme eines Drehzahlsensors realisiert. Anstelle eines Sensors wird in künstlich

erzeugten Ansteuerpausen die Gegen-EMK gemessen, aus der sich die

Drehzahlinformation ableiten lässt. Wenn die H-Brücken-Schaltung von einem 24V

Netzteil gespeist wird, liegen effektiv nur ca. 22V an den Anschlussklemmen des 24V

DC-Motor an. Das resultiert unter anderem aus dem Spannungsabfall an den

Gleichrichterdioden der H-Brücken-Platine und der Ankerwicklung des Motors. Um die

Generatorspannnung zu ermitteln, die eine zur Drehzahl proportionale Spannung ist,

muss diese A/D-gewandelt werden. Da der MSP430F449 eine eingebaute

Referenzspannungsquelle von 2,5V besitzt, wird ein Spannungsteiler benötigt, der die

maximale Generatorspannung auf diesen Wert runterteilt. Damit gegebenenfalls auch

eine etwas höhere Netzteilspannung als 24V angelegt werden kann, um z.B. die

Messpausen auszugleichen, werden folgende Widerstandswerte ausgewählt: R1 =

1,1kOhm, R2 = 10kOhm.

Ui

R + R2 11,1kΩ

= 10,09

= 1

=

1,1kΩ

U ADC

R1

⇒ UiMAX =

R1 + R2

11,1kΩ

U ADC =

* 2,5V = 25,23V

R1

1,1kΩ

(Gl. 8.1)

(Gl. 8.2)

44

Aus Gl. 8.1 folgt dass das Spannungsverhältnis Ui / UADC = 10,09 beträgt und laut Gl.

8.2 ist die maximal messbare Generatorspannung 25,23V. Das reicht aus, um das

Netzteil mit 27V betreiben zu können und so durch die Spannungserhöhung den

Spannungsverlust durch die Messpausen auszugleichen.

Abb. 9-1: Schematischer Aufbau des Spannungsteilers

Theorie Drehzahlerfassung über die Messung der EMK - Theorie

Eine Möglichkeit der sensorlosen Drehzahlerfassung ist es, den Motor als Tachogenerator zu verwenden. Das ist möglich, weil in den Ankerwicklungen eine

Spannung Ui (EMK) induziert wird, die der Drehzahl proportional ist:

Ui = c *Φ *Ω

(Gl. 6.1)

Im stationären Zustand ergibt sich an den Klemmen des Motors:

U A = U i + I A * RA

(Gl. 6.2)

Daraus folgt:

U i = U A − I A * RA

(Gl. 6.3)

U A : Ankerspannung

Ui : induzierte Spannung

IA :

Ankerstrom

RA : Ankerwiderstand

c:

Motorkonstante

Φ:

Ω:

45

magnetischer Fluss

Winkelgeschwindigkeit

Damit die induzierte Spannung wirklich mit der Drehzahl proportional ist, darf in den

Ankerwindungen beim Messen kein Strom mehr fließen.

Um dieses zu gewährleisten, gibt es zwei Methoden:

1. Messen der induzierten Spannung in den Puls-Pausen

2. Einlegen von Messpausen

Die erste Methode kann eingesetzt werden, wenn der Motor mit PWM betrieben wird

und gleichzeitig die PWM-Frequenz niedrig ist. In diesem Fall sind die Puls-Pausen so

lang, dass in dieser Zeit die Ankerinduktivität entladen wird und der Strom null ist.

Danach wird in der verbliebenen Zeit die Spannung gemessen (Abb. 6-1).

Vorteil: Es müssen keine Messpausen eingelegt werden, so dass immer die volle

Klemmenspannung am Motor anliegt.

Nachteil: Bei einem hohen Duty Cycle sind die Puls-Pausen zu kurz oder bei 100%

Duty Cycle nicht vorhanden.

Bei der zweiten Methode werden Messpausen eingelegt, bei denen der Motor im Lauf

kurzzeitig abgeschaltet wird. Die Messpausen dürfen nicht zu lang sein, damit die

Drehzahl des Motors nicht merklich abnimmt. Sie müssen aber lang genug sein, damit

der Strom in den Ankerwindungen beim Messen null ist.

Abb. 9-1: Messung der EMK zwischen den Puls-Pausen

Vorteil: Es kann auch bei 100% Duty Cycle gemessen werden.

Nachteil: Durch das Einlegen von Messpausen liegt nicht mehr die volle Klemmenspannnug am Motor an.

46

UPWM

PWM

t

UA(t)

IA*RA+Ui

EMK

Ui

tmess

t

Abb. 9-2: Messung der EMK in der Messpause

In dieser Diplomarbeit wird im weiteren Verlauf die zweite Methode aus folgenden

Gründen näher betrachtet:

hohe PWM-Frequenz wählbar

Drehzahl bei 100% Duty Cycle bestimmbar

Messen der EMK an realen DC 24V-Motoren

Um festzustellen, ob der Zusammenhang zwischen der EMK und der Drehzahl nicht nur

in der Theorie, sondern auch in der Praxis besteht, wurde die Generatorspannung nach

dem Abschalten des Motors bei 100% Duty Cycle mit dem Oszilloskop aufgezeichnet.

Dieses wird mit dem Maxon- und dem Dunker-Motor durchgeführt, da nur diese im nicht

eingebauten Zustand vorliegen. Die Abb. 6-3 zeigt, dass der Maxon-Motor innerhalb

von 680ms und der Dunker-Motor innerhalb von 466ms zum Stehen kommt und die

Generatorspannung annähernd linear bleibt. Beide haben einen leichten Knick in der

Kennlinie des unteren Drehzahlbereichs, der scheinbar vom Getriebe herrührt. Im

oberen Drehzahlbereich des Maxon-Motors ist eine geringe Welligkeit zu sehen, die

aber bei abnehmender Drehzahl immer kleiner wird. Anders ist dies beim Dunker-Motor

in Abb. 6-4. Dieser Motor besitzt im Vergleich zum Maxon-Motor eine erheblich größere

Welligkeit, die bei hohen Drehzahlen und der späteren A/D-Wandlung zu

berücksichtigen ist.

47

Abb. 9-3: Generatorspannung des Maxon-Motors mit Getriebe

Abb. 9-4: Generatorspannung des Dunker-Motors mit Getriebe

9.15. Übung - Fragen zur A/D-Wandlung

1. In a binary number:

a. the digit position value increases by 1 times over the digit value to the right.

b. the digit position value increases by 2 times over the digit value to the right.

48

c. the digit position value increases by 4 times over the digit value to the right.

d. the digit position value increases by 8 times over the digit value to the right.

2. A decimal equivalent of a binary number:

a. is the addition of all the bit position values for all the bits equal to 1.

b. is the multiplication of all the bit position values for all the bits equal to 1.

c. is the subtraction of all the bit position values for all the bits equal to 1.

d. is the division by 2 of the bit position value of the LSB.

3. The principle used to design a resistor-string DAC is:

a. the MSB is one-eighth the full value and the next bit position is one half of the MSB

value.

b. the MSB is one-fourth the full value and the next bit position is one half of the MSB

value.

c. the MSB is one-third the full value and the next bit position is one half of the MSB

value.

d. the MSB is one-half the full value and the next bit position is one half of the MSB

value.

4. The equivalent resistance between VREF and ground of the R/2R ladder DAC is:

a. 4R.

b. 2R.

c. R.

d. R/2

5. The digit position current in the R/2R ladder DAC is:

a. one half the current in the bit position to the left.

b. one eighth the current in the bit position to the left.

c. one fourth the current in the bit position to the left.

d. equal to the current in the bit position to the left.

6. The voltage increment from a 10-bit resistor-string DAC with 10V applied is:

a. about 10 volts.

b. about one volt.

c. about 10 millivolts.

d. about 100 millivolts.

7. A simple current-steering DAC:

a. combines both voltage and current to produce the analog output.

b. adds binary-weighted voltages to produce the analog output.

c. produces the analog voltage by sensing a resistor string.

d. adds binary-weighted constant currents to produce the analog output.

8. The counting ADC:

a. contains a DAC whose input is the output of a counter.

b. contains a comparator to compare the analog input to the output of a DAC.

49

c. latches the counter output code when the comparator inputs are equal.

d. all of the above.

e. a and b only above.

9. The SAR gets its name from a process that:

a. successively compares the input analog voltage to the output of a DAC that has a

binaryweighted input code.

b. sums a series of binary-weighted currents.

c. sums current from a ladder resistor network.

d. sums voltages from a resistor string.

10. The maximum conversion time for a SAR DAC is:

a. 4n clock cycles.

b. n clock cycles.

c. 8n clock cycles.

d. n/2 clock cycles.

11. In Flash ADCs:

a. the high speed is made possible by simultaneous comparisons.

b. there are as many comparators as there are bits.

c. there are as many reference voltages as there are bits.

d. the basic string for comparisons is a capacitor charge-redistribution network.

12. A sample-and-hold circuit:

a. has a momentary switch that connects the input voltage to a capacitor long enough

for the

capacitor to charge.

b. has a resistor in series with a capacitor in series with a switch.

c. has a capacitor that is charged to hold the value of the input voltage.

d. a only above.

e. a and c above.

f. none of the above.

13. Filtering is important to DAC operation:

a. because it adds noise to the output signal.

b. because it returns the DAC output to a smooth continuous signal.

c. because it selects one frequency to pass on from the output.

d. because it acts as a very high-frequency high-pass filter.

Answers: 1.b, 2.a, 3.d, 4.c, 5.a, 6.c, 7.d, 8.d, 9.a, 10.b, 11.a, 12.e, 13.b.

50