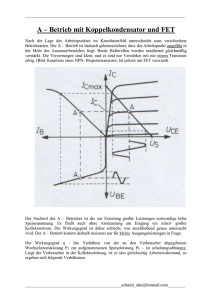

und Ausgangskennlinienfeld eines Feldeffekttransistors

Werbung

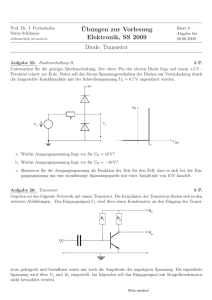

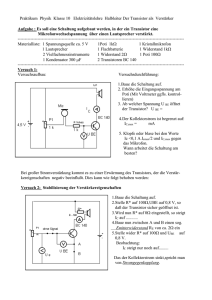

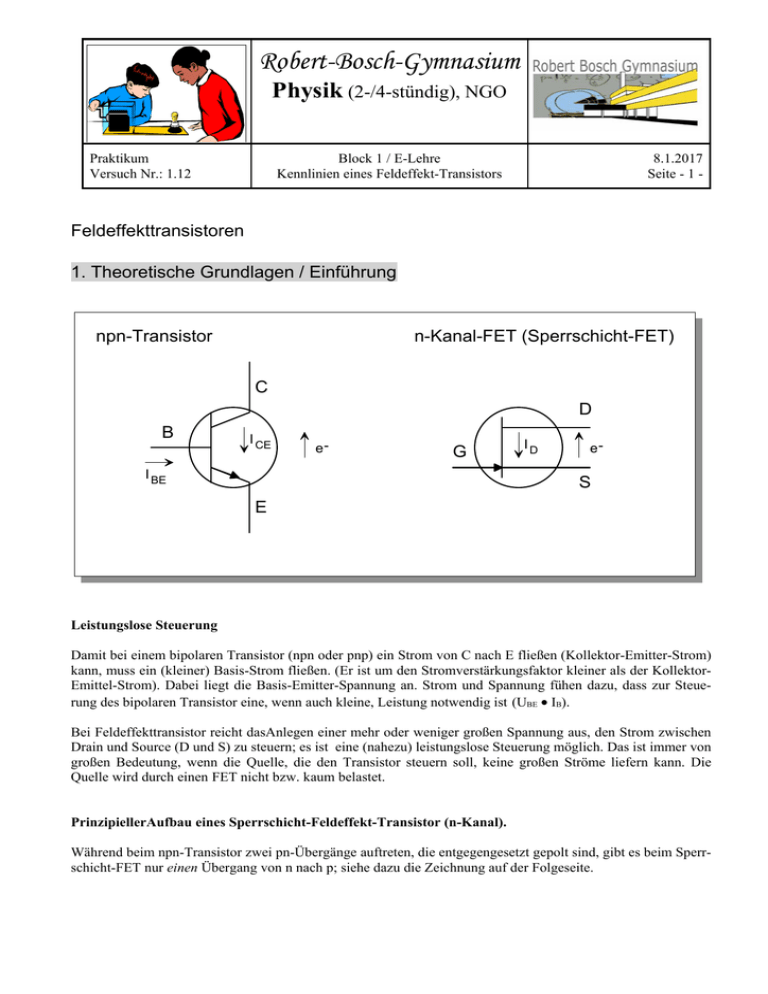

Robert-Bosch-Gymnasium Physik (2-/4-stündig), NGO Praktikum Versuch Nr.: 1.12 Block 1 / E-Lehre Kennlinien eines Feldeffekt-Transistors 8.1.2017 Seite - 1 - Feldeffekttransistoren 1. Theoretische Grundlagen / Einführung npn-Transistor n-Kanal-FET (Sperrschicht-FET) C D B I CE e- G I BE ID e- S E Leistungslose Steuerung Damit bei einem bipolaren Transistor (npn oder pnp) ein Strom von C nach E fließen (Kollektor-Emitter-Strom) kann, muss ein (kleiner) Basis-Strom fließen. (Er ist um den Stromverstärkungsfaktor kleiner als der KollektorEmittel-Strom). Dabei liegt die Basis-Emitter-Spannung an. Strom und Spannung fühen dazu, dass zur Steuerung des bipolaren Transistor eine, wenn auch kleine, Leistung notwendig ist (UBE IB). Bei Feldeffekttransistor reicht dasAnlegen einer mehr oder weniger großen Spannung aus, den Strom zwischen Drain und Source (D und S) zu steuern; es ist eine (nahezu) leistungslose Steuerung möglich. Das ist immer von großen Bedeutung, wenn die Quelle, die den Transistor steuern soll, keine großen Ströme liefern kann. Die Quelle wird durch einen FET nicht bzw. kaum belastet. PrinzipiellerAufbau eines Sperrschicht-Feldeffekt-Transistor (n-Kanal). Während beim npn-Transistor zwei pn-Übergänge auftreten, die entgegengesetzt gepolt sind, gibt es beim Sperrschicht-FET nur einen Übergang von n nach p; siehe dazu die Zeichnung auf der Folgeseite. Robert-Bosch-Gymnasium Physik (2-/4-stündig), NGO Praktikum Versuch Nr.: 1.12 Block 1 / E-Lehre Kennlinien eines Feldeffekt-Transistors Zunächst denken wir uns G mit S verbunden; dann sind beide Anschlüsse auf demselben Potential; die Sperrschicht zwischen p und n hat deshalb die Ausdehnung des spannungslosen Zustandes (ist also sehr schmal). Legt man nun eine Spannung zwischen D und S an, so fließt in der n-Schicht ein Strom, verursacht durch die freien Elekronen im n-dotierten Halbeiter. Ist D positiv ind S negativ gepolt, fließt der technische Strom von D nach S. Während bei einem bipolaren Transistor außer freien Elektronen auch Elektronenlöcher am Stromfluss beteiligt sind, nehmen hier nur Ladungsträger einer Sorte teil: daher spricht man auch von einem unipolaren Transistor. Der n-dotierte Bereich heißt dabei Kanal. Im vorliegenden Fall haben wir es mit einem n-KanalFET zu tun (man spricht auch von einem Unijunctions-Transistor). 8.1.2017 Seite - 2 - D Drain (Abfluss) + n G Gate (Tor) p p S - Source (Quelle) Bei einem pe-Kanal-Typ ist der Kanal p-dotiert und Elektronenlöcher stellen quasi die Ladungsträger dar (eigentlich: die Elektronen, die in entgegengesetzte Richtung die Löcher durchwandern). Wenn zwischen S und D ein Strom fließt, wirkt der Kanal wie ein ohm’scher Widerstand; längs des Kanals tritt demnach ein Spannungsgefälle (zwischen D und S) auf. Die Stromstärke des so genannten Drainstromes IDS wird dabei bestimmt von: der angelegten Spannung (IDS ist proportional zu UDS) dem Widerstand des n-Kanals zwischen D und S (und dieser hängt außer von der Länge und der Querschnittsfläche des Kanals hauptsächlich von dessen Dotierungsgrad ab). Das bedeutet auch, dass der Widerstand des Kanals durch dessen Querschnitt veränderbar ist; und genau dies geschieht bei der Steuerung des Transistors. Robert-Bosch-Gymnasium Physik (2-/4-stündig), NGO Praktikum Versuch Nr.: 1.12 Block 1 / E-Lehre Kennlinien eines Feldeffekt-Transistors 8.1.2017 Seite - 3 - Längs des n-Kanals gibt es durch die angelegte Spannung UDS ein Potentialgefälle; das Potential steigt von 0 V am Minospol auf 12 V am Pluspol. Liegt G auf gleichem Potential wie S, so sind die Übergänge zwischen p und auf beiden Seiten in Sperr-Richtung gepolt (p ist auf dem Potential 0 V, n auf einem Potential zwischen 0 V und 12 V). Die in Sperr-Richtung angelegte Spannung wächst also entlang des Kanals von S nach D; die Sperrschicht ist demnach unten relativ schmal und wird nach oben hin immer breiter. D 12V 12V n G pp p 9V 6V Die Verbreiterung der Sperrschicht zu D hin verringert umgekehrt den Querschnitt des n-Kanals und erhöht damit seinen Widerstand. Die Stromstärke IDS sinkt dadurch. Elektronen können nur im n-Kanal fließen. 3V 0V S Im p-dotierten Bereich der Sperrschicht liegen negative Ionen vor (z. B. Gallium-Anionen), im ndotierten Bereich dagegen positive Ionen (z. B. Arsen-Kationen). Steuerung des FET Legt man nun zusätzlich zur Spannung UDS eine Spannung UGS zwischen Gate und Source an, so dass das Gate negativ gegenüber Source ist, werden die Sperrschichten zwischen den p-Schichten und dem n-Kanal noch breiter, der Kanal dafür umso schmaler, der Widerstand größer; in der Folge sinkt IDS noch mehr: eine leichte Änderung der Gate-Spannung UGS änderden Gate-Strom IDS bereits sehr stark. Dabei muss kein Gate-Strom zwischen Source und Gate fließen. Es genügt das Anlegen der Spannung; wenn zwar eine Spannung anliegt, jedoch kein Strom fließt, wird auch keine elektrische Leistung umgesetzt. Die Steuerung des FET geschieht als leistungslos. Das ist wichtig, wenn die steuernde Quelle auch keinen großen Strom liefern kann (hochohmige Quellen). Hinweis: bei genügend großer Spannung UDS berühren sich irgendwann beide Sperrschichten wegen des hohen Potentials („Abschnürung“ / „Pinch-Effekt“). Dann hat eine Erhöhung der Drain-Source-Spannung keine Erhöhung der Stromstärke IDS mehr zur Folge; der Transistor geht in den Sättigungsbereich. Der Grenzwert ist gegeben durch die Abschnür- oder Pinchsspannung UDS(Pinch) Die Abschnürspannung ist umso niedriger, je breiter die Sperrschichten schon waren, je höher also die (negative) Gate-Spannung ist. Stoßen die Sperrschichten auf der ganzen Länge imn-Kanal zusammen, sperrt der Transistor komplett; es fließt gar kein Drain-Strom mehr. Grundsätzlicher Aufbau der Stromversorgung für einen bipolaren Transistor und einen Feldeffekttransistor: Robert-Bosch-Gymnasium Physik (2-/4-stündig), NGO Praktikum Versuch Nr.: 1.12 Block 1 / E-Lehre Kennlinien eines Feldeffekt-Transistors 8.1.2017 Seite - 4 - n-Kanal-FET (Sperrschicht-FET) npn-Transistor 15 V 15 V C D B G S Steuerspannung E Steuerspannung 0V 0V 2. Versuchsaufbau, Durchführung der Messung / Sicherheitshinweise / Messaufgaben 1. Ausgangskennlinienfeld eines n-Kanal-Sperrschicht-Feldeffekttransistors (n-Kanal-FET) Wir untersuchen einen n-Kanal-Sperrschicht-FET und erstellen für ihn ein Ausgangskennlinienfeld. Dabei wird der Drain-Strom als Funktion der Drain-Source-Spannung aufgetragen mit der Gate-Spannung als weiterem Parameter. D. h. für jede Gate-Spannung wird eine ID-UDS-Kennlinie aufgenommen; insgesamt entsteht ein Kennlinienfeld (eine Kennlinienschar). Aufbau / Schaltung /Spannungsversorgung Dazu wird zunächst die auf der Folgeseite dargestellte Schaltung aufgebaut. Zur Spannungsversorgung benutzt man am besten eine Spannungsquelle mit zwei symmetrischen Spannungen z. B. 15 V. Alternativ benötigt man zwei erdfreie Spannungsquellen, bei denen man den Plus-Pol der einen mit dem Minuspol der anderen verbindet. Robert-Bosch-Gymnasium Physik (2-/4-stündig), NGO Praktikum Versuch Nr.: 1.12 Block 1 / E-Lehre Kennlinien eines Feldeffekt-Transistors 8.1.2017 Seite - 5 - BF245 15 V D 1 M G S 15 V 200 200 Messaufgabe Es werden Gate-Spannungen (von 0 V aus) im Halb-Volt-Abstand eingestellt. Bei jeder Gatespannung UGS nimmt man punktweise eine IDS-UDS-Kennlinie auf. Ist die Gate-Spannung einmal mit Hilfe der Potentiometerschaltung eingestellt, darf sie während des Versuchs nicht mehr verändert werden. Am besten während der Messung ab und zu den Wert kontrollieren! 2. Eingangskennlinienfeld eines n-Kanal-Sperrschicht-Feldeffekttransistors (n-Kanal-FET) Wir untersuchen nun die Eingangskennlinie des FET. Dazu bauen wir wieder die oben benutzte Schaltung auf. Jetzt wird aber eine konstante Drain-Source-Spannung eingestellt (und konstant belassen), z. B. UDS = 12 V. Bei dieser Spannung variiert man nun die Gate-Soucespannung UGS zwischen 0 V und -10,0 V und liest die Stromstärkewerte des Drain-Source-Stromes ab. Wer noch Zeit hat, kann weitere Eingangskennlinien bei anderen Drain-Source-Spannungen (z. B. 14 V, 10 V, 8 V,...) aufnehmen. Sicherheitshinweise Es wird nur mit den ausgegebenen Netzgeräten gearbeitet. Die Spannungen liegn im nicht-berührungsgefährlichen Bereich. Bei Fehlern / Defekten Netzgerät abschalten bzw. Not-Aus-Taster im Saal betätigen. Es wird daran erinnert, dass Essen und Trinken im Labor, insbesondere, wenn elektrische Aufbauten benutzt werden, nicht erlaubt ist. (Gefahr des Verschüttens.) Robert-Bosch-Gymnasium Physik (2-/4-stündig), NGO Praktikum Versuch Nr.: 1.12 Block 1 / E-Lehre Kennlinien eines Feldeffekt-Transistors 8.1.2017 Seite - 6 - 3. Auswertung In der Auswertung befindet sich das Originalmessprotokoll. Sodann sind die oben genannten Messaufgaben entsprechend auszuwerten (Tabellen, Diagramme). Alle Ergebnisse sind verbal zu beschreiben, d. h. außer den Tabellen und Diagrammen muss zu den Messaufgaben noch mindestens ein Ergebnissatz formuliert werden. Es sind mindestens zwei Diagramm zu erzeugen: die Eingangskennlinie des FET und dasAusgangskennlinienfeld. Wer mehrere Eingangskennlinien gemessen hat, kann auch für die Eingangskennlinien ein Kennlinienfeld als Diagramm erstellen. 5. Fehlerbetrachtung Zu allen Messungen ist eine Größtfehlerbetrachtung durchzuführen.