BR-ETH - kws

Werbung

BR-ETH V1

Hardware-Beschreibung

kws 17. Jan. 2003

1

BR-ETH

Hardware-Beschreibung BR-ETH

gültig ab Hardware-Revision 1

Stand: Januar 2003

Die BR-ETH gehört zu der Familie der

ARCNET-Bridges. Diese intelligenten

Baugruppen koppeln die verschiedensten

dezentralen Ein- bzw. Ausgabeeinheiten

direkt an das ARCNET.

So stellt die BR-ETH eine Verbindung mit

Hilfe des integrierten Ethernet –

Controllers im MC68EN302 10MBit Ethernet her.

Aufgrund eines umfangreichen

Speicherangebotes ( 8MByte DRAM,

2MByte batteriegepuffertes SRAM und

4MByte Flash ) lassen sich auch

komplexe Betriebssysteme wie OS9

installieren.

Für wichtige Systemeinstellungen gibt es

ein serielles EEPROM. In einem

512kByte großen EPROM oder FLASH

lassen sich Hardwarebezogene

Programmteile speichern.

Mittels einer Memorycard läßt sich auf

einfache Weise ein Systemupdate

durchführen.

2

Inhalt

Inhalt:

1

2

3

4

Datenblatt ..................................................................................5

1.1

Blockschaltbild ....................................................................................5

1.2

Kurzdaten ............................................................................................6

Mikrocontroller und Speicher....................................................7

2.1

CPU ......................................................................................................7

2.2

Programm- und Datenspeicher..........................................................7

2.3

Pufferbatterie für SRAM und RTC ..................................................9

2.4

EEPROM .............................................................................................9

Periphere Komponenten ..........................................................11

3.1

ARCNET - Controller ( Basisadresse 0xF0C000 ) .........................11

3.2

RTC-72421 ( Basisadresse 0xF0A000 ) ...........................................12

3.3

Memorycard (PCMCIA) ..................................................................14

3.4

Statusanzeige ( Basisadresse 0xF00000 ).........................................15

3.5

HexSchalter ( Basisadresse 0xF02001 ) ...........................................15

3.6

Platinenrevision ( Basisadresse 0xF0E000 )....................................15

Taster und Steckerbelegungen.................................................17

4.1

Taster und Schalter...........................................................................17

3

BR-ETH

4.2

Versorgungsstecker...........................................................................17

4.3

ARCNET ( RS485 ) ...........................................................................18

4.4

COM1 und COM2 (RS232)..............................................................19

4.5

Lageplan.............................................................................................19

Tabellen:

Tabelle 1: Kurzdaten .................................................................................... 6

Tabelle 2: Anschlußbelegung EEPROM...................................................... 9

Tabelle 3: Offsetadresse der ARCNET - Controllerregister....................... 12

Tabelle 4: Offsetadressen des RTC-72421................................................. 13

Tabelle 5: Belegung des Statusregisters für die Memorycard .................... 14

Tabelle 6: Belegung des ARCNET-Steckers.............................................. 18

Tabelle 7: Belegung der RS232-Stecker .................................................... 19

Abbildungen:

Abbildung 1: Blockschaltbild....................................................................... 5

Abbildung 2: Speicheraufteilung.................................................................. 8

Abbildung 3: Basisadressen im IO-Berich ................................................. 11

Abbildung 4: Belegung der Statusanzeigen ............................................... 15

Abbildung 5: Belegung des 3poligen Versorgungssteckers ....................... 17

Abbildung 6: Belegung des 4poligen Versorgungssteckers ....................... 18

Abbildung 7: Lageplan der Taster, LED’s und Stekcer. ............................ 19

Die Informationen in diesem Text wurden von uns sorgfältig überprüft und

sollten vollständig und korrekt sein. Dennoch können wir für fehlende oder

unrichtige Hinweise und sich daraus unter Umständen ergebende Schäden in

keinem Fall die Haftung übernehmen. Liefermöglichkeiten, Änderungen und

Irrtum vorbehalten.

KWS Computersysteme GmbH / Carl Zeiss-Straße 1 / D-76275 Ettlingen /

Telefon: +49(0)7243/215-0 / Fax: +49(0)7243/215-100 /

Internet: http://www.kws-computer.de

4

1.Datenblatt

1 Datenblatt

1.1 Blockschaltbild

Service

DRAM

SRAM

8MByte

2MByte

FLASH

EPROM

4MByte

512kByte

CPU

MC68EN302

SCC1,2,3 Ethernet

LXT905

ETHERNET

4

RS232

TTL

4

RS232

TTL

Statusanzeige

HEX-Schalter

EEPROM

93C46

COM20020

Memorycard

( PCMCIA )

COM2

HYC9088

KOAX

TTL

Uhr

RTC-72421

COM1

RS485

TTL

BNC-ARC

ARCNET

Abbildung 1: Blockschaltbild

5

BR-ETH

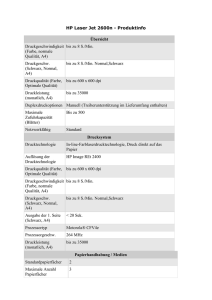

1.2 Kurzdaten

Prozessor:

DRAM:

SRAM:

FLASH:

EPROM/FLASH:

EEPROM

ARCNET:

Ethernet

Serielle Schnittstellen

Versorgungsspannung:

Leistungsaufnahme

Pufferbatterie

Tabelle 1: Kurzdaten

6

MC68EN302 20MHz

8MByte ( 16Bit Datenbreite )

2MByte ( 16Bit Datenbreite, mit Pufferbatterie )

4MByte ( 16Bit Datenbreite )

1MByte / 512kByte ( 8Bit, Boot – ROM )

Parameterspeicher ST93C46 (seriell, 64x16)

COM20020–Controller ( KOAX oder RS485 )

IEEE 802.3 kompatibles 10BASE – T

2 x RS232 ( 4 Draht )

+24V +10V

Typ. 3,5W

Type CR2032 min. 3V

2. Mikrocontroller und Speicher

2 Mikrocontroller und Speicher

2.1 CPU

Als Prozessor kommt der Controller MC68EN302 mit 20MHz Taktfrequenz

zum Einsatz. Folgende integrierten Funktionsgruppen des Controllers werden

bei der BR-ETH verwendet:

-

-

Ein 802.3 Ethernet kompatibler Controller bildet die Verbindung zum

10MBit Ethernet. Der Transceiver LXT905 wandelt die vom Prozessor

angebotene MAC - Schnittstelle in eine IEEE802.3 kompatible 10BASE-T

Ethernet – Schnittstelle. Die drei Leuchtdioden mit den Beschriftungen

RX, TX und LINK zeigen die Aktivitäten auf dem Ethernet an.

Der DRAM - Controller verwaltet die Speicherzugriffe und die Refreshzyklen des Arbeitspeichers. Mittels der Chip - Select - Logik werden die

Speicherbereiche der übrigen externen Komponenten verwaltet.

Von den vorhandenen SCC-Controllern werden die SCC1 und SCC3 als 4Draht RS232 - Schnittstellen verwendet. Deren TTL - Pegel werden

mittels Transceiver auf RS232 - kompatible Signalpegel gewandelt und auf

die Stecker CON1 bzw. CON2 geführt.

2.2 Programm- und Datenspeicher

Der 16MByte Adreßraum des MC68EN302 wird dynamisch vom DRAM Controller und der CS - Signalsteuerung verwaltet.

-

Beim DRAM handelt es sich um vier Bausteine vom Type 4MBit x 4, Fast

Page Mode. Dieser Speicher erscheint für den Prozessor als 16Bit-Device

und wird mit Hilfe des DRAM - Controllers verwaltet.

-

Der Flash - Speicher besteht aus zwei Bausteinen mit jeweils 2MByte

( 2MBit x 8 ) und ist an das /CS2 – Signal des Prozessors als 16Bit –

Device angeschlossen.

-

Das SRAM besteht aus zwei Speicherbänken mit je zwei 512kByte

Bausteinen ( 512kBite x 8 ). Angesteuert wird dieser Speicher als 16Bit –

Device mit dem /CS1 – Signal des Prozessors.

7

BR-ETH

-

Als Boot – ROM kann ein EPROM ( max. 1MByte, Lötbrücken L11 und

L12 verbunden zwischen 1-2 ) oder ein Flash - ROM ( max. 512kByte,

Lötbrücken L11 und L12 verbunden zwischen 1-2 ) dienen. Das FlashROM läßt sich on - Board programmieren. Der Prozessor spricht diesen

Speicher mit dem /CS0 – Signal als 8Bit – Device an.

-

Im IO-Bereich lassen sich diverse periphere Komponenten ansprechen. Er

benötigt einen Adreßraum von 64kByte. Der IO – Adreßdecoder wird mit

dem /CS3 – Signal vom Prozessor angesteuert. Ein externes Steuerwerk

liefert für den gesamten IO - Bereich ein /DACK zurück. Der Prozessor

betrachtet den gesamten IO – Bereich als 16Bit – Device. Weitere

Informationen zu den IO – Komponenten befinden sich im Kapitel

‘Periphere Komponenten‘.

Das Boot - ROM stellt folgende Speicheraufteilung ein:

CPU-Register 0xF4'0000 ... 0xFF'FFFF

frei

0xF1'0000 ... 0xF3'FFFF

IO ( 64kByte) 0xF0'0000 ... 0xF0'FFFF

0xEF'FFFF

Boot ROM

( 1MByte )

0xE0'0000

0xDF'FFFF

0x7F'FFFF

SRAM

( 2MByte )

DRAM

( 8MByte )

0xC0'0000

0xBF'FFFF

Flash

( 4MByte )

0x00'0000

0x80'0000

Abbildung 2: Speicheraufteilung

8

2. Mikrocontroller und Speicher

2.3 Pufferbatterie für SRAM und RTC

Der Inhalt der SRAM - Bausteine und die Funktion der Uhr (RTC) bleibt durch

eine Pufferbatterie auch im ausgeschalteten Zustand erhalten. Die Sicherung

der SRAM - Daten sowie die fehlerfreie Funktion der Uhr wird ab einer

Batteriespannung von min. 2,5V garantiert. Dabei wird die Batterie mit

maximal. 1,5µA belastet. Ein Statusbit im Statusregister für die Memorycard

( Adresse: 0xF02000 ) zeigt den Ladezustand der Pufferbatterie an. Ist das

Bit 7 auf 1 so hat die Batterie noch mindestens 2,5V.

Ferner befindet sich auf der Platine ein großer Pufferkondensator (GOLD-Cap

mit 100mF ). Dieser wird unabhängig von der Pufferbatterie nach einer

Betriebszeit von ca. 10Minuten auf seine volle Spannung (4V) aufgeladen.

Solange die Spannung des Kondensators über der Batteriespannung liegt,

übernimmt der Kondensator die Pufferung und die Batterie bleibt unbelastet.

Ein voller Pufferkondensator unterschreitet erst nach ca. 2 Stunden eine

Spannung von 3,6V. Ohne Pufferbatterie sinkt diese Spannung weiter ab und

unterschreitet erst nach ca. 20 Stunden eine Spannung von 2V ( gemessen

direkt am SRAM ).

Der Batteriehalter kann eine Knopfzelle Type CR2032 (min. 3V) aufnehmen.

Der Pufferkondensator erlaubt das Wechseln der Batterie in jedem Betriebszustand. Auch durch versehentliches Kurzschließen der Batteriekontakte wird

der Datenerhalt nicht beeinträchtigt.

2.4 EEPROM

Ein serielles EEPROM vom Type 93C46 ist für das Speichern diverser

Systemeinstellungen vorgesehen. Es ist in der 16Bit – Organisation konfiguriert und an die folgenden SCC2-Pins angeschlossen:

SCC-Pins

CTS2

CD2

RCLK2

TCLK2

EEPROM Pins

CS

SCLK

DO

DI

Tabelle 2: Anschlußbelegung EEPROM

9

3.Pheriepere Komponenten

3 Periphere Komponenten

Der 64kByte große IO-Berich wird mit einem externen Adreßdecoder in

Blöcke mit je 8 kByte eingeteilt. Das Bild zeigt, welchen Blöcken die jeweiligen IO - Komponenten zugeteilt sind. Die IO – Komponenten werden in den

folgenden Kapiteln genauer beschrieben.

0xF0'FFFF

0xF0'E000

0xF0'DFFF

ARCNET-Controller

0xF0'C000

0xF0'BFFF

Uhr ( RTC )

0xF0'A000

0xF0'9FFF

Memorycard

0xF0'8000

0xF0'7FFF

frei

0xF0'6000

Adressregister

0xF0'5FFF

der Memorycard 0xF0'4000

Hexschalter und

0xF0'3FFF

Memorycardstatus 0xF0'2000

0xF0'1FFF

7-Segementanzeige

0xF0'0000

Platinenversion

Abbildung 3: Basisadressen im IO-Berich

3.1 ARCNET - Controller ( Basisadresse 0xF0C000 )

Als ARCNET - Controller kommt ein COM20020 der Firma SMSC zum

Einsatz. Er besitzt 8 Datenleitungen, die mit D0 bis D7 des Prozessors

verbunden sind. Da der IO - Bereich grundsätzlich als 16Bit – Device

angesprochen werden, ergeben sich folgende Adressen für die 8 IO - Register

des COM20020:

11

BR-ETH

Offsetadresse

Read

Write

:

+0x01

Status

Interrupt Mask

+0x03

Diag. Status

Command

+0x05

Adress Pointer High

Adress Pointer High

+0x07

Adress Pointer Low

Adress Pointer Low

+0x09

Data

Data

+0x0B

(reserved)

(reserved)

+0x0D

Configuration

Configuration

+0x0F

TentID/NodeID/Setup TentID/NodeID/Setup

Tabelle 3: Offsetadresse der ARCNET - Controllerregister

Als physikalisches Anschlussmedium bietet die BR-ETH zwei Alternativen an.

So wird neben der optisch entkoppelten RS485 Schnittstelle auch noch eine

Anschlussmöglichkeit an ein RG59 - System angeboten.

-

Für die RG59 Verbindung ist der Hybrid HY9088 zu bestücken. Die

Lötbrücken L18, L20 und L23 bleiben geöffnet. So kann das ARCNET an

den BNC-Stecker mit der Bezeichnung BNC-ARC angeschlossen werden.

-

Für die RS485 Verbindung bleibt der Hybrid HY9088 unbestückt. Die

Lötbrücken L18, L20 und L23 werden geschlossen. So kann das ARCNET

an den 9 poligen DSUB - Stecker mit der Bezeichnung ARCNET

angeschlossen werden.

Eine Leuchtdiode mit der Beschriftung BUS AKTIVE zeigt Aktivitäten auf

dem ARCNET an.

3.2 RTC-72421 ( Basisadresse 0xF0A000 )

Als Uhr kommt der RTC72421 von der Firma EPSON zum Einsatz. Er besitzt

4 Datenleitungen, die mit D8 bis D11 des Prozessors verbunden sind. Da der

IO - Bereich grundsätzlich als 16Bit – Device angesprochen werden ergeben

sich folgende Adressen für die 16 IO - Register der RTC72421:

12

3.Pheriepere Komponenten

Offsetadresse

:

+0x00

+0x02

+0x04

+0x06

+0x08

+0x0A

+0x0C

+0x0E

RTC-Register:

Offsetadresse:

RTC-Register:

SEC1

SEC10

MIN1

MIN10

HOUR1

HOUR10

DAY1

DAY10

+0x10

+0x12

+0x14

+0x16

+0x18

+0x1A

+0x1C

+0x1E

MON1

MON10

YEAR1

YEAR10

WEEK

REG D

REG E

REG F

Tabelle 4: Offsetadressen des RTC-72421

13

BR-ETH

3.3 Memorycard (PCMCIA)

Für das Aufspielen der Systemsoftware ist eine Memorycard als Wechselmedium vorgesehen. Das Interface zu dieser Memorycard entspricht dem

Memorymodus des PCMCIA – Standards. So sind Register- und Memoryzugriffe möglich, wogegen IO - Zugriffe nicht unterstützt werden.

Mangels Adreßraum ist das Interface für die Memorycard im IO - Bereich

angesiedelt. Dort ist der Speicher in Blöcken zu je 512Byte immer ab der

Adresse 0xF08000 anzusprechen. In einem Adreßregister ( 16Bit auf der

Adresse 0xF04000 ) wird der gewünschte Speicherblock ausgewählt. Dabei

entsprechen die Datenbits D0 bis D14 den Adreßleitungen A9 bis A23 der

Memorycard. Das Datenbit D15 steuert das REG – Signal der Memorycard

Steht REG auf Eins, so werden Registerzugriffe, andernfalls Memoryzugriffe

auf die Memorycard ausgeführt.

Die Versorgungsspannung der Memorycard läßt sich mit Pin PB8 des

Prozessors steuern. Mit Null wird die Spannung eingeschaltet.

Ein 8 Bit Statusregister auf der Adresse 0xF02000 gibt über den aktuellen

Zustand der Memorycard Auskunft. Die folgenden Signale des Interfaces sind

auf das Register geführt:

Bit

D0

D1

D2

D3

D4

D5

D6

D7

Signal

RDY

/CD1 oder /CD2

BVD0

BVD1

WP

RESET

VCC ok.

BATT_OK

Beschreibung

0: Memorycard steckt.

Batterie Ladezustand der Memorycard

Zustand des Write Protect Schalters

1: Memorycard im Resetzustand.

0: Versorgungsspannung ist ok.

1: Pufferbatteriespannung > 2,5V

Tabelle 5: Belegung des Statusregisters für die Memorycard

14

3.Pheriepere Komponenten

3.4 Statusanzeige ( Basisadresse 0xF00000 )

Das 16Bit - Register für die Ansteuerung der Statusanzeige ( zweistelligen 7Segmentanzeige ) sollte immer wortweise beschrieben werden. Dabei werden

die mit 0 beschriebenen Segmente aktiviert. Ein Lesezugriff auf dieses Register

zerstört dessen Inhalt. Die Zuordnung der Datenbits zu den Leuchtsegmenten

ist der folgende Skizze zu entnehmen:

D8

D13

D12

D14

D11

D0

D9

D10

D15

D5

D4

D6

D3

D1

D2

D7

Abbildung 4: Belegung der Statusanzeigen

3.5 HexSchalter ( Basisadresse 0xF02001 )

Für die Einstellung der ARCNET-ID Nummer wurden auf der BR-ETH zwei

HEX - Drehschalter vorgesehen. Die Stellung dieser Schalter kann als Byte auf

der Adresse 0xF02001 abgefragt werden. Dabei bestimmt der Schalter mit der

Beschriftung LOW die Datenbits D0 bis D3 und HIGH Datenbits D4 bis D7.

3.6 Platinenrevision ( Basisadresse 0xF0E000 )

Damit Programme abwärtskompatibel programmiert werden können, ist es

erforderlich, den Revisionsstand der Platine abfragen zu können. Dazu wurde

hier ein möglichst preisgünstiges und dennoch nach oben offenes Verfahren

angewendet.

Mit Hilfe zweiter 3-State-Buffer wird ein 2 Bit - Register realisiert, welche an

den Datenleitungen D0 und D1 des Prozessors angeschlossen ist. Es läßt sich

auf der Adresse 0xF0E000 auslesen. Ferner existiert eine Bushold–Schaltung.

Diese sorgt dafür, daß der letzte Zustand der Datenleitungen solange

festgehalten wird, bis dieser aktiv umgeschaltet wird.

Zum Ermitteln der Revisionsnummer sind die folgenden Schritte erforderlich:

15

BR-ETH

1.

2.

Ein Unterprogramm schreibt 0x00 auf die 0xF0E001, um auch die

inaktiven Registerbits auf 0 zu setzen.

Anschließend kann direkt die Revisionsnummer auf der Adresse

0xF0E001 eingelesen werden.

ACHTUNG: Zwischen diesen beiden Befehlen dürfen keine 16Bit-Devices

angesprochen werden. Daher muß sich das Unterprogramm im

Boot-ROM befinden und alle Interrupts abgeschaltet sein.

Die folgende C-Routine verdeutlicht nochmals die Vorgehensweise:

unsigned char getRevision ( void )

{

volatile unsigned char *Adr;

Adr

*Adr

= (unsigned char *)0xF0E001;

= 0x00;

return *Adr;

}

16

3. Taster und Steckerbelegungen

4 Taster und Steckerbelegungen

4.1 Taster und Schalter

Die folgende Taster sind auf der Platine mit der entsprechenden Beschriftung

vorhanden:

RES:

Der Taster mit Beschriftung RES löst einen Hardwarereset

am Prozessor aus. Dieser Schalter ist an der rechten oberen

Ecke der Platine unter dem Schutzblech angebracht. Nur

durch eine Bohrung im Schirmblech läßt sich der Schalter

betätigen. So ist er im Normalbetrieb vor ungewolltem

Betätigen geschützt:

Service:

Der Serviceschalter steuert den RxD2-Pin des SCC2. Wird

der Schalter betätigt, wird eine EINS an dem Pin angelegt.

Der Schalter ist auch nach der Montage des Schirmblechs

noch gut erreichbar.

Schiebeschalter: Zusätzlich sind für Testzwecke zwei Schiebeschalter auf

der Platine vorgesehen. Sie beeinflussen Eingänge RTS2

und TxD2 der SCC2. Diese Schalter sind nach der Montage

des Schirmblechs nicht mehr bedienbar.

4.2 Versorgungsstecker

Für die Versorgung der BR-ETH mit 24V + 10V sind zwei AMP –

Steckertypen bestückbar.

-

3Polig mit PE Klemme: MSTBV 2,5/3-GF-5.06

Dieser Stecker hat folgende Belegung:

PE +24V GND

MSTBV 2,5/3-GF-5.06

Abbildung 5: Belegung des 3poligen Versorgungssteckers

-

4Polig ohne PE Klemme: MCV 1,5/4-GF-3,81

17

BR-ETH

Dieser Stecker hat folgende Belegung:

+24V GND

MCV 1,5/4-GF-3,81

Abbildung 6: Belegung des 4poligen Versorgungssteckers

4.3 ARCNET ( RS485 )

Pinnr.:

1

2

3

4

5

6

7

8

9

Funktion

Schutzerde (PE)

Not connected

DATA-B (-)

Not connected

GND

+5V (max100mA)

Not connected

DATA-A (+)

Not connected

Tabelle 6: Belegung des ARCNET-Steckers

ACHTUNG:

Ein Leitungsabschluß befindet sich nicht auf der BR-ERH-Platine und muß

daher extern realisiert werden.

18

3. Taster und Steckerbelegungen

4.4 COM1 und COM2 (RS232)

Von den vorhandenen SCC-Controller werden die SCC1 ( COM1 ) und SCC3 (

COM2 ) als 4-Draht RS232 - Schnittstellen verwendet. Die TTL - Pegel

werden mittels Transceiver auf RS232 - kompatible Signalpegel gewandelt.

Die entsprechenden DSUB – Stecker sind dabei folgendermaßen belegt:

Pinnr.:

1

2

3

4

5

6

7

8

9

SCC1( COM1)

Not connected

RxD1

TxD1

Not connected

GND

Not connected)

RTS1

CTS1

Not connected

SCC3( COM2)

Not connected

RxD3

TxD3

Not connected

GND

Not connected)

RTS3

CTS3

Not connected

Tabelle 7: Belegung der RS232-Stecker

4.5 Lageplan

BUS

AKTIVE

Reset

BOOT-

ARCNET

(RS485)

PufferBatterie

ROM

READY

Status Anzeige

HALT

Memorycard

Ethernet RX

Ethernet TX

Ethernet LINK

Service

PE

COM1

COM2

Ethernet

BNC-ARC

Versorgung

HEX-Schalter

Abbildung 7: Lageplan der Taster, LED’s und Stecker.

19