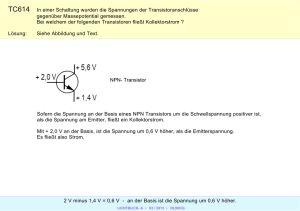

01.Aufbau und Funktionsweise von MOS

Werbung

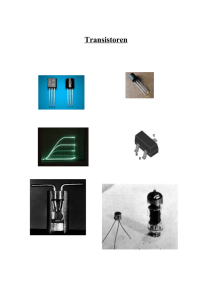

Statische CMOS Schaltungen Aufbau und Funktionsweise von MOS Transistoren gehalten von: Arne Schumann am: 06.05.2005 Proseminar Statische CMOS Schaltungen Prof. Dr. Zehendner SS05 1 Inhalte – Outline - Geschichte Bändermodell bei Halbleitern p- und n-Dotierung pn-Übergang pn-Übergang mit äußerer Spannung nMOS Aufbau MOS Struktur MOS Schwellspannung Body Effekt nMOS Schwellspannung Drainstrom Ungesättigter Stromfluss Gesättigter Stromfluss pMOS Aufbau pMOS Formeln und Unterschiede zum nMOS Schaltsymbole von MOSFETs Herstellung eines CMOS Inverters Literatur 2 03 04 05 07 08 09 11 15 16 16 18 19 20 22 22 24 26 28 Geschichte - Erste Patentanmeldungen über Feldgesteuerte Halbleiter 1928 von Julius Lilienfeld und 1934 von Oskar Heil 1940 Dotierung und pn-Übergang von Russel Ohl 1951 JFET von William Shockley Einkristallsilizium löst Germanium als Hauptstoff für Transistoren ab 1952 Das Konzept des integrierten Schaltkreises wird entwickelt 1954 Oxid-Masken Verfahren entwickelt 1960 Erster MOSFET hergestellt Anfang der 60er Jahre haben integrierte Schaltkreise einige duzend Bauelemente 1961 Erster kommerzieller Integrierter Schaltkreis 1963 CMOS Technologie entwickelt 3 Bändermodell W/eV Atom 2er Molekül Kristall - Verschiedene Energieniveaus, auf denen sich Elektronen aufhalten können - Bei einer Kristallstruktur wie in Halbleitern wechselwirken viele Atome miteinander - Die Niveaus der einzelnen Atome weichen minimal voneinander ab - Für den gesamten Kristall können die Niveaus daher als Bänder aufgefasst werden - Das im Grundzustand höchste besetzte Band heißt Valenzband - Bei Halbleitern hat das folgende Band (Leitungsband) einen nur geringen Abstand - Schon bei geringer Energiezufuhr wird der Halbleiter also leitend (springen Elektronen vom Valenz- ins Leitungsband [Generation - Rekombination]Î Eigenleitfähigkeit) 4 n-Dotierung W Si Si Si Si Si Si Si P Si Si Si Si Si Si Si L WD DN V x 0 - Da die Elektronen des Halbleiters nicht ausreichen um eine hinreichende Leitfähigkeit zu erreichen, dotiert man Fremdatome ein um diese zu erhöhen - n-Dotierung: Die 4-wertige Kristallstruktur wird mit 5-wertigen Atomen dotiert - Diese können ein Elektron ins Leitungsband abgeben und heißen deswegen Donatoren - Das Fremdatom bleibt als feste positive Ladung zurück - Die Majoritätsladungsträger eines n-dotierten Stoffes sind also die Elektronen - Die Minoritätsladungsträger entsprechen die Defektelektronen bzw. Löcher - Diese erhöhte Leitfähigkeit wird Störstellenleitfähigkeit genannt 5 p-Dotierung W Si Si Si Si Si Si Si B Si Si L AN WA Si Si Si Si V Si x - Bei der p-Dotierung wird mit 3-wertigen Fremdatomen dotiert - Ihr Energieniveau liegt nahe am Valenzband, weswegen sie Elektronen aus dem Valenzband aufnehmen können (Akzeptoren) - Sie erzeugen dadurch ein bewegliches Loch - Die Majoritätsladungsträger eines n-dotierten Stoffes sind also die Löcher - Die Minoritätsladungsträger entsprechend die Elektronen 6 pn-Übergang Diffusion p n Feldwirkung - Bei einem pn-Übergang liegen eine p- und eine n-dotierte Schicht direkt aneinander - In der n-Schicht gibt es freie Elektronen, in der p-Schicht freie Löcher - An der Grenzschicht zwischen beiden Schichten rekombinieren diese durch Diffusion der Elektronen - Es bleiben feste Raumladungen zurück, zwischen denen sich ein el. Feld aufbaut, was der Diffusion entgegenwirkt - Sind diese beiden Effekte gleich groß, stellt sich ein Gleichgewicht ein 7 pn-Übergang Diffusion p n Feldwirkung - Über eine angelegte äußere Spannung U wird der pn-Übergang gesperrt oder leitend - Liegt der Pluspol am n-Bereich, so wird die Diffusionsspannung auf UD+U erhöht - Die Feldwirkung erhöht sich, die Raumladungszonen werden zur Sperrschicht für die MajLT und der Übergang ist gesperrt - In der anderen Richtung wird die Diffusionsspannung verringert: UD-U - Die Feldstärke verringert sich, die Raumladungszonen verengen sich, der Diffusionsstrom wird begünstigt - Da der Diff.Strom aus MajLT besteht, wird der Übergang leitend 8 nMOS Aufbau Source Drain Metal Metal Plug Plug Gate [M] n+, Nd L p+ Substrat, Na Oxide [O] n+, Nd Semiconductor [S] Bulk - Der MOSFET hat vier Anschlüsse: Source, Gate, Drain, Bulk - Das Gate besteht aus zwei Teilen: PolySilizium und Metall - Die zentrale Region Gate-Oxid-Halbleiter bildet eine Kondensator-Struktur - Die Gatespannung kontrolliert den Stromfluss im Transistor - Erst ab einer gewissen Schwellspannung (threshold voltage) am Gate wird der Transistor leitend - Die Leitfähigkeit resultiert aus einem n-leitenden Kanal zwischen Drain und Source - Bei dem abgebildeten Transistor handelt es sich um einen Anreicherungs-Typ (Enhancement Mode) Î er ist selbstsperrend 9 nMOS Aufbau Wichtige Größen: - Kanallänge L - Kanallänge Aufsicht L’ (>L) - Kanalbreite W - Seitenverhältnis W/L - Akzeptor-Dotierungsdichte Na (cm-3) - Donator-Dotierungsdichte Nd (cm-3) 10 - Drain-Source Spannung VDSn - Gate-Source Spannung VGSn - Source-Bulk Spannung VSBn - Schwellspannung VTn - Drain-Source Strom IDn MOS Struktur +VG Metall Gate M Polysilizium Vox Gate Oxid Oberflächenladung QS O xox S x S p-Typ, Na - Das Gate bildet zusammen mit dem Halbleitersubstrat eine Kondensatorstruktur - Es lässt sich also eine Kapazität C berechnen: ε *A ε C= d in F Î Cox = ox in F/cm² d xox - Man sieht: Ein dünnerer Isolator erhöht die Kapazität und damit die Leitfähigkeit - εox ≈ 3.9 ε0 F/cm für Siliziumdioxid und xox ca. 0.01µm oder kleiner - Damit liegt Cox in der Gegend von 10-7 F/cm² oder mehr 11 Der Feldeffekt M O S VG Vox S x - Liegt eine positive Spannung VG am Gate an, so bildet sich ein el. Feld - Dieses Feld verursacht eine negative Ladung im Halbleiter unter dem Oxid (Feldeffekt) - Nach Kirchhoff: VG = Vox + φS - Man sieht: Eine größere Gate-Spannung erhöht das Oberflächenpotential φS 12 MOS Struktur - Verarmung +VG<VTn Metall Gate M Polysilizium O QB S x Verarmungs-Region p-Typ, Na - Sobald eine Spannung VG am Gate anliegt, werden durch den Feldeffekt die freien Elektronen (MinLT) des p-dotierten Halbleiters an dessen Oberfläche bewegt - Diese rekombinieren dort mit den Löchern (MajLT) - Übrig bleiben die eindotierten, unbeweglichen, neg. geladenen Akzeptoren - Dieser Vorgang wird Verarmung (depletion) genannt - Die entstandene Ladung nennt man Bulk-Ladung (bulk-charge) QB - QB ergibt sich aus: QB = - 2qε Si N aφ S in C/cm² - Mit q = 1.6*10-19C, εSi = 11.8 ε0, Na = Akzeptordotierungsdichte (typisch: 1015 cm-3) - Während der Verarmung gilt: QS ≈ QB 13 MOS Struktur - Inversion +VG>VTn Metall Gate M Polysilizium O Qn Inversionsschicht QB S p-Typ, Na - Überschreitet VG einen bestimmten Spannungswert (Schwellspannung VT0n), sodass keine Löcher mehr unter dem Oxid sind, setzt die Inversion (inversion) ein - Die angezogenen Elektronen können nicht mehr rekombinieren und sammeln sich in einer Inversionsschicht mit der Ladungsdichte: Qn in C/cm² unter dem Oxid - Q = CV, und somit Qn =-Cox(VG-VTn) - Bei Inversion gilt : QS = QB + Qn - Das Oberflächenpotential bei Entstehung dieser Schicht beträgt φS ≈2|φF| - φF heißt Fermi-Potential. 2|φF| hat bei einem Standart nMOS einen Wert von ca. 0.58V 14 MOS Struktur - Schwellspannung - Die Schwellspannung der MOS Struktur ist die Spannung, die überschritten werden muss, damit sich eine Inversionsschicht bildet - Bei VG = VT0n gilt noch: Qn ≈ 0 und somit QS ≈ QB QB 2qε Si N a (2 | φ F |) Q - V= , also: Vox= = C C ox C ox 1 - Kirchhoff: VT0n = φS + Vox = 2 | φ F | + 2qε Si N a (2 | φ F |) als idealer Wert C ox - Nicht berücksichtigt: Ladungen im Oxid, die das el. Feld beeinflussen und Unterschiede im Material von Gate und Substrat Î Flachbandspannung VFB - Da die zu addierende Flachbandspannung normalerweise negativ ist, wird VT0n negativ - Schwellspannungs-Regulierungs-Ionenimplantat (threshold adjustment ion implant) - Es werden Ionen in einer Menge von DI in cm-2 implantiert qDI 1 2qε Si N a (2 | φ F |) ± - Schwellspannung somit: VT0n = VFB + 2 | φ F | + C ox C ox - Akzeptorimplantat: + qDI qDI ; Donatorimplantat: ; C ox C ox 15 Body Bias Effekt VTn +VSBn +VDSn +VGSn n+, Nd n+, Nd VT0n p-Typ, Na VSBn 0 - Die Schwellspannung eines nMOS ist ähnlich der der MOS-Struktur - Hinzu kommt jedoch die Source-Bulk Spannung, die den Body Bias Effekt auslöst - Mit VSBn liegt eine Spannung in Sperrichtung über dem pn-Übergang, dies erhöht die BulkqDI 1 2qε Si N a (2 | φ F | +VSBn ) ± Ladung QB: VTn = V FB + 2 | φ F | + C ox C ox 1 - ∆VTn = γ ( 2 | φ F | +VSBn − 2 | φ F | ) mit γ = 2qε Si N a als Body-Bias-Faktor C ox - Schwellspannung des nMOS: VTn = VT0n + γ ( 2 | φ F | +VSBn − 2 | φ F | ) - Man sieht: VTn kann in der Herstellung durch Cox und Na beeinflusst werden - Für einen nMOS (Anreicherungstyp) gilt per Definition: 0.5V ≤ VTn ≤ 0.9V 16 I-V Characteristics VS = 0 n+, Nd +VDSn q- +VGSn E Qn IDn n+, Nd QB p-Typ, Na - Solange VGSn < VTn, ist einer von beiden pn-Übergängen gesperrt (cutoff-Mode), hier gilt also IDn ≈ 0 - Wie bei der MOS-Struktur entsteht bei VGSn ≥ VTn eine Inversionsschicht - Die Ladung wird zusätzlich beeinflusst durch VDSn: Qn = -Cox [VGSn –VTn – V(y)] - Dabei gilt für die Grenzen V(0) = VS = 0V und V(L) = VDSn - MaW: [VGSn –VTn – V(y)] ist die Nettospannung über den Kanal an der Stelle y Die Spannung, die die Inversionsschicht unterstützt 17 I-V Characteristics - Drainstrom 0 dy y L Source Drain V(0) W n+, Nd V(L) n+, Nd p-Typ, Na - Über den Widerstand eines Kanalabschnitts kommt man auf: IDn dy = µn Cox W [VGSn-VTn-V(y)] dV mit µn als Elektronenbeweglichkeit in cm²/Vs - Integriert über die Länge des Kanals ergibt sich: W VDSn IDn = k n' [VGSn − VTn − V ( y )] dV L ∫V =0 - Dabei ist k’n= µn Cox der Leitwertparameter (process transconductance), da die Leitfähigkeit von µn, εox und 1/xox abhängt - βn = k’n(W/L) heisst Verstärkungsfaktor (device transconductance), da hier alle wichtigen durch die Produktion beeinflussbaren Größen enthalten sind, die den Strom erhöhen 18 I-V Characteristics – Ungesättigter Stromfluss VS = 0 n+, Nd +VDSn q- +VGSn E Qn IDn n+, Nd QB p-Typ, Na - Bei niedriger Spannung VDSn spricht man von ungesättigtem Stromfluss - Der ungesättigte Strom IDn ergibt sich also zu: β W 1 2 2 ] = n [2(VGSn − VTn )VDSn − VDSn ] IDn = k n' [(VGSn − VTn )V DSn − VDSn L 2 2 - Sobald ein Strom fließt, beginnt der Kanal sich einzuengen - Dies ist auch an der Formel für Qn zu erkennen 19 I-V Characteristics – Gesättigter Stromfluss VGSn-VTn VS = 0 +VGSn n+, Nd q- IDn pinch off n+, Nd QB p-Typ, Na - Sättigung tritt ein bei VDSn = Vsat = VGSn -VTn. Einsetzen: IDn | VDSn =Vsat = βn [2(VGSn − VTn )(VGSn − VTn ) − (VGSn − VTn ) 2 ] = βn (VGSn − VTn ) 2 2 2 - Ist die Sättigung erreicht, schnürt der Kanal sich ab(pinch-off) - Einfachste Form: IDn bleibt bei Sättigung konstant auf diesem Wert - Erhöht man VDSn weiter, wird der Kanal kürzer, dadurch sinkt der Widerstand: IDn| VDSn ≥Vsat = βn (VGSn − VTn ) 2 [1 + λ (V DSn − Vsat )] 2 - Dabei λ ist der Kanallängen-Modulations Parameter 20 I-V Characteristics – Stromkurven IDn IDn VGSn VGSn VDSn 0 VDSn 0 - Kurven für IDn bei einfacher und realer Fortführung im Sättigungsbereich I Dn | Border = βn 2 [2(VGSn − VTn )Vsat − Vsat2 ] = 21 βn 2 Vsat2 pMOS Metal Metal Plug Plug Gate [M] p+, Na n-well, Nd L p+, Na connected to Vmax p+ Substrat - Um pn-Übergänge zu erzeugen wird auf das Substrat eine n-Wanne aufgedampft - Die n-Wanne ist mit der höchsten Spannung verbunden und dient als Bulk Elektrode - Die Kontrollspannung muss negativ sein, der Kanal besteht aus Löchern - Strom fließt hier von Source zu Drain 1 2qε Si N d (2 φ F , p ) < 0 - Schwellspannung ohne Bias: VT0p = V FB. p − 2 φ F . p − C ox - Schwellspannung: VTp = VT 0 p − γ p ( 2 φ F , p + VBSp − 2 φ F , p ) 22 pMOS Metal Metal Plug Plug Gate [M] p+, Na n-well, Nd L p+, Na connected to Vmax p+ Substrat - Ungesättigter Strom: IDp = - Gesättigter Strom: IDp = βp 2 βp 2 [2(VSGp − | VTp |)VSDp − VSDp ] (VSGp − | VTp |) 2 [1 + λ (VSDp − Vsat )] 2 - βp ist hier auch der Verstärkungsfaktor mit - k’p = µpCox als Leitwertparameter - Es gilt: µp < µn und somit: k’p < k’n. Das Verhältnis liegt bei ca. k’p ≈ 2.5 k’n 23 Schaltsymbole Für CMOS Schaltungen sind p- und nMOSFETs als Anreicherungstypen notwendig E-Mode nMOS: G Gate VGSn - + IDn Source n+ Bulk p + VSBn S Drain n+ - D B - VDSn + E-Mode pMOS: G Gate VSGp - + IDp Source p+ Bulk n-well D Drain p+ + B VBSp - - VSDp + 24 S Schaltsymbole In CMOS Schaltungen werden stets beide Transistortypen verwendet (complementary) Schaltungsbeispiel CMOS-Inverter: VDD Vin Vout 25 Herstellung eines CMOS Inverter CMOS Inverter als integrierter Schaltkreis: 1. Oxidieren der Substrat Oberfläche 2. Maskendurchlauf für Dotierung einer p-Wanne 3. Oxidieren und Maskendurchlauf zum Dotieren von Gate und Source des pMOS 26 4. Oxidieren und Maskendurchlauf zum Dotieren von Gate und Source des nMOS 5. Oxidieren und Maskendurchlauf für die Gate-Anschlüsse 6. Maskendurchlauf für Kontakte 7. Maskendurchlauf zum Aufdampfen von Metall 27 Literatur - CMOS Logic Circuit Design John P. Uyemura, Kluwer 1999 S. 01-22+104 - Principles of Semiconductor Devices http://ece-www.colorado.edu/~bart/book/ B. Van Zeghbroeck, 2004 Professor an der Universität von Colorado - Modeling Semicondutor Devices using the VHDL-AMS Language http://www.ececs.uc.edu/~dpl/vishwa_thesis/ Vishwa Shanth R Kasula Srinivas - Tutorium - Funktionsweise des MOS-Transistors http://olli.informatik.uni-oldenburg.de/weTEiS/weteis/tutorium.htm Transistortutorium von der Universität Oldenburg - Einführung in die Halbleiter-Schaltungstechnik http://smile.unibw-hamburg.de/smile/toc.htm Holger Göbel, 2005 Springer-Verlag, Berlin - http://www.wikipedia.org Internet-Enzyklopädie deutsch und englisch 28 29