Entwurf digitaler Schaltungen (F1)

Werbung

Entwurf digitaler Schaltungen (F1)

Einführung

Prof. G. Kemnitz

Institut für Informatik, Technische Universität Clausthal

20. April 2015

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

1/74

Was ist Technische Informatik

Zwei relativ selbständige Gebiete:

die technischen Anwendungen der Informatik

informationstechnische Erfassung, Modellierung und

Steuerung technischer Systeme

die technische Basis der Informatik

Digitaltechnik: Modellierung, Simulation, Entwurf und Test

digitaler Schaltungen

Die LV Entwurf digitaler Schaltungen legt die Grundlagen für

den zweiten Teil. Lernziele: Verständnis und praktische

Fertigkeiten für die Funktionsweise, Modellierung und den

Entwurf digitaler Schaltungen

Voraussetzung imperative Programmierung (C, Pascal o.ä.)

Prüfung schriftlich

Hausübungen

begleitende Laborübungen

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

2/74

Transistoranzahl

Digitale Systeme sind groÿ

109

108

107

106

105

104

103

Six Core Core i7

Zunahme der TransistorCore 2 Duo

anzahl in Prozessoren

Pentium 4

(Verdopplung alle

2 Jahre)

Pentium

80486

80386

8086

Z80

Einführungsjahr

4004

1970

1980

1990

2000

2010

Nach dem Moorschen Gesetz verdoppelt sich die Transistoranzahl

digitaler Schaltungen alle 2 Jahre. Die gröÿten derzeit gefertigten

Schaltkreise enthalten über eine Milliarde Transistoren.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

3/74

Wenn es die Möglichkeit gibt, innerhalb weniger Jahre

funktionierende digitale Schaltungen mit 109 Transistoren zu

entwickeln, herzustellen und in Betrieb zu nehmen, sollte es für

einen angehenden Bachelor of Engineering möglich sein,

funktionierende Schaltungen aus einigen Hundert bis Tausend

Gattern zu verstehen, zu entwerfen und auszuprobieren.

Wie beherrscht man so groÿe Entwürfe?

rechnergestützt, teilautomatisiert,

hierarchisch, mit gut abgestimmten Bausteinkonzepten.

Bausteinsysteme für den Baugruppenentwurf:

Standardschaltkreise,

Rechnerschaltkreise,

programmierbare Logikschaltkreise sowie

Sensoren und Ansteuereinheiten für Aktoren mit digitalen

Ein- und Ausgängen, die direkt oder über Anpassungsschaltkreise an das digitale System anschlieÿbar sind.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

4/74

Aufbau der Vorlesung

Thema 1: Zwei einführende Beispiele

traditioneller Entwurf mit Standardschaltkreisen und

ein vergleichbarer Entwurf in einer Hardware-Beschreibungssprache und einem programmierbaren Logikschaltkreis.

Lernziel:

Der traditionelle Entwurf ist ein Zusammenfügen passgerechter Bausteine nach einfachen Regeln, überwiegend

Fleiÿarbeit. Der Hauptaufwand entfällt wie bei der

Software-Entwicklung auf Test und Fehlersuche.

Der moderne Digitalentwurf funktioniert fast genauso wie

die Software-Entwicklung. Beschreibung der Zielfunktion in

einer Programmiersprache. Simulation auf dem Rechner.

Prototyp-Fertigung ähnlich wie die Programmierung von

Mikrorechnern.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

5/74

Thema 2: Handwerkszeug Teil 1:

Simulation mit VHDL,

synthesegerechte Beschreibung,

Logikoptimierung und

Rechenwerke.

Lernziele:

Einführung in VHDL, ereignisgesteuerte Simulation

kombinatorischer und getakteter Schaltungen, Testrahmen.

Synthesegerechte Beschreibung, Optimierung auf

Hochsprachenniveau und typische Beschreibungsfehler.

Optimierungsziele. Bleistift-und-Papier-Optimierung mit

KV-Diagrammen. Das klassische Verfahren von Quine und

McCluskey sowie die modernen Optimierungsmethoden mit

geordneten binären Entscheidungsdiagrammen.

Rechenwerke: Aufwands- und geschwindigkeitsoptimierte

Schaltungen für die Addition, Subtraktion, Multiplikation,

Vergleicher und Block-Shifter.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

6/74

Thema 3: Handwerkszeug Teil 2:

Automaten,

Operationssteuerungen,

Zeitverhalten und

asynchrone Eingabe.

Lernziele:

Beschreibung von Abläufen mit Automaten. Schaltungsentwurf für Automaten mit KV-Diagrammen. Beschreibung von

Automaten in VHDL. Umgang mit redundanten Zuständen.

Erweiterung des Automatenmodells um die Steuerung und

Auswertung von Register-Transfer-Operationen. Sequentiell

arbeitende Rechenwerke.

Modellierung und Kontrolle von Zeitbedingungen.

Robuste Datenübernahme von Schaltern, Tastern und

Systemen mit nicht ausgerichtetem Takt.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

7/74

Thema 4: Vom Transistor zum Logikbaustein

Aufbau und Funktionsweise von MOS-Transistoren, Gattern,

Speicherzellen, Latches, Registern, RAM, ROM, Flash bis

hin zu programmierbaren Logikschaltkreisen.

Lernziel:

Grundvorstellung der inneren Funktion digitaler Bausteine.

Lösen einfacher Entwurfsaufgaben auf Transistorebene.

Einschätzung der Realisierbarkeit, des Aufwands, der

Geschwindigkeit und des Stromverbrauchs digitaler Systeme.

Thema 5: Komplexe Entwürfe

Dafür erforderliche weitere VHDL-Beschreibungsmittel,

Schrittweiser Entwurf

einer seriellen Schnittstelle,

eines Cordic-Rechenwerks (Sinus, Kosinus, ...) und

eines Spezialrechners für FIR-Filter (Signalverarbeitung).

Lernziele:

Festigung der zuvor vermittelten Lehrinhalte an Beispielen.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

8/74

Inhalt des Foliensatzes

1.1

1.2

1.3

1.4

1.5

2.1

2.2

2.3

2.4

Standardschaltkreise

Beispielentwurf

Test

Schaltungen mit Registern

Leiterplattenentwurf

Aufgaben

VHDL + FPGA

Einfache Gatterschaltung

Zähler und Ampelsteuerung

Simulation

Aufgaben

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

9/74

1. Standardschaltkreise

Prof. G. Kemnitz

Standardschaltkreise

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

10/74

1. Standardschaltkreise

Aufbau und Schaltplan einer digitalen Schaltung

Inverter, Schmitt-Trigger (Schwellwertschalter mit Hyterese)

Steckverbinder

Taster

Kondensator

Widerstand

(US-Symbol)

Das Beispiel zeigt ein Foto und einen Ausschnitt aus dem

Schaltplan einer Mikrorechneransteckbaugruppe für unsere

Mikrorechnerversuchsbaugruppen im Labor mit vier Tastern.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

11/74

1. Standardschaltkreise

UM

Dir En Motorspannung UM

0V

0

UVM

0 1

−UVM

1 1

Sensorsign.

UVM

Der H-Brückenschaltkreis bildet aus den Steuersignalbelegungen

von EN (Enable, Freigabe) und Dir (Direction, Richtung) vom

Mikrocontroller die Spannung für den Motor. Die beiden Inverter

invertieren die vom Motor kommenden Sensorsignale und passen

die Pegel für null und eins an die vom Mikrorechner erwarteten

an.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

12/74

1. Standardschaltkreise

Logikfamilie

Schaltkreise mit unterschiedlichen Logikfunktionen, gleicher

Herstellungsprozess, gleiche Schaltungstechnik mit ähnlichen

elektrischen und mechanischen Eigenschaften, die sich problemlos

kombinieren lassen. Am verbreitetsten war die 74...-Serie.

Schaltungstechnik TTL (Transistor-Transistor-Logik) heute

veraltet. Ein Nachfolger 74HC... CMOS, Bezeichnungen und

Anschlusswerte kompatibel zur 74er-Serie.

74HC00 4

74HC02 4

74HC04 6

74HC08 4

74HC10 3

74HC11 3

74HC14 6

Trigger

Prof. G. Kemnitz

×

×

×

×

×

×

×

·

NAND2

NOR2

Inverter

AND2

NAND3

AND3

Inverter Schmitt

74HC20 2 × NAND4

74HC30 1 ×NAND8

74HC32 4 ×OR2

74HC74 2 ×D-Flipop

74HC75 4 × Latch

74HC86 4 × EXOR

74HC174 6-Bit-Register

...

Institut für Informatik, Technische Universität Clausthal

20. April 2015

13/74

1. Standardschaltkreise

74HC00: 4 × NAND2

UV B4 A4 Y4 B3 A3 Y3

14

13

12

11

10

&

2

8

14

4

5

6

7

74HC174: 6 Bit-Register mit Taktund Rücksetzeingang

10

1

UV Versorgungsspannung

Masse

2

9

8

=1

=1

3

4

5

6

7

A1 B1 Y1 A2 B2 Y2

U V D6 Q6 D5 Q5 D4 Q4

16

15

Funktion:

Bei R̄ = 0 werden alle 6 Speicherzellen gelöscht: Qi = 0

sonst bei steigender Flanke an T

Übernahme Qi ← Di

sonst speichern

·

11

=1

&

3

12

=1

A1 B1 Y1 A2 B2 Y2

Prof. G. Kemnitz

13

&

&

1

9

74HC86 4 × EXOR

UV B4 A4 Y4 B3 A3 Y3

1

2

14

13

12

11

D

R

D

R

D

R

R

D

R

D

R

D

3

4

5

6

T

10

9

7

8

R̄ Q1 D1 D2 Q2 D3 Q3

Institut für Informatik, Technische Universität Clausthal

20. April 2015

14/74

1. Standardschaltkreise

Elektrische Eigenschaften

Testschaltung

Signalverzögerung

Übertragungsfunktion

Ue

UOH

UV

&

Ue

UOH

UIH

UOL

UIL

Ua

Ua

UOL

Ua

UIL UIH Ue

td

minimale Spannung für eine 1 am Ausgang

minimale Spannung für eine 1 am Eingang

maximale Spannung für eine 0 am Ausgang

maximale Spannung für eine 0 am Eingang

Typische elektrische

Eigenschaften der

74HC-Familie

Prof. G. Kemnitz

·

UV

2V

4,5 V

6V

UOH

1,9 V

4,4 V

5,9 V

UIH

1,5 V

3,2 V

4,2 V

UIL

0,5 V

1,4 V

1,8 V

Institut für Informatik, Technische Universität Clausthal

td

t

UV Versorgungsspannung

td Verzögerungszeit

UOL

0,1 V

0,1 V

0,1 V

td

100 ns

20 ns

16 ns

20. April 2015

15/74

1. Standardschaltkreise

Untersuchung einer Beispielschaltung

UV = 3...5 V

C

R1

R2

&

&

BT1 BT2

a

&

&

b

R3

c

LD1

R4

d

LD2

1 × 74HC00

2 Taster

R1 , R2 Pullup-Widerstände 10...100 kΩ

R3 , R4 LED-Vorwiderstände 50...200 Ω

C

Stützkondensator

LD.. Leuchtdioden

2...10 mA bei

UF = 1, 5...2, 5 V

Was passiert, wenn man die Taster nacheinander wie folgt drückt:

BT1

BT2

a

b

c

d

LD1

LD2

aus

an

aus

aus

aus

aus

aus

an

0

1

1

0

aus

an

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

16/74

1. Standardschaltkreise

Einige wichtigste Regeln für den Entwurf

Alle Versorgungsanschlüsse aller Schaltkreise mit

UV = 2...6 V und alle Masseanschlüsse mit Masse verbinden.

Stützkondensator von 10/100nF zwischen UV - und

Masseanschluss der Schaltkreise.

Ein Ausgang kann mehrere Eingänge oder eine Low-Current

LED treiben.

LEDs brauchen immer einen Vorwiderstand zur

Strombegrenzung.

Ungenutzte Eingänge nicht oen lassen, sondern mit UV

oder Masse verbinden.

Ausgänge nie miteinander, mit UV oder Masse verbinden.

Wenn Eingangsspannungen > UV oder < 0 nicht

ausschlieÿbar sind, bei Eingabe über Stecker, 100Ω

Schutzwiderstand in Reihe schalten.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

17/74

1. Standardschaltkreise

Prof. G. Kemnitz

1. Beispielentwurf

Beispielentwurf

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

18/74

1. Standardschaltkreise

Entwurf einer Zählfunktion

1. Beispielentwurf

Aufgabe sei der Entwurf eines 4-Bit-Zählers aus Gattern und

einem 4-Bit-Register. Schaltungsentwurf für die Zähloperation:

Zähloperation

x3 x2 x1 x0

+

c0

y3 y2 y1 y0

x0

y0 x 1

=1

c0

&

+

y1

=1

c1

&

für jedes Bit

Wertetabelle

xi ci ci+1 si

0 0

0 0

0 1

0 1

1 0

0 1

1 1

1 0

Beispiel

x2

1011

1

1100

y2

=1

c2

&

x3

y3

xi

=1

c3

&

c4

Schaltung

=1

yi

ci

Erfordert einen 74HC08 (4×AND2) und einen 74HC86

(4×EXOR).

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

&

ci+1

20. April 2015

19/74

1. Standardschaltkreise

Platzierung und Verdrahtung

x2

74HC08

14

13

12

x3 c4

11

10

9

8

UV

14

13

&

&

UV

y2

74HC86

12

11

y3

10

9

8

UV

&

1

1. Beispielentwurf

2

c0 x0

=1

&

3

4

5

x1

=1

=1

6

7

1

2

=1

3

4

y0

5

6

7

y1

Anordnung auf einem Steckbrett. Blau gesteckte Drahtbrücken,

rot Stützkondensatoren. Eingerahmte Punkte sind verbunden.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

20/74

1. Standardschaltkreise

Prof. G. Kemnitz

2. Test

Test

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

21/74

1. Standardschaltkreise

Schaltungsaufbau mit Electronics Explorer

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

2. Test

20. April 2015

22/74

1. Standardschaltkreise

Testen

statischer Test

UV

···

Testobjekt

···

2. Test

dynamischer Test

UV

SignalTestgenera· · · objekt · · ·

tor

Logikanalysator

Ein statischer Test legt die logischen Eingaben über Schalter oder

Steckbrücken an und prüft die Ausgabewerte mit Leuchtdioden

oder einem Multimeter. Kontrolliert wird die Funktion nach der

Wertetabelle. Bei einem dynamischen Test werden die Eingaben

in Echtzeit von einem Signalgenerator erzeugt und die Ausgabe

mit einem Logikanalysator aufgezeichnet. Dabei werden

zusätzlich die Signalverzögerungen kontrolliert.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

23/74

1. Standardschaltkreise

Statischer Test

2. Test

Der Explorer kann über die Oberäche Static IO unterschiedliche Ein- und Ausgabeelemente für den statischen Test

nachbilden: Leuchtdioden, Schalter, Taster, 7-Segment-Anzeige ...

c4

y3

y2

y1

y0

x3

x2

x1

x0

c0

Der Test der Beispielschaltung erfordert fünf Schalter als Eingabe

und fünf Leuchtdioden als Ausgabe. Damit ist eine Stichprobe

der Zeilen aus der Wertetabelle zu überprüfen. Erkannte Fehler

sind zu beseitigen.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

24/74

1. Standardschaltkreise

Dynamischer Test

2. Test

Für den dynamischen Test sind über die Bedienoberäche

Generator die Anschlusszuordnung und die Signalverläufe für

die Eingabe festzulegen.

Im Beispiel bilden die Eingänge x0 bis x3 einen Bus und c0 ist ein

Einzelsignal. Für alle Eingangssignale ist eingestellt 10 MHz

und Zufallssignale. Nach Konguration starten mit Run.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

25/74

1. Standardschaltkreise

Ergebnisaufzeichnung mit Logikanalysator

2. Test

Ein Logikanalysator zeichnet digitale Abtastwerte auf. Erforderliche Einstellungen: abzutastende Signale, Abtastfrequenz,

Trigger (Bedingung

für den Aufzeichnungsbeginn), ...

·

Prof. G. Kemnitz

Institut für Informatik, Technische Universität Clausthal

20. April 2015

26/74

1. Standardschaltkreise

2. Test

Im Beispiel werden alle Ein- und Ausgangssignale mit 100 MHz,

d.h. mit 10 Werten je Eingabeänderung aufgezeichnet. Damit sind

Verzögerungen mit einer Auösung in 10ns-Schritten erkennbar.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

27/74

1. Standardschaltkreise

Prof. G. Kemnitz

3. Schaltungen mit Registern

Schaltungen mit Registern

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

28/74

1. Standardschaltkreise

Schaltungen mit Registern

3. Schaltungen mit Registern

Ein Register besitzt i.Allg. einen Initialisierungs-, einen Datenund einen Takteingang. Wenn das Signal am Initialisierungseingang aktiv ist (im Bild I = 1), Übernahme eines

Anfangswertes, meist null. Sonst bei aktiver Taktanke (hier

steigender) Datenübernahme, sonst speichern.

x

I

T

x

I

T

y

y

I

Dateneingang

Initialisierungseingang

Takteingang

Datenausgang

T

1

0

I

1

0

x

y

1

0

1

0

unbestimmt

beliebig

Mit Registern werden Schaltungen mit Gedächtnis realisiert, die

ihre Folgezustände und Ausgaben aus der Eingabe und dem

aktuellen Zustand bilden.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

29/74

1. Standardschaltkreise

Vom bisherigen Entwurf zum Zähler

3. Schaltungen mit Registern

Auf der Register-Transfer-Ebene besteht ein Zähler aus dem

bisher entworfenen

4

x

+

Rechenwerk für +c0 c0

und einem 4-Bit-Register mit

I

I

Takt- und Initialisierungseingang.

T

T

I

c0

x

y

y

1

0

1

0

1

0

0100

0100

0000

0001 0010 0011 0100 0101 0101 0110

0000

0001 0010 0011 0100 0100 0101

Als 4-Bit-Register eignet sich z.B. der Schaltkreis 74HC174, der

ein 6-Bit-Register mit Takt- und Initialisierungseingang enthält.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

30/74

1. Standardschaltkreise

Prof. G. Kemnitz

4. Leiterplattenentwurf

Leiterplattenentwurf

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

31/74

1. Standardschaltkreise

Beispielschaltplan in Eagle

4. Leiterplattenentwurf

zwei Schaltkreise, einer mit 4 NAND2 und einer mit 4 EXOR

Stecker mit 3 Eingängen, 2 Ausgängen,

Versorgungsspannung und Masse

Stützkondensatoren bei der Platzierung, unmittelbar an den

Schaltkreisen anzuordnen.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

32/74

1. Standardschaltkreise

Platzierung

4. Leiterplattenentwurf

Nach Wechsel von Bauteile platziert. Die braunen Linien

der Schaltung- zur sind noch anzuordnende Verbindungen

Geometrieansicht.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

33/74

1. Standardschaltkreise

Verdrahtung

4. Leiterplattenentwurf

(blau Unterseite, rot Oberseite; grün Lötaugen, bei

zweiseitigen Leiterplatten mit Durchkontaktierungen (Vias)).

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

34/74

1. Standardschaltkreise

Zusammenfassung

4. Leiterplattenentwurf

Der traditionelle Digitalentwurf bildet die Zielfunktion aus

Schaltkreisen nach. Zusammenfügen passgerechter Bausteine

nach einfachen Regeln, ist überwiegend Fleiÿarbeit. Der

Hauptaufwand entfällt wie bei der Software-Entwicklung auf

Inbetriebnahme, Test und Fehlersuche.

Auÿer mit Gattern und Registern gibt es auch höher integrierte

Schaltkreise mit

Zählern, Schieberegistern, Multiplexern,

Rechenwerken, Rechnerbausteine, Prozessoren, ...

Als es noch Stand der Technik war, Schaltungen aus solchen

Bausteinen zusammen zu setzen, hatte sich eine Vorlesung zum

Entwurf von Digitalschaltungen ab hier weiter mit den

Funktionen dieser quasi Standardbausteine und ihrer Erweiterung

zu gröÿeren Systeme befasst.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

35/74

1. Standardschaltkreise

Prof. G. Kemnitz

5. Aufgaben

Aufgaben

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

36/74

1. Standardschaltkreise

Aufgabe 1.1: Ausfüllen der Wertetabelle

5. Aufgaben

Gegeben ist die nachfolgende Schaltung. Füllen Sie die

Wertetabelle rechts daneben aus.

x1

&

z4

&

z5

z1

x2

z2

x3

Prof. G. Kemnitz

&

z3

·

&

y

x3

0

0

0

0

1

1

1

1

x2

0

0

1

1

0

0

1

1

x1

0

1

0

1

0

1

0

1

z5 z4 z3 z2 z1

Institut für Informatik, Technische Universität Clausthal

y

20. April 2015

37/74

1. Standardschaltkreise

Aufgabe 1.2: Signalverläufe bestimmen

&

x

I

T

5. Aufgaben

y1

z1

≥1

z2

y2

I

I

unbestimmt

beliebig

T

1

0

I

1

0

x

1

0

z1

1

0

z2

1

0

y1

1

0

y2

1

0

Ergänzen Sie die Signalverläufe für z1 ,z2 , y1 und y2 .

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

38/74

1. Standardschaltkreise

Aufgabe 1.3: Verdrahtungen

5. Aufgaben

Die Schaltung aus Aufgabe 1.1 soll mit je einem Schaltkreis vom

Typ 74HC00 und 74HC10 aufgebaut werden. Entwickeln Sie eine

Schaltplan und tragen Sie in die nachfolgende Tabelle die

Signalnamen ein, an die die Schaltkreisanschlüsse in der

Schaltung anzuschlieÿen sind.

74HC00

UV B4 A4 Y4 B3 A3 Y3

14

13

12

11

10

&

2

2

UV C1 Y1 C3 B3 A3 Y3

14

13

12

11

10

&

3

4

5

3

4

9

8

6

7

&

&

&

6

A1 B1 Y1 A2 B2 Y2

1

74HC10

8

&

&

1

9

5

7

6

1

2

3

4

5

A1 B1 A2 B2 C2 Y2

7

8

9

10

11

12

13

14

74HC00

74HC10

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

39/74

2. VHDL + FPGA

Prof. G. Kemnitz

VHDL + FPGA

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

40/74

2. VHDL + FPGA

Hardware-Programmierung

Heutiger Stand der Technik für den Entwurf digitaler

Schaltungen ist die Beschreibung der Zielfunktion in einer

Hardware-Beschreibungssprache. Simulation auf dem Rechner.

Prototyp-Fertigung mit programmierbaren Logikschaltkreisen

(FPGA eld programmable logic circuits). FPGAs bestehen aus

programmierbaren Logikblöcken,

programmierbaren EA-Schaltungen,

einem programmierbaren Verbindungsnetzwerk und

optional weiteren kongurierbaren Schaltungsblöcken, z.B.

Blockspeichern, Multiplizierern, Taktversorgung (Taktteiler

und -vervielfacher, Zeitversatzkorrektur) und

Prozessorkernen.

Programmierung ähnlich wie bei Mikrorechnern über eine serielle

Programmierschnittstelle (JTAG, ISP,...). Programmierdauer

wenige Minuten.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

41/74

2. VHDL + FPGA

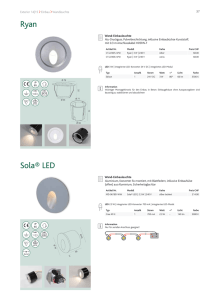

Prototyp-Plattform für die Laborübungen

IO

PLB

PLB

PLB

PLB

IO

IO

PLB

IO

Prof. G. Kemnitz

programmierbarer

Logikblock

programmierbares

Verbindungsnetzwerk

programmierbare Eingabe-Ausgabe-Schaltung

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

42/74

2. VHDL + FPGA

Das verwendete Prototypboard hat

einen programmierbaren Schaltkreis für Schaltungen, die mit

normalen Schaltkreisen bis zu 106 Gatter umfassen können,

50MHz Quarztakt, 8 Leuchtdioden, 4 7-Segment-Anzeigen,

8 Schalter, 4 Taster, 1MB SRAM,

Anschlüsse für PS2, UART und VGA.

Ausreichend für alles, was im Studium vermittelbar ist.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

43/74

2. VHDL + FPGA

Prof. G. Kemnitz

1. Einfache Gatterschaltung

Einfache Gatterschaltung

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

44/74

2. VHDL + FPGA

Einprogrammieren von Logikfunktionen

1. Einfache Gatterschaltung

Schalter

SW0

SW1

SW2

SW3

SW4

SW5

SW6

SW7

programmierbarer Schaltkreis

F12

G12

H14

H13

J14

J13

K14

K13

Leuchtdioden

&

K12

LD0

&

P14

LD1

≥1

L12

LD2

=1

N14

LD3

Im ersten Beispiel sollen vier Gatter so einprogrammiert werden,

dass die Eingänge von Schaltern steuer- und die Ausgänge mit

LEDs beobachtbar sind. Die Kästchen mit F12 etc. sind die

Bezeichner der Schaltkreisanschlüsse, an denen die Schalter und

LEDs auf der Baugruppe angeschlossen sind.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

45/74

2. VHDL + FPGA

1. Einfache Gatterschaltung

Eine VHDL-Beschreibung besteht aus Schnittstellenbeschreibung:

entity Gatterschaltung is

port(sw: in std_logic_vector(7 downto 0);

led: out std_logic_vector(3 downto 0));

end entity;

und einer Beschreibung der Realisierung

architecture test of Gatterschaltung is

begin

SW0

F12

led(0) <= sw(0) and sw(1); SW1 G12

led(1) <= sw(2) nand sw(3); SW2 H14

led(2) <= sw(4) or sw(5);

SW3

H13

led(3) <= sw(6) xor sw(7);

SW4

J14

end architecture;

SW5

J13

SW6

&

K12

LD0

&

P14

LD1

≥1

L12

LD2

K14

LD3

=1

N14

Die Schnittstelle deniert für die

SW7

K13

Anschlüsse Bezeichner, Flussrichtungen (Ein-/Ausgang) und Datentyp. In der Realisierung

stehen im Beispiel Zuweisungen logischer Verknüpfungen von

Eingabesignalen an Ausgabesignale.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

46/74

2. VHDL + FPGA

Entwurf

1. Einfache Gatterschaltung

Projekt anlegen, einige Kongurationen vornehmen, ...

Beschreibung eingeben, Syntaxtest, optional Simulation, ...

Übersetzen (Synthesize bis Congure Target Device)

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

47/74

2. VHDL + FPGA

Das Constraint-File

1. Einfache Gatterschaltung

Die Constraint-Datei enthält alle zusätzlichen Informationen zur

Vorgabe der Zielfunktion, die nicht in der VHDL-Datei stehen:

die Pin-Namen der Schaltungsanschlüssen (s.o.), Taktfrequenz,

obere und untere Schranken für Verzögerungen, ...

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

48/74

2. VHDL + FPGA

Synthese

1. Einfache Gatterschaltung

Berechnung einer Schaltung aus der VHDL-Beschreibung. Im

Beispiel ist das trivial, weil die Schaltung nur aus vier Gattern

besteht. Für gröÿere Entwürfe wird die Zielfunktion mit

Bitvektoren, arithmetischen Operatoren, Fallunterscheidungen,

Unterprogrammen, ... beschrieben. Die Synthese muss daraus die

logischen Funktionen extrahieren, optimieren, mit

Teilschaltungen nachbilden, ...

x0 x1 ∧ ∧ ∨ ⊕

Unser programmierbarer Schaltkreis hat

0 0 0 1 0 0

statt Gatter als logische Grundbausteine

0 1 0 0 1 1

1 0 0 0 1 1

Tabellenfunktionen (LUT Look-Up Table,

1 1 1 0 1 0

kleine programmierbare Speicher).

An den Anschlüssen werden Buer eingefügt, die die internen

kleineren Spannungspegel (0/1V) auf die gröÿeren Anschlusspegel

(0/2,5...3,3V) umsetzen.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

49/74

2. VHDL + FPGA

sw(7:0)

Prof. G. Kemnitz

I

ibuf

O

sw 0 IBUF

I

I

ibuf

O

sw 1 IBUF

ibuf

O

sw 2 IBUF

I

I

ibuf

O

sw 3 IBUF

ibuf

O

sw 4 IBUF

I

I

ibuf

O

sw 5 IBUF

ibuf

O

sw 6 IBUF

I

·

ibuf

O

sw 7 IBUF

1. Einfache Gatterschaltung

O

I1

I0

lut2

I

obuf

O

led(3:0)

led 0 obuf

led 0 annd00001

I1

I0

O

lut2

I

obuf

O

led 1 obuf

led 1 not00001

O

I1

I0

lut2

I

obuf

O

led 2 obuf

led 2 or00001

O

I1

I0

lut2

I

obuf

O

led 3 obuf

Mxor led<3> Result1

Institut für Informatik, Technische Universität Clausthal

lut programmierte

Tabellenfunktion

(look-up table)

ibuf Eingangstreiber

(input buffer)

obuf Ausgangstreiber

(output buffer)

20. April 2015

50/74

2. VHDL + FPGA

Verdrahtung

1. Einfache Gatterschaltung

Prof. G. Kemnitz

BRAM

VN

LUTs

Nach der Synthese folgt die Platzierung der einzelnen

Funktionsblöcke und ihre Verdrahtung. Ein FPGA besteht aus

kongurierbaren Funktionsblöcken (LUTs), EA-Schaltungen,

Multiplizierern, Blockspeichern (BRAM),... und programmierbare

Verbindungsnetzwerken (VN).

sw(4)

sw(5)

led(2)

EA

sw(2)

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

51/74

2. VHDL + FPGA

1. Einfache Gatterschaltung

Ein vergröÿerter Ausschnitt mit dem Logikblock, in den das

EXOR-Gatter programmiert ist, und den beiden

Eingangstreibern vor dem EXOR. Handverdrahtung ist möglich,

aber nicht zu empfehlen.

Pin sw(6)

mit ibuf

LUT mit EXOR-Funktion

Leitung zu

led(3)

progr.

Verbindungsnetzwerk

spezielle Signalleitungen

Prof. G. Kemnitz

·

progr.

Verbindungsnetzwerk

Pin sw(7)

mit ibuf

allgemeine Signalleitungen

Institut für Informatik, Technische Universität Clausthal

20. April 2015

52/74

2. VHDL + FPGA

Komplexere Gatterschaltungen

1. Einfache Gatterschaltung

Die Inkrementoperation

c4 y = x + c0

(x, y 4-Bit-Vektoren) lässt sich mit derselben Schaltung wie auf

Folie 19 implementieren:

x0

y0 x 1

=1

c0

&

y1

=1

c1

&

x2

y2

x3

=1

c2

&

=1

c3

entity Increment4Bit is

port(cin: in std_logic;

x: in std_logic_vector(3 downto 0);

y: out std_logic_vector(3 downto 0);

cout: out std_logic);

end entity;

Prof. G. Kemnitz

·

y3

&

Institut für Informatik, Technische Universität Clausthal

c4

20. April 2015

53/74

2. VHDL + FPGA

x0

y0 x 1

=1

c0

&

1. Einfache Gatterschaltung

y1

=1

c1

&

x2

y2

=1

c2

&

x3

y3

=1

c3

&

c4

architecture Gatter_Arch of Increment4Bit is

signal c: std_logic_vector(4 downto 0);

begin

c(0) <= cin;

y(0) <= x(0) xor c(0); c(1) <= x(0) and c(0);

y(1) <= x(1) xor c(1); c(2) <= x(1) and c(1);

y(2) <= x(2) xor c(2); c(3) <= x(2) and c(2);

y(3) <= x(3) xor c(3); c(4) <= x(3) and c(3);

cout <= c(4);

end architecture;

Neu benutzte Konstrukte: Bitvektoren und Signale für interne

Verbindungen.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

54/74

2. VHDL + FPGA

1. Einfache Gatterschaltung

Die vier bis auf die Indizes gleichen Zeilen können auch zu einer

Schleife zusammengefasst werden. Das ist keine Ablaufschleife,

deren Anweisungen im Schleifenkörper hintereinander mit dem

Index 0 bis 3 abgearbeitet werden, sondern eine

Generierungsschleife, die bei der Übersetzung durch je eine

Anweisungspaar für jeden Indexwert ersetzt wird.

architecture Gen_Arch of Increment4Bit is

signal c: std_logic_vector(4 downto 0);

begin

c(0) <= cin;

genHA: for i in 0 to 3 generate

y(i) <= x(i) xor c(i); c(i+1) <= x(i) and c(i);

end generate;

cout <= c(4);

end architecture;

Die Schleifenvariable einer Generierungsschleife braucht keine

explizite Deklaration und die Iterationsgrenzen müssen zum

Übersetzungszeitpunkt bekannt sein.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

55/74

2. VHDL + FPGA

1. Einfache Gatterschaltung

Noch einfacher ist theoretisch die Beschreibung mit dem

Additionsoperator:

use ieee.numeric_std.all;

...

architecture Num_Arch of Increment4Bit is

signal sum: unsigned(4 downto 0);

begin

sum <= ('0' & x) + cin;

y <= sum(3 downto 0);

cout <= sum(4);

end architecture;

Anmerkungen:

Das Package ieee.numeric_std deniert unsigned und den

Additionsoperator dafür.

x, y müssen hier vom unsigned(3 downto 0) und cin vom Typ

unsigned(0 downto 0) sein. Erfordert Typumwandlungen.

'0' & ... hängt an a zur Verlängerung auf 5 Bit eine

führende null an. Erforderlich für Übertragsberechnung.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

56/74

2. VHDL + FPGA

Prof. G. Kemnitz

2. Zähler und Ampelsteuerung

Zähler und Ampelsteuerung

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

57/74

2. VHDL + FPGA

Zähler als Taktteiler

2. Zähler und Ampelsteuerung

z24

z25

z26

+1

z

32

z27

z28

z29

z30

GCLK0

T9

z31

K12

P14

L12

N14

P13

N12

P12

P11

led(0)

led(1)

led(2)

led(3)

led(4)

led(5)

led(6)

led(7)

(50 MHz)

An Pin T9 liegt auf der Baugruppe der 50MHz-Takt an. Dieser

soll mit einem 32-Bit-Zähler gezählt und die höchstwertigen 8 Bit

auf LEDs ausgegeben werden. Jedes Zählbit halbiert den Takt:

Prof. G. Kemnitz

·

f (zi ) = 50 MHz · 2−(i+1)

Institut für Informatik, Technische Universität Clausthal

20. April 2015

58/74

2. VHDL + FPGA

2. Zähler und Ampelsteuerung

programmierter Schaltkreis

z24

z25

z26

+1

Takteingang

Prof. G. Kemnitz

32

z27

z28

z29

z30

T9

GCLK0

GCLK0

z0

z1

z2

z3

z

z31

K12

P14

L12

N14

P13

N12

P12

P11

Leuchtdioden

led(0)

led(1)

led(2)

led(3)

led(4)

led(5)

led(6)

led(7)

tP = f1

0,67 s

1,34 s

2,68 s

5,37 s

10,7 s

21,5 s

43,0 s

83,9 s

50 MHz

25 MHz

12,5 MHz

6,25 MHz

3,125 MHz

1

0

1

0

1

0

1

0

1

0

·

f

1,5 Hz

745 mHz

373 mHz

186 mHz

93 mHz

47 mHz

23 mHz

11 mHz

Institut für Informatik, Technische Universität Clausthal

20. April 2015

59/74

2. VHDL + FPGA

2. Zähler und Ampelsteuerung

Schnittstellenbeschreibung:

entity Taktteiler is

port(GCLK0: in std_logic;

led: out unsigned(7 downto 0));

end entity;

Beschreibung der Realisierung:

architecture test of Taktteiler is

signal z: unsigned(31 downto 0);

begin

process(GCLK0)

begin

if rising_edge(GCLK0) then

z24

z25

z <= z + 1;

end if;

end process;

-- Ausgabefunktion

led <= z(31 downto 24);

end architecture;

Prof. G. Kemnitz

·

z26

+1

z

32

z27

z28

z29

z30

T9

z31

K12

P14

L12

N14

P13

N12

P12

P11

led(0)

led(1)

led(2)

led(3)

led(4)

led(5)

led(6)

led(4)

GCLK0

Institut für Informatik, Technische Universität Clausthal

20. April 2015

60/74

2. VHDL + FPGA

2. Zähler und Ampelsteuerung

Die Beschreibungsschablone für eine Register-Transfer-Funktion

ist ein Prozess1 mit dem Takt in der Weckliste2 (hier CCLK0)

und Signalzuweisungen nur bei aktiven Taktanke:

process(GCLK0)

begin

if rising_edge(GCLK0) then

z <= z + 1;

end if;

end process;

32

z

8

+1

led

GCLK0

Die Beschreibungsschablone einer einfachen kombinatorischen

Schaltung, hier die Verbindung der Registerausgänge mit den

Schaltkreis- ausgängen zu den LEDs, bleiben weiterhin

nebenläuge Signalzuweisungen ohne Prozessrahmen:

led <= z(31 downto 24);

Prozess ist ein Rahmen, in dem die Anweisungen bei der Simulation

imperativ, d.h. wie bei einem normalen Programm hintereinander, statt

nebenläug abgearbeitet werden.

2

Signalliste hinter process, deren Wertänderungen den Prozess wecken.

1

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

61/74

2. VHDL + FPGA

2. Zähler und Ampelsteuerung

Die meisten Register-Transfer-Funktionen haben eine asynchrone

Anfangsinitialisierung für die Reset-Funktion des Gesamtsystems.

Bei dieser steht zusätzlich zum Takt das Initialisierungssignal in

der Weckliste. Wenn es aktiv ist (im Beispiel bei I='1')

übernimmt das Register eine Konstante (im Beispiel alles null).

Alle anderen Signalzuweisungen nur bei inaktivem

Initialisierungssignal und aktiver Taktanke:

process(I, GCLK0)

begin

if I='1' then

z <= (others=>'0')3 ;

elsif rising_edge(GCLK0) then

32

z

8

+1

I

led

I

GCLK0

z <= z + 1;

end if;

end process;

Das ist eine Zuordnungsliste, die allen anderen Bits, den der Wert nicht

explizit zugeordnet wird, z.B. mit 0=>'1' der Wert '0' zugeordnet.

3

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

62/74

2. VHDL + FPGA

Erweiterung zu einer Ampelsteuerung

2. Zähler und Ampelsteuerung

z24

+1

GCLK0

T9

z

32

z(28...25)

0000

0001

0010

0011

0100

...

Autos

gelb

gelb

grün

grün

grün

...

Fussg.

rot

rot

rot

rot

rot

...

K12

led(0)

N14

P13

N12

P12

P11

led(3)

led(4)

led(5)

led(6)

led(7)

Komplexere kombinatorische Funktionen werden durch Prozesse

mit allen Eingabesignalen in der Weckliste beschrieben, die bei

bei jedem Aufwecken alle Ausgabesignale neu berechnen:

process(z)

begin

led(0) <= z(24);

-- Ausgabe von z24 auf eine LED

<Beschreibung der Tabelle siehe nächste Folie>

end process;

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

63/74

2. VHDL + FPGA

2. Zähler und Ampelsteuerung

z24

+1

GCLK0

T9

z

32

z(28...25)

0000

0001

0010

0011

0100

...

Autos

gelb

gelb

grün

grün

grün

...

Fussg.

rot

rot

rot

rot

rot

...

K12

led(0)

N14

P13

N12

P12

P11

led(3)

led(4)

led(5)

led(6)

led(7)

Tabellenbeschreibung mit einer Case-Anweisung:

case z(28 downto 25) is

when "0000"|"0001" => led(7 downto 3) <= b"010_01"; --A:gelb, F:rot

when "0010"|"0011"

=> led(7 downto 3) <= b"100_01"; --A:grün, F:rot

-- ab hier selbst weiterentwickeln

when others

=> led(7 downto 3) <= b"001_01"; --A:rot, F:rot

end case;

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

64/74

2. VHDL + FPGA

Prof. G. Kemnitz

3. Simulation

Simulation

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

65/74

2. VHDL + FPGA

Simulation

3. Simulation

Die Simulation benötigt ein Testobjekt. Das sei hier die

nachfolgende Zählfunktion:

Zusätzlich wird ein Testrahmen zur Erzeugung der

Eingabesignale benötigt. Das ist eine Entwurfseinheit mit dem

Testobjekt als Teilschaltung und im einfachsten Fall einem

Prozess zur Erzeugung der Eingabe.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

66/74

2. VHDL + FPGA

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

3. Simulation

20. April 2015

67/74

2. VHDL + FPGA

Simulationsarten

3. Simulation

Simulation des Verhaltens ohne Verzögerungen:

Simulation der synthetisierten und verdrahteten Schaltung

(mit Verzögerungen)

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

68/74

2. VHDL + FPGA

Zusammenfassung

3. Simulation

Im modernen Digitalentwurf wird die Zielfunktion in einer

Hochsprache mit Datentypen und -objekten, arithmetischen und

logischen Operatoren, Fallunterscheidungen, Schleifen,

Unterprogrammen, ... beschrieben. Eine so beschriebene

Schaltung kann simuliert und innerhalb weniger Minuten

übersetzt, in einem Schaltkreis geladen und getestet werden.

Ähnlich wie im Software-Entwurf.

Die bisher eingeführten Beschreibungsmittel sind bereits

ausreichend, um die Zielfunktionen digitaler Schaltungen mit

einigen hundert bis tausend Gattern zu beschreiben, zu simulieren

und erfolgreich in Betrieb zu nehmen. Die weiteren Foliensätze

werden VHDL detaillierter einführen und auf weitere nützliche

Beschreibungsmittel eingehen, insbesondere für Testrahmen,

synthesegerechte Beschreibungen und ezientes Debuggen.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

69/74

2. VHDL + FPGA

Prof. G. Kemnitz

4. Aufgaben

Aufgaben

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

70/74

2. VHDL + FPGA

4. Aufgaben

Aufgabe 2.4: Beschreibung einer Gatterschaltung

Beschreiben Sie die nachfolgende Gatterschaltung in VHDL.

Prof. G. Kemnitz

x1

x2

x3

·

&

z3

&

z4

&

z5

z1

z2

&

Institut für Informatik, Technische Universität Clausthal

y

20. April 2015

71/74

2. VHDL + FPGA

Aufgabe 2.5: Extraktion einer Gatterschaltung

4. Aufgaben

Zeichnen Sie die Schaltung zu der nachfolgenden

VHDL-Beschreibung.

entity GSxx is

port(

x: in std_logic_vector(3 downto 0);

y: out std_logic_vector(1 downto 0);

end entity;

architecture a1 of GSxx is

signal z: std_logic;

begin

z <= x(0) and (not x(1)) and x(3);

y(0) <= z or (x(2) and not(x(0)));

y(1) <= z or (not(x(2) and x(3));

end architecture;

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

72/74

2. VHDL + FPGA

4. Aufgaben

Aufgabe 2.6: Schaltung mit Speicherelementen

Beschreiben Sie die nachfolgende Schaltung in VHDL.

&

x

I

T

y1

z1

≥1

z2

y2

I

I

Hinweis: Die Initialisierung sei asynchron. Verwenden Sie die

Beschreibungsschablone auf Folie 62.

Prof. G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

20. April 2015

73/74

2. VHDL + FPGA

Aufgabe 2.7: Testrahmen

4. Aufgaben

Entwickeln Sie einen Testrahmen, der für die Schaltung und das

Simulationsmodell aus der Aufgabe zuvor die zu ergänzenden

Signalverläufe in der nachfolgenden Abbildung berechnet.

T

1

0

I

1

0

x

1

0

z1

1

0

z2

1

0

y1

1

0

y2

1

0

Prof. G. Kemnitz

0

·

20

40

60

80

100 120 140 160

Institut für Informatik, Technische Universität Clausthal

t in ns

20. April 2015

74/74