Bachelor-/Masterarbeit - "Eingebettete Systeme und ihre

Werbung

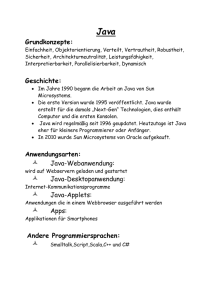

Bachelor-/Masterarbeit: Toplevel-Integration eines CGRAs auf einer Zynq-Plattform Abb : Schematischer Aufbau des Toplevel-Moduls (rote Komponenten und Verbindungen sind neu zu implementieren) Ein Coarse Grain Reconfigurable Array (CGRA) besteht aus einer Menge von miteinander verbundenen Processing Elements (PE) mit jeweils eigenem Daten- (REGFILE) und Programmspeicher (ContextMem). Es kann Algorithmen auf Instruktionsebene parallel und damit beschleunigt ausführen. Für den produktiven Einsatz als eingebettetes System muss ein CGRA aber auch mit verschiedenen Peripheriekomponenten und einem Host-Prozessor kommunizieren: • Einlesen von Sensordaten in das CGRA • Ausgeben von Aktordaten durch das CGRA • Beschreiben der Programmspeicher durch den Host-Prozessor • Austausch von temporären Daten mit einem an den Hauptspeicher angeschlossenen Cache • Streamen von Berechnungsergebnissen/Log-Daten in den Hauptspeicher Im Rahmen einer Masterarbeit soll ein CGRA in ein Xilinx Zynq Multi-Processor System on Chip (MPSoC) integriert werden. Das MPSoC besteht aus einem Processing System (PS), der Programmable Logic (PL) sowie verschiedenen Speicher und Bussen (bspw. AXI) zum Datenaustausch zwischen PS und PL. Das ARM-basierte PS soll als Host-Prozessor verwendet werden. Folgende Komponenten werden dabei vorgegeben: • ein Xilinx Zynq Evaluationsboard (XC7Z045) inklusive Vivado Toolchain • ein vom FG RS (FB 18) entworfenes Java Programm, welches die Verilog-Beschreibung eines CGRAs inklusive dessen Anbindung an einen Daten-Cache generiert • die Verilog-Beschreibungen verschiedene Sensor-/Aktor Controller, die ihre Daten in Ein/Ausgabespeicher (BRAM) schreiben • die Verilog-Beschreibung eines exemplarischen AXI-Controller, mit dem die Programmspeicher der PEs beschrieben werden kann Diese Komponenten sollen nun um verschiedene Module erweitert werden (für eine Bachelorarbeit wird eine angemessene Teilmenge dieser Aufgaben ausgewählt): • C/C++ API und eine entsprechende AXI-Implementierung zur gezielten Modifikation der PE Programmspeicher durch den Host-Prozessor • Anschluss eines Daten-Speichers an die vorhandenen Log-Ports des CGRAs • Sortieren und Filtern der Log-Daten gemäß Vorgabe durch den Host-Prozessor • Speichercontroller zum Streamen der (selektierten) Log-Daten in den Hauptspeicher • Anschluss der vorhandenen Peripherieports des CGRAs sowie des Host-Prozessors an die Sensor/Aktor Controller • Konfigurierbarer Takt- und Zyklenzähler, der die Abtastrate für die Periherie-Komponenten vorgibt und sowohl CGRA als auch den Host-Prozessor über den Beginn einer neuen Abtastperiode informiert Alle Verilog Module (auch die bereits vorgegebenen) sollen dabei durch das (in Java implementierte) Generator-Programm gemäß verschiedener Konfigurationsparameter erzeugt werden. Ein Grundgerüst des Toplevel-Generators ist bereits vorhanden. Die erzeugten Module müssen dokumentiert und charakterisiert (Funktionsfähigkeit, Durchsatz, Latenz, etc.) werden. Der Arbeitsfortschritt ist durch regelmäßiges Einpflegen des Quellcodes in ein Versionsverwaltungssystem (Git) nachzuweisen. Benötigte Kenntnisse: Java, Verilog, C Bei Interesse melden Sie sich bei: Andreas Engel ([email protected]), S2|02 E106