Entwurf Integrierter Schaltungen I

Werbung

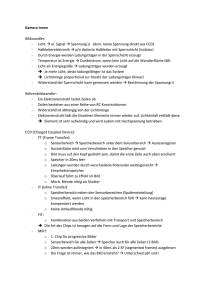

Fragen Entwurf Integrierter Schaltungen I Florian Franzmann∗ 7. April 2009, 23:52 Uhr Abbildungsverzeichnis Tabellenverzeichnis 1 Beispiele für ideale und reale Bauelemente . . . . . . . . . . . . . . . . . . 27 Inhaltsverzeichnis 1 Einführung 1.1 Fragen aus dem Skript . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.2 Zusätzliche Fragen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 2 4 2 Technologie 2.1 Fragen aus dem Skript . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.2 Zusätzliche Fragen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 5 7 3 Das Verhalten des MOS-Transistors 8 3.1 Fragen aus dem Skript . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 3.2 Zusätzliche Fragen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 4 Elektrische Grundschaltungen CMOS 13 4.1 Fragen aus dem Skript . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 4.2 Zusätzliche Fragen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 ∗ [email protected] 1 1 Einführung 5 Elektrische Probleme des Entwurfs 19 6 Layout 23 7 Schaltungssimulation 27 7.1 Fragen aus dem Skript . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 7.2 Zusätzliche Fragen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 8 Aufbau- und Montagetechnik 30 8.1 Fragen aus dem Skript . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 8.2 Zusätzliche Fragen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 1 Einführung 1.1 Fragen aus dem Skript Frage 1.1 Was besagt Moore’s Law? Ist es physikalisch begründet? Antwort 1.1 Die Dichte der Transistoren auf einem neuen Chip verdoppelt sich alle 24 Monate. Das Gesetz ist nicht physikalisch begründet und gilt nur so lange wie eine weitere Verkleinerung der Strukturen wirtschaftlich ist. Frage 1.2 Welche Entwurfsstile kennen Sie? Antwort 1.2 ASIC Kundenspezifischer IC, meist mit speziellen Zeit und Aufwand sparenden automatisierten Entwurfsmethoden entwickelt. ASSP Anwendungsspezifische Standardprodukte. Werden in großen Stückzahlen für verschiedene Gerätehersteller entwickelt. Full Custom Vollständig speziell entwickelte Schaltung mit entsprechendem handoptimiertem Layout. Semi Custom Überbegriff für ASIC, Standardzellen und Gate Array. Hersteller liefert Teile, die funktionieren „wie simuliert“. Standardzellen Entwurf unter Verwendung eines vorher entwickelten Katalogs von LayoutBausteinen. Ausgehend von der Netzliste kann das Layout automatisch erzeugt werden. Alle Maskenebenen müssen erzeugt werden. „Standard“ bedeutet hier „Zellen gleicher Höhe“. Das Verfahren ist für mittlere bis große Stückzahlen geeignet, ca. 70000 Transistoren pro Personenmonat sind möglich. 2 1 Einführung Gate Array Vorgefertigte Siliziumscheiben mit Matrix von Einzeltransistoren. Nur die Verdrahtung wird bei der Entwicklung neu erzeugt ⇒ nur wenige Maskenebenen. Für kleine bis mittlere Stückzahlen, tritt heute zugunsten von FPGA zurück. FPGA Kein Entwurf von Masken nötig, Katalog-Bauelemente. Logiksynthese ausgehend von Hardwarebeschreibungssprache auf Basis verfügbarer Strukturen. Programmierung fest, löschbar oder flüchtig. Für Versuchsmuster, kleine bis mittlere Serien. Frage 1.3 Was versteht man unter Dickschichtschaltung, was unter Dünnschichtschaltung? Antwort 1.3 Dickschichtschaltung Schaltungen werden im Siebdruckverfahren mit Hilfe geeigneter Pasten aufgedruckt und eingebrannt (keramisches Substrat). Möglich sind Verdrahtung, Widerstände, Isolation, Kondensatoren. Dünnschichtschaltung Abscheidung dünner Schichten auf eine Glasplatte, die durch Photolithographie und Ätzverfahren strukturiert werden. Montage von ICs ist möglich. Frage 1.4 Was versteht man unter monolithischer Integration? Antwort 1.4 Gemeinsame Herstellung vieler Aktiv- und Passivelemente auf einem gemeinsamen Substrat. Frage 1.5 Was versteht man unter Fin-Fet? Antwort 1.5 Hochkant stehender Doppeltransistor, derzeit noch nicht in Produktion. Frage 1.6 Wie sieht der Querschnitt eines Bipolartransistors aus? Antwort 1.6 Grafik Frage 1.7 Nach welche Grundsätzen sind FPGAs aufgebaut? Welche Möglichkeiten der Programmierung gibt es? Antwort 1.7 Programmierbare Logikelemente und programmierbare Verbindungen, sowie Look-UpTables. Programmierung kann fest, löschbar oder flüchtig erfolgen. 3 1 Einführung Frage 1.8 Welche Probleme machen es in Zukunft immer schwerer die Integrationsdichte weiter zu erhöhen? Antwort 1.8 Photolithographie braucht elektromagnetische Wellen zur Belichtung. Die kleinsten darstellbaren Strukturen liegen in der Größenordnung der Wellenlänge. Kurzwellige Strahlung läßt sich aber nur schlecht fokussieren. Außerdem elektrische Probleme – Uth läßt sich nicht senken und ist somit die untere Grenze für die Betriebsspannung. Hitzeprobleme, Übersprechen. Frage 1.9 Wie läßt sich die Ausbeute modellieren? Antwort 1.9 YGesamt = Y YEinzelschritt ∀Fertigungsschritte Frage 1.10 Wie ist die Ausbeute von Chips auf einem Wafer definiert? Wie kann man sie erhöhen? Antwort 1.10 Verhältnis von Chips, die die Abnahmetests bestehen zu geometrisch möglichen Chips. Kann erhöht werden durch Verkleinerung der Chipfläche. Frage 1.11 Was für Defekte begrenzen die Ausbeute? Antwort 1.11 Punktförmige Defekte, z. B. verursacht durch Staub. Frage 1.12 Wie lautet Moores Ausbeuteformel? Ist sie theoretisch begründet? Antwort 1.12 YW = e− √ AD Sie ist nicht theoretisch begründet, sondern empirisch gefunden worden. 1.2 Zusätzliche Fragen Frage 1.13 Wie ändern sich die IC-Kosten, wenn bei gleichbleibender Defektdichte D = 1 cm−2 die IC-Fläche von 2 cm2 auf 1 cm2 halbiert wird (verwenden Sie die Ausbeuteformel von Moore)? 4 2 Technologie Antwort 1.13 √ Kneu Aneu e− Aalt·D = · √ Kalt Aalt e− Aneu·D 2 Technologie 2.1 Fragen aus dem Skript Frage 2.1 Welche Parasitären Bipolartransistorean gibt es im 1. n-Wannen-Prozeß? 2. p-Wannen-Prozeß? Welche Probleme können sie bewirken? Antwort 2.1 Grafik Vertikale Bipolartransistoren verursachen Leckstrom über Substrat ⇒ Verlustleistung. Latch-Up-Effekt kann Schaltungen irreparabel beschädigen. Frage 2.2 Warum verwendet man gerne selbstjustierende Prozesse? Antwort 2.2 Bei selbstjustierenden Prozessen ist die Größe der Überlappungen nicht von Justierungstoleranzen abhängig sonder nur noch von der Unterdiffusion der Dotierung. Poly schützt vor Eindiffusion. Frage 2.3 Warum sind MOS-Prozesse im Prinzip günstiger für monolithische Integration als bipolare? Antwort 2.3 MOS-Transistoren müssen nicht aufwendig voneinander getrennt werden ⇒ weniger Prozeßschritte. Frage 2.4 Durch welche zusätzliche Maßnahme kann man aus einem CMOS-Prozeß einen BiCMOSProzeß machen? Antwort 2.4 Man benötigt eine zusätzliche Diffusion (Wanne). Frage 2.5 Diskutieren Sie die elektrische Leistungsaufnahme eines CMOS-Inverters im Vergleich zu Invertern mit Depletion-Lastelement! 5 2 Technologie Antwort 2.5 Bei einer logischen 1 am Eingang muß der NMOS mit Depletion-Lastelement ständig den Strom des Lastelements tragen. CMOS hingegen hat Last nur während der Umschaltevorgangs (mal abgesehen von parasitären Effekten). Frage 2.6 Wozu dient die Feldmaske? Antwort 2.6 Sie verhindert die Inversion von n-/p-Transistoren und sorgt für die Isolation zwischen n und p. Frage 2.7 Welche Strukturen blockieren eine Implantation? Antwort 2.7 SiO2 blockiert eine Implantation. Frage 2.8 Welche Verbesserungen waren im letzten Jahrzehnt nötig und wie haben sie die Prozeßtechnologie verändert? Antwort 2.8 • Widerstand des Gatematerials zu hoch ⇒ Metall auf Poly legen. • Transistoren ungenügend, Latch-Up-Empfindlichkeit zu hoch ⇒ Verwendung eines niederohmigen Substrats und einer hochohmigen Epi-Schicht zur Bekämpfung des Latch-Ups ⇒ Hintergrunddotierung besser einstellbar. • Feldstärke am Drain-Ende des Transistors zu hoch ⇒ Lightly Doped Drain • Vogelschnabeleffekt reduziert die Kanalweite des MOS-Transistors in schlecht kontrollierbarer Weise ⇒ Grabenätzung (Shallow Trench) zur Definition der Transistorgeometrie • Waferoberfläche wird hügelig durch Verdrahtungsebenen ⇒ Chemical Mechanical Planarization Frage 2.9 Was versteht man unter Shallow Trench, Lightly Doped Drain, Bird’s Beak und Oxide Encroachment? Antwort 2.9 Shallow Trench Gegenmaßnahme gegen Bird’s Beak, Grabenätzung zur Definierung der Transistorgeometrie. 6 2 Technologie Lightly Doped Drain Dotierung des Draingebietes um elektrische Felder gleichmäßiger zu verteilen, verhindert Druchbruch- und Heiße-Elektronen-Effekte. Bird’s Beak Oxidiertes Material braucht mehr Platz als das Ausgangsmaterial, verändert Kanalweiten in schlecht kontrollierbarer Weise. Oxide Encroachment Synonym für Bird’s Beak. Frage 2.10 Wie kommt der Latch-Up-Effekt zustande? Antwort 2.10 Parasitäre Bipolartransistoren bilden einen Thyristor, der – sofern er zündet – die Schaltung zerstören kann. Frage 2.11 Was ist als Entwicklungsergebnis an die Fertigung abzuliefern? Antwort 2.11 Die Maskengeometrie bzw. der vollständige Maskensatz (oder Netzliste, je nach Entwurfsstil). 2.2 Zusätzliche Fragen Frage 2.12 Beeinflußt die Unterdiffusion bei der Herstellung von Transistoren deren Weite? Antwort 2.12 Die Weite ist weitestgehend unabhängig von der Unterdiffusion. Frage 2.13 Warum hat Poly Metall als Gate-Material abgelöst? Antwort 2.13 Bei Poly besteht die Möglichkeit der Selbstjustage, Metall würde den hohen Temperaturen von Diffusionsprozessen nicht standhalten. Frage 2.14 Durch welchen Prozeßschritt wird der Einsatz von vielen (mehr als drei) Metalllagen ermöglicht? Antwort 2.14 Chemisch-mechanisches Planarisieren. Frage 2.15 Warum geht der Trend zu einer erhöhten Anzahl von Metalllagen? Antwort 2.15 • Kürzere Leitungslängen ⇒ höhere Schaltfrequenz. • Verdrahtung einfacher, platzsparender. • IC-Fläche reduziert sich. 7 3 Das Verhalten des MOS-Transistors 3 Das Verhalten des MOS-Transistors 3.1 Fragen aus dem Skript Frage 3.1 Kennlinien des MOS-Transistors zeichnen, Gebiete benennen, Kanalzustand beschreiben. Antwort 3.1 Grafik Frage 3.2 Was ist Inversion, wie kommt sie zustande? Antwort 3.2 An der Oberfläche des Siliziums versammeln sich – von der stark erhöhten Feldstärke angezogen – eine Schicht aus Minoritätsträgern, die dort durch ihre hohe Konzentration den Leitfähigkeitstyp umkehren. Frage 3.3 Warum kann man den Effekt der Akkumulation nicht für den Betrieb eines MOSFET verwenden? Antwort 3.3 Damit der Kanal leitend wird ist die Anwesenheit von Minoritätsträgern erforderlich, im Akkumulationsgebiet werden jedoch nur die Majoritätsträger angereichert. Frage 3.4 Welche aktiven Elemente gibt es in der CMOS-Technologie? Antwort 3.4 1. PMOS- und NMOS Enhancement-Transistoren, manchmal auch zusätzliche mit geänderter Schwellspannung (Depletion). 2. Vertikale Bipolartransistoren, die aus Source-/Drain-Diffusion als Emitter, Wanne als Basis und Substrat als Collector gebildet werden. 3. Parasitäre MOS- und Bipolartransistoren, Feldschwell-MOS-Transistoren und laterale Bipolartransistoren. Frage 3.5 Welche Maßnahmen trifft man gegen das Auftreten parasitärer Feldschwelltransistoren? Antwort 3.5 Implantation des Gebiets zwischen diffundierten Gebieten, dickes Feld-Oxid. Frage 3.6 Welche Effekte beeinflussen Länge und Weite des Transistors? Antwort 3.6 Weite Wird durch die Feldmaske bestimmt. Ungenauigkeiten entstehen durch 8 3 Das Verhalten des MOS-Transistors • Ätzung der Feldmaske (Nitrid) (±?) • Vogelschnabel (−∆W ) • Unterdiffusion Länge Wird durch die Polymaske bestimmt. Ungenauigkeiten entstehen durch • Ätzungenauigkeiten beim Gate-Poly (±?) • Unterdiffusion (−2Lov ) Frage 3.7 Wie verändert sich die Schwellspannung bei Verkürzung und Schmälerung von Transistoren? Antwort 3.7 Die Länge/Weite der Transistoren hat keinen Einfluß auf die Schwellspannung. Diese hängt ab von der Dotierung, der Oxidladung und der Oxiddicke. Frage 3.8 Was bestimmt die minimal zulässige Kanallänge? Antwort 3.8 Der Kurzkanaleffekt darf nicht auftreten, da sonst die Schwellspannung so niedrig wird, daß der Transistor nicht mehr abschalten kann. Frage 3.9 Was können heiße Ladungsträger bewirken? Antwort 3.9 Heiße Ladungsträger können in das Gate-Oxid hineintunneln und eine Verschiebung der Threshold-Spannung bewirken. Frage 3.10 Wie werden sie erzeugt? Antwort 3.10 Durch Feldstärken von über 104 V cm . Frage 3.11 Wovon ist die Beweglichkeit abhängig? Antwort 3.11 Von elektrischem Längs- und Querfeld sowie der Temperatur. Frage 3.12 Ist die Shichman-Hodges-Modellierung für Entwurfszwecke ausreichend? Wenn nein – welche wesentlichen Effekte moderner Transistoren berücksichtigt sie nicht? Antwort 3.12 Das Shichman-Hodges-Modell ist im Sperrbereich zu optimistisch, da es den unter dem MOS-Transistor liegenden Bipolartransistor nicht berücksichtigt. Dieser läßt immer einen Strom fließen (Sub-Threshold-Strom). 9 3 Das Verhalten des MOS-Transistors Frage 3.13 Wo stört der Weak-Inversion-Strom besonders? In welchen Szenarios wird er stärker? Antwort 3.13 Besonders störend wirkt er bei Verwendung des Transistors als Kondensator bei dynamischen Speicherelementen, sowie bei der Verwendung des Transistors als Schalter. Er wird stärker für kleinere Geometrien. Frage 3.14 Kann man äußere Signale direkt auf die Gates von CMOS-Schaltungen schalten? Wenn nein, wie geht man vor? Antwort 3.14 Nein, die Spannung muß erst durch entsprechende Treiber angepaßt werden, außerdem muß der IC gegen Injektion von Minoritätsträgern durch entsprechende Strukturen geschützt werden (Latch-Up-Gefahr). Frage 3.15 Welche Durchbruchmechanismen an MOS-Transistoren gibt es? Welche sind irreversibel? Antwort 3.15 • Durchbruch des Gateoxids (irreversible). • Punch-Through – Sperrschichtberührung Source-Drain (reversibel). • Lawinendurchbruch am Drain – heiße Ladungsträger, abhängig von Gate- und Drainspannung (reversibel). Frage 3.16 Welche Kapazitäten sind im Ersatzschaltbild eines MOS-Transistors zu berücksichtigen? Antwort 3.16 • Source-Bulk (spannungsabhängig) • Gate-Source-Overlap (abhängig von Weite und Länge) • Gate-Source (spannungsabhängig) • Gate-Bulk (spannungsabhängig) • Gate-Drain (spannungsabhängig) • Gate-Drain-Overlap (abhängig von Weite und Länge) • Drain-Bulk (spannungsabhängig) Frage 3.17 Warum sind Sperrschichtkapazitäten spannungsabhängig? Antwort 3.17 Weil die Sperrschichtweite eine Funktion der Spannung ist. 10 3 Das Verhalten des MOS-Transistors Frage 3.18 Nimmt die Kapazität mit steigender Spannung in Sperrschichtrichtung zu oder ab? Antwort 3.18 Die Kapazität nimmt zu. Frage 3.19 Ist die Sperrschichtkapazität in erster Linie von der Dotierungskonzentration auf der stark dotierten Seite abhängig? Antwort 3.19 Sie ist in erster Linie von der schwach dotierten Seite abhängig, da sich die Sperrschicht bevorzugt dorthin ausbreitet. Frage 3.20 Warum sind bei Source- und Draingebieten die Sperrschichtkapazitäten für Fläche und Umfang getrennt zu berechnen? Antwort 3.20 Weil sich die durch Implantation geschaffenen Dotierungsverhältnisse an der Oberfläche von denen nach unten unterscheiden können. Frage 3.21 Wie verhält sich die MOS-Kapazität in Abhängigkeit von der Spannung? Antwort 3.21 Anreicherung maximal Verarmung fallend schwache Inversion steigend Sättigung gleichbleibend linearer Bereich steigend Frage 3.22 Ist es richtig, daß für die Gate-Elektrode ein sehr schwach leitfähiges Halbleitermaterial verwendet werden muß, damit sich im Inneren eine Raumladungszone ausbreiten kann? Antwort 3.22 Nein, es kann z. B. Aluminium verwendet werden. Frage 3.23 Warum muß sich S und D etwas überlappen? Antwort 3.23 Damit trotz Fertigungstoleranzen ein Kanalgebiet sichergestellt ist. Frage 3.24 Was ist ein Substrat-Effekt? 11 3 Das Verhalten des MOS-Transistors Antwort 3.24 Erhöhung der Schwellspannung Ut durch eine Raumladung im Substrat. Frage 3.25 Wieso kann er stören? Antwort 3.25 Weil der Transistor nicht mehr schaltet, wenn die Schwellspannung zu hoch wird. Frage 3.26 Wieso braucht man überhaupt ein Substrat? Antwort 3.26 Das Substrat ist der Träger, auf dem die notwendigen Strukturen aufgebracht werden. Frage 3.27 Was passiert mit der Gate-Substrat-Kapazität des MOS-Transistors, wenn man vom gesperrten Zustand in den eingeschalteten (ohmschen) übergeht? Antwort 3.27 Sie verschwindet. 3.2 Zusätzliche Fragen Frage 3.28 Was ist der Hauptgrund dafür, daß das Shichman-Hodges-Modell deutlich höhere Ströme vorhersagt, als bei modernen MOS-Transistoren gemessen werden? Antwort 3.28 Die Ladungsträgerbeweglichkeit unterliegt einem Sättigungseffekt. µp und µn sinken bei hoher Feldstärke ⇒ weniger Strom fließt. Frage 3.29 Durch welche technologischen Maßnahmen wird die Entstehung von „heißen Elektronen“ reduziert? Antwort 3.29 Lightly Doped Drain, Reduktion der Feldstärken. Frage 3.30 Erklären Sie die Ursache der Steigung der Kennlinien des MOS-Transistors im Sättigungsbereich! Antwort 3.30 Kanallängenmodulation: Der Kanal schnürt ab, die effektive Kanallänge verkürzt sich, der Drainstrom steigt bei gleichbleibendem UtextGS und UDS an. Frage 3.31 Welche Leckeffekte treten bei ausgeschaltetem Transistor auf? Antwort 3.31 Diodenleckstrom, parasitäre Bipolartransistoren. 12 4 Elektrische Grundschaltungen CMOS Frage 3.32 Wie verändert sich die Overlap-Kapazität eines Transistors, wenn die 1. Länge 2. Weite des Transistors verdoppelt wird? Antwort 3.32 1. keine Veränderung 2. Verdopplung Frage 3.33 Warum ersetzen Digitalschaltungen, wenn möglich, Analogschaltungen? Nennen Sie zwei Gründe! Antwort 3.33 • Höhere Genauigkeit. • Niedrigerer Entwicklungsaufwand. • Niedrigeres Entwicklungsrisiko. • Analogschaltungen sind schlecht automatisch synthetisierbar. Frage 3.34 Woher kommen hauptsächlich die Ladungsträger eines MOSFETs, die den leitenden Kanal bilden (Betrieb im Sättigungsbereich)? Antwort 3.34 Aus dem Source-Gebiet (Größenordnungen höher als aus dem Substrat). 4 Elektrische Grundschaltungen CMOS 4.1 Fragen aus dem Skript Frage 4.1 Was ist Komplementärsymmetrie? Antwort 4.1 Bei CMOS-Schaltungen werden n- und p-MOS-Transistoren grundsätzlich paarweise verwendet. Entweder ist das n-Netz oder das p-Netz geschaltet. Frage 4.2 Warum ist es heute üblich CMOS und nicht die einfacherere NMOS-Technologie zu verwenden? Antwort 4.2 • Geringerer Leistungsverbrauch, kein statischer Querstrom. 13 4 Elektrische Grundschaltungen CMOS • Großer Störabstand (ca. 40% der Versorgungsspannung). • Hohe Unempfindlichkeit gegen Parameterstreuung, Pegel unabhängig vom Verhältnis Treibertransistor/Lasttransistor. Frage 4.3 Was ist Ratio-Less-Logic? Was genau sind Pullup- und Pulldown-Netzwerke? Antwort 4.3 Ratio-Less-Logic bedeutet, daß im statischen Zustand kein Strom fließt. Das Pullup-Netzwerk ist der Teil der CMOS-Schaltung, der den Pegel auf High zieht, das Pulldown-Netzwerk ist der Teil, der den Pegel auf Low zieht. Beide sind komplementärsymmetrisch zueinander. Frage 4.4 Ein komplementärsymmetrisches CMOS-Gatter hat vier Eingänge. Wieviel Transistoren enthält es mindestens? Begründung? Antwort 4.4 Mindestens acht Transistoren, da für jeden Eingang ein Transistor und dessen Komplement benötigt wird. Frage 4.5 Um CMOS zu layouten benötigt man mindestens eine Metallebene. Wieso reicht Poly und Diffusion nicht? Antwort 4.5 • Polysilizium wird vor Diffusion aufebracht (selbstjustierender Prozeß). • Diffusion kann nicht wannenübergreifend verbunden werden. • Kein Kontakt von Poly zu n+, p+ im Prozeß vorgesehen. Frage 4.6 Wie kann man die unterschiedliche Beweglichkeit (p- und n-Kanal) und die Parallelbzw. Serienschaltung von Transistoren ausgleichen? Beispiel 2-Input-NOR-Gatter, 3Input-NAND-Gatter? Was ist bei Serienschaltungen von Transistoren zu beachten? Antwort 4.6 Das Transistornetzwerk wird durch Widerstände, Kapazitäten und ideale Schalter modelliert. Gleiche Schaltzeiten haben p- und n-Kanal-Transistoren, wenn ihre Weiten folgender Formel folgen: µp Wn = Wp µn Frage 4.7 Was ist ein Komplexgatter? Bildungsgesetz? Praktische Grenzen? 14 4 Elektrische Grundschaltungen CMOS Antwort 4.7 Abbildung logischer Funktionen auf eine geeignete Verschaltung von Transistoren. OR wird im Pulldown-Netz durch Parallelschaltung verwirklicht, im Pullup-Netz durch Serienschaltung, AND wird im Pulldown-Netz durch Serienschaltung, im Pullup-Netz durch Parallelschaltung umgesetzt. Der Ausgang ist invertiert. Die praktische Grenze liegt bei etwa fünf Eingängen. Frage 4.8 Warum kann ein CMOS-Transfergatter eine Spannung (statisch) fehlerfrei übertragen, ein einzelner NMOS-Transistor dagegen nur eingeschränkt? In welchem Bereich reicht ein NMOS-Transistor, in welchem ein PMOS-Transistor? Antwort 4.8 PMOS-Transistoren übertragen niedrige Spannungen schlecht, während NMOS-Transistoren hohe Spannungen schlecht übertragen (für UGS < Ut ). Frage 4.9 Was tut man, wenn ein Treiber zu langsam ist? Was ist schlecht daran, wenn er zu schnell ist? Antwort 4.9 Man vergrößert die Weite des Treibers. Wenn er zu schnell ist sind möglicherweise andere Schaltungsteile nicht schnell genug um noch mit ihm zusammenzuarbeiten. Frage 4.10 Was tut man, wenn eine große kapazitive Last zu treiben ist (z. B. Endstufentransistor)? Antwort 4.10 Man steuert die Last mit einer Kette von Treibern steigender Weite an. Frage 4.11 Was ist zu tun, wenn eine gegebene Logikschaltung so zu realisieren ist, daß die elektrische Leistungsaufnahme im Betrieb minimal wird? Antwort 4.11 • Versorgungsspannung minimal halten. • Bitwechselrate reduzieren. • Kapazität reduzieren ⇒ Transistoren weiter machen. Frage 4.12 Wie mache ich aus dem Exor auf S. 116 ein Exnor? Antwort 4.12 Ersetze alle PMOS-Transistoren durch NMOS und alle NMOS-Transistoren durch PMOS. Frage 4.13 Warum benutzt man in synchronen Schaltwerken Master-Slave-FFs und keine einfachen Latches? 15 4 Elektrische Grundschaltungen CMOS Antwort 4.13 Weil Master-Slave-FFs taktgesteuert sind, Latches zustandsgesteuert. Frage 4.14 Zeichnen Sie ein D-Latch, das für ein Steuersignal mit H-Level transparent wird! Antwort 4.14 Zeichnung Frage 4.15 Wie genau funktioniert ein D-Latch, wie ein RS-Latch? Antwort 4.15 D-Latch C auf H ⇒ D liegt an Q an, C auf L ⇒ Wert, der zuletzt an D anlag als C auf H war liegt an Q an. RS-Latch Wie D-Latch, jedoch zusätzlich mit asynchronem Set/Reset. Frage 4.16 Was ist bei Benutzung asynchroner Set- bzw. Reset-Funktion zu beachten? Antwort 4.16 Sie dürfen nur zur Herstellung eines Anfangszustandes verwendet werden. Frage 4.17 Was ist eine Setup-, was eine Hold-Zeit? Antwort 4.17 Setup-Zeit Diejenige Zeitspanne, die der Eingang stabil sein muß bevor die Taktflanke schaltet. Hold-Zeit Diejenige Zeitspanne, die der Eingang stabil sein muß nachdem die Taktflanke geschaltet hat. Frage 4.18 Was ist Metastabilität? Antwort 4.18 Metastabilität bezeichnet einen schwach stabilen Zustand, der zu vermeiden ist, da unklar ist wie lange es dauert, bis er in einen stabilen Zustand übergeht. Frage 4.19 Warum ist das Zeitverhalten eines Taktverteilungssystems wichtig? Antwort 4.19 Damit alle vom Takt abhängigen Komponenten den gleichen Takt zum gleichen Zeitpunkt erhalten. Frage 4.20 Was bedeutet Clock Skew? 16 4 Elektrische Grundschaltungen CMOS Antwort 4.20 Clock Skew bezeichnet den maximalen Taktversatz durch das Taktverteilungssystem. Frage 4.21 Was ist beim dynamischen Speicher „dynamisch“? Antwort 4.21 Der verwendete Kondensator entlädt sich mit der Zeit und muß wieder aufgeladen werden. Außerdem wirkt das Auslesen des Speichers destruktiv auf den Inhalt. Frage 4.22 Erläutern Sie die Funktion der Bit- und Wortleitung bei einem Speicherblock! Antwort 4.22 Reihenadressierung wählt genau eine Wortleitung aus. Durch Spaltenadressierung wählt man genau ein Bitleitungspaar aus, über das die gewählte Zelle gelesen und geschrieben wird. Frage 4.23 Wie funktioniert ein 1. SRAM 2. DRAM 3. EEPROM Antwort 4.23 1. SRAM: Flip-Flop 2. DRAM: Kondensator 3. EEPROM: Fester Inhalt gegeben durch Aufbau oder strukturelle Veränderungen. Frage 4.24 Wie funktioniert speziell das Schreiben, Lesen, der Speichermechanismus? Antwort 4.24 SRAM Einschreiben durch Takt und Eingang, lesen am Ausgang. DRAM Einschreiben durch Anlegen einer Spannung und Trennen vom Eingang. Lesen durch Messen der gespeicherten Ladung, anschließend Wiedereinschreiben erforderlich. Wiederauffrischen des Speicherinhalts in regelmäßigen Abständen. EEPROM Einschreiben durch Strukturveränderung (Verpuffen von Transistorgates, Verschieben der Schwellspannung etc.). Auslesen direkt am Ausgang. Frage 4.25 Warum braucht man beim DRAM einen Refresh? 17 4 Elektrische Grundschaltungen CMOS Antwort 4.25 Weil der Kondensator sich durch Leckströme entlädt. Frage 4.26 Was ist ein flüchtiger Speicher? Antwort 4.26 Ein Speicher, der seinen Inhalt ohne Refresh verlieren würde. Frage 4.27 Wie entwirft man ein ROM? Wie legt man seinen Inhalt fest? Antwort 4.27 Der Inhalt wird während der Herstellung festgelegt (bei EPROM später durch Veränderung der Struktur). Der Inhalt kann auf Ebene der Feldmaske, der Kontaktmaske oder durch Implantation festgelegt werden. 4.2 Zusätzliche Fragen Frage 4.28 Welche Probleme treten beim Entwurf von Komplexgattern auf? Geben Sie Verbesserungsvorschläge an! Antwort 4.28 Zu viele Eingänge, zu viele gekoppelte Transistoren, zu langsam. ⇒ PMOS-Last, Precharge/Keeper, mehrstufige Realisierung. Frage 4.29 Weshalb wird kapazitives Übersprechen zwischen Leitungen bei jeder Technologieverkleinerung immer bedeutender? Antwort 4.29 Die kapazitives Kopplung zueinander steigt an, da Weite und Abstand der Leiterbahnen geringer werden, die Dicke aber nicht (wegen Leitungswiderstand). Frage 4.30 Was sind die Folgen des Übersprechens? Nennen Sie Maßnahmen dagegen! Antwort 4.30 Pegeländerung auf benachbarten Leitungen kann Störung/Verzögerung erzeugen. Gegenmaßnahmen: • Leitungen nicht über große Distanz parallel führen. • Auf Anordnung beim Verlegen achten, z. B. Signal-Versorgung-Signal-Versorgung, ... • Abschirmung, Zweidrahtleitungen, Symmetrierung. 18 5 Elektrische Probleme des Entwurfs 5 Elektrische Probleme des Entwurfs Frage 5.1 Welche Gesichtspunkte muß man bei der Dimensionierung von Ausgangstreibern beachten? Antwort 5.1 Es darf nicht zum Latch-Up durch zu hohe externe Lasten kommen. Frage 5.2 Was ist Alpha-Ratio? Was ist Beta-Ratio? Was ist Ratio-Less-Logic? Antwort 5.2 Alpha-Ratio beschreibt das Verhältnis einer Kaskade. Ratio-Less-Logic bedeutet, daß im statischen Zustand kein Strom fließt. Frage 5.3 Wie führt man Energieversorgungsleitungen auf einem Chip? Antwort 5.3 • Versorgungsleitungen für Inneres und Peripherie trennen. • Analogschaltungen separat versorgen. • Keine rechten Winkel wegen Elektromigration. Leitungen schlitzen, 45◦ -Winkel verwenden. Frage 5.4 Was ist bei der Taktversorgung zu beachten? Wie gestaltet man sie? Antwort 5.4 Der Takt muß alle an ihn angebundene Elemente gleichzeitig erreichen ⇒ Clock Skew minimieren. Übersprechen und ungleichmäßige Belastung können das Clock-Signal verzerren ⇒ Clock-Tree, Clock-Grid, H-Tree. Frage 5.5 Wie kommen elektrostatische Beschädigungen zustande? Wie schützt man ICs dagegen? Antwort 5.5 Beschädigungen kommen durch Aufladung des Chips, des Moduls oder eines Menschen und anschließende Entladung zustande. Schutz ist möglich durch Vermeidung der Aufladung (leitfähige Beläge, Luftbefeuchtung), sowie entsprechende Schutzstrukturen auf dem Chip. Frage 5.6 Welcher Schutz ist auf dem IC selbst möglich? Antwort 5.6 1. Eingänge Widerstand/Kapazität/Diode, Ableitung der Überspannung über Udd . Ausgänge Transistoren genügend weit auslegen, Treiberkaskaden. 19 5 Elektrische Probleme des Entwurfs 2. Teile, die hohe Spannungen/Strom führen genügend weit auslegen, viele Kontakte vorsehen, Abschrägung, große Überlappungen. Frage 5.7 Welche ESD-Modelle gibt es? In welchen Szenarios werden sie angewandt? Antwort 5.7 • Human Body Model • Machine Model • Charged Device Model Frage 5.8 Warum sind Stromversorgungen für Ausgangstreiber kritisch? Antwort 5.8 Weil die Last, die die Ausgangstreiber umladen müssen sehr groß ist. Frage 5.9 Warum versorgt man Analogschaltungen meist durch separate Anschlüsse? Antwort 5.9 Weil digitale Schaltungen getaktet schalten und sehr starke Störungen auf der Stromversorgung erzeugen. Frage 5.10 Was ist „Slow-Wave“-Wellenausbreitung? Antwort 5.10 Bei hochohmigem Substrat kommt es durch die erhöhte Induktivität zu höherer Eindringtiefe und damit langsamerer Wellenausbreitung ⇒ erhöhte Verluste. Frage 5.11 Was ist der Unterschied zwischen Constant Voltage- und Constant-Field-Scaling? Antwort 5.11 Constant Voltage Scaling • Versorgungsspannung kann beibehalten werden. • Probleme mit Feldstärken, nicht geeignet für Submikrometerbereich. • Elektrisches Verhalten der Transistoren verbessert sich ⇒ schnelleres Schalten. • Verlustleistungsdichte erhöht sich schnell. Constant Field Scaling • Alle horizontalen und vertikalen Dimensionen werden um den Skalierungsfaktor S1 verkleinert. • Die Versorgungsspannung wird um 1 S verkleinert. • Die Gatekapazität pro Flächeneinheit erhöht sich um S. 20 5 Elektrische Probleme des Entwurfs • Der Strom durch den MOS-Transistor reduziert sich um 1 S. • Die Kapazität des Transistorgates reduziert sich um • Die Verlustleistung des Transistors reduziert sich um 1 S. 1 . S2 • Die Substratdotierung wird vergrößert, die Sperrschichtweite reduziert sich um S1 . • Die Flächenkapazität der Verdrahtung reduziert sich um den Faktor S1 , die Randkapazität um S1 . • Die Verzögerungszeiten aktiver Stufen bleiben konstant. • Die Verzögerungszeit von Leitungen kann sich erhöhen, da sich ihr Widerstand um S erhöht. Frage 5.12 Was ist Latch-Up? Wie schützt man sich beim Einsatz von ICs dagegen? Antwort 5.12 Latch-Up bezeichnet das Zünden eines parasitären Thyristors. Beim IC-Entwurf sollte folgendes beachtet werden: Niedrige Bahnwiderstände, ausreichende Anbindung von Wannen und Substrat, Minoritätsträger durch Guard-Bars absaugen, hohe Lasten vermeiden, Strominjektionen vermeiden, Stromversorgungen, Takt und Signal in der richtigen Reihenfolge einschalten. Der Abstand zwischen Wanne und gleichartiger Diffusion sollte eingehalten werden. Der Substratwiderstand sollte niedrig gehalten werden und es sollte eine isolierende Epi-Schicht aufgebracht werden. Direkte Nachbarschaft von n- und p-MOS-Transistoren sollte bei benachbarten Treibern vermieden werden. Frage 5.13 Was muß der IC-Entwickler gegen Latch-Up tun? Antwort 5.13 Siehe vorhergehende Frage. Frage 5.14 Wie modelliert man Leitungen? Antwort 5.14 Mit Hilfe infinitesimal kleiner Vierpole. Frage 5.15 Wann kann man den induktiven Leitungsbelag vernachlässigen? Antwort 5.15 Wenn die Leitungslänge L < 1 10 λ ist. Frage 5.16 Wie hängt die Leitungsverzögerung von der Länge ab? 21 5 Elektrische Probleme des Entwurfs Antwort 5.16 R·C · L2 2 Td (L) = Frage 5.17 Was ist zu beachten um Leitungsverzögerungen auf dem IC klein zu halten? Antwort 5.17 • Leitungslängen kurz halten. • Mehr Verdrahtungsebenen einsetzen. • Treiberstärken erhöhen (W erhöhen). • Einsatz von Verstärkern. • Reduzierung von Spannungshüben. • Verwendung von Dielektrika niedriger Dielektrizitätskonstante. Frage 5.18 Was ist ein Ringoszillator? Funktion? Wovon hängt die Frequenz ab? Antwort 5.18 Eine ungerade Anzahl von Invertern wird als Ring geschaltet. Die Frequenz ist abhängig von Prozeßparametern, der Versorgungsspannung und der Temperatur. Der Ringoszillator wird als Voltage Controlled Oscillator verwendet um den Systemtakt zu erzeugen, aber auch als Teststruktur um Rückschlüsse auf die Produktionsparameter zu ermöglichen. Frage 5.19 Wie kann man beim Layout von Leitungen das Übersprechen reduzieren? Antwort 5.19 Vermeidung paralleler Führung über große Längen. Symmetrische Leitungen. Systematische Permutation der Leitungslage. Frage 5.20 Wie verhalten sich Verbindungsleitungen zwischen Chips? Antwort 5.20 Gemäß der Telegraphengleichung ohne Widerstand und Leitwert. Frage 5.21 Warum verhalten sie sich anders als Verbindungsleitungen auf dem Chip? Antwort 5.21 Sie sind länger als den. 1 10 λ, der induktive Leitungsbelag kann also nicht vernachlässigt wer- 22 6 Layout Frage 5.22 Wie kann man einen schnellen Takt auf einem Chip generieren und wie kann man ihn mit einem externen Referenztakt synchronisieren? Antwort 5.22 Man erzeugt einen externen Referenztakt im Bereich von einigen MHz und benutzt eine Phase Locked Loop im auf dem Chip einen Vielfaches dieses Taktes zu erzeugen. 6 Layout Frage 6.1 Wie funktioniert ein Maze Runner? Antwort 6.1 Für alle Felder, die bereits markiert sind: Markiere alle benachbarten Felder mit dem nächhöheren Zähler, sofern dieses Feld noch nicht markiert oder blockiert ist. Wiederhole bis das Zielfeld markiert ist. Dann: Rückverfolgung. Frage 6.2 Was für grundlegende geometrische Entwurfsregeln gibt es? Antwort 6.2 1. Durch den Herstellungsprozeß begründete Regeln a) Abstand und Weite i. Photolithographie (Streulicht) ii. Ätzung (isotrope Ätzung) iii. Metallisierung (Spiegelung durch Aluminium) iv. Diffusion (findet auch zu den Seiten hin statt) b) Überlappungsregeln Kommen zustande durch Toleranz der Kantendefinition und Justage. 2. Durch elektrische und physikalische Randbedingungen begründete Regeln (Metal Migration). 3. Durch Latch-Up-Vermeidung begründete Regeln (Wanne und Substrat in gewissen Abspänden anschließen . . . ) Frage 6.3 Was ist das Grundprinzip eines Standardzellenlayouts? Antwort 6.3 Vorgegebene Zellen gleicher Höhe werden in Zeilen angeordnet. Das Layout kann automatisch anhand der Netzliste erzeugt werden. Frage 6.4 Welche Schritte (und welche Algorithmen) verwendet man für die automatische Layoutgenerierung von Standardzellen oder Sea-of-Gates-Entwürfe? 23 6 Layout Antwort 6.4 1. Floor Planning: a) Schätzen der Blockfläche i. Berechnung der Nettozellfläche. ii. Schätzung der Verdrahtungsfläche (Zahl der Netze, Zahl der Anschlüsse). iii. Summe b) Festlegen des Breiten-Höhen-Verhältnisses oder einer bestimmten Gestalt. c) Festlegen der Position der Anschlüsse nach außen. d) Partitionieren der Menge der Zellen in Reihen, Gebiete oder Spalten (Anlagerungsverfahren, Kernighan-Lin, Simulated Annealing). e) Platzieren mit dem Ziel kürzester bzw. flächenminimaler Verdrahtung und Randbedingungen: i. kritische Laufzeitpfade ii. Kopplungen iii. Testbarkeit Platzieren basiert auf Partitionierungsverfahren. Verdrahtung evt. in Kanälen (Channel Router, Feed Through). Heute sind im Allgemeinen mehr als zwei Verdrahtungsebenen verfügbar, das Problem ist dann nicht mehr Channel Router sondern 3D-Switchbox. Frage 6.5 Für welche Anwendungen verwendet man noch immer Handlayout? Warum? Antwort 6.5 Für alle Fälle, in denen in hohem Maße optimiert werden muß, da es für die auftretenden Probleme keine allgemeingültigen optimalen Lösungen gibt. Ein gut ausgebildeter Mensch bringt in der Regel bessere Ergebnisse als ein automatisiertes Verfahren. Frage 6.6 Was ist eine Standardzelle? Was ist dabei standardisiert? Antwort 6.6 Standardzellen sind Layoutelemente gleicher Höhe, die in Zeilen angeordnet werden. Standardisiert ist lediglich die Höhe der Zellen. Die Anordnung kann automatisch auf Basis der Netzliste erfolgen. Frage 6.7 Was versteht man unter IP? Antwort 6.7 Urheber- und Verwertungsrechte. In Zusammenhang mit Schaltungsentwurf Entwürfe von Teilschaltungen, die man von entsprechenden Firmen lizensieren kann. 24 6 Layout Frage 6.8 Warum ist die Wiederverwertung von einmal bewährten Entwürfen schwierig? Was kann man überhaupt wiederverwerten. Antwort 6.8 Die Wiederverwertung ist schwierig, da für die nächste Prozeßgeneration Parameter unterschiedlich skaliert werden. Deswegen können einmal entworfene Schaltungen nur sehr grob wiederverwendet werden und müssen in weiten Teilen auf die neue Technologie angepaßt werden. Frage 6.9 Kann man einen Analogblock in einen Standard-Logik-IC einbauen? Unter welchen Voraussetzungen? Antwort 6.9 Analogschaltungen werden für gewöhnlich in der Ecke des ICs platziert, da sie eine separate Stromversorgung benötigen und entkoppelt werden müssen. Frage 6.10 Wie zeichnet man einen MOS-Transistor im Handlayout? Antwort 6.10 Kreuzung von Aktiv und Poly. Frage 6.11 Wie erkennt ein Layout vs. Schematic-Programm einen MOS-Transistor? Einen Widerstand? Antwort 6.11 Transistor Verundung von Poly- und Aktivmaske. Widerstand Muß auf einer separaten Hilfsebene markiert werden. Frage 6.12 Kann man in eine n-Wanne einen n-Kanal-Transistor zeichnen? Was passiert, wenn man es tut? Antwort 6.12 Das Programm wird bemängeln, daß die Überlappung von Aktiv und Poly nicht eingehalten wurde. Frage 6.13 Was versteht man unter „Simulated Annealing“? Antwort 6.13 „Aufrütteln“ des Zwischenergebnisses mit dem Ziel ein lokales Minimum der Kostenfunktion zu verlassen. Frage 6.14 Was ist im Layout zu beachten um Latch-Up zu vermeiden? 25 6 Layout Antwort 6.14 Wanne und Substrat müssen an die Stromversorgung angeschlossen werden, laterale Bipolartransistoren müssen durch zusätzliche Abstände entschärft werden, Injektion von Minoritätsträgern muß durch Schutzringe verhindert werden. Frage 6.15 Welches sind die wesentlichen Layout-Verifikationsverfahren? Antwort 6.15 Geometrischer Design Rule Check Stellt sicher daß Abstand, Weite und Überlappungen eingehalten wurden. Electrical Rules Check Findet floatende Strukturen, offensichtlich falsche Anschlüsse von Transistoren. Meist nur auf Digitalschaltungen anwendbar. Electrical Parameter Check Prüft ob alle elektrischen Dimensionierungsgrundsätze eingehalten wurden. Network Consistency Check auch Layout vs. Schematic Check. Vergleicht aus dem Layout rekonstruierte Netzliste mit ursprünglicher Vorgabe. Frage 6.16 Was heißt eigentlich Verifikation? Antwort 6.16 Prüfen ob der Entwurf den Vorgaben entspricht und so funktionieren kann. Frage 6.17 Was ist ein Design Rule Check? Antwort 6.17 Prüfen ob die (geometrischen) Entwurfsregeln eingehalten wurden. Frage 6.18 Wozu benötigt man Layout Parameter Extraction? Antwort 6.18 Um festzustellen welche parasitären Elemente wirken. Frage 6.19 Wozu wird man kritische Schaltungen nach der LPE noch einmal simulieren? Antwort 6.19 Um sicherzustellen, daß sie auch in Anwesenheit parasitärer Elemente noch funktionieren. 26 7 Schaltungssimulation Tabelle 1: Beispiele für ideale und reale Bauelemente Antwort 7.2 Symbol Reales Bauelement Ideales Element R Widerstand (resistor) Widerstand (resistance) C Kondensator (capacitor) Kapazität (capacitance) G Transistor (Anlaufgebiet, Sättigungsgebiet) L Spule (inductor) U Batterie I Transistor (Sättigungsgebiet) Stromquelle (current source) M Transformator (transformer) Gegeninduktivität (mutual inductance) Leitwert (conductance) Induktivität (inductance) Spannungsquelle (voltage source) 7 Schaltungssimulation 7.1 Fragen aus dem Skript Frage 7.1 Wozu dient Schaltungssimulation? Antwort 7.1 Entwurfsunterstützung Design Centering Zentrierung des Entwurfs bezüglich der Technologieparameter mit dem Ziel die Ausbeute zu maximieren. Entwurfsverifikation Fertigungstests Feststellen des voraussichtlichen Verhaltens bei definierten Erregungen in Abhängigkeit von Betriebs- und Herstellungsparametern. Frage 7.2 Nennen Sie ein Beispiel für ein ideales und ein reales Bauelement! Siehe Tabelle 1 Frage 7.3 Was ist der Unterschied zwischen einem Großsignalmodell und einem Kleinsignalmodell? 27 7 Schaltungssimulation Antwort 7.3 Das Kleinsignalmodell ist ein vereinfachtes Modell, das nur im Arbeitspunkt gilt. Das Großsignalmodell ist eine allgemeinere Beschreibung. Frage 7.4 Wie wird eine Wechselstrom-Kleinsignalanalyse durchgeführt? Antwort 7.4 Linearisierung im Arbeitspunkt, Analyse im Frequenzbereich. Frage 7.5 Worin besteht der Unterschied zwischen Knotenspannungsanalyse und modifizierter Knotenspannungsanalyse? Antwort 7.5 Die modifizierte Knotenspannungsanalyse ermöglicht die Verwendung idealer Spannungsquellen. Es werden zusätzliche Zeilen und Spalten eingeführt. Frage 7.6 Welche Eigenschaften haben die einfachsten Verfahren der numerischen Integration? Antwort 7.6 Vorwärts-Euler kleiner Stabilitätsbereich, großer Fehler. Rückwärts-Euler großer Stabilitätsbereich, großer Fehler. Trapez stabil, kleiner Fehler. Frage 7.7 Wie genau läuft die Transientenanalyse ab? Antwort 7.7 1. DC-Analyse 2. Setze Schrittweite in Differenzengleichung ein 3. Ersetze Nichtlinearitäten 4. Löse lineares Gleichungssystem, weiter bei 3 5. Speichere Ergebnisse (Zeitschrittsteuerung, dann weiter bei 2) Zeitschrittsteuerung: Weiter bei 2 oder Ende. Frage 7.8 Welche Arten von Differentialgleichungen beschreiben elektrische Schaltungen? Antwort 7.8 Gewöhnliche Differentialgleichungen erster Ordnung. 28 7 Schaltungssimulation 7.2 Zusätzliche Fragen Frage 7.9 Geben Sie für die folgenden Fälle jeweils geeignete Analysearten für eine Simulation an: 1. Übertragungskennlinie eines Inverters 2. Kleinsignalphasengang eines Operationsverstärkers 3. Einschwingverhalten einer Schaltung 4. Transistor-Kennlinienfeld Antwort 7.9 1. DC-Sweep 2. AC-Analyse 3. Transientenanalyse 4. DC-Sweep Frage 7.10 Wie kann die Setup-Zeit eines Flip-Flops simulativ ermittelt werden? Antwort 7.10 Wechsel des Eingangssignals immer näher an den Taktzeitpunkt schieben, Signalverzögerung zum Ausgang beobachten. Ist diese Zeit um 5% angestiegen, so ist dieser zeitliche Abstand die Setup-Zeit. Frage 7.11 Was versteht man unter dem Modell eines Bauelements? Antwort 7.11 Die mathematische Beschreibung des Verhaltens des realen Bauelements im interessierenden Bereich zur Nutzung für die Schaltungssimulation. Frage 7.12 Welche Analysearten kennen Sie? Wofür setzt man sie ein? Antwort 7.12 DC-Analyse Gleichspannungs-/Gleichstromübertragungsverhalten. Arbeitspunktanalyse Grundlage anderer Analysearten. DC-Sweep Eingangs-Ausgangs-Übertragungskennlinie z. B. eines Verstärkers, Darstellung der Kennlinien eines Bauelements. AC-Analyse Berechnung des Kleinsignalübertragungsverhaltens im Frequenzbereich. 29 8 Aufbau- und Montagetechnik Pol-Nullstellen-Analyse Unterstützt die Entwurfsentscheidung anknüpfend an analytische Verfahren. Rauschanalyse Analyse des Rauschverhaltens der beteiligten Bauteile. Transientenanalyse Schaltverhalten eines Gatters, Einschwingverhalten von Analogschaltungen. 8 Aufbau- und Montagetechnik 8.1 Fragen aus dem Skript Frage 8.1 Schildern Sie den Ablauf einer Fertigung! Antwort 8.1 Spezifikation → Design → Masken → Produktion → Parameter-Messung → Test → Gehäusen → Versand Frage 8.2 Wie kann man Chips vereinzeln? Antwort 8.2 Durch Schleifen. Frage 8.3 Was sind die Aufgaben des Wafersorts? Des finalen Tests? Antwort 8.3 Wafersort Markieren defkter schadhafter Chips, aussortieren. Finaler Test Aussortieren einzlener Chips, die während der Montage Schaden genommen haben. Frage 8.4 Was versteht man unter Parametertest? Antwort 8.4 Der Parametertest mißt bestimmte Parameter anhand von Teststrukturen um zu entscheiden ob das Los lieferwürdig ist. Frage 8.5 Welche Arten des Bondens gibt es? Wozu dient der Bond-Pull-Test? Antwort 8.5 • Thermisches Bonden • Ultraschallbonden 30 8 Aufbau- und Montagetechnik • Thermosonic-Bonden Der Bond-Pull-Test dient dazu destruktiv oder nichtdestruktiv die Zugfestigkeit der Bondung zu prüfen. Fehlermechanismen: Querschnittsverringerung der Bonddrahtes, Padfläche nicht sauber, Padfläche zerstört. Frage 8.6 Was versteht man unter DIE-Bond? Welche Techniken gibt es? Antwort 8.6 Bei der Montage der Chips die Kontaktierung. Es gibt Pins am Rand, die durchgesteckt werden, Pins über Fläche verteilt, Oberflächenmontage bedrahtet oder unbedrahtet, Flip Chip und Tape Automated Bonding. Frage 8.7 Welche Gehäusearten gibt es? Antwort 8.7 Einsteckmontage und Oberflächenmontage. Frage 8.8 Welche gehäuselosen Montagearten gibt es? Antwort 8.8 • Leiterplatten auf Epoxidharz-Basis • Flexible Leiterplatten • Dickschichtschaltungen auf Kermiksubstrat Frage 8.9 Was versteht man unter „Wärmewiderstand“? Antwort 8.9 Widerstand, den ein Objekt der Ausbreitung von Wärme durch seinen Körper entgegensetzt. Kehrwert der Wärmeleitfähigkeit. Frage 8.10 Wann sind Lebensdauerversuche im Zeitraffer möglich? Arrheniusgesezt? Antwort 8.10 Wenn einem Ausfallsereignis eine Aktivierungsenergie zugeordnet werden kann. Das Arrhenius-Gesetz beschreibt den Zusammenhang zwischen Temperatur und chemischer Reaktionsgeschwindigkeit. Frage 8.11 Was sind die zu erfüllenden Bedingungen, damit ein Waferlos an den Kunden einer Halbleiterfabrik geliefert werden kann? Antwort 8.11 Ein vereinbarter Anteil an Wafern muß die designunabhängigen Parametertoleranzen eingehalten haben. 31 8 Aufbau- und Montagetechnik Frage 8.12 Was ist ein Sägerahmen? Antwort 8.12 Ein Teil der Waferoberfläche, der zum Vereinzeln herausgeschliffen wird, enthält oft Teststrukturen. Frage 8.13 Was versteht man unter „Known Good Dice“? Antwort 8.13 Chips, die so vollständig ausgetestet sind, daß bei einem Einbau in Hybride oder MultichipCarrier keine Ausfälle zu befürchten sind. Frage 8.14 Sind Plastikgehäuse hermetisch dicht? Antwort 8.14 Nein, sie sind wasserdurchlässig. Frage 8.15 Wie stellt die IC-Entwicklung sicher, daß ein neuer Chip in ein Gehäuse passt? Antwort 8.15 Man entwickelt „von außen nach innen“. Frage 8.16 Was ist MCM? Antwort 8.16 Auf einem Träger werden bis zu 100 Chips montiert. Der Träger enthält zusätzlich noch Pads für den Anschluß nach außen. Der Träger kann aus Keramik, Silizium oder Polymer bestehen. Frage 8.17 was ist ein Ball-Grid-Array? Antwort 8.17 Auf der Unterseite eines Chips werden Kügelchen aus Lötzinn zur Kontaktierung angebracht. Diese werden im Ofen geschmolzen. Frage 8.18 Was ist TAB? Antwort 8.18 Tape Automated Bonding. Auf dem Chip sind Buckel aus Lötzinn angebracht, die alle gleichzeit kontaktiert werden. Frage 8.19 Warum führt man einen Burn-In durch? Antwort 8.19 Um diejenigen Chips auszusortieren, die ohnehin innerhalb kurzer Zeit ausfallen würden. 32 Literatur 8.2 Zusätzliche Fragen Frage 8.20 Nennen Sie drei Prüfverfahren um eine Drahtverbindung zwischen einem IC und dem Gehäuse zu testen! Antwort 8.20 • Bond-Pull • Abschertest • Wiederholte elektrische Belastung im Testautomat • Röntgenuntersuchung Literatur [1] Anantha Chandrakasan, Jan M. R.: Digital Integrated Circuits. New Jersey : Prentice Hall, 2003. – ISBN 0–1312–0764–4 [2] Glauert, Wolfram H.: Entwurf Integrierter Schaltungen I. Erlangen : Vorlesungsskript zur gleichnamigen Veranstaltung, 2006 33 Index A Burn-In, 32 Abnahmetest, 4 AC-Analyse, 29 Ätzung, 3, 9 Akkumulation, 8 Aktivierungsenergie, 31 Alpha-Ratio, 19 Aluminium, 11 Analogschaltung, 13, 19, 25 Arbeitspunkt, 28 Linearisierung, 28 Arrheniusgesetz, 31 ASIC, 2 ASSP, 2 Ausbeute, 4 von Chips auf einem Wafer, 4 Ausbeuteformel Moore, 4 C Charged Device Model, 20 Chemical Mechanical Planarization, 6 Chemisch-mechanisches Planarisieren, 7 Clock Skew, 16 CMOS, 5, 10, 13 aktive Elemente, 8 Collector, 8 Constant Field Scaling, 20 Constant Voltage Scaling, 20 D DC-Analyse, 28 DC-Sweep, 29 Defekt, 4 punktförmiger, 4 Defektdichte, 4 Depletion, 8 Design Centering, 27 Dickschichtschaltung, 3 DIE-Bond, 31 Differentialgleichung, 28 gewöhnliche, 28 Diffusion, 5, 7, 14 Drain, 8 Source, 8 Digitalschaltung, 13 Diodenleckstrom, 12 Doppeltransistor, 3 Dotierung, 9 Konzentration, 11 DRAM, 17 DRC, 26 Dünnschichtschaltung, 3 Durchbruch, 10 des Gateoxids, 10 Lawinen-, 10 Sperrschicht, 10 B Ball-Grid-Array, 32 Basis, 8 Batterie, 27 Bauelement ideales, 27 Modell, 29 reales, 27 Beweglichkeit, 9, 12, 14 BiCMOS, 5 Bipolartransistor, 3 lateraler, 8 parasitärer, 5, 7, 8, 12 vertikaler, 5, 8 Bird’s Beak, 6, 7 Bitleitung, 17 Bond-Pull-Test, 31 Bonden thermisch, 30 thermosonic, 31 Ultraschall, 30 34 Index E Widerstand, 6 Gate Array, 2, 3 Gate-Material, 7 Gegeninduktivität, 27 Gehäuse, 31 geometrisch mögliche Chips, 4 Glasplatte, 3 Großsignalmodell, 27 EEPROM, 17 Elektronen heiße, 12 Emitter, 8 Entwicklungsergebnis, 7 Entwurf kundenspezifischer, 2 Entwurfsregeln geometrische, 23 Entwurfsstil, 2 Entwurfsunterstützung, 27 Entwurfsverifikation, 27 EPC, 26 Epi-Schicht hochohmige, 6 ERC, 26 ESD, 19 Modell, 20 Schutz, 19 Euler Rückwärts, 28 Vorwärts, 28 H Handlayout, 24 Hardwarebeschreibungssprache, 3 Hilfsebene, 25 Hold-Zeit, 16 Human Body Model, 20 I Implantation, 8 blockierende Strukturen, 6 Induktivität, 27 Integration monolithische, 3 numerische, 28 Integrationsdichte Erhöhung, 4 Inversion, 8 IP, 24 Isolation, 3 F Feld-Oxid, 8 Feldmaske, 6, 8, 9 Feldstärke, 6, 12 Fertigung, 30 Fertigungstest, 27 Fertigungstoleranz, 11 Fin-Fet, 3 Finaler Test, 30 Flip-Flop, 17 Simulation, 29 Fokussierung, 4 FPGA, 3 Aufbau, 3 Full Custom, 2 J Justierungstoleranz, 5 K Kanallänge, 9 Kanallängenmodulation, 12 Kapazität, 27 Gate-Substrat, 12 parasitäre, 10 spannungsabhängige, 10 Sperrschicht, 10, 11 Katalog von Layout-Elementen, 2 Kleinsignalmodell, 27 G Gate Material, 11 35 Index Knotenspannungsanalyse, 28 modifizierte, 28 Known Good Dice, 32 Komplementärsymmetrie, 13, 14 Komplexgatter, 14 Probleme, 18 Kondensator, 3, 17, 18, 27 als Speicher, 17 Kurzkanaleffekt, 9 LVS, 25, 26 M Machine Model, 20 Maske, 2, 3 Master-Slave-Flip-Flop, 15 Maze Runner, 23 MCM, 32 Metallebene CMOS, 14 Metastabilität, 16 Minoritätsträger, 8, 10 Montage gehäuselos, 31 Moore’s Law, 2 MOS-Transistor, 5, 8, 25 Feldschwell-, 8 Kapazität, 11 Kennlinie, 12 Kennlinien, 8 parasitärer, 8 L Ladungsträger, 13 heiße, 9 Länge, 8, 9, 13 Längsfeld, 9 Latch D, 16 RS, 16 Latch-Up, 5–7, 10, 19, 21, 25 Layout handoptimiertes, 2 Layout Parameter Extraction, 26 Layout-Verifikation, 26 Lebensdauerversuch, 31 Leckeffekt am Transistor, 12 Leckstrom, 5, 18 Leistungsaufnahme CMOS, 5 Depletion-Lastelement, 5 minimieren, 15 Leitung induktiver Belag, 21 Modell, 21 Leitungsbelag induktiver, 22 Leitungsverzögerung, 21, 22 Leitwert, 27 Lightly Doped Drain, 6, 7, 12 Lizenz, 24 Los Lieferwürdigkeit, 30 LPE, 26 N n-Wannen-Prozeß, 5 Netzliste, 2 Netzwerk Pulldown, 14 Pullup, 14 NMOS, 8, 13 O Oxid Dicke, 9 Ladung, 9 Oxide Encroachment, 6, 7 P p-Wannen-Prozeß, 5 Parametertest, 30 Phase Locked Loop, 23 Photolithographie, 3, 4 Plastikgehäuse, 32 PMOS, 8 36 Index Poly, 5, 7, 14 Gate, 9 Prozeß selbstjustierender, 5, 14 Prozeßtechnologie Verbesserungen des letzten Jahrzehnts, 6 Prüfverfahren für Drahtverbindungen, 33 Pulldown, 14 Pullup, 14 Q Querfeld, 9 Querstrom, 13 R Ratio-Less-Logic, 14, 19 Referenztakt, 23 Refresh, 17, 18 Reihenadressierung, 17 Reset asynchroner, 16 Ringoszillator, 22 ROM, 18 Spannungsquelle, 27 Speicher dynamischer, 10, 17 flüchtiger, 18 Sperrbereich, 9 Sperrschicht Weite, 10 Spule, 27 SRAM, 17 Standardzelle, 2, 23, 24 Staub, 4 Störabstand, 14 Stromquelle, 27 Stromversorgung für Analogschaltungen, 20 Sub-Threshold-Strom, 9 Substrat, 3, 5, 12 keramisches, 3 niederohmiges, 6 Substrat-Effekt, 11 T TAB, 32 taktgesteuert, 16 Taktversatz, 17 Taktversorgung, 19 Taktverteilungssystem, 16 Telegraphengleichung, 22 Temperatur, 7, 9 Teststruktur, 22 Thresholdspannung, 4, 9 Thyristor, 7, 21 Transfergatter CMOS, 15 Transformator, 27 Transientenanalyse, 28, 29 Transistor, 27 als Kondensator, 10 als Schalter, 10 Enhancement, 8 Feldschwell parasitärer, 8 Trapez, 28 S Sägerahmen, 32 Schaltungssimulation, 27 Schutzring, 26 Schwellspannung, 9, 12 Sea-of-Gates, 23 Selbstjustage, 7 Semi Custom, 2 Setup-Zeit, 16 Shallow Trench, 6 Shichman-Hodges-Modell, 9 Strom, 12 Siebdruckverfahren, 3 Simulated Annealing, 25 Simulation, 29 Slow-Wave, 20 Spaltenadressierung, 17 37 Index Treiber, 15 Dimensionierung, 19 Kette, 15 Versorgung, 20 U Überlappung, 5, 11 Kapazität, 13 Übersprechen, 18, 22 Gegenmaßnahmen, 18 Unterdiffusion, 5, 7, 9 Urheberrecht, 24 V Verbindungsleitung auf dem Chip, 22 zwischen Chips, 22 Verdrahtung, 3 Vereinzeln, 30 Verifikation, 26 Versorgungsleitung, 19 Verwertungsrecht, 24 Vogelschnabel, 6, 9 W Wärmewiderstand, 31 Waferlos, 31 Wafersort, 30 Wanne, 14 Weak-Inversion-Strom, 10 Wechselstrom-Kleinsignalanalyse, 28 Weite, 7–9, 13 Welle elektromagnetische, 4 Länge, 4 Widerstand, 3, 25, 27 Wiederverwertung von Entwürfen, 25 Wortleitung, 17 Z zustandsgesteuert, 16 38