Übungsblatt 5 mit Musterlösung

Werbung

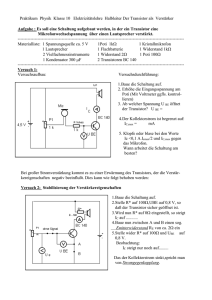

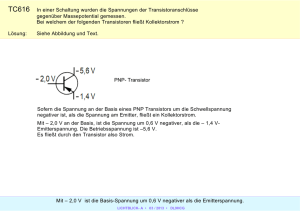

Musterlösung Übungsblatt 1 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 5 Prof. Baitinger / Lammert b) Die Diode wird in der Schaltung nach Abb. 1-2 betrieben. Berechnen Sie jeweils die Spannung UR, die am Widerstand R anliegt, wenn für das Verhalten der Diode D die Kennlinien aus Abb. 1-1 b) und c) zugrundegelegt werden. Besprechung: 15.01.2001 Aufgabe 1 R Idealisierte Diode UR 5V Von einer realen Diode D seien die zwei folgenden Kennlinien in Abb. 1-1 b) und c) gegeben, die in zwei Stufen versuchen eine Linearisierung der Diodenkennlinie zu erzielen. a) Geben Sie für die Kennlinien aus Abb. 1-1 b) und Abb. 1-1 c) jeweils ein Ersatzschaltbild an. Verwenden Sie dabei nur ideale Dioden ( Kennlinie: Abb. 1-1 a) ) Widerstände und Spannungsquellen. a) b) I c) I 100mA I = UD D Abbildung 1-2 Da die Diode in Abb. 1-2 in Durchlaßrichtung gepolt ist, sind nur die „rechten“ Teile der Ersatzschaltungen interessant: 100mA R UR -1,4 UR ID 0,7V = -1,4 U ID R 0,7 U[V] 0,7 -1µA 1,4 U[V] -1µA 5V 5V = = R1 R3 Abbildung 1-1 Abbildung 1-3: Vereinfachte Ersatzschaltungen 0,7V = R2 R1 R4 R3 Für den Diodenstrom gilt: UD 100mA I D = ------- = ----------------- ⋅ U D 0, 7V R1 UD 100mA I D = ------- – 100mA = ----------------- ⋅ U D – 100mA 0, 7V R3 0, 7V R 1 = ----------------- = 7Ω = R 3 100mA Abbildung 1-1-1: Ersatzschaltbilder Seite 1 von 11 Seite 2 von 11 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 Für die Spannung am Widerstand R ergibt sich: U R = 5V – R 1 ⋅ I D Aufgabe 3 4, 3V U R = 4, 3V – R 3 ⋅ ---------------R + R3 R1 U R = 5V ⋅ 1 – -------------- R + R 1 R3 U R = 4, 3V ⋅ 1 – -------------- R + R 3 R U R = 5V ⋅ ---------------- R + R 1 Aufgabe 2 In der Digitaltechnik dient der Transistor als Schaltelement. Damit das Ausgangssignal eindeutig einem Pegel zugeordnet werden kann, muss die Schaltung entsprechend dimensioniert werden. Gegeben sei die Schaltung nach Abb. 3-1 mit der Eingangsspannung Ue und der Ausgangsspannung Ua. Die Innenwiderstände des Transistors T sind vernachlässigbar und im gesättigten Zustand beträgt die Collector-Emitter-Spannung U CE = OV . Die Durchlassspannung der Basis-Emitter-Diode ist U BE = 0, 7V , der Verstärkungsfaktor des Transistors beträgt B N = 200 . U R = 5V – 0, 7V – R 3 ⋅ I D 5V U R = 5V – R 1 ⋅ ---------------R + R1 Transistor als Schalter R U R = 4, 3V ⋅ ---------------- R + R 3 IC Ersatzschaltbild des NPN-Transistors RC In Abb. 2-1 ist ein vereinfachter, bipolarer NPN-Transistor gegeben. Der Transistor werde normal betrieben. RBB sei der Basisbahnwiderstand, CCB die Sperrschichtkapazität zwischen Basis und Collector. Zeichnen Sie die restlichen Elemente des Ersatzschaltbildes ein. Achten Sie dabei auf die Pfeilrichtung bei Spannungs- und Stromquellen! IB Ue B E RB = T U0 Ua C Abbildung 3-1: Transistor als Schalter a) Welche Logik-Schaltung wird in Abb. 3-1 realisiert ? RBB CBE p n p RCC n CCB p RBE UBEe b) Gegeben sei U 0 = 5V und R C = 500Ω . Wie groß ist der maximale Collectorstrom ICmax ? ICB BNIN p Ist Ue groß, dann leitet der Transistor T und U a = U CE wird klein, während bei kleinem Ue der Transistor sperrt und U a = U CE auf die Betriebsspannung U0 ansteigt. Daher handelt es sich um einen Inverter. CCS Der maximale Collectorstrom fließt, wenn an RC die maximale Spannung anliegt, d. h. der Transistor sich im gesättigten Zustand mit U CE = OV befindet. Nach der Maschenregel gilt: U RC + U CE = U 0 mit U RC = R C I Cmax ICS U 5V I Cmax = ------0- = ------------- = 10mA RC 500Ω Abbildung 2-1: Ersatzschaltbild des NPN-Transistors Seite 3 von 11 Seite 4 von 11 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 c) Berechnen Sie den maximalen Basisstrom IBmax. Nehmen Sie dabei an, dass sich der Transistor T an der Grenze zwischen linearem und gesättigten Bereich befindet. f) Zeichnen Sie die Übertragungskennlinie U a = f ( U e ) . Ua / V Im Grenzbereich zwischen linearem und gesättigten Zustand gilt gerade noch: gesperrt 5 IC I C = B N I B ⇒ I B = -----BN linear 2,5 Der maximale Basisstrom IBmax fließt, wenn der Collectorstrom maximal ist: gesättigt I Bmax I Cmax 10mA = ------------= -------------- = 0, 05mA BN 200 0 d) Dimensionieren Sie den Widerstand RB so, dass bei I B = I Bmax die Eingangsspannung U e = U Highmin = 2, 5V beträgt. Da der Transistor leitet, beträgt U BE = 0, 7V . Nach der Maschenregel gilt: U R B + U BE = U e mit U R B = R B I Bmax . 0,7 1,6 2,5 Ue / V Abbildung 3-2: Übertragungskennlinie des Inverters g) In welchem Spannungsbereich müssen die Logikpegel High und Low liegen, damit eine nachfolgende Logikschaltung mit den gleichen Eigenschaften die Pegel eindeutig erkennt ? Nach Teilaufgabe d) liegt UHigh im Bereich von 2,5V bis 5V, während ULow nach Teilaufgabe e) zwischen 0V und 1,6V liegt. U e – U BE 2, 5V – 0, 7V - = -------------------------------- = 36kΩ R B = ---------------------0, 05mA I Bmax Aufgabe 4 e) Am Eingang liege eine Spannung von U e = 1, 6V . Wie groß ist Ua in diesem Fall ? Da U e > 0, 7V ist, leitet der Transistor T und befindet sich wegen U e < U Highmin im linearen Bereich. Nach der Maschenregel gilt: U R B + U BE = U e mit U R B = R B I B . U e – U BE I B = ---------------------- = 25µA RB Nach der Maschenregel gilt: U RC + U CE = U 0 mit U RC = R C I C = R C B N I B und U CE = U a . Grundlagen des MOS-Transistors a) Welche Betriebsbereiche hat ein MOS-Transistor ? Der MOS-Transistor hat 3 Betriebsbereiche: -gesperrter Bereich -linearer Bereich -gesättigter Bereich b) Geben Sie für jeden Bereich an, welche Werte die Gate-Source- und die DrainSource-Spannung annehmen kann. Im gesperrten Bereich ist die Gate-Source-Spannung UGS kleiner als die Schwellspannung Uth. Im linearen Bereich und gesättigten Bereich ist U GS > U th . Für die Drain-Source-Spannung UDS gilt im linearen Bereich U DS < U GS – U th , während im gesättigten Bereich U DS > U GS – U th ist. U a = U 0 – R C B N I B = 5V – 500Ω ⋅ 200 ⋅ 25µA = 2, 5V Seite 5 von 11 Seite 6 von 11 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 c) Zeichnen Sie einen Querschnitt durch einen N-Kanal MOS-Transistor. Gate Si-Oxid Source Aluminium g) Zeichnen Sie die Abschnürspannung UP in das Kennlinienfeld ein. K 2 Im Bereich der Abschnürspannung UP gilt: I D = ---- ⋅ U DS . Diese Gleichung ist in 2 das Kennlinienfeld in Abb. 4-1 eingezeichnet. Drain n-Si n-Si Die Abschnürspannung UP ist die Drain-Source-Spannung, die an der Grenze zwischen linearem und gesättigten Bereich am MOS-Transistor anliegt. Für UP gilt: U P = U GS – U th . p-Si h) Kennzeichnen Sie im Kennlinienfeld die 3 Betriebsbereiche des MOS-Transistors. Abbildung 4-0: Querschnitt durch N-Kanal MOS-Transistor d) Welcher Unterschied besteht zwischen Source und Drain ? Da der MOS-Transistor symmetrisch aufgebaut ist, besteht kein Unterschied zwischen dem Source- und dem Drain-Gebiet. Die Grenze zwischen linearem und gesättigten Bereich stellt die Abschnürspannung UP dar, der gesättigte und gesperrte Bereich wird durch die Kennlinie U GS = U th voneinander getrennt (siehe Abb. 4-1). Aufgabe 5 In Abb. 4-1 ist ein Kennlinienfeld eines MOS-Transistors gegeben. Schaltung mit MOS-Transistor Gegeben sei die Schaltung nach Abb. 5-1. Der Strom I sei so gewählt, daß der Transistor in den Sättigungsbereich gelangt. Bekannt sei der Widerstand R, der Strom W I, die Schwellspannung Uth sowie die Transistorkenngröße K = µc OX ----- . L ID UP IR linear UR ID R I gesättigt UGS IG UDS IR UGS UR gesperrt R UGS=Uth UDS Abbildung 5-1: Abbildung 4-1: Ausgangskennlinienfeld eines MOS-Transistors e) Wie heißt dieses Kennlinienfeld ? Es handelt sich um das Ausgangskennlinienfeld eines MOS-Transistors. a) Wie lautet die Formel für den Drainstrom ID in Abhängigkeit von K, UGS und Uth? f) Was ist die Abschnürspannung UP ? Seite 7 von 11 Seite 8 von 11 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 Im Sättigungsbereich gilt für den Drainstrom: tivem Wurzelvorzeichen bei steigender Stromstärke I der Strom IR und damit auch die Gate-Source-Spannung UGS und der Drainstrom ID sinken würden. K 2 I D = ---- ( U GS – U th ) 2 d) Wie groß ist die Drain-Source-Spannung UDS und der Drainstrom ID ? Für die Drain-Source-Spannung UDS gilt: b) Stellen Sie eine quadratische Gleichung mit dem Strom IR auf. Überlegen Sie sich dabei, wie groß der Gatestrom IG eines idealen MOS-Transistors ist. 2 ( KRU th – 1 + 1 + 2KR ( RI – U th ) ) U DS = 2U R = 2RI R = -----------------------------------------------------------------------------------------KR Nach der Knotenregel gilt: I = I R + I D K 2 I R = I – I D = I – ---- ( U GS – U th ) 2 Nach der Knotenregel gilt für den Drainstrom ID: (*) KR ( RI – U th ) + 1 – 1 + 2KR ( RI – U th ) I D = I – I R = ---------------------------------------------------------------------------------------------------2 KR Da der Transistor als ideal angenommen werden kann, ist der Gate-Strom IG = 0 . Aufgabe 6 U GS = U R = RI R Ersatzschaltbild des MOS-Transistors a) Zeichnen Sie das Ersatzschaltbild eines gesperrten und eines leitenden MOSFeldeffekttransistors. Nach dem Einsetzen in Gl. (*) ergibt sich: b) Markieren Sie darin die parasitären Stromquellen. K 2 I R = I – ---- ( RI R – U th ) 2 G G Diese quadratische Gleichung wird nach IR sortiert: 2 2 CGD 2 K R ⋅ I R + 2 ( 1 – KRU th ) ⋅ I R + ( K U th – 2I ) = 0 S c) Berechnen Sie den Strom IR in Abhängigkeit von den gegebenen Größen. Zur Berechnung von IR muß die Lösungsformel für quadratische Gleichungen angewandt werden:: 2 2 D S CSB CDB CSB CDB ISB IDB CGS* IDS CGB D 2 CGD* CGS ISB IDB B B MOS-Transistor gesperrt MOS-Transistor leitend 2 Diskr = 4 ( 1 – KRU th ) – 4KR ( K U th – 2I ) = 4 ( 1 – 2KRU th + 2K R I ) = 4 ( 1 + 2KR ( RI – U th ) ) KRU th – 1 + 1 + 2KR ( RI – U th ) ( – 2 ) ( 1 – KRU th ) ± 2 1 + 2KR ( RI – U th ) - = ---------------------------------------------------------------------------------I R = --------------------------------------------------------------------------------------------------2 2 2K R KR Abbildung 6-1: Ersatzschaltbild eines MOS-Transistors Es muß das positive Vorzeichen vor der Wurzel genommen werden, da bei negaSeite 9 von 11 Seite 10 von 11 Elektrotechnische Grundlagen, WS 00/01 c) Gegeben sei die Gate-Drain-Kapazität C GD , die Gate-Source-Kapazität C GS und die Gate-Body-Kapazität C GB für den gesperrten Transistor. Berechnen Sie daraus die Kapazitäten C GD∗ und C GS∗ für den leitenden Transistor. Nehmen Sie dabei den Gesamtwert von C GB als konstant an. Der leitende Kanal schirmt das Gate vom Body ab. Die MOS-Kapazität liegt nun nicht mehr zwischen Gate und Body, sondern zwischen Gate und dem Kanal. Als einfachste Näherung wird diese neue Kapazität aufgeteilt und Drain und Source zugerechnet: C GB C GB - und C GS∗ = C GS + --------C GD∗ = C GD + --------2 2 Seite 11 von 11