Kleiner, schneller, billiger und höher

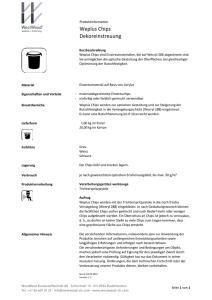

Werbung

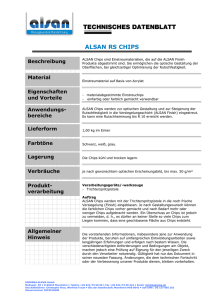

12 f o k us HoHe CHips Logik- und Speicherfunktionen in einem «Hochhaus»-Chip Kleiner, schneller, billiger und höher Seit Jahrzehnten waren die Zielsetzungen der Elektronik kleiner, schneller und billiger. Aber nunmehr fügten Forscher der Stanford University mit drei Innovationen ein weiteres Ziel hinzu: höher. » Henning Wriedt, USA-Korrespondent Während der letzten IEDMKonferenz in San Francisco erläuterte das Forscherteam der Stanford University den Aufbau eines «hohen» Chips. Dieser soll die Performance der gegenwärtigen Logik- und Speicherchips auf den bekannten Platinen wesentlich übertreffen. Die heutigen Schaltungsplatinen sind mit den jeweiligen Chips vollgepackt, und wenn die Funktionsanforderungen das Maximum erreichen, entsteht auf den zahlreichen Leitungen oft ein Datenstau. Links ein traditioneller Chip, rechts ein sogenannter «Hochhaus»-Chip stapeln der Logik- und speicherchips verhindert Datenstau Nach Ansicht der Forscher vermeidet deren Projekt diese Engpässe durch ein Stapeln der Logik- und Speicherchips, die auf diese Weise eng miteinander verbunden sind. Viele Tausende von elektronischen Nano-«Fahrstühlen» transferieren Daten zwischen den Ebenen wesentlich schneller und benötigen weniger Energie als die herkömmlichen Leitungen auf den flachen Chips. Geleitet wird diese Forschungsarbeit von den Professoren Subhasish Mitra und H.-S. Philip Wong von der Stanford School of Engineering. Die Erfindung der Forscher beruht auf drei bahnbrechenden Entdeckungen. Die drei bahnbrechenden Innovationen Die erste Entdeckung ist eine neue Herstellungstechnologie für Transistoren. Die zweite Entdeckung betrifft einen neuen Computerspeicher, der sich besonders gut für die Mehrschichtenherstellung eignet. Und der dritte Punkt dreht sich um die Höhenstrukturen für die neuen Logik- und Speichertechnologien, die sich von den bisherigen Stapelkonzeptionen für Chips wesentlich unterscheiden. Professor Mitra: «Dieses Forschungsprojekt befindet sich in einem frühen Stadium, aber unsere Design- und Herstellungstechniken sind bereits skalierbar. Bei weiterer Entwicklung dieser Architektur kann man davon ausgehen, dass diese Konzeption eine wesentlich bessere Computer-Performance als bisher erreicht.» Professor Wong fügte hinzu, dass der während der IEDM vorgestellte Prototypchip zeigte, wie man Logik und Speicher in einer dreidimensionale Struktur umsetzt, die zudem in Serienproduktion gehen kann. Wong: «Paradigmenwechsel ist ein viel gebrauchtes Wort, aber in diesem Fall ist es wohl angebracht. Mit der neuen Architektur können Elektronikhersteller eine Supercomputerleistung in die Hände der Anwender legen.» Die Wärme des siliziums Ingenieure fertigen Siliziumchips schon seit Jahrzehnten, aber die Wärme, die von den Handys und Laptops ausstrahlt, ist der Beweis für ein Problem. Auch wenn die Siliziumtransistoren abgeschaltet sind, tritt im- mer noch etwas Elektrizität aus, und Anwender fühlen das als Wärme. Und auf der Systemebene entleeren diese Leckagen die Akkus und verursachen somit Verlustleistungen. Forscher versuchen dieses grosse Problem mit der Herstellung von Transistoren aus Kohlenstoffnanoröhren (CNT = Carbon Nanotube) zu lösen. Sie sind so schmal, dass fast zwei Milliarden CNTs auf die Breite eines menschlichen Haares passen. CNTs sollten zudem weniger Elektrizität verlieren, denn deren winzige Durchmesser sind leichter zu «drosseln». In einem zweiten Vortrag zeigten Mitra und Wong, wie ihr Team einige CNTTransistoren fertigten, die eine extrem gute Performance aufweisen. Sie erzielten diesen Erfolg dadurch, dass sie genügend viele CNTs auf einer Fläche aufbrachten, aus der ein brauchbarer Chip entstehen kann. Bisher konnten die üblichen standardisierten Herstellungsverfahren für das Züchten von CNTs keine ausreichende Dichte dieser Röhren erzielen. Aber auch dieses Problem lösten die StanfordForscher mit einer genialen Technik. siliziumwafer ist die Grundlage des stapelchips Sie begannen die Züchtung der CNTs wie gewöhnlich auf runden Quarzwafern. Aber dann entwickelten sie eine Art Metallfilm, der wie ein Klebeband funktioniert. Mit diesem Adhäsivprozess hoben sie ein ganzes CNT-Bündel von dem Quarzmedium und platzierten dieses auf einen Siliziumwafer. Damit wurde der Siliziumwafer die Grundlage ihres Stapelchips. Aber zuerst mussten die Forscher eine CNT-Schicht mit ausreiPolyscope 4/15 HoHe CHips 13 fokus Darstellung des Vierebenen-Chips der Stanford-Forscher chender Dichte herstellen, um Logikelemente hoher Performance zu bekommen. Also wurde dieser Prozess 13-mal wiederholt. Das Ergebnis war eine der höchsten CNT-Dichten überhaupt - und das mit den üblichen Laborsystemen auch auf mehreren Logikebenen. Neuer speichertyp direkt auf den CNT-schichten Die Herstellung der Ebenen aus CNT-Transistoren hoher Performance war nur ein Teil der Innovationen, denn sie konnten auch einen neuen Speichertyp, der nicht auf Silizium basiert, direkt auf den CNT-Schichten herstellen. Das Stanford-Team verwendete bei der Speicherherstellung Titannitrid, Hafniumoxid und Platin. Damit formten sie ein Metall-Oxid-Metall-Sandwich. Legt man eine Spannung an dieses Drei-Metalle-Sandwich an, kann dieses Sandwich einen Stromfluss verhindern. Dreht man die Elektrizität allerdings um, wird die Struktur einen elektrischen Strom leiten. Das erklärt den Namen: Resistive Random Access Memory oder RRAM. Diese Speicher kann man zudem bei Temperaturen fertigen, die wesentlich unter denen der Siliziumspeicher liegen. senkrechte Verbindungsebenen Mitentscheidend für den Forschungserfolg war der Niedertemperaturherstellungsprozess für die RRAMs und CNTs, denn dadurch konnte man jede Speicherebene direkt auf der CNT-Logikebene anordnen. Und während die Speicherebene positioniert wurde, bohrte man Tausende von Verbindungen in die darunter liegende Logikebene. Gerade diese Mehrfachverbindungen verhindern die Datenengpässe, die auf den Verbindungsleitungen bisheriger 3D-Chips auftreten. « Infoservice Stanford University Stanford, CA 94305–6104, USA www.stanford.edu Polyscope 4/15 NEU: MEMS-OSZILLATOREN SICHERHEIT IN SERIE Die Spezialisten von Jauch stehen Ihnen mit Rat und Tat zur Seite: bei der Auslegung Ihrer Schaltung, bei allen messtechnischen Anforderungen sowie bei allen Fragen rund um Ihr Batteriesystem. Unser Produktprogramm reicht von Quarz- und MEMS-Oszillatoren über Standardzellen bis zum speziellen Akkupack. Ihr Vorteil: Auch individuelle Anforderungen erfüllen wir zuverlässig und Ihre Anwendung läuft sicher in Serie. QUARZE BATTERIEPACKS OSZILLATOREN LITHIUM-POLYMER-/ LITHIUM-IONEN-BATTERIEN MEMS-OSZILLATOREN Kontakt Quarze: Jauch Quartz GmbH D-78056 VS-Schwenningen www.jauch.de BATTERIE-MANAGEMENT-SYSTEM (BMS) Kontakt Batterien: Jauch Quartz GmbH CH-4435 Niederdorf www.jauch.de