D/A- und A/D

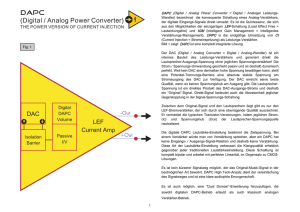

Werbung

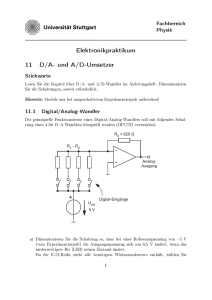

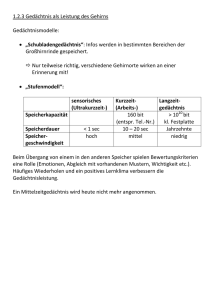

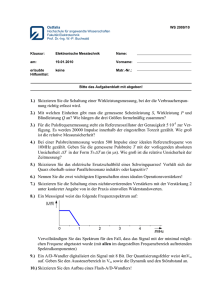

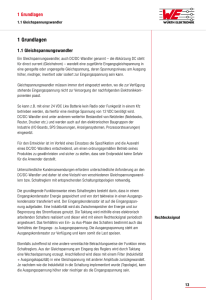

D/A- und A/D- Wandler © Roland Küng, 2011 1 Konversion Analog Digital 7 6 5 4 3 2 1 0 VREF v ana log = VREF D D D D (D1 + 2 + 3 + 4 + ... NN−1 ) 2 2 2 4 8 2 D/A-Wandler Grundprinzip S1 = MSB SN = LSB Grundidee Digital/Analog Wandler (DAC) basiert auf dem OpAmp Summierer v0 = VREF D D D D (D1 + 2 + 3 + 4 + ... NN−1 ) 2 2 4 8 2 Widerstände sind als 2er Potenzen gestuft ausgeführt Di = 0 oder 1 3 R-2R Ladder Der Widerstand beträgt vor jedem Knoten nach rechts betrachtet R Zeigen sie, dass dies eine Spannungshalbierung von Knoten zu Knoten und damit eine Stromhalbierung durch den 2R Widerstand bewirkt 4 Verbessertes D/A- Prinzip • Statt Widerstand zu verdoppeln – Spannung halbieren N MSB LSB I0 = ∑ 1 I1 2(K −1) Verbesserung mit Hilfe R-2R Ladder Netzwerk Alles mit demselben Widerstandswert R realisierbar erlaubt höhere Anzahl Bit und genauer zu wandeln 5 DAC komplett Nachteil: schnelle DAC nicht realisierbar wegen OpAmp Bandbreite. Schnelle Wandler: DAC als hochohmige Stromquelle (also ohne Opamp) 6 Alternative Implementation basierend auf Stromquellen N=5 • Stromquellen besser integrierbar • Breitbandigere Schaltungen N=4 MSB Stromspiegel mit FET: ID ~ W/L 7 Frequency – Voltage Converter Averaging DAC Anwendungen: Umdrehung zu Spannung, Tachometer, Flow Speed, Sound Switch, Licht-Datenübertragung (LED – PD)… in Schmitt Trigger One Shot Multivibrator out Averaging Filter LM2907 R C 8 Frequency – Voltage Converter Averaging DAC Trigger Averaging Tiefpass Differenzierer Mono-shot T0 Wahl R⋅C für Ripple < ½ LSB von n Bit: R ⋅ C = τ = 0.69(n + 1) T o Dauer bis Endwert erreicht wird: 2 t settle ≈ 0.5(n + 1) T o 9 Multiplying DAC Analoge Signale gewichten LTC 1590 Gewichtung Ausgangssignal Eingangssignal 10 Digital Potentiometer DigiPot 11 Digital Potentiometer DigiPot W H L Typ. 10…200 kΩ 500 kHz Bandbreite 256….1024 Stufen 12 A/D-Wandler Applikationstypen langsam veränderliche Signale z.B. phys. Parameter, Regeltechnik Wechselsignale, Pulse Spektrum bis fg unkorrelierte Puls-Amplitudensignale mit Dauer To 13 A/D-Wandler Wechselsignale Wandler mit N Bit Auflösung für Vmax und Erfassungszeit ∆t für ein Sample Signal mit Vpeak max. Fehlerspannung ∆V ∆V = 1 1 LSB = V max • N 4 4 2 ∆V max. Frequenz ∆V 1 = ⋅ f max ∆t 2π Vpeak ∆t 14 A/D-Wandler Begriffe Aperture (Delay) Time: Zeit während der das Signal seit dem Abtastzeitpunkt noch ändert Aperture Uncertainty Time: Unsicherheit des Abtastzeitpunktes Acquisition Time: Zeit die die Abtast-Halteschaltung braucht um auf den Signalwert zu gelangen Conversion Time A/D: Zeit die der digitale Teil zum Abwägen benötigt Hold Time: Zeit die ein Halteglied die Spannung mit max. ¼ LSB Fehler halten muss Wandlungszeit = Acquisition Time + Aperture Time + Conversion Time A/D Sampling Rate = Abtastrate = 1 / Wandlungszeit 15 Sample & Hold Für rasch ändernde Signale und hohe Auflösung empfiehlt sich eine vorgeschaltete Abtast/Halteschaltung (Sample & Hold) Aperture Delay Time unkritisch solange immer gleich gross Abweichung = Jitter Takt Sample & Hold Steuerung 16 Aperture Uncertainty Max. Fehler ½ LSB Bsp: 10 kHz sinus 12 Bit ADC ap. unc. time < 2 ns Gilt für • Wandler ohne S&H • S&H Aperture Uncertainty Time tj ≤ 1 4 ⋅ π ⋅ f ⋅ 2N Hohe Auflösung erfordert präzisen Taktoszillator ! 17 Wandlerfehler Offset und Gain Fehler sind korrigierbar Nichtlinearität und nicht Monotonie sind nicht korrigierbar Missing code und Sticking code sind unerwünscht schwieriger je mehr Bit Auflösung verlangt ist 18 Wieviel Bit darfs sein? wanted stört 0 -20 Applikationsabhängig! -40 8 Bit - z.B. Temperatur -400 – 600 in 0.50 Auflösung 16 Bit - z.B. Funksignal mit starkem Störer -60 19 A/D-Wandler Parallelprinzip Hierbei vergleicht man die Eingangsspannung am N- Bit Wandler gleichzeitig mit n = 2N Referenzspannungen und stellt fest, zwischen welchen beiden sie liegt. Der Vorteil bei diesem Verfahren ist, dass man nur einen Schritt braucht, das Ganze läuft also schnell ab. Dafür ist aber der Aufwand sehr groß. 20 A/D-Wandler Parallelprinzip Flash Converter Flash-Wandler: Wandlung sofort Limitiert durch Anzahl Komparatoren 10 Bit 1024 21 A/D-Wandler Parallelprinzip Half Flash Converter Mit mehreren gestaffelten Flash Convertern kann die Auflösung mit vernünftigem Aufwand gesteigert werden z.B. für 2n = 16 Bit ADC: 2 mal einen n=8 Bit Flash Dafür ist zusätzlich ein präziser Verstärker mit Av = 2n notwendig 22 A/D-Wandler Parallelprinzip Pipelined Flash Converter 23 A/D-Wandler Zählprinzip Bei diesem Verfahren wird abgezählt, wie oft man die Referenzspannung der niedrigsten Stelle addieren muss, um die Eingangsspannung zu erhalten. Die Zahl der Schritte ist gleich dem Ergebnis. Es geht dementsprechend langsam, der Aufwand dafür ist aber klein. • Tracking Converter • Single Slope Converter • Dual Slope Converter 24 A/D-Wandler Zählprinzip Tracking Converter Geeignet für langsam veränderliche Signale 25 http://www.chemgapedia.de/vsengine/vlu/vsc/de/ch/11/cmt/vlus/ad.vlu/Page/vsc/de/ch/11/cmt/simulationen/ad/zaehlsim.vscml.html A/D Wandler Zählprinzip Dual Slope Verfahren RC Zeitkonstante muss nicht genau sein Tfix 26 http://www.chemgapedia.de/vsengine/vlu/vsc/de/ch/11/cmt/vlus/ad.vlu/Page/vsc/de/ch/11/cmt/simulationen/ad/doppelsim.vscml.html A/D-Wandler Zählprinzip Dual Slope Verfahren T2 = T1 va VREF Z 2 = Z1 va VREF 27 A/D-Wandler Wägeprinzip engl. Successive Approximation Beim Wägeverfahren beginnt man mit der höchsten Stelle und ermittelt, ob die Eingangsspannung kleiner oder größer ist als die Referenzspannung für die höchste Stelle. Ist die Spannung größer, setzt man die höchste Stelle auf Eins und subtrahiert die Referenzspannung. Den Rest vergleicht man mit der nächst niedrigeren Stelle usw. Man benötigt also so viele Vergleichsschritte, wie die Zahl Stellen besitzt und ebenso viele Referenzspannungen. 28 A/D-Wandler Wägeprinzip Sukzessive Approximation MSB (zu viel) 2nd MSB (zu viel) „Wandlerbit Positionen durchtesten“ 3rd MSB (zu klein) 29 http://www.chemgapedia.de/vsengine/vlu/vsc/de/ch/11/cmt/vlus/ad.vlu/Page/vsc/de/ch/11/cmt/simulationen/ad/waegesim.vscml.html A/D-Wandler Wägeprinzip Charge Redistribution Converter 1) 2) 3) 4) 5) 6) Alle C's parallel aufladen auf Vin mit Sc geschlossen und Si auf Vin Gemeinsame Platte aller C's mit Sc von Masse trennen, S1...SN auf Masse legen , Si auf VREF schalten -> -Vin am Komparator MSB Anschluss mit S1 auf VREF legen -> Umladeprozess -Vin +VREF/2 Vergleich mit Masse als Schwelle, falls kleiner MSB = 1, sonst MSB = 0 S1 im Fall MSB = 1 auf Position VREF belassen, sonst auf Masse legen Repeat 3) – 5) für alle N Bit's 30 Details Schritt 1 Ladung laden Schritt 2 Ladung halten Schritt 3 - n Ladung wägen 31 A/D-Wandler Sigma-Delta Converter Eigenständiger Ansatz: Umwandlung Analogsignal in Pulsdichte Takt massiv (z.B. 256 mal) höher als Abtastfrequenz erst massive Filterung ergibt die Auflösung von N Bits Grobe Messung. Messfehler wird integriert und fortwährend kompensiert in Gegenkopplung 32 Sigma-Delta Converter Output seriell 33 Voltage to Frequency Converter Variable Stromquelle Komparator mit Reset Analog IN Frequency OUT Puls Symmetrie Integrator-C Entlade Switch 34 Extremes Charge Redistribution Converter 35 Extremes 36 Extremes 37 Zusammenfassung Sigma-Delta Pipelined Parallel 38 Praktikum Lautstärkeregler Digital Audio/Sinus ±5Vpeak R = 1.2…8.2 k Digital Attenuation Input VDD = -VSS = 10 V LED oder 50 Ω Speaker Aufgaben: DC 5V: Messen Knotenspannungen, Kennlinie DAC vout = f(Di) Sinus: Applikation Digitale Signalabschwächung (LED als Last) 39