Tephys-Simulation

Werbung

Prof. Dr. R. Kessler FH-Karlsruhe, Sensorsystemtechnik,

D:\TestPDF\RT3_PDF\PLL_2.DOC

16.05.01,

Seite1

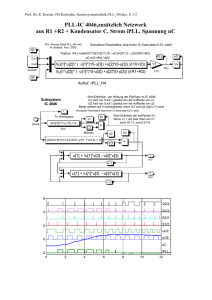

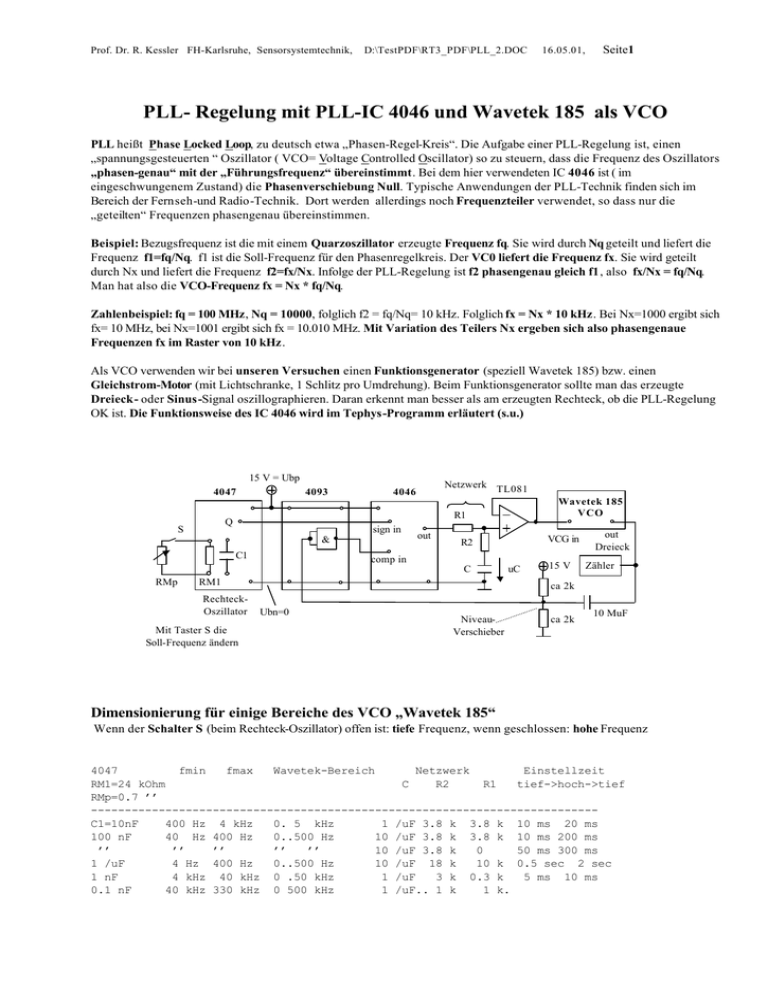

PLL- Regelung mit PLL-IC 4046 und Wavetek 185 als VCO

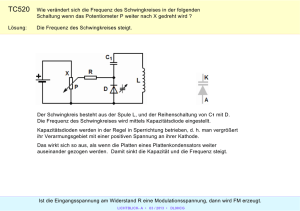

PLL heißt Phase Locked Loop, zu deutsch etwa „Phasen-Regel-Kreis“. Die Aufgabe einer PLL-Regelung ist, einen

„spannungsgesteuerten “ Oszillator ( VCO= Voltage Controlled Oscillator) so zu steuern, dass die Frequenz des Oszillators

„phasen-genau“ mit der „Führungsfrequenz“ übereinstimmt. Bei dem hier verwendeten IC 4046 ist ( im

eingeschwungenem Zustand) die Phasenverschiebung Null. Typische Anwendungen der PLL-Technik finden sich im

Bereich der Fernseh-und Radio-Technik. Dort werden allerdings noch Frequenzteiler verwendet, so dass nur die

„geteilten“ Frequenzen phasengenau übereinstimmen.

Beispiel: Bezugsfrequenz ist die mit einem Quarzoszillator erzeugte Frequenz fq. Sie wird durch Nq geteilt und liefert die

Frequenz f1=fq/Nq. f1 ist die Soll-Frequenz für den Phasenregelkreis. Der VC0 liefert die Frequenz fx. Sie wird geteilt

durch Nx und liefert die Frequenz f2=fx/Nx. Infolge der PLL-Regelung ist f2 phasengenau gleich f1, also fx/Nx = fq/Nq.

Man hat also die VCO-Frequenz fx = Nx * fq/Nq.

Zahlenbeispiel: fq = 100 MHz, Nq = 10000, folglich f2 = fq/Nq= 10 kHz. Folglich fx = Nx * 10 kHz. Bei Nx=1000 ergibt sich

fx= 10 MHz, bei Nx=1001 ergibt sich fx = 10.010 MHz. Mit Variation des Teilers Nx ergeben sich also phasengenaue

Frequenzen fx im Raster von 10 kHz.

Als VCO verwenden wir bei unseren Versuchen einen Funktionsgenerator (speziell Wavetek 185) bzw. einen

Gleichstrom-Motor (mit Lichtschranke, 1 Schlitz pro Umdrehung). Beim Funktionsgenerator sollte man das erzeugte

Dreieck- oder Sinus-Signal oszillographieren. Daran erkennt man besser als am erzeugten Rechteck, ob die PLL-Regelung

OK ist. Die Funktionsweise des IC 4046 wird im Tephys-Programm erläutert (s.u.)

15 V = Ubp

4047

4093

sign in

&

C1

out

comp in

RM1

RechteckOszillator

Mit Taster S die

Soll-Frequenz ändern

VCG in

R2

C

RMp

Wavetek 185

VCO

R1

Q

S

Netzwerk TL081

4046

uC

15 V

out

Dreieck

Zähler

ca 2k

Ubn=0

NiveauVerschieber

ca 2k

10 MuF

Dimensionierung für einige Bereiche des VCO „Wavetek 185“

Wenn der Schalter S (beim Rechteck-Oszillator) offen ist: tiefe Frequenz, wenn geschlossen: hohe Frequenz

4047

fmin

fmax

Wavetek-Bereich

Netzwerk

Einstellzeit

RM1=24 kOhm

C

R2

R1

tief->hoch->tief

RMp=0.7 ’’

--------------------------------------------------------------------------C1=10nF

400 Hz 4 kHz

0. 5 kHz

1 /uF 3.8 k 3.8 k 10 ms 20 ms

100 nF

40 Hz 400 Hz

0..500 Hz

10 /uF 3.8 k 3.8 k 10 ms 200 ms

’’

’’

’’

’’

’’

10 /uF 3.8 k

0

50 ms 300 ms

1 /uF

4 Hz 400 Hz

0..500 Hz

10 /uF 18 k

10 k 0.5 sec 2 sec

1 nF

4 kHz 40 kHz 0 .50 kHz

1 /uF

3 k 0.3 k

5 ms 10 ms

0.1 nF

40 kHz 330 kHz 0 500 kHz

1 /uF.. 1 k

1 k.

Prof. Dr. R. Kessler FH-Karlsruhe, Sensorsystemtechnik,

D:\TestPDF\RT3_PDF\PLL_2.DOC

16.05.01,

Seite2

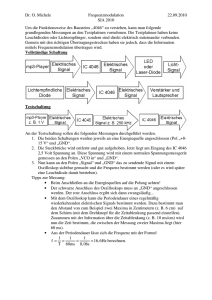

Tephys-Datei c:\Regel\ PLL_neu\wavetm5.txt

1

2

3

4

5

u1alt=u1

{ u1alt = alter Wert von u1, benötigt für Finden der Auf-Flanke von u1 }

u2alt=u2

{ u2alt = alter Wert von u2 „

„

„

„ „

„

„ u2 }

Q1alt=Q1

{ Q1alt = alter Wert von Q1 , benötigt für Rücksetzen Flip-Flop}

Q2alt=Q2

{ Q2alt = alter Wert von Q2 , ebenfalls........}

f1=f10+f1'*(t-tf1)+aP*ja(t-t1)*ja(t2-t) { f1= Führfrequenz. f10=Grundwert, Änderung

von f1 wahlweise durch linearen Anstieg (mit f1’*(t-tf1)

oder sprunghaft im Bereich t1..t2 (mit aP*ja(t-t1)*ja(t2-t) ) }

wi1=wi1+f1*dt

{ wi1= „Winkel“ von f1 = Zeitintegral der Frequenz f1, zur Bildung von u1 }

6

7 u1=ja(sw1-saeg(wi1))

8

{ u1= Rechteckspannung mit Frequenz f1. u1 gebildet aus

Sägezahn saeg(wi) : Wenn Schwelle sw1 > saeg(wi1), dann ist u1 = 1 sonst ist u1 = 0 }

S1=ja(u1-u1alt)

{ S1= „Sprung“ von u1: Wenn u1 von low (=0) nach high(=1) geht, dann ist

S1 = 1, sonst ist S1 =0. Funktion: Wenn u1 größer als der „alte“ Wert u1alt, nur dann ist S1 = 1 }

Z=ja(t-tZ1)*ja(tZ2-t)*(aZ+az*sin(2*pi*fz*t))

{ Z = Störfunktion , nicht benutzt}

9

10 Y=begr(Y0+ja(reg)*YMai,Ymax,0) { Y= Stellgröße für Erzeugung der Frequenz f2}

11 f2id=begr(kVCO*fmax*Y,nf*fmax,0) { f2id = „idealer“ Wert der Frequenz f2 : Die

Steuerspannung Y erzeugt die Freq. kVCO * fmax* Y, sie wird aber begrenzt auf nf*fmax und ist >= 0}

12 f2=f2id*ja(f2id) { f2 = Frequenz des VCO }

13 iPLL=nein(Q1*Q2)*(ja(Q1)*(Ubp-uC)+ja(Q2)*(Ubn-uC))/(R1+R2)

{ iPLL ist der Strom, den das PLL-IC an seinem Ausgang liefert:

Wenn beide internen FlipFlops high sind (also Q1*Q2 =1), dann ist der Ausgang intern hochohmig

geschaltet, also der Strom =0.

Wenn Q1 high ist, ist der Ausgang mit der positiven Betriebs-Spannung Ubp verbunden,

also fließt der Strom (Ubp-uC )/(R1+R2).

Wenn Q2 high ist, ist der Ausgang mit der negativen Betriebs-Spannung Ubn verbunden,

also fließt der Strom (Ubn-uC)/(R1+R2). }

14 uC=uC+iPLL*dt/C { uC = Kondensator-Spannung. Der Kondensator wird mit dem

Strom iPLL geladen }

15 YMai=uC+R2*iPLL { Ymai = Stellspannung für den VCO . Ymai = Spannung am

Verbindungspunkt von R1 und R2. Damit dieser Punkt nicht „belastet“ wird, wird er mit einem

Spannungsfolger verbunden (vgl. Schaltung). }

16 wi2=wi2+f2*dt

{ wi2 = Zeitintegral der Frequenz f2 des VCO }

17 u2d=drei(wi2)

{ u2d = Dreieckspannung des VCO. sie hat die Frequenz f2 }

18 u2=ja(sw2-saeg(wi2)) { u2= Rechteckspannung, gewonnen aus der VCO- Dreieckspannug

durch Komparator}

19 S2=ja(u2-u2alt) { S2 =1 beim Sprung von u2 von low nach high, sonst =0, vgl. S1 }

20 Q1=ja(S1)+nein(S1)*Q1-Q1alt*Q2alt

{ Q1= Ausgang FlipFlop1: Es wird gesetzt,

wenn S1=1 wird (also von der Auf-Flanke von u1) und wird rückgesetzt wenn beide Flip-Flops high sind }

21 Q2=ja(S2)+nein(S2)*Q2-Q1alt*Q2alt{ Q1 = Ausgang FlipFlop2: Es wird von S2 gesetzt

und rückgesetzt , wenn beide Flip-Flops high sind. }

22 Utri=KQ*(Q1-Q2) { Utri = „symbolische“ Differenz Q1-Q2. Mit der hier benutzten Schaltung

kann Utir NICHT gemessen werden }

23 t=t+dt

Kommentar in der Tephys-Datei

PLL, Heft R12, 23.8.95, Heft R14,S.145, R19,110

Prof. Dr. R. Kessler FH-Karlsruhe, Sensorsystemtechnik,

D:\TestPDF\RT3_PDF\PLL_2.DOC

16.05.01,

Seite3

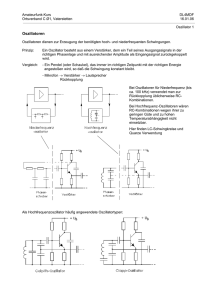

u1=FührungsSchwingung, u2= nachgeführte Schwingung

S1 bzw. S2 high-Impulse (Dauer=dt) beim low->high Sprung von u1 bzw. u2

Q1,Q2 Flip-Flop-Ausgänge des "zweiten" Phasen-Komparators im IC 4046:

Q1 wird gesetzt von S1 und zurückgesetzt, wenn Q1 UND Q2 high sind.

Q2 " " " S2 " "

" " " " " " .

(Lit: Tietze-Schenk: Frequenzempfindlicher Phasendetektor)

PLL. Ziel: Freq. f2 so ändern, dass u2 phasenstarr gleich u1 wird.

als VCO Wavetek, vgl Exp Heft R14 S.145, 5.5.96

Datei Wavetm5.txt : Methode Maier, ab Okt. 96, Exp R19,110..

Hier wird geregelt (reg=1)

Der VCO (=Wavetek185)

ist im Bereich 0 bis 500 Hz.

Die SollFrequenz f1 springt

von 50 auf 450 Hz und

zurück. Zu optimieren sind

die 3 Parameter R1, R2, C.

Hier ist C=10 Mikrofarad,

R1=500 Ohm, R2=1000

Ohm.

Prof. Dr. R. Kessler FH-Karlsruhe, Sensorsystemtechnik,

D:\TestPDF\RT3_PDF\PLL_2.DOC

16.05.01,

Seite4

Prof. Dr. R. Kessler FH-Karlsruhe, Sensorsystemtechnik,

D:\TestPDF\RT3_PDF\PLL_2.DOC

16.05.01,

Seite5

Prof. Dr. R. Kessler FH-Karlsruhe, Sensorsystemtechnik,

D:\TestPDF\RT3_PDF\PLL_2.DOC

16.05.01,

Seite6