Schaltungsentwurf mit Standardschaltkreisen

Werbung

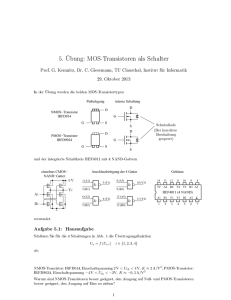

1. Übung EDS: Schaltungsentwurf mit Standardschaltkreisen Prof. G. Kemnitz, Dr. C. Giesemann, TU Clausthal, Institut für Informatik 23. April 2014 Abb. 1 zeigt eine Schaltung aus den jeweils vier Gattern eines 74HC08 (4×AND2) und eines 74HC86 (4×EXOR) angeschlossen an den digitalen Ein-/Ausgängen (DIO's) des Electronics Explorers und einen Vorschlag für den Aufbau auf dem Steckbrett (ohne Verbindungen zu den DIOs). x0 y0 x 1 =1 & c0 y1 x2 =1 c1 & y2 x3 =1 c2 & y3 =1 c3 & c4 DIO 0 1 2 3 4 8 9 10 11 12 Anschluss c0 x0 x1 x2 x3 y0 y1 y2 y3 c4 x2 74HC08 14 13 12 x3 c4 11 10 9 14 UV & & UV 13 12 11 y3 10 9 8 UV & 1 y2 74HC86 8 a) 2 c0 x0 =1 & 3 4 5 =1 =1 6 7 1 x1 2 =1 3 y0 4 5 6 y1 7 b) Abbildung 1: Testschaltung für den Logiktest a) Schaltplan b) Steckbrettaufbau Schaltungsaufbau Electronics Explorer an Spannung und über USB an den PC anschlieÿen. Programm Waveforms starten (all Programms > Digilent >Waveforms). Device auswählen. Schaltung auf dem Steckbrett des Electronics Explore aufbauen, Ein- und Ausgänge mit den DIOs verbinden (nummerierte Anschlüsse der Digital-x-Blöcke), Masse und Versorgungsspannung mit ↓ und Vcc verbinden. 1 2 Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik Kontrolle aller Verbindungen mit Multimeter als Durchgangsprüfer. Sichtkontrolle durch den Übungsleiter. Erst dann Spannung einschalten. Statischer Test Ein statischer Test kontrolliert die logische Funktion ohne Berücksichtigung potentieller Probleme durch Signalverzögerungen. In jedem Testschritt werden Eingabewerte eingestellt (z.B. mit Schaltern) und die Ausgaben überprüft (z.B. mit Leuchtdioden). Hier soll der Test mit SoftwareSchaltern und Leuchtdioden erfolgen. Im Startfenster von WaveForms Static I/O önen. Für die Beispielschaltung sind DIO 0 bis DIO 4, wie in Abb. 1 als Schalter zu kongurieren (rechte Maustaste > Push/Pull Switch). DIO 8 bis DIO 12 sind als Leuchtdioden zu belassen. Der Test besteht darin, Schalterwerte einzustellen und Ausgabewerte zu protokollieren bzw. mit Sollwerten zu vergleichen. c4 y3 y2 y1 y0 x3 x2 x1 x0 c0 Abbildung 2: Konguration des Static-I/O-Fensters für die Testschaltung in Abb. 1 Aufgabe 1.1 Aktivieren Sie im Fenster Power Supplies and Voltmeter die Quelle Vcc. Führen Sie die Tests durch und füllen Sie Tabelle 1 aus: Test mit Logikgenerator und Logikanalysator Ein Logikgenerator stellt Folgen digitale Eingabesignale bereit und ein Logikanalysator zeichnet digitale Signalfolgen auf. Der Electronics Explorer hat 32 digitale Anschlüsse, die alle auÿer als static I/O's, auch als Logikgeneratorausgänge und Logikanalysatoreingänge genutzt werden können. Vor Nutzung als Generatorausgänge Static I/O-Fenster schlieÿen. Das Logikgeneratorfenster wird über die Schaltäche Patterns in der Spalte Digital geönet. Für das Beispiel sind im Logikgenerator-Fenster Eingabebus denieren: Add > Bus > Name: Eing; DIO 4 bis DIO 0 nach Selected; Format Hexadecimal; ok; Korrektur: Bus Eing auswählen > Edit > Edit Properties of "Eing" Eingabedaten festlegen: Bus Eing auswählen > Edit > Edit Parameters of "Eing" > Type Random; Optput: PP; Idle: Low; Frequency: 1 kHz Abspielfenster: Run: 10ms; Scale: Auto Wiederholanzahl Repeat: 1 (Abb. 3). 3 Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik DIO 4 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 DIO 3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 DIO 2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 DIO 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 DIO 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 DIO 8 DIO 9 DIO 10 DIO 11 DIO 12 Tabelle 1: Wertetabelle Abbildung 3: Kongurationsfenster des Logikgenerators Das Logikanalysatorfenster wird über die Schaltäche Analyzer in der Spalte Digital geönet. Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik 4 Abbildung 4: Kongurations- und Aufzeichnungsfenster des Logikanalysators Im Logikanalysatorfenster sind folgende Kongurationen vorzunehmen (Abb. 4): Eingabebus denieren: Add > Bus > Name: Eing; DIO 4 bis DIO 0 nach Selected; Format Hexadecimal; ok; Ausgabebus denieren: Add > Bus > Name: Ausg; DIO 12 bis DIO 8 nach Selected; Format Hexadecimal; ok; Aufzeichnungsbeginn bei Start des Signalgenerators: Source: Patterns Darstellungszeit 0 bis 10 ms ab Start: Base: 1 ms/div; Pos: 5 ms Mode Normal (Abb. 4). Aufzeichnung: Vcc, falls noch nicht erfolgt, einschalten. Im Logikanalysator-Fenster Button Single betätigen. Warten bis der Trigger-Zustand von Ready auf Armed (scharf) wechselt. Im Logikgeneratorfenster Button Run betätigen. Warten bis der Trigger-Zustand über Trig'd auf Done wechselt. Zur Untersuchung der Verzögerungszeiten ist der Test wesentlich schneller durchzuführen, z.B. Mit einem Takt von 10 MHz statt 1 kHz. Dazu im Logikgeneratorfenster umstellen: Generatortakt: Bus Eing auswählen > Edit > Edit Parameters of "Eing" > Frequency: 10 MHz Anzeigefenster anpassen: Run 1 µs Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik 5 Abbildung 5: Schnelle Datenaufzeichnung Im Logikanalysator ist auch das Zeitfenster umstellen: Base: 100 ns/div; Pos: 500 ns. Abb. 5 zeigt den so aufgezeichneten Signalverlauf, in dem die Ausgabeänderungen sichtbar gegenüber den Eingabeänderungen verzögert sind. Aufgabe 1.2 Führen Sie für die aufgebaute Beispielschaltung die beschriebenen Tests mit dem Logikgenerator und -analysator durch. Kontrollieren Sie, dass die logischen Ausgaben in jedem Testschritt mit denen aus der vorherigen Aufgabe übereinstimmen. Aufgabe 1.3 Erweitern Sie das bisherige Testobjekt, die Inkrement-Funktion, mit einem zusätzlichen Schaltkreis 74HC174 (6 Registerzellen) zu einem 4-Bit-Zähler. Führen Sie mit dieser Schaltung zuerst einen statischen und dann einen dynamischen Test durch. Aufgabe 1.4 Entwerfen Sie mit den verfügbaren Schaltkreisen eine weitere Schaltung ihrer Wahl und probieren Sie diese in derselben Weise aus.