5. Übung: MOS-Transistoren als Schalter

Werbung

5. Übung: MOS-Transistoren als Schalter

Prof. G. Kemnitz, Dr. C. Giesemann, TU Clausthal, Institut für Informatik

29. Oktober 2013

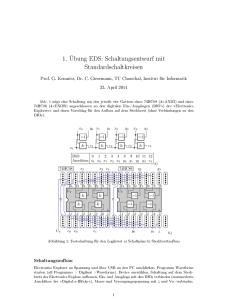

In der Übung werden die beiden MOS-Transistortypen

Pinbelegung

interne Schaltung

D

D

NMOS−Transistor

IRFD014

G

G

S

Schutzdiode

(Bei korrekter

Beschaltung

gesperrt)

S

D

D

PMOS−Transistor

IRFD9024

G

G

S

S

und der integrierte Schaltkreis HEF4011 mit 4 NAND-Gattern

einzelnes CMOS−

NAND−Gatter

Anschlussbelegung der 4 Gatter

5V

1 (A1)

&

Yi

Ai

Bi

8 (A3)

3 (Y1)

&

2 (B1)

10 (Y3)

Gehäuse

14

5V

9 (B3)

13

12

11

10

A4

B4

Y4

Y3

9

B3 A3

HEF4011 (4 NAND)

6 (A2)

&

13 (A4)

4 (Y2)

&

11 (Y4)

12 (B4)

5 (B2)

A1

B1

Y1

Y2

B2

A2

1

2

3

4

5

6

verwendet.

Aufgabe 5.1:

8

Hausaufgabe

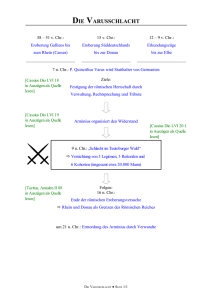

Schätzen Sie für die 4 Schaltungen in Abb. 1 die Übertragungsfunktion

Ua = f (Ue.i )

i ∈ {1, 2, 3, 4}

ab:

NMOS-Transistor: IRFD014, Einschaltspannung 2 V < Uth < 4 V, K ≈ 2 A/V2 ; PMOS-Transistor:

IRFD9024, Einschaltspannung −4 V < Uth < −2V, K ≈ −0, 5 A/V2

Warum sind NMOS-Transistoren besser geeignet, den Ausgang auf Null- und PMOS-Transistoren

besser geeignet, den Ausgang auf Eins zu ziehen?

1

7

2

Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik

5V

NLS

5V

NHS

1 kΩ

Ue =

0...5V

Ue =

0...5V

Ua1

NMOS-Transistor als Low-Side-Schalter

5V

PLS

1 kΩ

Ua2

NMOS-Transistor als High-Side-Schalter

5V

PHS

1 kΩ

Ue =

0...5V

Ue =

0...5V

Ua3

PMOS-Transistor als Low-Side-Schalter

1 kΩ

Ua4

PMOS-Transistor als High-Side-Schalter

Abbildung 1: MOS-Transistoren als Schalter

Aufgabe 5.2

Bauteile:

Widerstand 1 kΩ, NMOS-Transistor: IRFD014, PMOS-Transistor: IRFD9024

Überprüfen Sie Ihre Abschätzung aus der Aufgabe zuvor experimentell mit der Versuchsschaltung

in Abb.2. Die Übertragungsfunktion ist im Bereich von Ue = 0 . . . 5 V zu erstellen1 .

NLS

VP+ (5 V, 20 mA)

1 kΩ

Vref1, Vmtr1

AWG1, DC1

Ue

Ua1

Vmtr2

DC2

VP+ (5 V, 20 mA)

NHS

Vref1, Vmtr1

AWG1, DC1

Vmtr2

Ue 1 kΩ

DC2

Ua2

NMOS-Transistor als Low-Side-Schalter NMOS-Transistor als High-Side-Schalter

PLS

VP+ (5 V, 20 mA)

1 kΩ

Vref1, Vmtr1

AWG1, DC1

Ue

Ua3

Vmtr2

DC2

PHS

VP+ (5 V, 20 mA)

Vref1, Vmtr1

AWG1, DC1

Vmtr2

DC2

Ue 1 kΩ

Ua4

PMOS-Transistor als Low-Side-Schalter PMOS-Transistor als High-Side-Schalter

für Einzelmessung

mit AWG und Oszi

Abbildung 2: Messschaltungen

1 Wie

auf dem vorherigen Aufgabenblättern dürfen Sie die Übertragungsfunktion entweder mit Einzelmessungen

oder mit dem Signalgenerator und dem Oszilloskop bestimmen. In beiden Fällen müssen Sie bei der Abnahme das

exportierte Datenle und das m-Skript zur Erzeugung des Matlab-Plots vorweisen können. Vergessen Sie nicht, im

Fenster Power Supplies and Voltmeter für VP+ eine Spannung von 5 V und eine Strombegrenzung von 20 mA

einzustellen und die Quelle zu aktivieren.

3

Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik

Aufgabe 5.3

Bauteile:

Schaltkreis HEF4011

Bestimmen Sie mit dem Versuchsaufbau in Abb. 3 die Übertragungsfunktion eines NAND-Gatters

und stellen Sie diese mit Matlab graphisch dar.

VP+ (5 V, 20 mA)

14

1 (A1)

Vref1, Vmtr1

AWG1, DC1

2 (B1)

7

Ue

Vmtr2

DC2

3 (Y1)

&

zu nutzende Anschlüsse

des Electronics Explorers

für Einzelmessung

mit AWG und Oszi

Ua

Abbildung 3: Messschaltung zur Bestimmung der Übertragungsfunktion eines NAND-Gatters

Aufgabe 5.4

Bauteile:

Schaltkreis HEF4011

Bauen Sie aus NAND-Gattern die Schaltung in Abb. 4 auf:

VP+ (5 V, 20 mA)

14

13 (A4)

Vref1, Vmtr1

Ue1

12 (B4)

1 (A1)

2 (B1)

&

&

11 (Y4)

9 (B3)

3 (Y1)

8 (A3)

5 (B2)

6 (A2)

Vref2, Vmtr2

&

4 (Y2)

&

10 (Y3)

Ua

7

Ue2

Abbildung 4: Test einer Logikschaltung

Bestimmen Sie die logische Funktion, indem Sie nachfolgende Tabelle ausfüllen:

Ue1

Ue2

Ua

0

0

5V

0

0

5V

5V

5V

Vmtr3

Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik

4

Aufgabe 5.5

Bauteile:

Schaltkreis HEF4011, 2 Widerstände 1 kΩ, 2 Leuchtdioden rot

Bauen Sie aus NAND-Gattern die Schaltung in Abb. 5 auf:

VP+ (5 V, 20 mA)

14

1 (A1)

Vref1, Vmtr1

Ux1

2 (B1)

&

Vmtr3

1 kΩ

Uy1

5 (B2)

6 (A2)

Vref2, Vmtr2

3 (Y1)

&

Ux2

1 kΩ

4 (Y2)

Uy2

7

Vmtr4

Abbildung 5: Test eines RS-Flipops

Bestimmen Sie die logische Funktion, indem Sie nachfolgende Tabelle ausfüllen:

Ux1

Ux2

Uy1

Uy2

5V

5V

5V

0

5V

5V

0

5V

5V

5V

0

0

0

5V

Was passiert, wenn beide Eingänge gleichzeitig von 0 nach 5 V wechseln? Tritt immer derselbe

Folgezustand auf oder ist der Folgezustand Zufall?

Abnahmekriterien

Aufgabe 5.1:

Vier plausible Übertragungsfunktionen Ua = f (Ue.i ) als Skizzen.

Vier plausible Übertragungsfunktionen jeweils als Matlab- oder WaveForms-Bild

und als Skizze mit beschrifteten Achsen.

Aufgabe 5.2:

Eine plausible Übertragungskennlinie als Matlab- oder WaveForms-Bild und als

Skizze mit beschrifteten Achsen.

Aufgabe 5.3:

Aufgabe 5.4:

Ausgefüllte Tabelle.

Aufgabe 5.5:

Ausgefüllte Tabelle, beantwortete Frage.

Die Teilnehmer sagen, welche Aufgaben sie gelöst haben. Der Hilfswissenschaftler führt Stichprobenkontrollen zu den als fertig gemeldeten Aufgaben durch.

Logiktest (Zusatzaufgaben für Interessierte)

Abb. 6 zeigt eine Schaltung aus den vier Gattern eines HEF 4011, angeschlossen an den digitalen

Ein-/Ausgängen (DIO's) des Electronics Explorers und einen Vorschlag für den Aufbau auf dem

Steckbrett.

Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik

5

Vcc

SW

SW

SW

SW

SW

DIO2

&

DIO3

DIO6

2

5

3

9

14

&

&

DIO7

DIO8

HEF 4011 DIO4

1

4

8

10

DIO1

13

&

7

6

SW

Schalter in Static I/O

LED

Leuchtdiode in Static I/O

12

11

DIO0

DIO5

LED

LED

LED

LED

a)

b)

Abbildung 6: Testschaltung für den Logiktest a) Schaltplan b) Steckbrettaufbau

Statischer Test

Ein statischen Test kontrolliert die logische Funktion ohne Berücksichtigung potentieller Probleme

durch Signalverzögerungen. In jedem Testschritt werden Eingabewerte eingestellt (z.B. mit Schaltern) und die Ausgaben überprüft (z.B. mit Leuchtdioden). Das lässt sich mit WaveForms im

Static-I/O-Fenster nachbilden (zu önen mit dem Icon Static I/O). Für die Beispielschaltung

sind DIO 2, DIO 3, DIO 6, DIOv7 und DIO 8 wie in Abb. 6 als Schalter zu kongurieren (rechte

Maustaste > Push/Pull Switch). DIO 0, DIO 1, DIO 4 und DIO 5 sind als Leuchtdioden zu belassen. Der Test besteht aus Schalterwerte einstellen und Ausgabewerte protokollieren bzw. mit

Sollwerten vergleichen.

Abbildung 7: Konguration des Static-I/O-Fensters für die Testschaltung in Abb. 6

Aufgabe 5.6

Bauen Sie die Beispielschaltung wie im Foto in Abb. 6 auf. Kongurieren Sie das Static-I/OFenster wie in Abb. 7. Aktivieren Sie im Fenster Power Supplies and Voltmeter die Quelle Vcc.

Führen Sie die Tests durch und füllen Sie die nachfolgende Tabelle aus:

6

Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik

DIO 2

0

1

1

1

1

1

0

0

0

0

DIO 3

0

0

1

1

1

1

1

0

0

0

DIO 6

0

0

0

1

1

1

1

1

0

0

DIO 7

0

0

0

0

1

1

1

1

1

0

DIO 8

0

0

0

0

0

1

1

1

1

1

DIO 0

DIO 1

DIO 4

DIO 5

Test mit Logikgenerator und Logikanalysator

Ein Logikgenerator stellt Folgen digitale Eingabesignale bereit und ein Logikanalysator zeichnet

digitale Signalfolgen auf. Der Electronics Explorer hat 32 digitale Anschlüsse, die wahlweise als

static I/O's, als Logikgeneratorausgänge oder als Logikanalysatoreingänge genutzt werden können.

Das Logikgeneratorfenster wird über die Schaltäche Pattern in der Spalte Digital geönet.

Für das Beispiel sind im Logikgenerator-Fenster

Eingabebus denieren: Add > Bus > Name: Eing; DIO 2, DIO 3, DIO 6, DIO 7, DIO 8 nach

Selected; Format Hexadecimal; ok;

Korrektur: Bus Eing auswählen > Edit > Edit Proporties of "Eing"

Eingabedaten festlegen: Bus Eing auswählen > Edit > Edit Parameters of "Eing" > Type

Johnson Counter2 ; Optput: PP; Idle: Low; Frequency: 1 kHz

Abspielfenster: Run: 10ms; Show: 1 ms/div (Abb. 8).

Abbildung 8: Kongurationsfenster des Logikgenerators

Das Logikanalysatorfenster wird über die Schaltäche Anaylzer in der Spalte Digital

geönet. Für das Beispiel sind im Logikanalysatorfenster folgende Kongurationen vorzunehmen

(Abb. 9):

Eingabebus denieren: Add > Bus > Name: Eing; DIO 2, DIO 3, DIO 6, DIO 7, DIO 8 nach

Selected; Format Hexadecimal; ok;

2 Ein

Johnson

Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik

7

Abbildung 9: Kongurations- und Aufzeichnungsfenster des Logikanalysators

Ausgabebus denieren: Add > Bus > Name: Ausg; DIO 0, DIO 1, DIO 4, DIO 5 nach Selected;

Format Hexadecimal; ok;

Aufzeichnungsbeginn bei Start des Signalgenerators: Source: Patterns

Darstellungszeit 0 bis 10 ms ab Start: Base: 1 ms/div; Pos: 5 ms.

Aufzeichnung:

im Logikanalysator-Fenster Button Single betätigen.

Warten bis der Triggerzustand von Ready auf Armed (scharf) wechselt.

Im Logikgeneratorfenster Button Run betätigen.

Warten bis der Triggerzustand über Trig'd auf Done wechselt.

Zur Untersuchung der Verzögerungszeiten ist der Test wesentlich schneller durchzuführen, z.B.

Mit einem Takt von 1 MHz statt 1 kHz. Dazu im Logikgeneratorfenster umstellen:

Generatortakt: Bus Eing auswählen > Edit > Edit Parameters of "Eing" > Frequency:

1 MHz

Anzeigefenster anpassen: Run 10 µs, Show: 1 µs/div

Im Logikanalysator ist auch das Zeitfenster umstellen: Base: 1 µs/div; Pos: 5 µs.

Abb. 10 zeigt den so aufgezeichneten Signalverlauf, in dem die Ausgabeänderungen sichtbar

gegenüber den Eingabeänderungen verzögert sind. Diese Verzögerungen lassen sich mit einem

Zoom-Fenster vergröÿern (Button Zoom betätigen). In dem Foto des Zoom-Fensters in Abb. 11 ist

ablesbar, dass aller 10 nS ein Wert abgetastet wurde und dass die Änderung an DIO 4 gegenüber

Prof. G. Kemnitz: Übungsaufgaben zur Einführung in die Elektronik

8

Abbildung 10: Schnelle Datenaufzeichnung

der an DIO 3 um 6 Abtastzeiten, d.h. 60 ns und DIO 1 gegenüber DIO 3 um 9 Abtastzeiten, d.h.

90 ns verzögert ist. Um die Verzögerung genauer zu bestimmen, muss mit einer noch höheren

Taktfrequenz getestet werden.

Abbildung 11: Zoom-Fester zu Abb. 10

Aufgabe 5.7

Führen Sie für die aufgebaute Beispielschaltung die beschriebenen Tests mit dem Logikgenerator und -analysator durch. Kontrollieren Sie, dass die logischen Ausgaben in jedem Testschritt

mit denen aus der vorherigen Aufgabe übereinstimmen. Bestimmen Sie die Verzögerung von der

fallenden Flanke an DIO 6 zu den nachfolgenden Signalwechseln an DIO 0, DIO 1 und DIO 5.