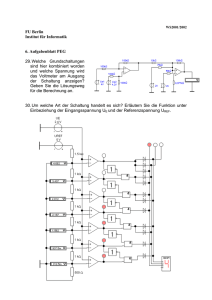

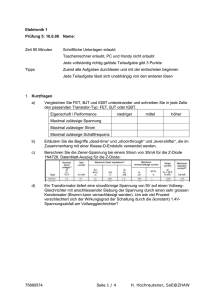

Digitalelektronik - Justus-Liebig

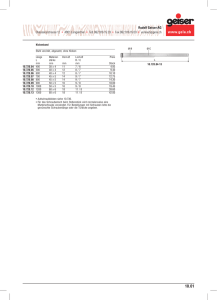

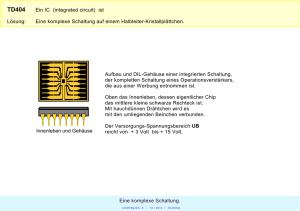

Werbung