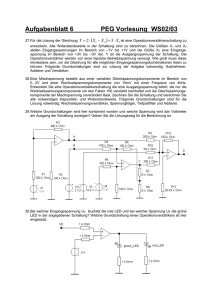

FU Berlin Institut für Informatik 6. Aufgabenblatt PEG 29. Welche

Werbung

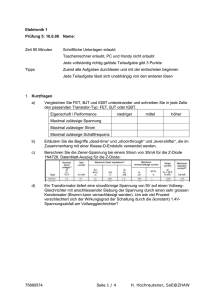

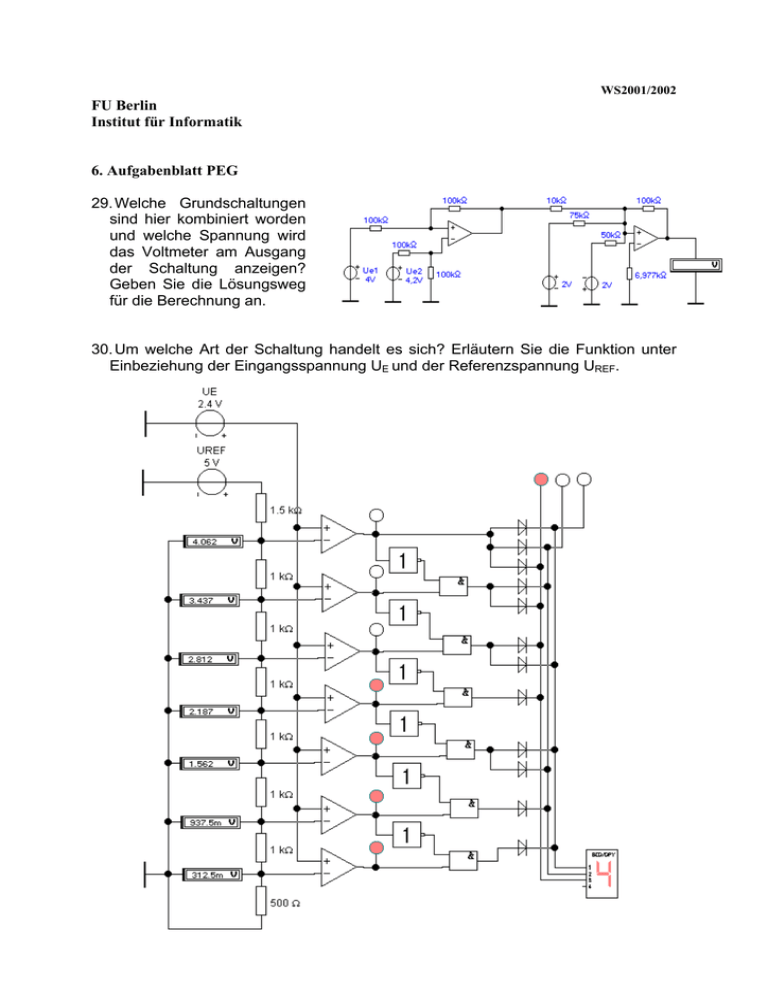

WS2001/2002 FU Berlin Institut für Informatik 6. Aufgabenblatt PEG 29. Welche Grundschaltungen sind hier kombiniert worden und welche Spannung wird das Voltmeter am Ausgang der Schaltung anzeigen? Geben Sie die Lösungsweg für die Berechnung an. 30. Um welche Art der Schaltung handelt es sich? Erläutern Sie die Funktion unter Einbeziehung der Eingangsspannung UE und der Referenzspannung UREF. 31. Die Gattersignallaufzeit der Inverter beträgt 2ns und des EXOR-Gatters 6 ns. Für die abgebildete Schaltung sind die Spannungsverläufe an den Knotenpunkten A2 und A3 in Abhängigkeit vom dargestellten Eingangssignal A1 in das Diagramm einzutragen. 32. Ein Logikgatter der HCT-Familie wird mit seinem Eingang an den Ausgang eines Std-TTL-Gatters angeschlossen. Wie groß ist der statische Störabstand in Volt für ein Low und ein High am Ausgang des TTL-Gatters? Schraffieren Sie die entsprechenden Bereiche im Diagramm. Wie verändert sich die Situation, wenn der Eingang eines Std-TTL Gatters an den Ausgang eines HCT-Gatters angeschlossen wird? Pegel der Schaltkreisfamilien: HCT UIL UIH UOL UOH =0,8 V =2,0 V =0,4 V =3,5 V Std-TTL UIL =0,8 UIH =2,0 V UOL =0,4 V UOH =2,4 V 33. Vervollständigen Sie die Schaltungen so, dass die in den Flächen genannten Logikfunktionen realisiert werden. Bezeichnen Sie die notwendigen Anschlüsse für die Betriebsspannung (+5V) und Masse (0V). 34. Welche Grundschaltung ist hier dargestellt? Erläutern Sie die Funktion der Schaltungen unter Nutzung einer Wahrheitstabelle für die Eingangsgrößen A, B und CS und die Ausgangsgröße Y. 35. Entwickeln Sie unter Nutzung einer Wahrheitstabelle die Schaltung für einen Vergleicher (2 Bit Datenbreite). Die möglichen Zustände A>B, A<B und A=B sollen an den Ausgängen Y1, Y2 und Y3 signalisiert werden. A0 A1 B0 B1 Y1 (A>B) Logik Y3 (A<B) A B C D 36. Entwickeln Sie aus JK-Flip-Flops mit integrierten Setz- und Rücksetzeingängen ein 4 Bit breites Schieberegister mit Paralleleingabe und Serienausgabe. R Setzen des Schieberegisters Datenbits der Eingabe Datenbit der Ausgabe Rücksetzen des Schieberegisters Takteingang Y P IS O R e g is te r T S A,B,C,D Y R T Y2 (A=B) S 37. Die abgebildete Schaltung arbeitet fehlerhaft. Messtechnisch wurde eine Tabelle der Verknüpfungen aufgenommen. Bestimmen Sie welche Logikglieder nicht oder fehlerhaft funktionieren. C 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 /A 1 0 1 0 1 0 1 0 /C 1 1 1 1 0 0 0 0 38. Entwickeln Sie die Gleichungen für die GAL-Programmierung eines Hexadezimal Siebensegmentdecoders. Nutzen Sie die vorgegebene PIN - Belegung. Bei LT=1 sollen alle Segmente leuchten, d.h. A-G sollen auf Logikpegel 1 liegen. Bei LT=0 werden nur die Segmente A-G entsprechend der Zahl die durch D0-D3 kodiert wird angesteuert. Die Zuordnung der Segmente A-G ist der Abbildung zu entnehmen. X 1 1 1 1 1 1 0 0 Y 1 1 1 0 1 0 1 0 F E K 1 1 1 1 1 1 1 0 A G Q 1 0 1 0 1 0 1 0 B C D GAL20V8 - PIN-Belegung Bez. VCC PIN 24 PIN 1 Bez. D0 NC 23 2 D1 A 22 3 D2 B 21 4 D3 C 20 5 NC D 19 6 NC E 18 7 NC F 17 8 NC G 16 9 NC NC 15 10 NC NC 14 11 LT NC 13 12 GND