ЗК№ × ЦШ ДУ ЧЭТШ × С Ш ГЦУТ Ц ЩТ Ш УТ Р × УТ Ц СЧ

Werbung

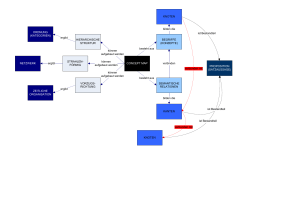

EXOR-basierte Logiksynthese

mit

Kronecker Functional Decision Diagrams

Dissertation

zur Erlangung des Doktorgrades

der Fakult

at fu

r Angewandte Wissenschaften

der Albert-Ludwigs-Universit

at,

Freiburg im Breisgau

vorgelegt von

Harry Hengster

Freiburg im Breisgau

Dekan

Prof. Dr.Gerald A. Urban

Referenten

Prof. Dr. Bernd Becker

Prof. Dr. Paul Molitor

Tag der Disputation

12. 03. 2001

Fu

r meine Frau Heike

sowie

meine T

ochter Yasmin und Sarah.

ii

Danksagung

Allen Personen, die einen Beitrag zum erfolgreichen Abschlu dieser Arbeit geleistet

haben, mochte ich herzlich danken.

Prof. Dr. Bernd Becker danke ich sowohl fur die umfassende Betreuung dieser Arbeit

als auch dafur, da er mich bereits wahrend meines Studiums fur die spannenden Themen und interessanten Probleme bei dem Entwurf und Test von integrierten Schaltkreisen

begeistern konnte. Meine wissenschaftliche Arbeit unterstutzte er durch zahlreiche Diskussionen, in denen er nicht nur wertvolle Hinweise zur Losung von verschiedenen Problemen

einbrachte, sondern auch weiterfuhrende Fragestellungen aufzeigte. Insbesondere fur seine

Beharrlichkeit bei den formalen Beweisen zur Testbarkeit bin ich ihm heute sehr dankbar.

Mein besonderer Dank gilt allen Mitarbeitern, ehemaligen Mitarbeitern und Studenten,

die am Lehrstuhl Algorithmen und Datenstrukturen entwickelt sowie die entsprechenden

Programme implementiert haben. Insbesondere aus der von Diplom-Informatiker Stefan

Eckrich und Diplom-Informatikerin Tonja Pfeier erstellten Basisimplementierung konnte

ich zahlreiche Algorithmen und Programmsegmente fur die Realisierung des Syntheseverfahrens ubernehmen. Fur die sehr gute Unterstutzung bei Implementierungsfragen,

die groe Hilfsbereitschaft bei der Anpassung von verschiedenen Software-Komponenten

und die zahlreichen Diskussionen mochte ich mich besonders bei Dr. Christoph Scholl,

Diplom-Informatiker Andreas Hett und Diplom-Informatiker Martin Keim bedanken.

Zu besonderem Dank bin ich den unermudlichen Korrekturlesern Dr. Christoph Scholl und

Diplom-Volkswirtin Heike Hengster verpichtet, denen es durch ihre sorgfaltige Arbeit

gelang, mich durch die Vielzahl der im Manuskript aufgefundenen Mangel in Erstaunen

zu versetzen.

Weiterhin mochte ich mich bei meiner Frau und meinen beiden Tochtern bedanken, die

mir durch ihre Liebe immer wieder neue Kraft gaben, obwohl sie mich leider auch an

vielen Abenden und Wochenenden entbehren muten.

iii

Inhaltsverzeichnis

Einleitung

1

1 Grundlagen

5

1.1 Boolesche Funktionen . . . . . . . . . . . . . . .

1.2 Schaltkreise . . . . . . . . . . . . . . . . . . . .

1.3 Decision Diagrams . . . . . . . . . . . . . . . .

1.3.1 Allgemeine Decision Diagrams . . . . . .

1.3.2 Kronecker Functional Decision Diagrams

1.3.3 Reduktionen . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

2.1 Funktionsdarstellung durch Abhangigkeiten im KFDD . . . . . . .

2.1.1 Aktive Pfade und Abhangigkeiten zwischen Knoten . . . . .

2.1.2 Abhangigkeiten aufeinanderfolgender Level . . . . . . . . . .

2.1.3 Komposition von Abhangigkeiten . . . . . . . . . . . . . . .

2.2 EXOR-basiertes Syntheseverfahren . . . . . . . . . . . . . . . . . .

2.2.1 Schaltkreisrealisierung der Abhangigkeitsmatrizen . . . . . .

2.2.2 Schaltkreisoptimierung mit lokalen Vereinfachungen . . . . .

2.2.2.1 Gatter mit konstanten Eingangssignalen . . . . . .

2.2.2.2 Gatter mit gleichen oder inversen Eingangssignalen

2.2.2.3 Inverterketten . . . . . . . . . . . . . . . . . . . . .

2.2.2.4 Anwendbarkeit in synthetisierten Schaltkreisen . .

2.2.2.5 Angepates Syntheseverfahren . . . . . . . . . . . .

2.2.3 Groenreduktion der KFDDs . . . . . . . . . . . . . . . . .

2.2.3.1 D-vollstandige KFDDs . . . . . . . . . . . . . . . .

2.2.3.2 Abhangigkeiten in D-vollstandigen KFDDs . . . .

2.2.3.3 Verallgemeinertes Syntheseverfahren . . . . . . . .

2.3 Experimentelle Ergebnisse . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 Erzeugte Decision Diagrams . . . . . . . . . . . . . . . . . .

2.3.2 Synthetisierte Schaltkreise . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

2 Logiksynthese mit KFDDs

iv

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

5

6

12

13

17

20

29

29

30

35

36

41

41

45

45

48

50

51

57

61

62

67

70

77

78

83

3 Testbarkeit der Schaltkreise

3.1 Stuck-at Fehler . . . . . . . . . . . . . . . . . . . . . .

3.2 Konstante Signale . . . . . . . . . . . . . . . . . . . . .

3.2.1 Konstante 0-Abhangigkeiten . . . . . . . . . . .

3.2.2 Konstante 1-Abhangigkeiten . . . . . . . . . . .

3.2.3 Angepates Syntheseverfahren . . . . . . . . . .

3.3 Bestimmung von Belegungen fur aktive Pfade . . . . .

3.3.1 Belegung fur genau einen aktiven Pfad . . . . .

3.3.2 Belegung fur eine gerade Anzahl aktiver Pfade .

3.4 Vollstandige Testbarkeit . . . . . . . . . . . . . . . . .

3.4.1 Fehler an primaren Eingangen . . . . . . . . . .

3.4.2 Fehler an Eingangen der Teilschaltkreise . . . .

3.4.3 Fehler an Eingangen der AND-Gatter . . . . . .

3.4.4 Fehler an primaren Ausgangen . . . . . . . . . .

3.4.5 Komplexitat der vollstandigen Testberechnung .

3.5 Experimentelle Ergebnisse . . . . . . . . . . . . . . . .

4 Optimierungen

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

4.1 Optimierung des vollstandigen Tests . . . . . . . . . . . . .

4.1.1 Fehlersimulation . . . . . . . . . . . . . . . . . . . .

4.1.2 Statische Kompaktierung . . . . . . . . . . . . . . . .

4.1.2.1 Entfernen von generalisierten Testmustern .

4.1.2.2 Kombination von kompatiblen Testmustern

4.1.3 Experimentelle Ergebnisse . . . . . . . . . . . . . . .

4.2 Optimierung der synthetisierten Schaltkreise . . . . . . . . .

4.2.1 Verschmelzen aquivalenter Gatter . . . . . . . . . . .

4.2.2 Experimentelle Ergebnisse . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

86

. 87

. 92

. 94

. 96

. 103

. 104

. 105

. 110

. 116

. 119

. 132

. 139

. 146

. 152

. 153

157

. 157

. 158

. 158

. 160

. 161

. 164

. 166

. 166

. 170

5 Vergleich mit anderen Verfahren

173

6 Schlubemerkungen

181

Literaturverzeichnis

183

5.1 Knotenersetzung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

5.2 SIS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

5.3 Automatische Testmustergenerierung . . . . . . . . . . . . . . . . . . . . . 178

Anhang

187

A Zur Groe DnB -vollstandiger KFDDs

187

B Verallgemeinertes Syntheseverfahren

197

v

Einleitung

Der gesamte Entwicklungsproze eines neuen Chips wird durch Computer-Aided Design

(CAD) Werkzeuge unterstutzt1 . Die Aufgaben der CAD-Werkzeuge umfassen einerseits

die Organisation und Verwaltung der einzelnen Arbeitsergebnisse, die sehr umfangreich

und komplex sein konnen. Andererseits mussen die relevanten Informationen fur die einzelnen Arbeitsschritte extrahiert und aufbereitet werden, um eine einfache und komfortable Nutzung durch die Entwickler zu ermoglichen. Aufgrund der hohen Komplexitat und

den kurzen Entwicklungszyklen wird fur die einzelnen Entwicklungsphasen ein moglichst

hoher Automatisierungsgrad angestrebt. In vielen Bereichen ist heute noch sehr viel Interaktion durch die Entwickler notig, um Teilaufgaben uberhaupt losen zu konnen bzw.

um entsprechende Qualitatsanforderungen zu erfullen. Fur andere Entwicklungsschritte

sind die Verfahren bereits soweit fortgeschritten, da die Rolle des Entwicklers darauf

reduziert werden kann, die notigen Eingabeparameter festzulegen und das automatisch

erzeugte Resultat zu uberprufen und zu bewerten.

In dem Gesamtentwicklungsproze umfat der Schritt der Logiksynthese die Aufgabe, eine gegebene Boolesche Funktion durch Verknupfung einzelner Logikbausteine zu

realisieren. Es gibt eine Vielzahl von unterschiedlichen Methoden fur die Logiksynthese, mit denen einerseits unterschiedliche Eigenschaften der einzusetzenden Technologie

berucksichtigt werden und andererseits verschiedene Optimierungsziele beachtet werden

mussen.

Bei Schaltkreisen, die als Programmable Logic Array (PLA) gefertigt werden, ist z.B. zu

berucksichtigen, da nur zweistuge Schaltkreise realisiert werden konnen. Um die Kosten

zu minimieren, mu bei PLAs im wesentlichen die Anzahl der Monome optimiert werden.

Dagegen konnen fur mehrstuge Schaltkreise verschiedene Grundgatter zur Realisierung

von unterschiedlichen Operationen in mehreren Stufen hintereinander geschaltet werden.

Dabei werden die Kosten im wesentlichen durch die Anzahl der verwendeten Grundgatter

und deren jeweilige Groe bestimmt. Bei der Synthese von mehrstugen Schaltkreisen mu

zusatzlich berucksichtigt werden, da die Anzahl und die Typen von Grundgattern auf

einem Pfad von einem Eingang zu einem Ausgang des Schaltkreises die Verzogerungszeit

des Schaltkreises und damit die maximal mogliche Taktfrequenz beeinut. Das Verhaltnis von Groe und Verzogerungszeit kann fur die Grundgatter in verschiedenen Technologien unterschiedlich sein. So benotigt eine CMOS-Realisierung fur ein EXOR-Gatter

wesentlich mehr Platz und hat eine deutlich hohere Verzogerungszeit als ein OR-Gatter.

Dagegen gibt es Field Programmable Gate Arrays (FPGAs), in denen EXOR-Gatter und

OR-Gatter mit gleicher Flache und Verzogerungszeit realisiert werden konnen.

Neben der Groe und der Verzogerungszeit gilt es insbesondere bei elektronischen Komponenten fur mobile Gerate auch noch die Leistungsaufnahme zu minimieren. Dazu konnen

1 In der gesamten Arbeit werden h

aug die aus der Literatur bekannten englischen Begrie bzw. deren

Abkurzungen verwendet.

1

2

EINLEITUNG

z.B. Realisierungen bestimmt werden, bei denen die Schaltwahrscheinlichkeit der einzelnen Gatter gering ist. Oder es kann zusatzliche Kontrollogik eingefugt werden, mit der

bestimmte Teile einer Schaltung vorubergehend deaktiviert werden konnen.

Schlielich entsteht ein groer Anteil der Kosten fur einen Chip durch die Entwicklung

und die Durchfuhrung des Produktionstests, bei dem die fehlerhaften Chips identiziert

werden sollen. Dazu wird mittels automatischer Testmustergenerierung eine Menge

von Testmustern bestimmt. Jedes dieser Testmuster wird an die Eingange der Chips angelegt und die Ausgabe der Chips mit den erwarteten Resultaten verglichen. Fur den

Produktionstest sollen einerseits moglichst wenige Testmuster notig sein, da dieser Test

fur jeden produzierten Chip durchgefuhrt werden mu und das Testequipment sehr teuer

ist. Andererseits sollen durch den Produktionstest moglichst alle defekten Chips aussortiert werden, da ein defekter Chips nach der Integration in ein komplexeres System oder

gar nach der Auslieferung an den Endkunden enorme Kosten sowie einen Imageverlust

verursacht.

Es gibt zwar Verfahren zur automatischen Testmustergenerierung. Allerdings kann die

Laufzeit dieser Verfahren bei ungunstigen Schaltkreisstrukturen sehr hoch werden. Ein

weiteres Optimierungskriterium fur Synthesewerkzeuge besteht also darin, eine moglichst

gute Testbarkeit zu erreichen. Dies kann einerseits durch Vermeiden von ungunstigen

Struktureigenschaften erreicht werden, so da problematische Konstellationen fur die automatische Testmustergenerierung vermieden werden. Andererseits kann bei einigen Verfahren bereits wahrend der Synthese eine Testmenge fur den Schaltkreis erzeugt werden,

ohne automatische Testmustergenerierung anwenden zu mussen.

In vielen CAD-Werkzeugen und insbesondere in Syntheseverfahren werden Decision

Diagrams (DDs) eingesetzt. DDs sind graphbasierte Datenstrukturen, die zur eÆzienten Reprasentation und Manipulation von Booleschen Funktionen entwickelt wurden. In

den Kronecker Functional Decision Diagrams (KFDDs) [23] konnen sowohl die Shannon Dekomposition als auch die Davio Dekompositionen angewendet werden. Damit

stellen KFDDs eine Verallgemeinerung der weit verbreiteten Binary Decision Diagrams

(BDDs) [38, 2, 15] und der Funktional Decision Diagrams (FDDs) [36] dar und konnen

die Vorteile dieser beiden Darstellungsformen vereinen.

Die Graphstruktur von DDs kann aber auch direkt dazu verwendet werden, um Schaltkreisrealisierungen fur die dargestellten Funktionen abzuleiten. Dabei werden Eigenschaften der Graphstruktur des DDs ausgenutzt. Einige Syntheseverfahren nutzen besondere

Eigenschaften von BDDs aus, so da der Einsatz von KFDDs Erweiterungen dieser Verfahren erfordert oder KFDDs uberhaupt nicht eingesetzt werden konnen. Sofern der Einsatz von KFDDs fur ein Syntheseverfahren moglich ist, resultieren aus der kompakteren

Darstellung als KFDD normalerweise auch bessere Schaltkreisrealisierungen.

In [35] wurde z.B. ein Verfahren vorgestellt, bei dem die Abhangigkeiten zwischen den

Knoten aus aufeinanderfolgenden Leveln eines BDDs analysiert werden. Dabei konnen nur

Abhangigkeiten zwischen Knoten aus aufeinanderfolgenden Leveln berucksichtigt werden.

Deshalb mussen zur Vorbereitung der eigentlichen Synthese zunachst neue Knoten in

dem BDD eingefugt werden, bis ein vollstandiges BDD erzeugt wurde. Dann konnen die

Abhangigkeiten zwischen den Knoten durch Teilschaltkreise mit einer einfachen Struktur

realisiert werden. Die einzelnen Teilschaltkreise werden durch weitere Teilschaltkreise zu

dem Gesamtschaltkreis zusammengesetzt, wobei die Struktur der neuen Teilschaltkreise

wiederum sehr einfach und regelmaig ist. Durch die Komposition der Teilschaltkreise

als balancierten, binaren Baum wird eine geringe Verzogerungszeit fur den mehrstugen

Gesamtschaltkreis erreicht. Auerdem sind in dem synthetisierten Gesamtschaltkreis alle

EINLEITUNG

3

und path-delay Fehler testbar, sofern 2-rail Logik verwendet wird. Dafur mu

jedoch die Anzahl der Eingange und Ausgange des Schaltkreises verdoppelt werden, was

fur den praktischen Einsatz nicht akzeptabel ist.

Auch das in dieser Arbeit vorgestellte Syntheseverfahren beruht auf der Grundidee

von [35]. Das Verfahren zur Analyse der Abhangigkeiten wird einerseits von BDDs auf

KFDDs erweitert. Somit konnen die kompakteren Darstellungen der Booleschen Funktionen als KFDD verwendet werden. In KFDDs wird neben der Shannon Dekomposition auch

die Davio Dekomposition eingesetzt, die auf der EXOR-Operation basiert. Daher wird

die Verwendung von EXOR-Gattern in den synthetisierten Schaltkreisen auf naturliche

Weise impliziert.

Daneben wird eine Reihe von lokalen Vereinfachungen fur die Schaltkreisrealisierung vorgestellt, die wahrend der Synthese implizit durchgefuhrt werden konnen. Dadurch wird die

Groe weiter optimiert sowie eine geringe Tiefe und damit eine geringe Verzogerungszeit

fur den Schaltkreis erreicht.

Zusatzlich wird gezeigt, da auch direkte Abhangigkeiten zwischen Knoten aus nicht benachbarten Leveln unmittelbar in der Schaltkreisrealisierung umgesetzt werden konnen,

so da fur das Syntheseverfahren keine vollstandigen KFDDs mehr benotigt werden. Die

fur das verallgemeinerte Syntheseverfahren notigen Anforderungen an die Struktur des

KFDDs konnen mit erheblich weniger Knoten erfullt werden als in dem Verfahren, bei

dem nur Abhangigkeiten zwischen Knoten aus benachbarten Leveln berucksichtigt werden

konnen. Die synthetisierten Schaltkreisrealisierungen sind bei beiden Verfahren gleich, sofern die oben erwahnten Vereinfachungen wahrend der Synthese konsequent durchgefuhrt

werden. Somit kann der Vorteil der eÆzienteren Darstellung des KFDDs genutzt werden

ohne die Qualitat der synthetisierten Schaltkreise zu beeinussen.

Die Testbarkeit der synthetisierten Schaltkreise wird bzgl. des stuck-at Fehlermodells

untersucht. Durch Analyse der Graphstruktur des verwendeten KFDDs mit eÆzienten

Graphalgorithmen kann erreicht werden, da in den erzeugten Schaltkreisen keine konstanten Signale existieren. Fur die so erzeugten Schaltkreise wird gezeigt, da sie auch

ohne den Einsatz der aufwendigen 2-rail Logik vollstandig testbar sind. Dazu werden

Verfahren vorgestellt, mit denen Testmuster fur alle stuck-at Fehler bereits wahrend der

Synthese bestimmt werden. Dabei werden wieder eÆziente Graphalgorithmen eingesetzt,

die jeweils auf die Graphen der KFDDs angewendet werden. Die Anwendung von automatischer Testmustergenerierung fur die synthetisierten Schaltkreise ist somit nicht mehr

erforderlich. Allerdings ist die Anzahl der erzeugten Testmuster sehr hoch, so da eine

Kompaktierung der erzeugten Testmengen notig wird.

Schlielich wird noch gezeigt, da die Groe und Tiefe der synthetisierten Schaltkreise durch Verschmelzen von aquivalenten Gattern weiter reduziert werden kann. Fur die

dabei erzeugten Schaltkreise kann die vollstandige Testbarkeit jedoch nur experimentell

nachgewiesen werden.

Die Arbeit ist folgendermaen gegliedert:

In Kapitel 1 werden Begrie, Verfahren und Datenstrukturen zur Beschreibung von Booleschen Funktionen eingefuhrt. Als Darstellungsformen fur Boolesche Funktionen werden

Schaltkreise und Decision Diagrams genauer betrachtet.

Das grundlegende Syntheseverfahren wird in Kapitel 2 vorgestellt. Dazu wird zunachst

beschrieben, wie eine Boolesche Funktion durch die Abhangigkeiten in einem KFDD dargestellt werden kann. In dem Syntheseverfahren werden fur diese Abhangigkeiten mehrstuge Schaltkreise mit AND-, OR-, EXOR- und NOT -Gattern erzeugt. Die Groe

der dabei erzeugten Schaltkreise kann durch konsequente Anwendung von lokalen Verstuck-at

4

EINLEITUNG

einfachungen optimiert werden. Durch entsprechende Anpassungen im Syntheseverfahren

werden die anwendbaren lokalen Vereinfachungen bereits wahrend der Synthese implizit

durchgefuhrt. Auerdem wird gezeigt, da das Syntheseverfahren auch auf D-vollstandige

KFDDs erweitert werden kann, wodurch die Groe der KFDDs erheblich reduziert wird,

wahrend die erzeugten Schaltkreisrealisierungen gleich bleiben. In den experimentellen

Ergebnissen werden schlielich die Kenngroen der verschiedenen DDs und der aus den

KFDDs erzeugten Schaltkreisrealisierungen angegeben.

Die Testbarkeitseigenschaften der synthetisierten Schaltkreise werden in Kapitel 3 untersucht. Zunachst wird das in dieser Arbeit betrachtete stuck-at Fehlermodell vorgestellt.

Da stuck-at Fehler an konstanten Signalen nicht testbar sind, wird eine Erweiterung des

Syntheseverfahrens prasentiert, bei der keine konstanten Signale erzeugt werden, und es

werden Methoden angegeben, um fur jeden stuck-at Fehler ein Testmuster zu erzeugen.

Sowohl die Vermeidung von konstanten Signalen als auch die Berechnung der Testmuster basiert auf eÆzienten Algorithmen zur Traversierung der Graphen der verwendeten

KFDDs. Durch experimentelle Ergebnisse wird die praktische Anwendbarkeit und die

EÆzienz der Verfahren bestatigt.

In Kapitel 4 werden Verfahren prasentiert, um die Testmengen und Schaltkreise weiter zu

optimieren. Zur Optimierung der Testmengen konnen neben der Fehlersimulation noch

verschiedene Methoden zur statischen Kompaktierung verwendet werden. In den experimentellen Ergebnissen wird zusatzlich die Kombination der beiden Verfahren untersucht.

Die Optimierung der synthetisierten Schaltkreise basiert auf dem Verschmelzen von aquivalenten Gattern. Dabei kann die vollstandige Testbarkeit der erzeugten Gatter jedoch

nur experimentell nachgewiesen werden.

Ein Vergleich mit anderen Verfahren zur Synthese und Testmustergenerierung erfolgt in

Kapitel 5. Es wird ein Syntheseverfahren betrachtet, das ebenfalls auf KFDDs basiert,

und ein Syntheseverfahren, das keine DDs verwendet. Schlielich wird noch ein ausgereifter Testmustergenerator eingesetzt, um Testmuster fur die synthetisierten Schaltkreise

zu erzeugen. Neben einer kurzen Darstellung der anderen Verfahren werden die jeweils

erzielten Resultate mit den Ergebnissen des vorgestellten Verfahrens verglichen.

In Kapitel 6 erfolgt eine Zusammenfassung und es werden weitere Einsatzmoglichkeiten

und Erweiterungen der vorgestellten Verfahren diskutiert.

Kapitel 1

Grundlagen

Es wird ein U berblick uber die in dieser Arbeit verwendeten Begrie, Verfahren und

Datenstrukturen sowie deren Einordnung in das jeweilige Umfeld gegeben.

Zunachst werden Boolesche Funktionen eingefuhrt. Aus der Vielzahl von moglichen Darstellungsformen fur Boolesche Funktionen werden Schaltkreise und Decision Diagrams

genauer betrachtet.

1.1

Boolesche Funktionen

Bei der Spezikation und dem Entwurf von digitalen Systemen werden nur zwei logische

Werte 0 und 1 betrachtet. Zur Beschreibung des digitalen Verhaltens werden Boolesche

Funktionen verwendet:

Denition 1.1

Sei

IB = f0; 1g.

a) Eine Boolesche Funktion ist eine Abbildung f : IBn ! IBm .

b) IBn;m bezeichnet die Menge der Booleschen Funktionen von IBn nach

IBn;1 wird auch die Kurzschreibweise IBn verwendet.

IBm . Fur

Es gibt eine Vielzahl von Moglichkeiten, das Funktionsverhalten einer Booleschen Funktion darzustellen. Jede dieser Darstellungsformen bringt Vor- und Nachteile mit sich. Eine

sehr einfache Darstellungsform bietet z.B. die Wahrheitstabelle.

Beispiel 1.1

Im folgenden ist die Wahrheitstabelle eines Volladdierers V A 2 IB3;2 gegeben, der fur die

Booleschen Werte a, b und cin deren Summe s und U bertrag cout berechnet (vgl. z.B. [26]):

a b cin s cout

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

5

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

6

KAPITEL 1. GRUNDLAGEN

Die linke Seite der Wahrheitstabelle enthalt alle moglichen Belegungen der Variablen a,

b und cin . Die rechte Seite gibt fur jede Belegung die entsprechenden Funktionswerte fur

die Summe s und den U bertrag cout an.

Die Darstellung einer Funktion aus IBn;m als Wahrheitstabelle benotigt jedoch 2n Zeilen mit jeweils m Eintragen aus IB. Dies ist nur fur Funktionen mit wenigen Eingangen

praktikabel.

Die Bezeichnungen, Notationen und Wahrheitstabellen fur die in dieser Arbeit verwendeten Booleschen Funktionen mit bis zu zwei Variablen und einem Ausgang sind in Abbildung 1.1 zusammengestellt.

C0 C1

0

BUF NOT

x1 x1

x1

1

0 1

0

1

0

1

AND 2 NAND 2 OR2 NOR2 EXOR2

x1 x2 x1 x2 x1 x2 x1 + x2 x1 + x2 x1 x2

1

0

0

0

1

1

0

1

0

1

0

0

0

1

1

1

1

0

0

1

1

1

1

0

0

0

0

1

1

0

Abbildung 1.1: Boolesche Funktionen mit keiner, einer und zwei Variablen

Boolesche Funktionen konnen weiterhin in algorithmischer Form, durch Boolesche Ausdrucke, Schaltkreise, Decision Diagrams usw. beschrieben werden. In dieser Arbeit werden

nur Schaltkreise sowie eine spezielle Form von Decision Diagrams verwendet.

1.2

Schaltkreise

Die Realisierung von elektronischen Systemen erfolgt heute meist durch Halbleiterbausteine modernster Technologien. Um die Struktur von Chips zu beschreiben und deren

Verhalten vorhersagen zu konnen, werden verschiedene Modelle benutzt. Mit Hilfe dieser

Modelle wird von den komplexen physikalischen Wechselwirkungen abstrahiert.

Bei der Beschreibung als Schaltkreise auf Gatterebene werden z.B. einzelne Gatter als

Grundbausteine betrachtet. Fur jedes Gatter wird das logische Verhalten durch eine einfache Boolesche Funktion beschrieben. Die Eigenschaften der einzelnen Gatter sind in

einer Bibliothek zusammengestellt. In einem Schaltkreis werden dann mehrere Gatter

miteinander verschaltet, um komplexere Boolesche Funktionen zu realisieren.

Im folgenden wird ein theoretisches Modell fur Schaltkreise auf Gatterebene beschrieben:

Denition 1.2

Eine Bibliothek Bib ist eine Menge von Grundzellen. Fur jede Grundzelle b

Bib ist gegeben:

der Eingangsgrad din (b) 2 IN.

der Ausgangsgrad dout (b) 2 IN.

die Grundfunktion h : IBdin (b) ! IBdout (b) .

b

2

7

1.2. SCHALTKREISE

Es wird eine Standardbibliothek ST D zugrundegelegt, die folgendermaen deniert ist:

ST D = fC0 ; C1 ; NOT; BUF g [

1

1

1

1

1

[

[

[

[

[

ANDi [

NAND i [

ORi [

NORi [

EXORi

i=2

i=2

i=2

i=2

i=2

Die funktionale Beschreibung der Grundzellen aus ST D ist durch Abbildung 1.2 gegeben. Da die Grundfunktionen ANDi , ORi und EXORi jeweils assoziativ und kommutativ

sind, kann fur die Grundzellen mit Eingangsgrad 2 auf eine Klammerung der Variablen verzichtet werden, und die entsprechenden Wahrheitstabellen konnen mit Hilfe von

Abbildung 1.1 hergeleitet werden.

b

din (b) dout (b)

hb

C0

0

1

0

C1

0

1

1

BUF

1

1

x1

NOT

1

1

x1

ANDi

i

1

x1 x2 : : : xi

NANDi

i

1

x1 x2 : : : xi

ORi

i

1 x1 + x2 + : : : + xi

NORi

i

1 x1 + x2 + : : : + xi

EXORi

i

1 x1 x2 : : : xi

Abbildung 1.2: Grundzellen aus ST D

Um eine beliebige Boolesche Funktion mit den gegebenen Grundfunktionen darzustellen,

mu noch beschrieben werden, wie die einzelnen Grundzellen zusammengesetzt werden.

Dazu werden Schaltkreise verwendet:

Denition 1.3

Ein Schaltkreis SK = (G ; typ; I=O) uber einer Bibliothek Bib ist gegeben durch:

1

einen gerichteten, azyklischen Graphen G = (V ; E ), fur den gilt:

{ Die Menge der Knoten V = Z [ Pin [ Pout [ S setzt sich zusammen aus den

endlichen, disjunkten Mengen der Gatter Z , der prim

aren Eingange

Pin , der primaren Ausgange Pout und der Signale S .

{ Die Menge der gerichteten Kanten E = FOS [ FOB setzt sich zusammen

aus den Mengen der Fanoutst

amme FOS (Z [ Pin ) S und der Fanoutzweige FOB S (Z [ Pout ).

{ Die Abbildung source : E ! V ordnet jeder gerichteten Kante e = (vs ; vd )

deren Quelle source(e) = vs zu. Entsprechend wird durch die Abbildung

drain : E ! V die Senke drain(e) = vd deniert.

{ Fur jeden Knoten v 2 V ist der Eingangsgrad din (v ) = jfe 2 E j

drain(e)= vgj und der Ausgangsgrad dout (v) = jfe 2 E j source(e) = vgj

deniert.1

j j bezeichnet die Anzahl der Elemente in einer Menge

S

S

.

8

KAPITEL 1. GRUNDLAGEN

typ : V ! Bib [ fIN g [ fOUT g [ fSIGg, mit:

{ 8v 2 Z : typ(v ) 2 Bib, din (v ) = din (typ(v )) und dout (v ) = dout (typ(v )).

{ 8v 2 Pin : typ(v ) = IN , din (v ) = 0 und dout (v ) = 1.

{ 8v 2 Pout : typ(v ) = OUT , din (v ) = 1 und dout (v ) = 0.

{ 8v 2 S : typ(v ) = SIG, din (v ) = 1 und dout (v ) 1.

eine Orientierung I=O = (I; O; PI; PO), d.h.:

{ Die eingehenden Kanten jedes Knoten v 2 V sind geordnet durch die surjektive Abbildung I : V IN ! E . Fur einen Knoten v 2 V wird der i-te

Eingang von v (i 2 f1; 2; : : : ; din (v )g) durch I(v; i) deniert und es gilt

drain(I(v; i)) = v. Das Signal source(I(v; i)) wird als i-tes Eingangssignal

die Typung

von v bezeichnet.

{ Die ausgehenden Kanten jedes Knoten v 2 V sind geordnet durch die surjektive Abbildung O : V IN ! E . Fur einen Knoten v 2 V wird der i-te

Ausgang von v (i 2 f1; 2; : : : ; dout (v )g) durch O(v; i) deniert und es gilt

source(O(v; i)) = v. Das Signal drain(O(v; i)) wird als i-tes Ausgangssignal von v bezeichnet.

{ Die primaren Eingange des Schaltkreises SK sind geordnet durch die

bijektive Abbildung PI : f1; 2; : : : ; jPin jg ! Pin . PI(i) bezeichnet den i-ten

primaren Eingang des Schaltkreises.

{ Die primaren Ausgange des Schaltkreises SK sind geordnet durch die

bijektive Abbildung PO : f1; 2; : : : ; jPout jg ! Pout . PO(i) bezeichnet den

i-ten primaren Ausgang des Schaltkreises.

Beispiel 1.2

In Abbildung 1.3 ist fur einen Schaltkreis SK = (G ; typ; I=O) uber der Bibliothek ST D

der zugrundeliegende Graph, die Typung und die Orientierung gegeben, wobei die Orientierung der ein- und ausgehenden Kanten nur fur die Knoten s1 und z1 angegeben ist. Die

Knotenmenge V des Graphen setzt sich dabei aus Z = fz1 ; z2; z3 ; z4; z5 g, Pin = fi1 ; i2; i3 g,

Pout = fo1 ; o2 g und S = fs1 ; s2 ; : : : ; s8 g zusammen. Damit ist die Kante (i1 ; s1 ) ein Fanoutstamm und (s1; z1 ) ein Fanoutzweig. Die Quelle der Kante (i1 ; s1) ist der primare

Eingang i1 und die Senke ist das Signal s1. Der Eingangsgrad des Gatters z1 ist 3 und der

Ausgangsgrad ist 1.

Da in dieser Arbeit nur Schaltkreise uber ST D betrachtet werden, kann die graphische

Darstellung von Schaltkreisen vereinfacht werden. In Abbildung 1.4 ist die vereinfachte

Darstellung fur den Schaltkreis SK aus Beispiel 1.2 wiedergegeben.

Fur die Gatter wird der Typ durch die Schaltsymbole aus Abbildung 1.5 wiedergegeben,

wobei der Eingangsgrad durch die Anzahl der eingehenden Kanten gegeben ist. Bei der

Typangabe eines Gatters kann der entsprechende Index auch entfallen. Damit ist z.B. der

Typ eines AND-Gatters aus fAND2 ; AND3; AND4 ; : : :g. Da die Grundfunktionen aller

verwendeten Gatter kommutativ sind, kann auch auf die Angabe der Orientierung der

Eingange fur die Gatter verzichtet werden.

Ein Signal wird nicht mehr durch einen Knoten, sondern durch den entsprechenden Fanoutstamm und die adjazenten Fanoutzweige reprasentiert. Zur Unterscheidung von U berkreuzungen und Verzweigungen werden Verzweigungen durch Punkte markiert.

Auch die primaren Ein- und Ausgange werden nicht mehr durch eigene Knoten dargestellt. Statt dessen sind alle Fanoutstamme, die mit keinen Gatterausgang verbunden sind,

9

1.2. SCHALTKREISE

o1

o2

s7

s8

z5

z1

s4

s5

s6

z2

z3

z4

v typ(v )

z1 EXOR3

z2 AND2

z3 AND2

z4 AND2

z5

OR3

i1

IN

i2

IN

i3

IN

o1 OUT

o2 OUT

s1

SIG

s2

SIG

s1 s2 s3

i1

i2

i3

Graph G = (V ; E )

v i

s1 1

z1 1

z1 2

z1 3

...

I(v; i)

v i O(v; i)

i PI(i)

(i1 ; s1) s1 1 (s1 ; z1) 1 i1

(s1 ; z1) s1 2 (s1 ; z2) 2 i2

(s2 ; z1) s1 3 (s1 ; z3) 3 i3

(s3 ; z1) z1 1 (z1 ; s7)

...

...

...

Orientierung I=O = (I; O; PI; PO)

i

1

2

PO(i)

o1

o2

...

...

s8

SIG

Typung typ

Abbildung 1.3: Beispielschaltkreis SK = (G ; typ; I=O)

s

cout

+

a b cin

Abbildung 1.4: Vereinfachte Darstellung von Schaltkreis SK

Grundzelle

Schaltsymbol

C0

0

C1 BUF NOT

AND

NAND

OR

NOR

1

Abbildung 1.5: Schaltsymbole fur die Grundzellen aus ST D

EXOR

+

10

KAPITEL 1. GRUNDLAGEN

als primare Eingange zu interpretieren. Entsprechend sind Fanoutzweige, die mit keinem

Gattereingang verbunden sind, als primare Ausgange zu interpretieren. Die Orientierung

der primaren Ein- und Ausgange wird durch Angabe von Bezeichnern fur die entsprechenden Fanoutstamme bzw. Fanoutzweige ersetzt. In Abbildung 1.4 sind z.B. die primaren

Eingange mit a, b und cin sowie die primaren Ausgange mit s und cout bezeichnet worden.

Zur Beschreibung der benotigten Flache und der Verzogerungszeit fur die Realisierung

eines Schaltkreises werden verschiedene Bewertungsmethoden verwendet. In dem einfachsten Modell tragt jedes Gatter unabhangig von seinem Typ einen konstanten Wert zu

Groe und Tiefe des Schaltkreises bei:

Denition 1.4

= (G ; typ; I=O) ein Schaltkreis mit G = (V ; E ). Dann gilt:

Die Groe jjSK jj ist durch die Anzahl der Gatter bestimmt, d.h. jjSK jj = jZ j.

Ein Pfad = ((pi; s0); (s0; z1); (z1 ; s1); (s1; z2); : : : ; (sp 1; zp); (zp; sp); (sp; po))

in einem Schaltkreis ist durch eine alternierende Liste von Fanoutstammen

und Fanoutzweigen aus E gegeben, wobei pi 2 Pin ein primarer Eingang und

po 2 Pout ein primarer Ausgang ist sowie zi 2 Z (i 2 f1; 2; : : : ; pg) Gatter und

si 2 S (i 2 f0; 1; : : : ; pg) Signale sind.

Vereinfachend kann auch als (pi; s0 ; z1 ; s1 ; z2 ; : : : ; sp 1 ; zp; sp ; po) geschrieben

Sei SK

werden.

Die Lange ( ) eines Pfades = (pi; s0 ; z1 ; s1 ; z2 ; : : : ; sp 1; zp ; sp; po) ist durch

die Anzahl der Gatter in bestimmt, d.h. ( ) = j fz1 ; z2 ; : : : ; zpg j = p.

Die Tiefe (SK ) des Schaltkreises SK ist durch die Lange des langsten Pfades

gegeben, d.h. (SK ) = max(( )), wobei alle Pfade von SK enthalt.

2

Beispiel 1.3

Entsprechend Denition 1.4 ist die Groe des Schaltkreises aus Abbildung 1.3 durch

jjSK jj = jZ j = 5 gegeben. Der Pfad 1 = (i1 ; s1; z1 ; s7; o1) hat eine Lange von (1) = 1.

Der Pfad 2 = (i1 ; s1; z2 ; s4; z5; s8; o2) hat eine Lange von (2 ) = 2. Neben 2 gibt es

noch weiter Pfade mit Lange 2. Da es aber keine langeren Pfade in SK gibt, ist die Tiefe

des Schaltkreises durch (SK ) = 2 gegeben.

Die Bewertungsmethode aus Denition 1.4 bietet nur eine eingeschrankte Aussagekraft

uber den tatsachlichen Flachenbedarf und die Verzogerungszeit eines Chips, da grundlegende physikalische Eigenschaften vernachlassigt werden. Aber bereits auf der Gatterebene lassen sich weitere Eigenschaften ablesen, die weitestgehend unabhangig von der

Technologie zur Realisierung eines Schaltkreises direkten Einu auf die Groe und Tiefe

haben.

Einerseits ist sowohl die Flache als auch die Verzogerungszeit der Realisierung eines Gatters abhangig von der Komplexitat der realisierten Grundfunktion. Daher ist auf Gatterebene ein Vergleich von Groe und Tiefe fur verschiedene Realisierungen nur dann

aussagekraftig, wenn die Grundfunktionen der verwendeten Gatter vergleichbare Komplexitat haben. Das kann z.B. dadurch erreicht werden, da nur Bibliotheken zugelassen

werden, die ausschlielich Gatter mit einem Eingangsgrad von maximal 2 enthalten.

1.2. SCHALTKREISE

11

Bei einer Realisierung auf Basis einer anderen Bibliothek mu zunachst jedes Gatter mit

groerem Eingangsgrad durch eine entsprechende Realisierung der zugehorigen Grundfunktion ersetzt werden. Bei assoziativen Funktionen kann dies einfach durch einen binaren

Baum aus Gattern mit jeweils 2 Eingangen geschehen. Fur die Ersetzung eines Gatters

mit n 2 Eingangen werden dabei n 1 Gatter mit 2 Eingangen benotigt. Falls ein

balancierter Baum verwendet wird, ist die Tiefe fur jeden Pfad von einem Eingang zu

dem Ausgang des Baumes durch dlog(n)e begrenzt.2; 3 Falls der Eingangsgrad eines Gatters nicht einer Zweierpotenz entspricht, gibt es in dem balancierten Baum auch kurzere

Pfade. Allerdings gibt es immer wenigstens einen Pfad mit der angegebenen worst case

Abschatzung.

Anstelle die Ersetzung von Gattern tatsachlich durchzufuhren, kann die Denition von

Groe und Tiefe so erweitert werden, da obige U berlegungen zu dem Eingangsgrad von

Gattern implizit berucksichtigt werden. In Denition 1.5 wird dementsprechend die Groe

neu deniert. Dabei wird die max-Funktion benotigt, um Gatter mit nur einem Eingang

(z.B. NOT ) weiterhin zu berucksichtigen. Bei der neuen Denition der Tiefe eines Pfades

wird der Eingangsgrad von Gattern in dem ersten Summenterm berucksichtigt. Auch hier

werden Gatter mit einem Eingang wieder durch die max-Funktion berucksichtigt.

Zusatzlich kann bereits auf der Gatterebene der Eekt berucksichtigt werden, da die

tatsachliche Verzogerungszeit eines Gatters mit der zu treibenden Last anwachst. Die Last

wird im wesentlichen durch die Eingangskapazitaten der direkt angeschlossenen Gatter

bestimmt. Dieser Eekt kann vereinfacht dadurch modelliert werden, da jeder Fanoutzweig eines Signals eine zusatzliche Verzogerung von d verursacht. In Denition 1.5 ist

dies bei der neuen Denition der Tiefe eines Pfades durch den zweiten Summenterm

berucksichtigt.

Denition 1.5

= (G ; typ; I=O) ein Schaltkreis mit G = (V ; E ). Dann gilt:

Die Groe jjSK jjd ist gegeben durch jjSK jjd = P max(1; din(z) 1).

z 2Z

Die Lange d() einesp Pfades = (pi; s0; z1 ; s1; z2; : :p: ; sp 1; zp; sp; po) ist geP

P

geben durch d ( ) = max(1; dlog(din(zi ))e) + d dout (si ).

i=1

i=0

Die Tiefe d (SK ) des Schaltkreises SK ist durch die Lange des langsten Pfades gegeben, d.h. d (SK ) = max(d ( )), wobei alle Pfade von SK enthalt.

2

Sei SK

Im folgenden wird fur d der Wert 0:2 verwendet. Dies entspricht der Bewertung, die

auch in dem weit verbreiteten Synthesetool Sis [50] bei der bibliotheksunabhangigen Berechnung der Tiefe eines Schaltkreises mit dem Sis-Befehl print delay -m unit fanout

angewendet wird.

Beispiel 1.4

Entsprechend Denition 1.5 ist die Groe des Schaltkreises aus Abbildung 1.3 durch

jjSK jjd = 2 + 1 + 1 + 1 + 2 = 7 gegeben. Der Pfad 1 = (i1; s1; z1 ; s7; o1) hat eine

Lange von d (1) = 2+0; 2 (3+1) = 2; 8. Der Pfad 2 = (i1; s1 ; z2; s4; z5 ; s8; o2) hat eine

2 log(z )

3 F

ur

bezeichnet in dieser Arbeit den Logarithmus der Zahl z zur Basis 2.

eine reele Zahl x bezeichnet die obere Gau-Klammer dxe die kleinste ganze Zahl k mit k x.

12

KAPITEL 1. GRUNDLAGEN

Lange von d (2 ) = 1 + 2 + 0; 2 (3 + 1 + 1) = 4; 0. Neben 2 gibt es noch weiter Pfade

mit Lange 4. Da es aber keine langeren Pfade in SK gibt, ist die Tiefe des Schaltkreises

durch d(SK ) = 4 gegeben.

Bisher wurde in dem Modell fur Schaltkreise noch nicht beschrieben, wie sich der Schaltkreis nach dem Anlegen von binaren Werten an die primaren Eingange verhalt. Da das

beschriebene Modell auf der Gatterebene basiert, kann das genaue zeitliche Verhalten

vernachlassigt werden, und es braucht nur das logische Verhalten beschrieben werden.

In der folgenden Denition werden die Belegungen in Schaltkreisen fur die Bibliothek

ST D deniert, bei der alle Gatter nur einen Ausgangsgrad von 1 haben. Dabei werden die

logischen Werte nicht den Signalen, sondern den Kanten in dem Schaltkreis zugeordnet.

Diese Denition erleichtert die Modellierung von Fehlern in Kapitel 3.

Denition 1.6

Sei SK = (G ; typ; I=O) ein Schaltkreis uber der Bibliothek ST D mit G = (V ; E ) und

Z V die Menge der Gatter, Pin V die Menge der primaren Eingange, Pout V

die Menge der primaren Ausgange sowie S V die Menge der Signale.

Eine Eingangsbelegung a = (a1 ; a2 ; : : : ; ajPin j) ordnet jedem primaren Eingang PI(i) 2 Pin (i 2 f1; 2; : : : ; jPinjg) den Booleschen Wert ai zu.

Fur eine Eingangsbelegung a ist die Schaltkreisbelegung vala : E ! IB folgendermaen

deniert:

8

ai

falls e = (p; s) 2 Pin S mit p = PI(i)

>

>

>

>

<

falls e = (s; z ) 2 S (Z [ Pout )

vala (e) = > vala (I (s; 1))

>

>

typ(z)(vala(I(z; 1)); vala (I(z; 2)); : : : ; vala(I(z; din(z))))

>

:

falls e = (z; s) 2 Z S

Fur eine Schaltkreisbelegung vala zu der Eingangsbelegung a ist die Ausgangsbelegung b = (b1 ; b2 ; : : : ; bjPoutj ) durch die Zuordnung bj = vala (I(PO(j ); 1))

(j 2 f1; 2; : : : ; jPoutjg) deniert.

Beispiel 1.5

In Abbildung 1.6 ist fur den Schaltkreis aus Beispiel 1.2 die Schaltkreisbelegung fur die

Eingangsbelegung (0; 1; 1) dargestellt. Insbesondere bei Signalen mit nur einem Fanoutzweig kann die Darstellung vereinfacht werden, indem der logische Werte nur fur den

zugehorigen Fanoutstamm oder Fanoutzweig angegeben wird.

1.3

Decision Diagrams

Decision Diagrams (DDs) werden zur graphbasierten Darstellung von Booleschen Funktionen verwendet. Auerdem bieten DDs einfache Methoden, um Boolesche Funktionen zu

manipulieren. Durch die EÆzienz der Darstellung und Manipulation haben DDs Einzug

in viele moderne Werkzeuge im Bereich CAD, Synthese und Verikation gefunden.

Der popularste Vertreter der DDs sind die Binary Decision Diagrams (BDDs) [15]. Dabei

wird eine Boolesche Funktion durch wiederholte Anwendung der Shannon-Dekomposition

zerlegt. In den Functional Decision Diagrams (FDDs) [36] wird die Boolesche Funktion mit

13

1.3. DECISION DIAGRAMS

s

cout

0

1

0

0

0

1

+

01 1

0

1

0

1

1

1

01 1

a b cin

Abbildung 1.6: Schaltkreisbelegung fur die Eingangsbelegung (0,1,1)

Hilfe der Davio-Dekomposition zerlegt. Eine allgemeinere Form bilden die Kronecker Functional Decision Diagrams (KFDDs) [23]. Hier kann sowohl die Shannon-Dekomposition als

auch die Davio-Dekomposition zur Zerlegung der Booleschen Funktion verwendet werden.

BDDs und FDDs konnen also jeweils als Spezialfall von KFDDs betrachtet werden. Durch

die gemeinsame Verwendung der Shannon-Dekomposition und der Davio-Dekomposition

in KFDDs kann die Darstellungsgroe im Vergleich zu BDDs oder FDDs zum Teil erheblich reduziert werden. In [7] wurde z.B. fur die Familie der Hidden Weighted Bit Funktionen [16] gezeigt, da die Groe einer Darstellung als BDD oder FDD immer exponentiell

mit der Anzahl der Variablen wachst, wohingegen es Darstellungen als KFDD gibt, bei

denen die Groe nur polynomiell anwachst.

In den folgenden Abschnitten werden zunachst die syntaktische Beschreibung von allgemeinen DDs sowie gebrauchliche Bezeichnungen eingefuhrt. Nach einem U berblick uber

die verschiedenen Klassen von DDs werden mit den KFDDs, BDDs und FDDs verschiedene Auspragungen von DDs vorgestellt. Weiterhin wird die Semantik der vorgestellten

DDs durch die Zuordnung einer Booleschen Funktion deniert. Abschlieend werden noch

Reduktionen und inverse Reduktionen eingefuhrt, mit denen Knoten entfernt bzw. eingefugt werden konnen, um zusatzliche Struktureigenschaften fur DDs zu erreichen. Eine

ausfuhrliche Abhandlung uber DDs ist in [21] zu nden.

1.3.1 Allgemeine Decision Diagrams

Ein DD ist durch einen Graphen mit besonderen Eigenschaften und einigen ausgezeichneten Knoten, den Wurzeln, gegeben. Die Wurzeln des DDs werden in der Wurzelliste

zusammengefat.

Formal werden die syntaktischen Eigenschaften von DDs folgendermaen deniert:

Denition 1.7

Ein Decision Diagram D = (G; R; Xn ) uber einer Menge von Booleschen Variablen Xn = fx1 ; x2 ; : : : ; xn g ist gegeben durch einen gerichteten und azyklischen

Graphen G = (V; E ) und eine Wurzelliste R = (r1 ; r2 ; : : : ; rm ) 2 V m (m 2 IN) mit

folgenden Eigenschaften:

14

KAPITEL 1. GRUNDLAGEN

Jeder Knoten, der keine Wurzel ist (v 2 V n fr1 ; r2 ; : : : ; rm g)4 , hat mindestens

eine eingehende Kante.5

Die Menge der Knoten V = VI [ VT setzt sich zusammen aus den disjunkten

Mengen der inneren Knoten VI und der terminalen Knoten VT .

{ Jeder innere Knoten v 2 VI ist mit einer Entscheidungsvariablen xi 2

Xn markiert und hat genau zwei ausgehende Kanten: die LOW-Kante

low(v) und die HIGH-Kante high(v).

{ Jeder terminale Knoten v 2 VT ist mit 0 oder 1 markiert und hat keine

ausgehende Kante.

Da in dieser Arbeit nur Auspragungen von DDs betrachtet werden, mit denen Boolesche

Funktionen dargestellt werden, wurden in Denition 1.7 bereits einige Einschrankungen

vorgenommen.

Es ist z.B. moglich, Entscheidungsvariablen aus Xn nicht nur fur Boolesche Werte, sondern

fur eine beliebige diskrete Menge M zu denieren. Dies fuhrt zu den in [52] vorgestellten

Multi-valued Decision Diagrams (MDDs). Fur MDDs reichen allerdings die zwei ausgehenden Kanten fur jeden inneren Knoten nicht aus. Statt dessen mu jeder innere Knoten

jM j ausgehende Kanten haben.

Die bisher beschriebenen DDs sind alle zur Darstellung von Funktionen in die Menge

der Booleschen Werte geeignet und werden als bit-level DDs bezeichnet. Eine weitere

Moglichkeit zur Verallgemeinerung bestehtn darin,m word-level DDs zu verwenden, mit denen pseudo-Boolesche Funktionen f : IB ! ZZ in die ganzen Zahlen dargestellt werden konnen. Dies kann sehr einfach dadurch erreicht werden, da die terminalen Knoten

mit ganzen Zahlen markiert sein durfen. Die dabei entstehenden DDs werden als MultiTerminal Binary Decision Diagrams (MTBDDs) [18] oder Algebraic Decision Diagrams

(ADDs) [4] bezeichnet.

Es gibt noch eine Vielzahl von weiteren Verallgemeinerungen fur bit-level und word-level

DDs, auf die im Rahmen dieser Arbeit aber nicht eingegangen wird. Ein umfangreicher

U berblick ist in [21] zu nden. Mit Denition 1.7 konnen alle hier betrachteten bit-level

DDs uber Booleschen Entscheidungsvariablen beschrieben werden.

Beispiel 1.6

In Abbildung 1.7 ist eine graphische Reprasentation fur ein DD D = (G; R; X4) gegeben.

Innere Knoten sind jeweils durch einen Kreis und terminale Knoten durch ein Quadrat

dargestellt. Der jeweilige Bezeichner ist rechts oberhalb des Knoten angegeben. Die Menge

der inneren Knoten VI besteht aus v1; v2 ; : : : ; v10 und die Menge der terminalen Knoten ist

VT = fv11 ; v12 g. Die Knoten in der Wurzelliste R = (v1 ; v2 ) sind durch zusatzliche Kanten

markiert, die nicht von einem Knoten ausgehen. Aus graphentheoretischem Blickpunkt

sind dies keine Kanten, da sie nicht zwei Knoten des Graphen verbinden. Aber durch die

Verwendung dieser zusatzlichen Kanten vereinfacht sich die Beschreibung der im folgenden

vorgestellten Algorithmen erheblich.

Eine gerichtete Kante e = (v; v0) wird durch einen Pfeil von Knoten v zu Knoten v0 dargestellt. Fur jeden inneren Knoten wird die LOW-Kante durch die linke ausgehende Kante

des Knotens reprasentiert. Analog wird die HIGH-Kante durch die rechte ausgehende

Kante reprasentiert. Fur Knoten v1 ist low(v1 ) = (v1; v3 ) und high(v1 ) = (v1 ; v5). Mengendierenz M1 n M2 enthalt alle Elemente, die in M1 aber nicht in M2 sind.

der hier verwendeten Terminologie durfen auch Wurzeln eingehende Kanten haben.

4 Die

5 In

15

1.3. DECISION DIAGRAMS

X1

X2

X3

v1

v3

X2

1

v6

X3

1

X4

X1

1

2

v4

X2

2

v7

X3

2

v9

X4

1

1

v2

v11

1

0

v5

3

v8

3

v10

2

v12

2

Abbildung 1.7: Graphische Reprasentation eines DDs

Folgende Bezeichnungen werden verwendet:

Denition 1.8

Sei D = (G; R; Xn) ein DD. Dann gilt:

Fur einen Knoten v 2 VI gibt der low-Nachfolger low(v ) den Knoten an, auf

den die Kante low(v ) zeigt. Entsprechend gibt der high-Nachfolger high(v )

den Knoten an, auf den die Kante high(v ) zeigt.

Fur alle Knoten aus V ist das Label durch die Funktion label : V ! Xn [f0; 1g

gegeben. Der Funktionswert ist jeweils durch die in Denition 1.7 eingefuhrten

Markierungen der Knoten deniert.

Fur alle Knoten aus V ist der Index durch die Funktion index : V ! f1; 2; : : : ;

n + 1g gegeben. Fur innere Knoten v 2 VI mit label(v ) = xi ist index(v ) = i.

Fur terminale Knoten v 2 VT ist index(v ) = n + 1.

Die Menge der Knoten V ist unterteilt in n + 1 disjunkte Level, die mit

level1 ; level2; : : : ; leveln+1 bezeichnet werden. leveli = fv 2 V j index(v) = ig

enthalt jeweils alle Knoten mit Index i. Insbesondere enthalt leveln+1 alle terminalen Knoten.

widthi = jlevelij als die Breite des Levels gegeben.

Fur alle Knoten aus leveli ist die Position durch die Bijektion posi : leveli !

f1; 2; : : : ; widthig gegeben.

Fur jeden Level ist

16

KAPITEL 1. GRUNDLAGEN

Die Gro

e jjDjj des DDs D ist deniert durch das Maximum aus der Anzahl

der inneren Knoten und der Anzahl von Leveln, d.h. jjDjj = max(jVI j; n + 1)6 .

Beispiel 1.7

Fur Knoten v1 des DDs D aus Abbildung 1.7 ist der low-Nachfolger low(v1 ) = v3 und der

high-Nachfolger high(v1 ) = v5 . Die Label sind innerhalb der Knoten gegeben. Fur den

inneren Knoten v1 ist label(v1) = x1 und fur den terminalen Knoten v12 ist label(v12) = 0.

Der Index eines Knoten kann direkt an dem Label abgelesen werden und ist deshalb nicht

separat angegeben. Die Knoten v1 und v2 mit Label x1 bilden level1 . Auerdem ist level5

durch die terminalen Knoten v11 und v12 gegeben. Da sowohl level1 als auch level5 jeweils

2 Knoten enthalt, gilt fur deren Breiten width1 = width5 = 2. Die Position ist jeweils

rechts unterhalb der Knoten angegeben. Fur die Knoten aus level1 ist pos1(v1 ) = 1 und

pos1 (v2) = 2. Die Groe des DDs ist jjDjj = 10.

Meist werden weitere strukturelle Eigenschaften fur DDs gefordert. In der folgenden Denition werden Einschrankungen an die Entscheidungsvariablen der Knoten auf den Pfaden

von den Wurzeln zu den terminalen Knoten gemacht.

Denition 1.9

Sei D ein DD uber Xn . Dann gilt:

a) D ist frei, falls jede Entscheidungsvariable auf jedem Pfad von einer Wurzel

zu einem terminalen Knoten hochstens einmal vorkommt.

b) D ist geordnet, falls D frei ist und die Entscheidungsvariablen auf jedem

Pfad von einer Wurzel zu einem terminalen Knoten in der gleichen Reihenfolge

vorkommen. Diese Reihenfolge wird als Variablenordnung bezeichnet.

c) D hat eine natu

rliche Variablenordnung, falls D geordnet ist und die Indizes der Knoten auf jedem Pfad von einer Wurzel zu einem terminalen Knoten

in steigender Reihenfolge vorkommen, d.h. fur jede Kante e = (v; v 0 ) 2 E gilt:

index(v) < index(v0).

Beispiel 1.8

Das DD aus Abbildung 1.7 ist frei, geordnet und hat eine naturliche Variablenordnung. Die Groe von geordneten DDs hangt sehr stark von der verwendeten Variablenordnung

ab. Daher ist es fur den praktischen Einsatz von DDs unabdingbar, die Variablenordnung

durch geeignete Methoden zu optimieren (siehe z.B. [28, 45, 27]). Um eine einfachere

und uberschaubare Beschreibung der in dieser Arbeit vorgestellten Methoden und Algorithmen zu ermoglichen, werden im folgenden jedoch nur geordnete DDs mit naturlicher

Variablenordnung betrachtet. Fur die experimentellen Ergebnisse wurde die Variablenordnung selbstverstandlich optimiert.

6 In der Literatur wird f

ur die Groe eines DDs meistens nur die Anzahl der inneren bzw. aller Knoten

verwendet. Fur praktische Beispiele ist diese Anzahl auch groer als die Anzahl von Leveln. Die hier

gewahlte Denition vereinfacht jedoch an einigen Stellen die Diskussion von Laufzeitschranken.

17

1.3. DECISION DIAGRAMS

1.3.2 Kronecker Functional Decision Diagrams

Es wird die Semantik von KFDDs7 durch die Zuordnung von Booleschen Funktionen zu

bit-level DDs uber Booleschen Entscheidungsvariablen deniert. Da BDDs und FDDs

Spezialfalle von KFDDs sind, ist damit auch deren Semantik gegeben.

Die Boolesche Funktion f 2 IBn;m eines KFDDs wird durch die Booleschen Funktionen

beschrieben, die durch die Wurzeln dargestellt werden. Daher werden zunachst Boolesche

Funktionen betrachtet, die durch einen Knoten dargestellt werden, die auch kurz als

Boolesche Funktion des Knotens bezeichnet wird.

Die Boolesche Funktion fv des inneren Knoten v eines DDs ergibt sich durch Anwendung

von Regeln zur Zusammensetzung aus den Booleschen Funktionen der beiden Nachfolger

low(v) und high(v). Sofern die durch die terminalen Knoten reprasentierten Funktionen

bekannt sind, kann die Funktion einer Wurzel rekursiv durch wiederholte Anwendung der

Regeln bestimmt werden.

Fur die Beschreibung der durch die Nachfolger eines Knotens dargestellten Booleschen

Funktionen sind die Kofaktoren von zentraler Bedeutung:

Denition 1.10

Sei f 2 IBn eine Boolesche Funktion uber der Booleschen Variablenmenge Xn und

sei xi eine Boolesche Variable aus Xn .

a) Die Kofaktoren von f nach xi und xi sind deniert durch:

fjxi (x1 ; : : : ; xi 1 ; xi ; xi+1 ; : : : ; xn )

fjxi (x1 ; : : : ; xi 1 ; xi ; xi+1 ; : : : ; xn )

= f (x1 ; : : : ; xi 1 ; 0; xi+1; : : : ; xn)

= f (x1 ; : : : ; xi 1 ; 1; xi+1; : : : ; xn)

b) Die Boolesche Dierenz der Kofaktoren von f ist deniert durch:

fjxi xi (x1 ; x2 ; : : : ; xn )

= fjxi (x1 ; x2 ; : : : ; xn) fjxi (x1 ; x2 ; : : : ; xn)

Im folgenden werden die Kofaktoren nach xi und xi sowie die Boolesche Dierenz der

Kofaktoren zusammenfassend als Kofaktoren bezeichnet.

Alle Kofaktoren einer Funktion f 2 IBn hangen nicht mehr von der Variablen xi ab. Daher

konnen fjxi , fjxi und fjxixi auch als Funktionen aus IBn 1 interpretiert werden. Durch

wiederholte Anwendung der Kofaktorbildung konnen Funktionen aus IB0 erreicht werden.

Dies sind nur die konstanten Funktionen 0 und 1.

In dem Shannonschen Entwicklungssatz werden Regeln angegeben, um die Gesamtfunktion mit Hilfe der Kofaktoren darzustellen:

Satz 1.1 (Shannonscher Entwicklungssatz)

Sei f 2 IBn eine Boolesche Funktion uber der Booleschen Variablenmenge Xn . Dann

gilt fur alle i 2 f1; 2; : : : ; ng:

f

f

f

7 Die

= xi fjxi + xi fjxi

= fjxi xi (fjxi fjxi )

= fjxi xi (fjxi fjxi )

Shannon

(S)

positiv Davio (pD)

negativ Davio (nD)

hier betrachteten geordneten KFDDs werden in der Literatur oft als OKFDDs bezeichnet.

18

KAPITEL 1. GRUNDLAGEN

Bemerkung 1.1

In Gleichung (S ) kann das OR durch ein EXOR ersetzt werden, d.h. fur f

und i 2 f1; 2; : : : ; ng gilt auch: f = xi fjxi xi fjxi

2 IBn

Die Gleichungen (S ), (pD) und (nD) werden auch als Shannon-Dekomposition, positive Davio-Dekomposition und negative Davio-Dekomposition bezeichnet. Der

Beweis des Satzes und der Bemerkung folgt direkt durch Nachrechnen. Zur Veranschaulichung dient folgendes Beispiel:

Beispiel 1.9

Sei f = x1 x2 x1x3 x2x3 2 IB3 gegeben. Dann sind die Kofaktoren von f nach x1 und

x1 gegeben durch fjx = x3 x2 x3 und fjx = x2 x2 x3 . Die Boolesche Dierenz der

Kofaktoren ist fjx x = x3 x2 . Damit kann f entsprechend den Dekompositionsregeln

1

1

aus Satz 1.1 folgendermaen dargestellt werden:

f = x1 (x3 x2 x3 ) + x1 (x2 x2 x3 )

= x3 x2x3 x1 (x3 x2 )

= x2 x2x3 x1 (x3 x2 )

1

1

In einem geordneten KFDD zu einem DD D = (G; R; Xn) mit naturlicher Variablenordnung wird dem Level leveli (1 i n) ein Dekompositionstyp di 2 fS; pD; nDg

zugeordnet. Die einzelnen Dekompositionstypen werden in einer Dekompositionstypliste (DTL) d = (d1 ; d2 ; : : : ; dn ) zusammengefat. Der Dekompositionstyp eines inneren

Knoten v 2 leveli entspricht dann dem Dekompositionstypen di von leveli und die durch

v dargestellte Funktion wird durch Anwendung der Dekompositionsregel di aus Satz 1.1

berechnet. Den terminalen Knoten werden die konstanten Funktionen 0 und 1 zugeordnet.

Formal lat sich ein KFDD und die durch die Knoten der Wurzelliste dargestellte Boolesche Funktion folgendermaen denieren:

Denition 1.11

Ein Kronecker Functional Decision Diagram K = (G; R; Xn ; d) ist gegeben

durch ein DD D = (G; R; Xn) uber Xn mit der Wurzelliste R = (r1 ; r2 ; : : : ; rm ) sowie

einer DTL d = (d1 ; d2; : : : ; dn ). Die durch einen Knoten v 2 V mit index(v ) = i

reprasentierte Boolesche Funktion fv 2 IBn sei induktiv deniert durch:

fv =

8

>

>

>

>

>

<

>

>

>

>

>

:

0

1

xi flow(v) + xi fhigh(v)

flow(v) xi fhigh(v)

flow(v) xi fhigh(v)

falls

falls

falls

falls

falls

i = n + 1 ^ label(v ) = 0

i = n + 1 ^ label(v ) = 1

i n ^ di = S

i n ^ di = pD

i n ^ di = nD

wobei flow(v) (fhigh(v) ) die durch den Knoten

Boolesche Funktion ist.

low(v) (high(v)) reprasentierte

Die durch das KFDD dargestellte Boolesche Funktion f = (fr1 ; fr2 ; : : : ; frm ) 2 Bn;m

ist dann durch die Booleschen Funktionen der Wurzeln deniert.

19

1.3. DECISION DIAGRAMS

Ein KFDD kann als Darstellung der rekursiven Zerlegung einer Booleschen Funktion

nach dem Shannonschen Entwicklungssatz interpretiert werden. Fur einen inneren Knoten

v 2 leveli stellen die Nachfolger von v abhangig von dem Dekompositionstyp di folgende

Kofaktoren dar:

Die Boolesche Funktion des low-Nachfolgers flow(v) entspricht fur di 2 S; pD dem Kofaktor

fv jx und fur di = nD dem Kofaktor fv jx . Die Boolesche Funktion des high-Nachfolgers

fhigh(v) ist fur di = S der Kofaktor fv jx und fur di 2 fpD; nDg die Boolesche Dierenz

der Kofaktoren fv jxixi .

Falls in einem KFDD verschiedene Boolesche Funktionen dargestellt werden, fur die aber

einzelne Kofaktoren der gleichen Booleschen Funktion entsprechen, dann konnen die gleichen Kofaktoren auch durch den gleichen Knoten des DDs dargestellt werden. Im nachsten

Abschnitt wird noch genauer darauf eingegangen, unter welchen Bedingungen gleiche Kofaktoren durch gleiche Knoten dargestellt werden und in welchen Fallen verschiedene

Knoten verwendet werden.

1

1

1

Beispiel 1.10

In Abbildung 1.8 ist ein KFDD basierend auf dem DD aus Beispiel 1.6 dargestellt. Entsprechend der DTL d = (S; pD; nD; S ) sind die einzelnen Dekompositionstypen jeweils

links von allen Knoten des jeweiligen Levels angegeben. Auerdem ist fur jeden Knoten

dessen dargestellte Funktion angegeben. Die Booleschen Funktionen fv und fv haben

jeweils den gleichen Kofaktor fv jx = fv jx = x4 x3 x4 x2 x3 x4 . Deshalb konnen beide

Kofaktoren durch den gleichen Knoten v5 dargestellt werden und die HIGH-Kanten von

v1 und v2 konnen beide zu v5 fuhren.

1

1

2

1

1

fv

DT

1

X1

S

v1

X1

1

v2

2

X2

v3

X2

1

v4

X2

2

v5

3

=

fv

fv

fv

fv

fv

fv

fv

fv

fv

fv

=

=

=

=

=

=

=

=

=

=

3

4

5

nD

X3

v6

X3

1

v7

X3

2

v8

3

6

7

S

X4

v9

X4

1

v10

2

8

9

10

11

1

v11

1

0

v12

2

=

fv

2

pD

2

12

x1 x3 x4 x1 x2 x4 x1 x2 x3 x4

x1 x4 x1 x3 x4 x1 x2 x3 x4

x1 x3 x4 x1 x2 x3 x4 x1 x4

x1 x3x4 x1 x2x3 x4

x3 x4 x2 x4 x2 x3 x4

x3 x4 x2 x3 x4

x4 x3 x4 x2 x3 x4

x3 x4

x4 x3 x4

x3 x4

x4

x4

1

0

Abbildung 1.8: KFDD und dargestellte Boolesche Funktionen

20

KAPITEL 1. GRUNDLAGEN

Bei der Darstellung von Booleschen Funktionen durch KFDDs hat neben der Variablenordnung auch die Wahl der DTL einen groen Einu auf die Groe des KFDDs. Verfahren

zur Optimierung von Variablenordnung und DTL werden z.B. in [23, 20, 34] beschrieben.

1.3.3 Reduktionen

In Beispiel 1.10 wurde bereits gezeigt, da verschiedene Kofaktoren, die der gleichen Booleschen Funktion entsprechen, durch den gleichen Knoten dargestellt werden konnen. Da

KFDDs in vielen Anwendungen nur zur Darstellung und Manipulation von Booleschen

Funktionen eingesetzt werden, ist es wunschenswert, die Groe der KFDDs zu minimieren. Dazu werden verschiedene Reduktionen eingefuhrt, mit denen Knoten mit gleicher

Boolescher Funktion identiziert und entfernt werden konnen. Fur die hier betrachtete

Anwendung ist es allerdings auch notig, da bestimmte Knoten mit gleicher Boolescher

Funktion in verschiedenen Leveln des KFDDs existieren. Zum Einfugen solcher Knoten

konnen inverse Reduktionen verwendet werden, die direkt aus den Reduktionen abgeleitet

werden konnen.

Zunachst werden strukturelle Beziehungen fur Knoten in einem KFDD deniert. Anschlieend wird gezeigt, da diese Bedingungen hinreichend fur die Gleichheit der Booleschen

Funktionen der Knoten sind.

Denition 1.12

= (G; R; Xn; d) ein KFDD und seien v; v0 2 V zwei Knoten des Graphen

G = (V; E ).

a) v ist isomorph zu v 0 , falls label(v ) = label(v 0 ) und bei inneren Knoten zusatzlich low(v ) = low(v 0 ) und high(v ) = high(v 0 ) gilt.

b) v ist S-aquivalent zu v 0 , falls v ein innerer Knoten mit dindex(v) = S ist und

low(v) = high(v) = v0 gilt.

c) v ist D-

aquivalent zu v 0 , falls v ein innerer Knoten mit dindex(v) 2 fpD; nDg

ist und low(v ) = v 0 sowie label(high(v )) = 0 gilt.

Zusammenfassend wird ein Knoten v als aquivalent8 zu einem Knoten v0 bezeichnet, falls

v isomorph, S-aquivalent oder D-aquivalent zu v 0 ist.

Sei K

Beispiel 1.11

In der oberen Halfte von Abbildung 1.9 sind Ausschnitte aus KFDDs mit aquivalenten

Knoten angegeben. Unabhangig von dem Dekompositionstypen ist Knoten u isomorph zu

u0 . Der Knoten v ist S-aquivalent zu v 0 , falls der Knoten v den Dekompositionstyp S hat.

Schlielich ist der Knoten w D-aquivalent zu w0, falls der Knoten w den Dekompositionstyp

pD oder nD hat.

Lemma 1.2

Seien v und v 0 zwei aquivalente Knoten eines KFDDs. Dann reprasentieren v und

v 0 die gleiche Boolesche Funktion.

8 Die Bezeichnung basiert auf der Aquivalenz

der dargestellten Booleschen Funktionen. Bei der S

Aquivalenz

und D-Aquivalenz

handelt es sich nicht um Aquivalenzbeziehungen

im klassischen Sinne, da

sie nicht symmetrisch sind, d.h. wenn v aquivalent zu v ist, dann folgt nicht, da v aquivalent zu v ist.

0

0

21

1.3. DECISION DIAGRAMS

Beweis:

Fur isomorphe, terminale Knoten folgt der Beweis direkt aus Denition 1.11. Ansonsten

konnen die Booleschen Funktionen der jeweiligen Nachfolger von v und v0 in die Gleichungen aus Denition 1.11 eingesetzt werden:

Falls v 2 leveli mit di = pD und v D-aquivalent zu v0 ist, gilt wegen low(v) = v0 und

label(high(v)) = 0, da flow(v) = fv0 und fhigh(v) = 0. Damit ist nach Denition 1.11

fv = flow(v) xi fhigh(v) = fv0 xi 0 = fv0 .

Fur die verbleibenden Falle folgt die Gleichheit der Booleschen Funktionen von v und v0

analog.

d i {S, pD, nD}

Xi

u

Xi

u1

u’

d i {S}

u2

Xi

v

Xj

v’

d i {pD, nD}

Xi

w

Xj

w’

0

I

-1

I

Xi

u1

S

-1

S

D

-1

D

u’

u2

Xj

v’

Xj

w’

Abbildung 1.9: Reduktionen und inverse Reduktionen

Um die Groe eines KFDDs mit aquivalenten Knoten zu reduzieren, konnen Knoten, die

zu einem anderen Knoten aquivalent sind, entfernt werden. Andererseits konnen aber auch

neue Knoten in das KFDD eingefugt werden, um bestimmte Struktureigenschaften des

zugrundeliegenden Graphen zu erreichen.

Im folgenden werden fur einen Knoten v eingehende Kanten und Vorkommen in der

Wurzelliste zusammenfassend als Referenzen bezeichnet. Die Ersetzung einer Referenz auf

v durch eine Referenz auf v 0 erfolgt fur eine eingehende Kante (u; v ) durch Entfernen von

(u; v) und Einfugen einer neuen Kante (u; v0). Fur ein Vorkommen von v in der Wurzelliste

erfolgt die Ersetzung der Referenz einfach, indem in der Wurzelliste das Vorkommen

von v durch v0 ersetzt wird. Damit lassen sich Reduktionen und inverse Reduktionen

folgendermaen denieren:

22

KAPITEL 1. GRUNDLAGEN

Denition 1.13

Sei K = (G; R; Xn; d) ein KFDD mit G = (V; E ).

a) Seien v; v 0 2 V zwei Knoten, wobei v aquivalent zu v 0 ist. Die Reduktion von

v auf v 0 ist folgendermaen deniert:

Ersetze alle Referenzen auf v durch Referenzen auf v 0 und losche den Knoten v .

Falls v ein innerer Knoten ist, losche auch die Kanten low(v ) und high(v ).

Existiert danach keine Referenz mehr auf high(v )9 , dann losche auch diesen

Knoten.

Falls v isomorph zu v0 ist, heit die Reduktion I-Reduktion von v auf v0

und wird mit I (v; v 0) bezeichnet.

Falls v S-aquivalent zu v0 ist, heit die Reduktion S-Reduktion von v auf

v 0 und wird mit S (v; v 0) bezeichnet.

Falls v D-aquivalent zu v0 ist, heit die Reduktion D-Reduktion von v

auf v 0 und wird mit D(v; v 0) bezeichnet.

b) Sei v 0 2 V ein Knoten mit Referenz r. Falls r als Wurzel v 0 gegeben ist, dann

sei 1 i < index(v 0 ). Falls r durch eine Kante (u; v 0) gegeben ist, dann sei

index(u) < i < index(v0).

Falls neben r noch mindestens eine weitere Referenz auf v0 existiert, dann

ist die inverse I-Reduktion I 1 (v 0 ; r) von v 0 bzgl. r folgendermaen deniert:

Fuge einen neuen Knoten v mit label(v ) = label(v 0 ) ein und ersetze die

Referenz r durch eine Referenz auf v . Falls v 0 ein innerer Knoten ist,

fuge auerdem zwei neue Kanten low(v ) = (v; low(v 0 )) und high(v ) =

(v; high(v0)) ein.

Die inverse S-Reduktion S 1(v0; r; i) von v0 bzgl. r auf Level i ist folgendermaen deniert:

Fuge einen neuen Knoten v mit label(v ) = xi sowie zwei neue Kanten

low(v ) = (v; v 0 ) und high(v ) = (v; v 0 ) ein und ersetze die Referenz r

durch eine Referenz auf v .

Die inverse D-Reduktion D 1(v0; r; i) von v0 bzgl. r auf Level i ist folgendermaen deniert:

Falls kein terminaler Knoten z mit label(z ) = 0 existiert, fuge einen solchen Knoten ein. Fuge auerdem einen neuen Knoten v mit label(v ) = xi

sowie zwei neue Kanten low(v ) = (v; v 0 ) und high(v ) = (v; z ) ein und

ersetze die Referenz r durch eine Referenz auf v .

Beispiel 1.12

In Abbildung 1.9 wird Knoten u durch die I-Reduktion I (u; u0), Knoten v durch die

S-Reduktion S (v; v0) und Knoten w durch die D-Reduktion D(w; w0) entfernt. Die resultierenden KFDDs sind jeweils in der unteren Halfte der Abbildung gezeigt.

Entsprechend resultieren die oberen KFDDs durch inverse Reduktionen aus den unteren

KFDDs. Dazu seien die Knoten u0, v0 und w0 in der jeweiligen Wurzelliste. Dann wird Knoten u durch die inverse I-Reduktion I 1(u0; u0), Knoten v durch die inverse S-Reduktion

S 1 (v 0 ; v 0 ; i) und Knoten w durch die inverse D-Reduktion D 1 (w0 ; w0; i) eingefugt. Die

Wurzellisten mussen noch entsprechend geandert werden.

9 Dies

kann nur bei der D-Reduktion vorkommen, falls high(v ) ein terminaler Knoten mit Label 0 ist.

23

1.3. DECISION DIAGRAMS

Denition 1.14

Sei K

= (G; R; Xn; d) ein KFDD mit G = (V; E ), e = (u; v) 2 E eine Kante und

w 6= v ein Knoten, so da folgendes gilt:

Fur Knoten v existiert auer e noch mindestens eine weitere Referenz.

Die Booleschen Funktionen von v und w sind gleich, d.h. fv = fw .

Dann ist die legale Kantenersetzung K (e; w) folgendermaen deniert:

Ersetze die Kante e = (u; v ) durch eine neue Kante (u; w).

Beispiel 1.13

In dem linken KFDD in Abbildung 1.10 seien die durch v und w dargestellten Booleschen Funktionen gleich. Durch die legale Kantenersetzung K (low(u); w) wird das linke

KFDD in das rechte KFDD uberfuhrt. Entsprechend wird durch die legale Kantenersetzung K (low(u); v) in dem rechten KFDD das linke KFDD erzeugt.

u

u

K

K

v

w

v

w

Abbildung 1.10: Legale Kantenersetzung fur fv = fw

Lemma 1.3

Sei K = (G; R; Xn; d) ein KFDD und K 0 sei aus K durch wiederholte Anwendung

von Reduktionen, inversen Reduktionen und legalen Kantenersetzungen entstanden.

Dann reprasentieren K und K 0 die gleiche Boolesche Funktion.

Der Beweis des Lemmas folgt direkt aus Denition 1.13 und Lemma 1.2 bzw. Denition 1.14.

Die vorgestellten Methoden zur Modikation eines KFDDs unter Beibehaltung der dargestellten Booleschen Funktion konnen nun verwendet werden, um KFDDs zu erzeugen,

die bestimmte strukturelle Eigenschaften erfullen.

24

KAPITEL 1. GRUNDLAGEN

Denition 1.15

Sei K = (G; R; Xn; d) ein KFDD.

a) K heit reduziert, falls auf K keine I-Reduktion, keine S-Reduktion und keine

D-Reduktion angewendet werden kann.

b) K heit vollstandig, falls auf K keine inverse S-Reduktion und keine inverse

D-Reduktion angewendet werden kann.

c) K heit quasi-reduziert, falls auf K keine I -Reduktion angewendet werden

kann.

Im folgenden wird gezeigt, da jedes gegebene KFDD sowohl in ein reduziertes als auch

in ein vollstandiges, quasi-reduziertes KFDD uberfuhrt werden kann. Weiterhin sind bei

gegebener DTL und naturlicher Variablenordnung beide Formen des KFDDs bis auf Isomorphie eindeutig bestimmt.

Denition 1.16

Sei K = (G; R; Xn; d) ein KFDD mit G = (V; E ) und R = (r1 ; r2 ; : : : ; rm ) und

0 ).

sei K 0 = (G0 ; R0 ; Xn ; d) ein KFDD mit G0 = (V 0 ; E 0 ) und R0 = (r10 ; r20 ; : : : ; rm

0

0

Dann heit K isomorph zu K , wenn es eine bijektive Abbildung : V ! V mit

folgenden Eigenschaften gibt:

8i 2 f1; 2; : : : ; mg : (ri) = ri0

8v 2 V : label((v)) = label(v)

8v 2 VI : low((v)) = (low(v)) und high((v)) = (high(v))

Lemma 1.4

Jedes KFDD K = (G; R; Xn ; d) kann in Zeit O(jjK jj) in ein reduziertes KFDD

uberfuhrt werden, das bis auf Isomorphie eindeutig bestimmt ist.

In [51] wurde gezeigt, da ein reduziertes BDD in linearer Zeit berechnet werden kann.

Der Beweis der Eindeutigkeit bei gegebener DTL und Variablenordnung wurde in [19]

fur KFDDs mit einer Wurzel gefuhrt. Beide Beweise lassen sich einfach auf KFDDs mit

mehreren Wurzeln ubertragen.

Fur das in dieser Arbeit vorgestellte Syntheseverfahren werden jedoch keine reduzierten

KFDDs, sondern zunachst vollstandige, quasi-reduzierte KFDDs verwendet. Um ein gegebenes KFDD in ein vollstandiges, quasi-reduziertes KFDD zu uberfuhren, kann nach

Lemma 1.4 zunachst ein reduziertes KFDD erzeugt werden. Dieses reduzierte KFDD kann

durch wiederholte Anwendung von inversen S-Reduktionen und inversen D-Reduktionen

in ein vollstandiges KFDD uberfuhrt werden. Dabei konnen allerdings isomorphe Knoten

erzeugt werden, welche wiederum durch Anwendung von I-Reduktionen entfernt werden

konnen. Da durch die Anwendung der I-Reduktionen keine neuen inverse S-Reduktionen

oder inverse D-Reduktionen anwendbar werden, wurde ein vollstandiges, quasi-reduziertes

KFDD erzeugt.

Die Anzahl der neu erzeugten, isomorphen Knoten hangt stark von der Reihenfolge ab,

in der die inversen S-Reduktionen und inversen D-Reduktionen durchgefuhrt werden. In

Algorithmus 1.1 wird ein Verfahren vorgeschlagen, bei dem keine isomorphen Knoten

erzeugt werden, d.h. wenn der Algorithmus auf ein reduziertes KFDD angewendet wird,

bleibt das bearbeitete KFDD immer quasi-reduziert. Sobald keine inversen S-Reduktionen

und inversen D-Reduktionen mehr anwendbar sind, ist das KFDD nach Denition 1.15

auch vollstandig.

25

1.3. DECISION DIAGRAMS

Um das Erzeugen von isomorphen Knoten zu vermeiden, wird fur jeden Knoten v des

reduzierten KFDDs ein Feld equiv angelegt. In diesem Feld wird fur jeden Level eingetragen, ob es bereits einen Knoten gibt, der die gleiche Boolesche Funktion wie v darstellt.

In den Zeilen (1) bis (4) der Hauptprozedur MakeComplete werden die Felder equiv

fur alle Knoten des reduzierten

KFDDs zunachst initialisiert. Mit Hilfe dieser Felder wird

1 und D 1 uberpruft, ob tatsachlich ein neuer Knoten mittels

in den Prozeduren Sequi

equi

inverser S-Reduktion bzw. inverser D-Reduktion erzeugt werden mu oder ob eine legale

Kantenersetzung auf einen bereits existierenden Knoten durchgefuhrt werden kann.

In den Zeilen (5) bis (7) wird zunachst abhangig vom Dekompositionstyp des jeweiligen

Levels bestimmt, mit welcher Prozedur Fi neue Knoten auf Level i eingefugt werden bzw.

die legalen Kantenersetzungen durchgefuhrt werden.

Danach wird in Zeile (8) fur jede Wurzel ein aquivalenter Knoten auf Level 1 erzeugt,

sofern die Wurzel nicht selbst schon in level1 ist.

Anschlieend wird dafur gesorgt, da alle Knoten auf Level i nur noch Kanten zu Knoten

in Level i +1 haben. Dazu werden die Knoten levelweise bearbeitet und fur jeden Knoten

v 2 leveli wird die Prozedur Fi+1 sowohl fur die LOW-Kante als auch fur die HIGHKante aufgerufen. Die entsprechende Prozedur erzeugt gegebenenfalls einen Knoten auf

Level i +1, der aquivalent zu low(v) bzw. high(v) ist, und ersetzt die entsprechende Kante

low(v ) bzw. high(v ). Da die neu erzeugten Knoten zu leveli+1 hinzugef

ugt werden, ist

deren Bearbeitung im Fortlauf von Prozedur MakeComplete gesichert.

Beispiel 1.14

Der Ablauf der Prozedur MakeComplete wird an einem Beispiel in Abbildung 1.11

veranschaulicht. Zunachst ist ein reduziertes KFDD gegeben.

Im ersten Schritt werden 1die Wurzeln bearbeitet. Da der Dekompositionstyp d1 = nD

ist, wird die Prozedur Dequi verwendet. Fur Knoten v1 ist equiv [1] = v1. Deshalb wird

1 ausgefuhrt, wobei das Vorkommen von v in der Wurzelliste

nur Zeile (16) von Dequi

1

wieder durch v1 ersetzt wird und die Wurzelliste somit unverandert bleibt. Danach wird