GGADS - Computer Science and Engineering

Werbung

GGADS - Ein bibliotheksunabhangiges

Layoutsynthesesystem fur

benutzerdenierbare

Gate-Array-Master-Strukturen

vorgelegt von

Diplom-Informatiker

Achim Homann

aus Backnang

Vom Fachbereich 20 - Informatik

der Technischen Universitat Berlin

genehmigte Dissertation zur Erlangung des akademischen Grades

Doktor-Ingenieur

Promotionsausschu:

Vorsitzender: Prof. Dr.-Ing. Hans Liebig

Berichter: Prof. Dr. rer. nat. Otto Manck (FB 19)

Berichter: Prof. Dr.-Ing. Hans-Ulrich Post

Tag der wissenschaftlichen Aussprache: 9. April 1992

Berlin 1992

D 83

1

Kurzfassung

In der vorliegenden Arbeit wird das System GGADS (General Gate-Array Design System)

vorgestellt. Das System erzeugt die Verdrahtungsmasken fur vom Anwender frei kongurierbare Gate-Array-Master-Strukturen aus einer Beschreibung der Mastergeometrien

und einer Schaltungsbeschreibung.

Das Konzept der Gate-Array-Technik bietet die Moglichkeit, verhaltnismaig kostengunstig leistungsfahige anwendungsspezische Schaltungen hochster Integrationsdichte zu

entwickeln. Anwendungsspezisch mu nur noch die Verdrahtung der Transistoren bestimmt werden. Das Aufkommen neuer Technologien, z.B. CMOS, BiCMOS, etc. fuhrt

dazu, da nicht nur groere, sondern immer wieder neue Gate-Array-Master-Strukturen

entwickelt werden.

Aus diesem Sachverhalt ergibt sich der Bedarf an Entwurfssystemen, die leicht an neue

Master-Strukturen angepat werden konnen. Weiterhin soll auch fur neue Technologien

der automatische Entwurf von achenezienten Layouts ermoglicht werden.

Bisherige automatische Layoutsysteme fur Gate-Arrays sind entweder nur fur spezische

Master oder aber sie konnen nur vorgegebene Bibliothekszellen auf bestimmten Referenzpunkten plazieren und verdrahten. GGADS hingegen erzeugt die erforderlichen Elementarverdrahtungen (Bibliothekszellen) selbst und lat sich dadurch mit erheblich geringerem Aufwand fur neue Master-Strukturen einsetzen. Dies ist wichtig, wenn neue MasterStrukturentwurfe auf ihre Eignung fur bestimmte Schaltungstypen untersucht werden

sollen.

In GGADS wird fur die globale Plazierung der neue Algorithmus SQP (Simultaneous

QuadriPartitioning) verwendet, der sich gegenuber traditionellen Verfahren als deutlich

uberlegen herausstellte. Bei der lokalen Plazierung und Verdrahtung verfolgt GGADS

einen konstruktiven Ansatz. Dabei werden von einer Ecke der Chipache ausgehend

sukzessive die Schaltelemente dicht plaziert und sofort verdrahtet. Leitungen, die zu

weiter entfernt liegenden Elementen fuhren, werden bis zum Rand der bereits belegten

und sukzessivee wachsenden Chipache gefuhrt.

Diese Vorgehensweise sieht von einem Reihenkonzept mit dazwischenliegenden Verdrahtungskanalen ab. Dadurch eignet sich GGADS auch fur den Entwurf von ECL-Schaltungen

oder von CMOS-Dominologik. Diese Schaltungstypen sind fur einen Standardzellenentwurf ungeeignet, da sie sich nicht aus eine Menge von wenigen unterschiedlichen Bibliothekselementen zusammensetzen lassen. Dadurch eronet GGADS zwei neue Anwendungsgebiete von Entwurfssystemen fur Gate-Array-Master-Strukturen.

Der konstruktive Ansatz des lokalen Plazierens und Verdrahtens wurde im Rahmen dieser

Arbeit als ein neues Konzept implementiert. Dabei wurde jedoch auf eine weitergehende

Verfeinerung der Algorithmen zur Leistungssteigerung verzichtet. Daher kann das durch

GGADS erzeugte Layout mit der Flachenezienz der besten kommerziellen Systeme wie

TANGATE nicht ganz mithalten. (TANGATE hat eine um ca. 20% bessere Ausbeute.)

Nichtsdestotrotz deuten die mit GGADS erzeugten Layouts daraufhin, da eine weitere Verfeinerung der Algorithmen eine vielversprechende Alternative zu bisher verfolgten

Entwurfskonzepten darstellt.

2

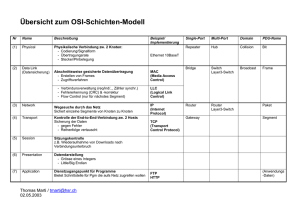

Inhaltsverzeichnis

1 Einfuhrung

1.1 Layoutentwurfsmethoden . . . . . . . . . . . . .

1.1.1 Halb- versus Vollkundenentwurf . . . . .

1.1.2 Der Semi-Kundenentwurfsstil . . . . . .

1.2 Kombinatorische Aspekte des Schaltkreislayouts

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

5

. 6

. 6

. 7

. 12

2 Der Gate-Array-Entwurf

15

3 Algorithmen fur den physikalischen Entwurf

21

4 Das Entwurfssystem GGADS

67

5 Layoutbeispiele und Vergleich mit TANGATE

79

6 Schlubemerkungen und Ausblick

89

2.1 Schaltungsentwurf auf Gate-Array-Master-Strukturen . . . . . . . . . . . . 15

2.2 Vorhandene Entwurfssysteme . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3 Konzeptionelle Besonderheiten . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.1 Die Plazierung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1 Losungsansatze zum Plazierungsproblem . . . . . . . . . . . . . . .

3.1.2 Das allgemeine Schaltkreispartitionierungsproblem . . . . . . . . . .

3.1.3 Denitionen und Komplexitatsergebnisse . . . . . . . . . . . . . . .

3.1.4 Iterative Verbesserungsheuristiken fur Hypergraphbipartitionierung

3.1.5 Plazieren durch rekursive Partitionierung . . . . . . . . . . . . . . .

3.1.6 SQP - ein neues globales MinCut-Partitionierungsverfahren . . . . .

3.1.7 Laufzeitanalyse der SQP Heuristik . . . . . . . . . . . . . . . . . .

3.2 Globale Verdrahtung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Integriertes globales Plazieren und Verdrahten . . . . . . . . . . . . . . . .

3.4 Lokale Verdrahtungsverfahren . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 Das Kanalverdrahtungsproblem . . . . . . . . . . . . . . . . . . . .

3.4.2 Die Idee der Vorzugsrichtung fur Verdrahtungsebenen . . . . . . . .

3.5 Lokales Plazieren und Verdrahten in GGADS . . . . . . . . . . . . . . . .

22

22

24

25

28

36

38

45

47

54

57

58

58

60

4.1 Der Makrogenerator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.2 Die Beschreibung von Gate-Array-Masterstrukturen . . . . . . . . . . . . . 75

5.1 Layoutbeispiele . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.2 Leistungsvergleich mit TANGATE . . . . . . . . . . . . . . . . . . . . . . . 85

3

INHALTSVERZEICHNIS

4

Literatur

7 Anhang

7.1 Tabellen . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 Denitionen . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 Die Beschreibungssprache fur Master-Strukturen . . . . . .

7.3.1 Beispiel fur eine Masterbeschreibung . . . . . . . .

7.3.2 Die Grammatik fur die Masterbeschreibungssprache

7.4 Bedienungsanleitung fur GGADS . . . . . . . . . . . . . .

7.5 Die Netzlistenformate . . . . . . . . . . . . . . . . . . . . .

7.5.1 Beispiel fur die Netzliste . . . . . . . . . . . . . .

7.5.2 Beispiel fur die Transistornetzliste . . . . . . . . .

Danksagung

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

93

99

99

103

104

106

126

131

133

133

134

135

Kapitel 1

Einfuhrung in den Entwurf

integrierter Schaltkreise

Bei dem Entwurf integrierter Schaltungen bestimmen Kosten, Leistungsmerkmale und

die Zeit, um eine neue Schaltung auf den Markt zu bringen, ganz entscheidend, ob ein

Hersteller integrierter Schaltungen auf dem Markt uberleben kann. Mehr als die Halfte

aller Semi-Kundenentwurfe waren Ende der 80er Jahre in den USA Gate-Array-Entwurfe

- keine Standardzellenentwurfe. Die Zahl der Vollkundenentwurfe hat daruberhinaus insgesamt eine abnehmende Tendenz gezeigt.

Das Konzept der Gate-Array-Technik bietet die Moglichkeit, verhaltnismaig kostengunstig leistungsfahige anwendungsspezische Schaltungen hochster Integrationsdichte zu

entwickeln. Anwendungsspezisch mu nur noch die Verdrahtung der Transistoren bestimmt werden. Dadurch ist auch eine kurzere Entwicklungszeit bei Gate-Arrays leichter

zu erreichen als bei Standardzellentwurfen.

Das Aufkommen neuer Technologien, z.B. CMOS, BiCMOS, etc. fuhrt dazu, da nicht nur

groere, sondern immer wieder neue Gate-Array-Master-Strukturen entwickelt werden.

Weiterhin erfordern verschiedene Schaltungstechniken unterschiedliche Mikroarchitekturen des verwendeten Gate-Arrays, um die vorhandene Flache gut ausnutzen zu konnen.

Beispielsweise erfordern statische CMOS-Schaltungen eine gleiche Anzahl von p-MOSund n-MOS-Transistoren. RAM-Strukturen hingegen benotigen mehr n-MOS- als p-MOSTransistoren. Somit werden auch durch bestimmte Anwendungsgebiete neue spezische

Gate-Array-Master-Strukturen erforderlich.

Bisherige automatische Layoutsysteme fur Gate-Arrays sind entweder nur fur spezische

Master [2] zugeschnitten oder sie erfordern die Eingabe von masterspezischen Elementarverdrahtungen von NAND, NOR, etc. [17]. GGADS (General Gate Array Design System)

erzeugt die erforderlichen Elementarverdrahtungen selbst und lat sich dadurch mit erheblich geringerem Aufwand fur neue Master-Strukturen einsetzen. GGADS lat sich

auch fur Entwurfe nach dem Master-Image Konzept [35] einsetzen.

In diesem Kapitel wird zunachst eine kurze Einfuhrung in die allgemeinen Probleme des

Layoutentwurfs gegeben. Aus der Sicht des Ingenieurs stehen die sich standig andernden

Anforderungen an die Entwurfswerkzeuge im Vordergrund. Aus algorithmischer Sicht

sticht insbesondere die kombinatorische Komplexitat hervor. Im folgenden sollen zunachst

generelle Losungstrategien erlautert werden. Anschlieend wird der kombinatorische

5

6

KAPITEL 1. EINFUHRUNG

Aspekt des Layoutentwurfs angesprochen.

1.1 Layoutentwurfsmethoden

1.1.1 Halb- versus Vollkundenentwurf

Auf einer abstrakten Ebene werden zwei unterschiedliche Arten des Layoutentwurfs unterschieden; Semi- und Vollkundenentwurf. Der Vollkundenentwurf setzt keinerlei Vorfertigung voraus. Dabei hat man die groten Freiheitsgrade, die einzelnen Schaltkreiselemente

zu realisieren. Wo die Elemente plaziert und wie sie miteinander verbunden werden, wird

durch den spezischen Entwurf frei bestimmt. Der extreme Fall des Vollkundenentwurfs

ist damit der Handentwurf. Dabei hat der Entwickler die volle Kontrolle uber alle Teile

des Entwurfsergebnisses.

Der Semi-Kundenentwurf bietet weniger Freiheitsgrade. Entweder sind durch die Entwurfsmethodik oder aber durch die benutzte Herstellungstechnologie Einschrankungen der

Entwurfsfreiheit gegeben. Fur einen U berblick uber die technologischen Aspekte des Entwurfs integrierter Schaltungen sei auf [47, 41] verwiesen. Zu den Semi-Kundenentwurfsstilen zahlen Entwurfsstile, die von einer vorfabrizierten Siliziumstruktur ausgehen (GateArray-Entwurf). Beim Standardzellenentwurf wird von einer vorhandenen Zellbibliothek ausgegangen, die Layouts von elementaren Schaltfunktionen enthalten. Hierbei beschrankt sich die Plazierung im wesentlichen darauf, Blocke fester Groe eindimensional

(in Reihen) anzuordnen. Zwischen zwei benachbarten Reihen entstehen dabei Verdrahtungskanale. Diese reihenorientierte Anordnung der Zellen hat den besonderen Vorteil,

da fur die erforderliche Verdrahtung besonders eziente und eektive Kanalverdrahtungsverfahren bekannt sind [51, 48, 55]. Traditionell wurde der Vollkundenentwurf kaum

durch Entwurfswerkzeuge unterstutzt. Die einzigen Werkzeuge waren interaktive Graphikeditoren fur den Handentwurf auf der Maskenebene. Weiterhin standen noch Werkzeuge

zur Verfugung, um die Korrektheit des Handlayouts zu uberprufen sowie um Schaltungsteile zu einem Gesamtlayout zusammenzusetzen.

Im Gegensatz dazu boten die Layoutwerkzeuge eine gute Unterstutzung fur Semi-Kundenentwurfsstile. Mit der Ausreifung der Layoutwerkzeuge verwischt die Trennung von

Halb- und Vollkundenentwurf immer mehr, da der Vollkundenentwurf heutzutage ebenfalls durch Werkzeuge immer mehr unterstutzt wird. Dadurch wird die Frage, ob ein

bestimmter Entwurfsstil Halb- oder Vollkundenentwurf genannt wird, zu einem gewissen Grad zu einer Ansichtssache. Hierbei spielen auch kommerzielle Aspekte eine Rolle,

da der Name Vollkundenentwurf eine hohere Qualitat des Entwurfs verspricht. Allgemein lat sich sagen, da Vollkundenentwurfe ein beliebiges Plazieren von rechteckigen

Blocken in der Ebene erlaubt. Hierbei kann noch eine Floorplanning-Phase vorgeschaltet

sein. Abbildung 1.1 zeigt Blocke, die unregelmaig in der Ebene angeordnet sind. Zwischen den Blocken sind Freiraume fur die notwendigen Verbindungsleitungen vorgesehen.

Bei Vollkundenentwurfen werden die einzelnen Zellen in der Regel mit Hand entworfen.

Zu diesem Zweck werden aber auch zunehmend Zell- und Modulgeneratoren eingesetzt.

Vollkundenentwurfe erfordern immer noch eine erheblich langere Entwurfsdauer als die

Semi-Kundenentwurfe. Zur Zeit ist man noch weit davon entfernt, den Vollkundenentwurf vollstandig automatisieren zu konnen und dabei zu Ergebnissen zu kommen, die

1.1. LAYOUTENTWURFSMETHODEN

7

Abbildung 1.1: Schematische Darstellung eines Vollkundenentwurfs

mit Handentwurfen konkurrieren konnten. Nichstdestotrotz wachsen die Bereiche des

Halb- und des Vollkundenentwurfs immer mehr zusammen. Fortschritte in der Fertigungstechnologie hat Gate-Arrays hervorgebracht, die eine fast uneingeschrankte Plazierung ermoglichen (sea-of-gates). Layouts, die darauf basieren, liegen auf der Grenzlinie

zwischen Halb- und Vollkundenentwurf.

Die Entscheidung fur den Semi- oder fur den Vollkundenentwurf hangt von dem Typ der

Schaltung und den wirtschaftlichen Randbedingungen ab. Wenn ein Schaltkreis hochster

Komlexitat fur groe Stuckzahlen entwickelt werden soll, so lohnt sich der kosteninsivere Vollkundenentwurf. Soll das Produkt im Gegensatz dazu eine anwendungsspezische

Schaltung (ein ASIC ) sein, so ist der kostengunstigere Semi-Kundenentwurfsstil zu bevorzugen. ASICs werden in der Regel in kleineren Stuckzahlen hergestellt, die Leistungsanforderungen an die Schaltung sind in der Regel nicht so hoch und die Entwicklungszeiten

sollten haug moglichst kurz sein.

Wenn die Layoutwerkzeuge weiter verbessert werden, wird der automatisierte Semi-Kundenentwurfsstil der Qualitat des Vollkundenentwurfs immer naher kommen.

1

1.1.2 Der Semi-Kundenentwurfsstil

Standardzellen-Technik

Bei dem Standardzellenentwurf sind die einzelnen Zellen klein und rechteckig. Die Zellen enthalten das Layout von elementaren Schaltfunktionen (z.B. NAND, NOR, etc.).

Meistens haben alle Zellen eine einheitliche Hohe und haben feste Anschlusse fur Takt

und Versorgungsspannung auf der linken und rechten Seite. Dadurch konnen die Standardzellen in Reihen aneinander gefugt werden, wobei gleichzeitig gewahrleistet ist, da

die Versorgungsspannungs- und Taktsignalleitungen der einzelnen Zellen miteinander verbunden sind. Wahrend der Plazierungsphase werden die Zellen in horizontalen Reihen

ASIC steht fur Application Specic Integrated Circuit. Als ASIC werden im allgemeinen Schaltungen

mit relativ geringer Stuckzahl bezeichnet. Daher werden fur den Entwurf von ASICs bevorzugt SemiKundenentwurfsmethoden eingesetzt.

1

KAPITEL 1. EINFUHRUNG

8

Abbildung 1.2: Beispiel fur einen Standardzellentwurf

plaziert. Die anschlieende globale Verdrahtungsphase bestimmt, an welchen Stellen die

einzelnen Signalleitungen von einer Zellreihe zu einer anderen gefuhrt werden. Diese Stellen werden auch feedthroughs genannt. Die detaillierte Verdrahtungsphase besteht damit

aus der Losung einer Reihe von Kanalverdrahtungsproblemen. Verdrahtungskanale entstehen zwischen jeweils zwei benachbarten Zellreihen. Abbildung 1.2 zeigt ein Beispiel fur

einen Standardzellentwurf.

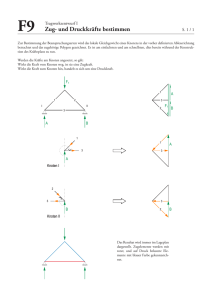

Gate-Array-Technik

Bei dem Gate-Array-Entwurf geht man - im Gegensatz zum Standardzellenentwurf - von

einer vorfabrizierten Struktur auf der Chipache aus. Genauer gesagt, sind alle Schaltelemente bereits vorfabriziert. Ein solch vorfabrizierter Wafer wird auch Master genannt.

Es werden nur noch die Verdrahtungsebenen schaltungsspezisch entworfen, um eine spezische Schaltung zu realisieren. Das heit, es werden auch nur noch die Masken fur

die zwei (eventuell mehr) vorhandenen Metallisierungsebenen zur Verdrahtung benotigt

sowie die zugehorigen Masken fur die Kontaktlocher zwischen den Verdrahtungsebenen

und Kontakten von der untersten Metallebene zu den Transistoranschlussen. Die Zahl der

schaltungsspezischen Masken wird also erheblich reduziert. Dies hat zur Folge, da nicht

nur die Layoutdaten reduziert werden, sondern auch die Herstellungskosten eines Chips.

Weiterhin wird die Herstellungszeit reduziert, da nur noch die letzten Schritte des Herstellungsprozesses schaltungsspezisch durchgefuhrt werden mussen. Die Master konnen

hingegen fur verschiedene Schaltungen in groen Stuckzahlen im vorhinein hergestellt

werden. Gate-Arrays erreichen jedoch nicht die Leistungsfahigkeit und Integrationsdichte von Standardzellen- und Vollkundenentwurfen. Dies ist durch die Einschrankungen

bedingt, die die fur allgemeine Verwendung entwickelten Master-Strukturen auferlegen.

Dazu zahlen auch die Fanouts der einzelnen Gatter, die nur in einem groben Raster

an den individuellen Bedarf angepat werden konnen. Abbildung 1.3 zeigt schematisch

verschiedene Gate-Array-Master-Strukturen. Die vorfabrizierten Layoutstrukturen werden auch Transistorzellen, oder Zellen (engl. cells) genannt. In Abbildung 1.3a) sind

die Transistorzellen in Reihen angeordnet. Auf anderen Mastern sind die Zellen ma-

1.1. LAYOUTENTWURFSMETHODEN

9

4k RAM

8k

RAM

a) Reihenstruktur

b) Sea-of-gates

c) Sea-of-Gates mit

Sonderstrukturen

Abbildung 1.3: Verschiedene Gate-Array-Master-Strukturen

trixartig angeordnet, wobei horizontale und vertikale Verdrahtungskanale zwischen den

Transistorzellen freigelassen sein konnen. In solchen Fallen werden die Zellen auch Inseln (engl. islands) genannt. Schaltelemente wie logische Gatter oder Flipops konnen

durch geeignete Metallisierungen uber den Transistorzellen realisiert werden. Die Schaltelemente konnen untereinander durch Signalleitungen verbunden werden, die durch die

vorgesehenen Verdrahtungskanale laufen. Diese beiden Arten von schaltungsspezischer

Verdrahtung realisieren die spezische Schaltung auf einem Master. Bei dem Gate-ArrayEntwurf ist das Plazierungsproblem im wesentlichen ein Zuweisungsproblem. Zu jedem

Gatter in der Netzliste mu eine geeignete Transistorzelle auf dem Master bestimmt werden, um die Gatterfunktion auf dem Chip zu realisieren. Abhangig davon, wie der Master

im einzelnen aussieht, kann das Layout fur ein Gatter nicht beliebig gedreht oder gespiegelt werden. Auch ist es moglich, da manche Schaltfunktionen nur in einem bestimmten

Bereich des Chips realisiert werden konnen, da nur dort die erforderlichen Transistortypen vorhanden sind (z.B. Bipolartransistoren). Das Verdrahtungsproblem ist dadurch

charakterisiert, da die Verdrahtungskanale auf dem reihenorientierten Master eine feste

Anzahl von Verdrahtungsspuren haben. Im Gegensatz dazu konnen bei dem Semi- oder

Vollkundenentwurf die Verdrahtungskanale auf den jeweiligen Bedarf genau zugeschnitten

werden.

2

Sea-of-gates

Neuere Entwicklungen der Gate-Array-Master weisen in ihrer Struktur einen grundlegenden Unterschied gegenuber Abbildung 1.3a) auf. Bei den Sea-of-gates Typen, die

heute den Standard bei Gate-Array-Master-Strukturen darstellen, sind keine speziellen

Verdrahtungskanale mehr vorgesehen (Abbildung 1.3b)). Stattdessen ist die gesamte

Chipache mit Transistorzellen belegt. Dadurch konnen wesentlich mehr Transistoren

auf dem Master untergebracht werden. Nichtsdestotrotz lat sich immer nur ein Bruchteil dieser Transistoren nutzen. Die ubrigen Transistoren konnen nicht in der Schaltung

verwendet werden, da ihre Anschlupunkte durch Verdrahtungsleitungen uberdeckt sind

2

Bei Standardzellenentwurf oder sea-of-gates

KAPITEL 1. EINFUHRUNG

10

NAND2.cif scale: 0.088764

(2255X)

E1

Size: 89 x 100 microns

E2

A

NAND2.r.k

VDD

VDD

VSS

VSS

E1

E2

A

Abbildung 1.4: Schematische Darstellung eines 2-NAND CMOS-Gatters im Vollkundenlayout. Die obere Halfte zeigt die Wanne fur die p-MOS-Transistoren.

oder kein Platz mehr fur die Verlegung der Anschlunetze vorhanden ist. Ein weiterer

wesentlicher Unterschied der Sea-of-gates-Master gegenuber den reihenorientierten GateArray-Mastern ist eine groere Zahl von Verdrahtungsebenen. Die Sea-of-gates-Technik

liegt zwischen dem Halb- und dem Vollkundenentwurfsstil. Auf der einen Seite werden

vorfabrizierte Master-Strukturen verwendet; auf der anderen Seite ist aber das Konzept

der Verdrahtungskanale aufgelost. Durch letzteres wird die Entscheidung daruber, ob

Verdrahtungskanale benutzt werden sollen und wo sie ggf. liegen sollen, von der Hardware in die Software - in die Layoutprogramme - verschoben. Der Erfolg der Sea-ofgates fur CMOS-Schaltungen wurde durch die Tatsache vorangetrieben, da der Entwurf

von CMOS-Zellen fur Vollkundenentwurfe ebenfalls dem Semi-Kundenentwurfsstil ahnelt.

Dies ist darauf zuruckzufuhren, da durch die erforderlichen p-MOS-Transistoren Wannen in das Diusionsgebiet eingelassen werden mussen, die groer sind als die Transistoren selbst. Daher bietet es sich an, mehrere p-MOS-Transistoren in einer gemeinsamen

Wanne unterzubringen. Dies mundet haug in p-MOS-Transistorreihen - ahnlich wie bei

Standardzellentwurfen. Siehe hierzu Abbildung 1.4. Daher ist fur CMOS-Schaltungen der

Unterschied zwischen Sea-of-gates-Entwurfen und Vollkundenentwurfen besonders gering.

Weiterhin erlauben Sea-of-gates-Master die Realisierung von besonders dichter Logik fur

Spezialanwendungen (z.B. fur RAMs) direkt auf dem Master, indem sie an einigen Stellen

spezielle RAM-Transistorstrukturen besitzen (Abbildung 1.3c)).

Bisher werden die Entwurfssysteme auf die Master-Strukturen eines Herstellers und einer

Technologie zugeschnitten. Wenn neue Technologien in das Angebot eines Herstellers aufgenommen werden, so mussen auch die Entwurfswerkzeuge daran angepat werden. Durch

diesen Sachverhalt sind nicht nur standige Eingrie in die Entwurfswerkzeuge erforderlich,

sondern der Layoutentwurf mu auch dem Chiphersteller uberlassen werden. Letzteres ist

allerdings nicht immer wunschenswert. Wenn Schaltungen hochster Leistungsfaghigkeit

entwickelt werden sollen, so mu bei dem derzeitigen Entwicklungsstand der Entwurfswerkzeuge der Schaltungsentwickler auch die Umsetzung der Schaltung in Layout kontrollieren und notigenfalls beeinussen konnen. Beispielsweise, um die Treiberstarke von

Gattern - so gut es bei Gate-Arrays geht - an die enstehenden Leitungslangen anzupassen.

1.1. LAYOUTENTWURFSMETHODEN

11

VCC

OUT

A

B

A

C

OUT

C

B

VREF

GND

Abbildung 1.5: Umsetzung von Gatterlogik in ECL-Technik. Oben ist die kombinierte

logische Funktion (A _ B) ^ C in ECL realisiert.

Die fortschrittlichsten bisher vorhandenen Entwurfswerkzeuge fur Gate-Arrays beschranken

sich im wesentlichen darauf, vorhandene Bibliothekselemente auf einem bestimmbaren Raster zu plazieren. Siehe hierzu Abschnitt 2.2. Dies hat einerseits zur Folge, da sich diese

Systeme nicht fur Experimente mit neuen Master-Strukturen eignen, da fur jede neue

Transistorzelle die Bibliothekselemente von Hand entwickelt werden muten.

Auf der anderen Seite bedeutet dies auch, da Schaltungstechniken, die sich nicht aus wenigen unterschiedlichen Bibliothekselementen zusammensetzen lassen, mit vorhandenen

Entwurfssystemen uberhaupt nicht geeignet behandeln lassen. Zu diesen Schaltungstechniken zahlen ECL-Schaltungen und die dynamische CMOS-Dominologik. Beide Schaltungstypen haben die Eigenart, da die einzelnen logischen Gatterfunktionen nicht Gatter fur Gatter elektrisch realisiert werden. Es werden vielmehr mehrere logische Gatter

bei der elektrischen Realisierung zu groeren Baumstrukturen zusammengefat. Dadurch

entstehen in einer Schaltung derart viele verschiedene Baumstrukturen, da diese sich

nicht mehr sinnvoll als Bibliothekselemente realisieren lassen. Siehe hierzu Abbildung 1.5.

Daher muten bisher ECL-Gate-Arrays immer noch von Hand entworfen werden.

Das neue Entwurfssystem GGADS

Das in dieser Arbeit vorgestellte System GGADS beinhaltet nicht nur ein Plazierungs- und

Verdrahtungsverfahren, sondern auch einen Makrozellengenerator, wodurch GGADS sehr

schnell auf neue Master-Strukturen angepat werden kann. Weiterhin ist das in GGADS

verwendete Verdrahtungsverfahren nicht auf Verdrahtungskanale angewiesen, wodurch

GGADS nicht mehr auf das bloe Plazieren und Verdrahten von Bibliothekselementen

angewiesen ist. Somit konnen mit GGADS auch die Layouts fur ECL-Schaltungen automatisch auf Gate-Arrays erzeugt werden.

KAPITEL 1. EINFUHRUNG

12

1.2 Kombinatorische Aspekte des Schaltkreislayouts

In kombinatorischer Hinsicht ist das Layoutproblem ein Optimierungsproblem mit einschrankenden Randbedingungen. Ein aktuelles und umfangreiches Kompendium von

Arbeiten hierzu bietet [40]. Generell kann man davon ausgehen, da eine Schaltkreisbeschreibung vorgegeben ist - meist in Form einer Netzliste, die die einzelnen Schaltungselemente beinhaltet und die Verbindungen der Schaltungselemente untereinander

beschreibt. Gesucht ist eine Zuweisung von geometrischen Platzen in der Ebene zu den

einzelnen Schaltungselementen. Dabei mussen die Randbedingungen der Fertigungstechnologie berucksichtigt werden. Diese bestehen in der Regel aus Mindestgroen fur die

Realisierung der verschiedenden Schaltungskomponenten sowie in Mindestabstanden zwischen den unterschiedlichen Elementen. Zum Beispiel Mindestbreite von Verdrahtungsleitungen und Mindestabstanden zwischen zwei Leitungen auf der gleichen Verdrahtungsebene. Optimierungskriterien sind weiterhin gegeben, zu denen in der Regel die resultierende

Chipache gehort. Weitere Optimierungskriterien konnen die Signallaufzeiten bestimmter

Signale sein oder der Leistungsverbrauch der Gesamtschaltung. Bei den letzten beiden

Kriterien gibt es eine ganze Reihe von Verfeinerungen, die insbesondere in den letzten

Jahren an Bedeutung gewannen. Dies ist in erster Linie auf weitere Ausreifung der vorhandenen Technologie zuruckzufuhren, wodurch immer mehr Schaltelemente auf einem

Chip realisiert werden konnen. Gleichzeitig damit werden die Schaltgeschwindigkeiten

immer groer.

So gut wie alle Versionen des Layoutproblems sind NP-schwierig. Dies bedeutet, da

Algorithmen, die tatsachlich ein Optimum nden - zum Beispiel eine Schaltung auf minimaler Flache realisieren - einen vollig unpraktikablen Rechenzeitaufwand haben. Die

Rechenzeit steigt exponentiell mit der Schaltungsgroe an. Daraus resultiert, da auch

durch den Einsatz zukunftiger schnellerer Rechner die Rechenzeiten nicht in akzeptable Groenordnungen kommen werden. Die einzige Moglichkeit, solche kombinatorischen

Probleme mit praktikablem Aufwand zu behandeln, besteht darin, Heuristiken zu deren

Losung einzusetzen. Heuristiken nden in der Regel keine optimale Losung fur ein gegebenes Problem, sie sind aber dafur sehr schnelle Verfahren. Durch den groen Geschwindigkeitsvorteil eignen sich heuristische Verfahren fur den Einsatz in der Praxis. Das Problem

hierbei ist, da die Qualitat der von Heuristiken gelieferten Losung haug schwer zu beurteilen ist. Da das jeweilige Optimum unbekannt ist, lat sich nichts Genaues daruber

aussagen, um wieviel Prozent die gefundene Losung vom Optimum abweicht. Man ist

bemuht, theoretische Beweise uber die Leistung von Heuristiken zu fuhren. Bisher konnten jedoch - abgesehen von wenigen Ausnahmen - nur relativ uninteressante Ergebnisse

erzielt werden. Wenn gezeigt wird, da eine bestimmte Heuristik ein Layout erzeugt, das

im schlechtesten Fall die minimal erforderliche Chipache um ein paar Hundert Prozent

ubersteigt, so ist dies fur die Praxis in der Regel keine verwertbare Aussage Trotzdem

ist man in der Praxis gezwungen, sich fur eine von mehreren moglichen Heuristiken zu

entscheiden, ohne gesicherte Ergebnisse daruber zu haben, da die gewahlte Heuristik

3

Zur groben Abschatzung der Leistungsfahigkeit von Heuristiken nimmt man Abschatzungen fur die

minimal oder maximal erforderliche Flache vor. Dies geschieht beispielsweise durch einfaches Aufaddieren

der Flache aller einzelnen Schaltungselemente unter Vernachlassigung des erforderlichen Platzes fur die

Verdrahtung.

3

1.2. KOMBINATORISCHE ASPEKTE DES SCHALTKREISLAYOUTS

13

bessere Ergebnisse herbeifuhrt als die zur Auswahl stehenden Alternativheursitiken.

Eine allgemeine heuristische Methode - divide and conquer - zerlegt das Gesamtproblem

in Teilprobleme, um diese nacheinander zu losen. In vielen Fallen sind die Teilprobleme

ihrerseits wieder NP-schwierig. Die Teilprobleme konnen rekursiv weiter in Teilteilprobleme zerlegt werden, bis zu einer geeigneten Komplexitat. Die nicht weiter unterteilten

Teilprobleme konnen dann entweder direkt optimal gelost werden, oder es konnen durch

schnelle Approximationsalgorithmen gute Losungen gefunden werden.

Eine der gangigsten Methoden, das Layoutproblem in Teilprobleme zu zerlegen besteht aus

dem folgenden: Als erster Schritt wird eine Plazierung der einzelnen Schaltkreiselemente vorgenommen. Anschlieend folgt eine globale Verdrahtungsphase bei der die einzelnen

Leitungen naherungsweise verschiedenen Bereichen des Chips zugewiesen werden. Danach

folgt eine detaillierte Verdrahtungsphase, die die Pfade fur die einzelnen Signalleitungen

bestimmt. Abschlieend kann noch eine geometrische Kompaktierungsphase durchgefuhrt

werden, um die benotigte Chipache zu verringern. Diese ganze Prozedur kann hierarchisch durchgefuhrt werden, indem zunachst nur einzelne Blocke einer Schaltung erzeugt

werden. Dieser Proze kann durch Algorithmen und Heuristiken realisiert werden, die

zwischen unterschiedlichen Layoutalternativen fur die einzelnen Blocke auswahlen. Die

Anordnung von Schaltungsblocken auf der Chipache wird auch als Floorplanning bezeichnet. Dabei konnen Blocke in ihrer Form auch variabel sein und beim Floorplanning

werden dann spezische Formen fur die einzelnen Blocke festgelegt.

Die genaue Art und Weise, wie ein Layoutproblem in Teilprobleme zerlegt werden kann,

hangt von der Entwurfsmethodik und der Herstellungstechnologie ab. Beispielsweise reduziert sich das detaillierte Verdrahtungsproblem bei dem Standardzellenentwurf im wesentlichen auf das Kanalverdrahtungsproblem. Im Gate-Array-Entwurf beinhaltet die Plazierungsphase eine Zuweisung von funktionalen Zellen des Schaltkreises auf Transistorzellen

des Masters. Die Reihenfolge der Entwurfsphasen ist das Ergebnis von langjahriger praktischer Erfahrung mit dem Einsatz von heuristischen Methoden beim Layoutentwurf von

Schaltkreisen. Eine notwendige Folge der heuristischen Vorgehensweise ist eine Einbue der Optimalitat des resultierenden Layouts. Qualitatseinbuen konnen an zwei Stellen

auftreten. Zum einen kann die naherungsweise Losung eines Teilproblems implizieren, da

die Gesamtlosung ebenfalls suboptimal ist. Auf der anderen Seite haben die unterschiedlichen Phasen des Layoutprozesses unterschiedliche Optimierungsfunktionen, die nicht immer miteinander in Einklang stehen. Zum Beispiel kann die Plazierungsphase versuchen,

die benotigte Verdrahtungsache zu minimieren - es mu aber auch die Verdrahtbarkeit in

ausreichendem Mae gewahrleistet sein. Da die Verdrahtung nach der Plazierung stattndet, kann die wahrend der Plazierungsphase veranschlagte Verdrahtungsache nur eine

grobe Abschatzung sein. Haug wird der halbe Umfang des alle Endpunkte eines Netzes

umspannenden Rechtecks genommen. Diese Abschatzung ist nur dann zutreend, wenn

das Netz ohne Umwege verlegt werden kann und - bei mehr als drei Endpunkten - die

Endpunkte nicht zu ungunstig verteilt sind. Somit kann diese Schatzfunktion nur eine

Untergrenze der tatsachlich benotigten Verdrahtungsache sein. Dadurch wurde bei der

Plazierung versucht werden, eine `falsche' Kostenfunktion zu optimieren. Dieses Abstimmungsproblem beim Layoutentwurf fur integrierte Schaltkreise stellt ein zentrales Problem

dar, das allgemein bei Problemen der kombinatorischen Optimierung auftritt. Dadurch

weicht man nicht nur vom Optimum ab, sondern es ist auch kaum moglich, das Ausma

14

KAPITEL 1. EINFUHRUNG

der Qualitatseinbue zu beschranken. Daher sind solchermaen erzeugte Losungen im

wahrsten Sinne des Wortes heuristisch. Es wird eine Losung gefunden, ohne da man

konkrete Aussagen uber ihre Qualitat machen kann. Daraus folgt auch, da heutzutage die Leistungen von Layoutsystemen nur untereinander verglichen werden konnen und

nicht mit der jeweils optimalen Losung. Dies wird mittels Testbeispielproblemen, die

allgemein als reprasentative Probleme angesehen werden, durchgefuhrt. Zur Zeit gibt

es allerdings keinen breiten Konsens daruber, welche Schaltungsbeispiele als allgemeine

Benchmarks angesehen werden konnen.

Fur einige Teilprobleme des Layoutproblems gibt es hervorragende Heuristiken. Dort

lassen sich teilweise sehr gute Obergrenzen fur die erzielte Abweichung von der optimalen

Losung beweisen.

Zum Beispiel konnten fur das Kanalverdrahtungsproblem schnelle Heuristiken entwickelt

werden, die hochstens eine oder zwei Verdrahtungsspuren mehr benotigen als unbedingt

erforderlich. Problematisch hierbei ist allerdings, da die hohe Qualtiat der Losungen

der einzelnen Kanalverdrahtungsprobleme bei der Zusammensetzung der verschiedenen

Teilproblemlosungen zu einer Gesamtlosung verloren geht. Als Konsequenz dieses Sachverhalts konnen keine absoluten Aussagen uber die Qualitat des resultierenden Gesamtlayouts gemacht werden.

Um die Gesamtleistung der verschiedenen Heuristiken zu verbessern, konnte man versuchen, die strikte Trennung der einzelnen Layoutphasen aufzulockern. Anstatt das Ergebnis

einer nachfolgenden Phase abzuschatzen, kann man versuchen, die nachfolgende Entwurfsphase in die augenblickliche Entwurfsphase zu integrieren. Dies wurde fur das Problem

der Plazierung und der daran anschlieenden globalen Verdrahtung von Homann [26]

durchgefuhrt. Siehe hierzu Abschnitt 3.1.6.

In diesem Abschnitt wurden allgemeine Probleme bei der Optimierung des Layoutentwurfs

angesprochen. Im folgenden Abschnitt wird auf die verschiedenen bekannten Strategien

fur den Layoutentwurf naher eingegangen.

Kapitel 2

Der Gate-Array-Entwurf

Zunachst soll auf die Besonderheiten des Entwurfs von integrierten Schaltungen auf GateArray-Master-Strukturen eingegangen werden. Im Anschlu daran wird ein U berblick

uber derzeit existierende Gate-Array-Entwurfssysteme gegeben. Nachfolgend wird dargestellt, inwiefern konzeptionelle Besonderheiten bei der Entwicklung von Entwurfswerkzeugen fur Gate-Arrays bestehen. Wie diese Besonderheiten in dem entwickelten System

GGADS berucksichtigt wurden, ist in Kapitel 4 beschrieben.

2.1 Schaltungsentwurf auf Gate-Array-Master-Strukturen

Die Besonderheiten bei Gate-Arrays bestehen im wesentlichen aus drei Punkten:

Die zur Realisierung einzelner Funktionen zur Verfugung stehenden Transistoren

sind in einem im vorhinein festgelegten geometrischen Raster angeordnet. Siehe

Abbildung 2.1. Damit sind auch die Dimensionierungen der einzelnen Transistoren

festgelegt. Somit kann beispielsweise die Ausgangstreiberstarke eines Gatters nicht

mehr beliebig an den individuellen Bedarf angepat werden, sondern nur noch in

Vielfachen eines einfachen Treibers realisiert werden. Der Entwurf hat sich an den

auf dem Master zur Verfugung stehenden Transistoren zu orientieren.

Durch die festgelegten Transistorpositionen konnen die sonst beliebig dimensionierbaren Verdrahtungskanale nur noch in einem bestimmten groben Raster dimensioniert werden. Entschliet man sich dazu, eine ganze Reihe von Transistorzellen

nur fur die Verdrahtung zu verwenden, so ist dies eine Entscheidung fur einen ganzen Block von Verdrahtungsspuren (haug in der Groenordnung von etwa 10 - 20

Spuren).

Werden Transistorzellen dazu `mibraucht', die Verdrahtung uber Ihnen durchzufuhren, so hat man dadurch teilweise keine gewohnlichen Verdrahtungskanale, wie

es beim Standardzellen- oder beim Vollkundenentwurf der Fall ist. Durch die darunterliegenden Polysilizium- und Diusionsbereiche ist es in manchen Fallen durch

15

KAPITEL 2. DER GATE-ARRAY-ENTWURF

16

Zelle 1

1

1

1

1

1

1

1

1

1

1

1

1

2

2

2

2

2

2

1

1

1

1

1

1

2

2

2

2

2

2

1

1

1

1

1

1

Zelle 2

Abbildung 2.1: Transistorzellen eines Gate-Arrays und deren Verteilung uber die

Chipache.

die Entwurfsregeln verboten, Vias zwischen der ersten und der zweiten Metallverdrahtungsebene zu legen. Dadurch ergibt sich ein erheblich verandertes Verdrahtungsproblem gegenuber dem ublichen Kanalverdrahtungsproblem.

Im folgenden Abschnitt wird kurz der Leistungsumfang von bisher vorhandenen Entwurfsystemen fur Gate-Arrays dargestellt, die exibel genug sind, um mit ihnen Entwurfe auf

unterschiedlichen Gate-Array-Master-Strukturen durchfuhren zu konnen. U ber eines der

ersten exiblen Entwurfsysteme wird in [57] berichtet.

2.2 Vorhandene Entwurfssysteme

Die folgenden Ausfuhrungen beziehen sich im wesentlichen auf die drei folgenden Entwurfssysteme:

TANGATE von Cadence (fruher von Tangcell).

GAS (Gate-Array System) von der Universitat Eindhoven [30].

Merlyn-G als Bestandteil des Gate-Array Working Systems (GAWS) von Tektronix.

Ein weiteres Gate-Array-Entwurfssystem in der neueren Literatur ist das ORCA System [29] von der Universitat Berkeley. Hierbei sind allerdings im wesentlichen nur neue

Entwurfsalgorithmen verwendet worden, die nicht spezisch fur Gate-Arrays sind, sondern gleichermaen fur den Standardzellen- oder den Vollkundenentwurf eingesetzt werden

konnen.

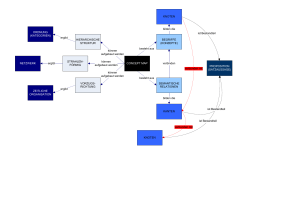

2.2. VORHANDENE ENTWURFSSYSTEME

17

Technologie

Master

Zellen

Master-,

Netzlistenkonvertierung

Netzliste

Zellen-,

TechnologieBibliothek

Plazierung

&

Verdrahtung

Extraktion

Maskengenerierung

Abbildung 2.2: Typischer Aufbau eines Halbkunden-Entwurfssystems

Im wesentlichen unterscheiden sich die genannten Systeme von Vollkundenentwurfssystemen dadurch, da die Funktionszellen nicht an beliebiger Stelle des Chips plaziert werden konnen. Sie konnen hingegen nur in einem festvorgegebenen Raster plaziert werden.

Der schematischer Aufbau der Systeme ist in Abbildung 2.2 zu sehen. Die verschiedenen

Eingabedaten sind ebenfalls der Abbildung zu entnehmen.

Der Aufbau aller genannten Systeme lat sich wie folgt beschreiben:

Zunachst sind zwei Teile zu unterscheiden. Der erste Teil enthalt die Datenbasis und geeignete Konvertierungsroutinen, wahrend der zweite Teil - die Plazierung und Verdrahtung

- das eigentliche Layout erzeugt.

Die Datenbasis enthalt

Eine Beschreibung der Master-Struktur. Dies beinhaltet die Groe des Masters, des

I/O Gebietes und des aktiven Gebietes. Weiterhin sind Plazierungsreferenzpunkte

zur Plazierung der Bibliothekslayouts von Funktionszellen gegeben. Damit sind auch

schon indirekt die Verdrahtungskanale deniert - wenn solche uberhaupt vorhanden

sind. Falls Power- und Groundverdrahtung vordeniert sind, so ist das jeweilige

Raster angegeben.

Die Beschreibung der physikalischen Realisierung von Funktionszellen. Die physikalischen Personalisierungsdaten der Funktionszellen enthalten die folgenden Punkte.

{ Die Hohe und Breite des Layouts.

{ Lage des Referenzpunktes.

18

KAPITEL 2. DER GATE-ARRAY-ENTWURF

{ Ort, Art und Namen der Terminals.

{ Die Innerzellverdrahtung, welche als Verdrahtungshindernisse deklariert wird.

{ Zusatzliche Eigenschaften der Zelle wie Symmetrieeigenschaften, aquivalente

Zellen und logisch aquivalente Pins.

Eine Technologiebeschreibung. Die Technologiebeschreibung enthalt im wesentlichen die Entwurfsregeln, die bei der Erzeugung des Gesamtlayouts der Schaltung

eingehalten werden mussen. Beispielsweise die Minimalabstande von Leitungen auf

der gleichen Metallebene.

Der zweite Teil des Halbkunden-Entwurfssystems ist der Plazierungs- und Verdrahtungsteil, der fur die Erzeugung eines korrekten Layouts verantwortlich ist. Wahrend die Systeme GAS, Merlyn-G und ORCA die Plazierung und detaillierte Verdrahtung streng

nacheinander durchfuhren, ist in dem System TANGATE ein Iterationszyklus implementiert. Bei GAS beispielsweise kann es geschehen, da eine durch die implementierten

Plazierungsverfahren - wahlweise ein analytisches Plazierungsverfahren oder ein Verfahren, das auf Simulated Annealing basiert - erzielte Plazierung der Zellen nicht von den

Verdrahtungsverfahren vollstandig verdrahtet werden kann ! Im Gegensatz dazu verfahrt

TANGATE wie folgt, falls dem lokalen bzw. detaillierten Verdrahtungsverfahren keine vollstandige Verdrahtung gelingt. TANGATE versucht zunachst einzelne Leitungen

wieder zuruckzunehmen und stattdessen Umwege fur diese Leitungen in Kauf zu nehmen, um eine vollstandige aber etwas langere Verdrahtung zu erreichen. Gelingt trotz

der in Kauf genommenen Umwege keine vollstandige Verdrahtung, so ist in TANGATE die Moglichkeit implementiert, die Plazierung einzelner Funktionszellen ebenfalls

zuruckzunehmen und neu zu plazieren. Anschlieend versucht das System erneut, die

lokale Verdrahtung vollstandig durchzufuhren. Durch diesen Iterationsproze, der prinzipiell beliebig oft wiederholt werden kann, erzielt TANGATE noch erstaunliche Verbesserungen gegenuber der ersten Plazierung und lokalen Verdrahtung. TANGATE ist - wie die

anderen erwahnten Systeme auch - nicht in der Lage, bei mehreren logisch aquivalenten

Pins eines Makros die ursprungliche Pin-Netz-Zuordnung der Netzliste zu permutieren.

Wie bereits erwahnt, bestehen alle genannten Systeme im Kern nur aus einem Plazierungsund Verdrahtungsverfahren fur vordenierte Bibliothekszellen auf einem Referenzpunktraster.

Daher ist keines dieser Systeme besonders dafur geeignet, unterschiedliche Master-Strukturen auf ihre Eignung zur Realisierung bestimmter Schaltungstypen zu vergleichen. Die

Systeme konnen fur unterschiedlich groe Gate-Array-Master eingesetzt werden. Sie

konnen auch mit variierenden Transistorzellen umgehen. Sie konnen allerdings nicht die

Layouts der einzelnen Makrofunktionen (NANDs, NORs, usw.) fur beliebige Transistorzellen selbstandig erzeugen. Bei allen Systemen ist gefordert, da die Layouts der

Makrofunktionen vom Benutzer angegeben werden. Wahrend diese Anforderung an den

Benutzer bei der praktischen Entwicklung von Schaltungen auf ein- und demselben Master

noch akzeptabel erscheint, eignen sich diese Systeme dadurch nicht dazu, unterschiedliche

Master-Strukturen zu entwerfen und auf ihre Tauglichkeit fur bestimmte Schaltungstypen

zu untersuchen.

Hervorzuheben ist, da selbst bei TANGATE, das den hochsten Reifegrad der vorgestellten Systeme aufweist, keine Permutierung von logisch aquivalenten Pins moglich ist.

2.3. KONZEPTIONELLE BESONDERHEITEN

19

Beispielsweise konnten die Eingangssignale eines 3-NAND-Gatters beliebig permutiert

werden, ohne die logische Funktion des Gatters in der Gesamtschaltung zu verandern.

Allerdings konnte die Verdrahtbarkeit erst durch ein Permutieren der Eingangssignale ermoglicht werden. In dem in dieser Arbeit vorgestellten Entwurfsystem GGADS

ist die Verbesserung der Anschlumoglichkeiten eines Makros durch Permutieren logisch

aquivalenter Signale realisiert.

2.3 Konzeptionelle Besonderheiten der

Gate-Array-Entwurfsautomatisierung

Die Besonderheiten im Abschnitt uber den Entwurf von Gate-Arrays stellen auch fur die

Entwicklung von Entwurfswerkzeugen fur Gate-Arrays besondere Schwierigkeiten dar.

Durch diese Besonderheiten konnen bekannte Standardentwurfsverfahren (fur Plazierung

und Verdrahtung) nicht unmittelbar fur den Gate-Array-Entwurf eingesetzt werden. Die

folgenden Punkte seien hervorgehoben:

Die Plazierung der einzelnen Makrozellen kann nur in einem vorgegebenen Raster

erfolgen.

Bei der Verdrahtung mu bei nicht-kanalorientierten Master-Strukturen die besonderen Einschrankungen fur das Setzen von Vias zwischen den verschiedenen Metallverdrahtungsebenen berucksichtigt werden. Wenn die verfolgte Entwurfsmethodik ein Verdrahtungskanalkonzept verfolgt, so kann die Kanalbreite (Anzahl der

Verdrahtungsspuren) nicht frei sondern nur in einem vorgegebenen Raster gewahlt

werden.

Fur den Zweck der Bewertung von frei kongurierbaren Master-Strukturen mu ein Entwurfssystem auch in der Lage sein, die Layouts fur Elementarfunktionen fur unterschiedlichste Transistorzellen selbsttatig zu entwerfen. Dabei mu das System in der Lage sein,

die spezischen Layoutregeln fur die einzelnen Transistorzellen zu beachten. Weiterhin

mu der Entwurf der Layouts fur die Elementarfunktionen geeignete Anschlumoglichkeiten

der Makrofunktionen erlauben. Welche Anschlupunkte besonders geeignet sind - ob z.B.

nur an der oberen und unteren Kante einer Transistorzelle Anschlusse herausgefuhrt werden oder zu allen Seiten oene Layouts erzeugt werden mussen - hangt von dem im System

verwendeten Entwurfsstil ab (z.B., ob der Entwurfsstil ein Kanalkonzept verfolgt oder ein

`over-the-cell-routing' durchfuhrt). Im nachsten Kapitel werden bekannte Entwurfsalgorithmen behandelt und einige neue Verfahren vorgestellt.

20

KAPITEL 2. DER GATE-ARRAY-ENTWURF

Kapitel 3

Algorithmen fur den physikalischen

Entwurf

In diesem Kapitel werden Algorithmen dargestellt, die zur Plazierung und Verdrahtung

von Bibliothekselementen eingesetzt werden konnen. Dazu werden zunachst bekannte

Verfahren kurz vorgestellt. Im Anschlu daran werden die eigens fur das Entwurfssystem GGADS entwickelten Verfahren vorgestellt. Hierbei handelt sich einerseits um das

neue globale Plazierungsverfahren SQP, dessen Leistungsfahigkeit sich als traditionellen

Plazierungsverfahren deutlich uberlegen herausstellte [26]. Weiterhin wird in GGADS

die globale Plazierungsphase und die globale Verdrahtung miteinander verschmolzen, um

ein verbessertes Gesamtergebnis zu erzielen. Fur die lokale Plazierung und Verdrahtung

wurde in GGADS ein vollig neues Konzept gewahlt. Es handelt sich dabei um ein konstruktives Verfahren, das plazierte Funktionszellen unmittelbar anschlieend verdrahtet.

Dadurch werden in einer Region nie mehr Funktionszellen plaziert als auch tatsachlich

verdrahtet werden konnen. Durch diese neuartige Vorgehensweise wird auch der Entwurf von Schaltungen, fur die ein zellbibliotheksorientierter Entwurfsstil ungeeignet ist,

unterstutzt. Dazu zahlen neben ECL-Schaltungen auch dynamische CMOS-Schaltungen

entsprechend der Domino-Logik.

Die folgenden Schritte werden gemeinhin bei der algorithmischen Vorgehensweise fur den

automatischen physikalischen Entwurf integrierter Schaltungen unterschieden.

Die Plazierung,

die globale Verdrahtung,

die lokale oder detaillierte Verdrahtung.

Zunachst werden zu allen drei Punkten bekannte Verfahren kurz vorgestellt. Bei der lokalen Verdrahtung wird wird deren Eignung fur die Verdrahtung auf frei kongurierbaren

Sea-of-gates Masterstrukturen erortert. Im Abschnitt 3.5 wird ein neues kombiniertes

lokales Plazierungs- und Verdrahtungsverfahren vorgestellt, das auf die besondere Problematik bei frei kongurierbaren Sea-of-gates Masterstrukturen zugeschnitten ist.

21

DEN PHYSIKALISCHEN ENTWURF

KAPITEL 3. ALGORITHMEN FUR

22

3.1 Die Plazierung

In diesem Kapitel wird zunachst allgemein auf das Plazierungsproblem bei der Layoutgenerierung eingegangen. Es werden bekannte Ansatze vorgestellt und in Abschnitt 3.4

wird ein neues Plazierungsverfahren - SQP vorgestellt, das in [26] vom Autor eingefuhrt

wurde. SQP wird in seiner Leistung mit traditionellen Verfahren verglichen. SQP stellt

sich dabei als den traditionellen Verfahren deutlich uberlegen heraus.

3.1.1 Losungsansatze zum Plazierungsproblem

Zur Losung des Plazierungsproblems sind in der Literatur verschiedene Ansatze vorgeschlagen worden.

Rekursive Partitionierungsverfahren (MinCut-Verfahren),

Kraftemodelle,

Probabilistische Verfahren (Simulated Annealing),

Analytische Verfahren,

Clusterverfahren,

Andere, weniger bedeutende Verfahren.

1

Haug unterteilt man die genannten Verfahrenstypen auch in iterative und konstruktive

Verfahren.

Iterative Plazierungsverfahren

Unter iterativen Plazierungsverfahren versteht man allgemein gesprochen alle Verfahren,

die mit einer wie auch immer gewonnenen, Initialplazierung beginnen und diese dann

iterativ zu verbessern suchen. Dafur wird einerseits ein Gutekriterium benotigt, mithilfe

dessen entschieden werden kann, welche von zwei Plazierungsalternativen als besser gelten

soll. Andererseits wird ein Abbruchkriterium fur den Iterationsproze benotigt, mithilfe

dessen entschieden werden kann, wann das Plazierungsverfahren keine weitere Verbesserung der gewonnenen Plazierung sucht und stattdessen terminiert. Somit kann man

allgemein bei Iterationsverfahren die folgenden drei Schritte unterscheiden:

1. Auswahl von Zellen, deren Plazierung abgeandert werden soll.

2. Neuplazierung dieser Zellen.

3. Bewertung der neuen resultierenden Gesamtplazierung.

Die Plazierung geschieht hierbei durch rekursive Partitionierung der Grundache und einer Zuordnung von Schaltungselementen zu den jeweils entstehenden partitionierten Flachen.

1

3.1. DIE PLAZIERUNG

23

8

-2

-4

-3

15

10

6

Abbildung 3.1: Angenommene Krafte bestimmen die iterativen `Verbesserungs'schritte.

Die rekursiven Partitionierungsverfahren bedienen sich fur jeden durchzufuhrenden Partitionierungsschritt in aller Regel iterativen Verbesserunsverfahren, die mit einer anfanglich

haug zufallig gewahlten Initialpartitionierung beginnen und sie schrittweise zu verbessern

suchen. Diese Klasse von Verfahren bendet sich in sehr breitem Einsatz und schneidet

bei Vergleichsstudien im allgemeinen auch stets als zumindest vergleichbar zu anderen

Verfahren in der resultierenden Plazierungsqualitat ab [19]. Sie werden in Abschnitt 3.1.2

ausfuhrlich behandelt. Iterative Verfahren nach Kraftemodellen verfolgen die Idee, Anziehungskrafte und Abstoungskrafte zwischen Zellen und moglichen Plazierungsorten anzunehmen. Somit wird bei jedem iterativen Verbesserungsversuch angestrebt, die Lange

der resultierenden Kraftvektoren jeder Zelle zu minimieren. Siehe Abbildung 3.1.

Verfahren, die auf der Idee des Simulated Annealing [32] beruhen, vertauschen zufallig

gewahlte Zellen miteinander. Dabei werden die zu vertauschenden Zellen nicht vollig

zufallig gewahlt; die Auswahl wird vielmehr durch bestimmte Parameter eingeschrankt.

Hierbei wird eine Verschlechterung der gegenwartigen Plazierung unter Umstanden auch

in Kauf genommen, um lokale Optima zu uberwinden und das globale Optimum anzustreben. Dabei wird eine Verschlechterung der gegenwartigen Plazierung nur mit einer

bestimmten Wahrscheinlichkeit akzeptiert. Die Wahrscheinlichkeit fur die Akzeptanz einer Verschlechterung wird dabei wahrend des Iterationsprozesses variiert - in der Regel

monoton abnehmend. Dies ist in Analogie zu dem physikalischen Proze des Abkuhlens

einer Flussigkeit zu sehen, wobei die Molekule gema des niedrigsten Energiestadiums angeordnet werden sollen. Wenn die Fluigkeit in der richtigen Geschwindigkeit abgekuhlt

wird, so ist die Wahrscheinlichkeit fur das Erreichen der richtigen Anordnung entsprechend gro. Das Energiestadium wird beim `Simulated Annealing' durch eine beliebige

zu optimierende Bewertungsfunktion ersetzt. Da sowohl die Abkuhlungsgeschwindigkeit

(Cooling schedule) wie auch die Optimierungsfunktion und die Modizierungsfunktion

nicht naher speziziert ist, handelt es sich bei Simulated Annealing also um eine ganze Klasse von Optimierungsverfahren. In der Tat hangt der Erfolg der Methode auch

sehr stark von der konkret gewahlten Modizierungsfunktion, der Optimierungsfunkti-

24

DEN PHYSIKALISCHEN ENTWURF

KAPITEL 3. ALGORITHMEN FUR

on und der `Abkuhlungsgeschwindigkeit' - der cooling schedule - ab [38, 1, 54]. Fur das

Plazierungsproblem konnten mit Simulated Annealing bisher vergleichbare Ergebnisse zu

rekursiven Partitionierungsverfahren erzielt werden [19, 12]. Allerdings sind die Rechenzeiten dafur in aller Regel sehr lang - um ein Vielfaches hoher als fur traditionelle rekursive

Partitionierungsverfahren.

Konstruktive Verfahren

Zu den konstruktiven Verfahren zahlen von den obengenannten die analytischen Verfahren und die Clusterverfahren (siehe z.B. [18, 31]). Charakteristisch fur sie ist, da die

Plazierung der Zellen konstruiert wird, anstatt eine Initialplazierung zu bestimmen und

diese dann iterativ zu verbessern. Die Partitionierungsverfahren konnen auch zu den konstruktiven Verfahren gezahlt werden, da sie die resultierende Plazierung sukzessive durch

rekursives Partitionieren konstruieren.

Clusterverfahren gehen von einem oder mehreren sogenannten Saatkornern aus, die

man anschlieend zu groeren Clustern wachsen lat. Die Saatkorner sind einzelne Zellen,

denen bestimmte Plazierungsregionen auf der Chipache zugeordnet werden und zu denen

nach bestimmten Kriterien weitere Zellen hinzugefugt werden, um Zellencluster enstehen

zu lassen.

Analytische Verfahren basieren auf der Losung bzw. Optimierung von Gleichungsoder Ungleichungssystemen. Aus den erhaltenen Werten fur die einzelnen Variablen lat

sich die Plazierung der einzelnen Zellen auf der Chipache herleiten. Neuere Ansatze

dieser Art nden sich unter anderem in [33, 34].

3.1.2 Das allgemeine Schaltkreispartitionierungsproblem

Die Partitionierung ist aus verschiedenen Grunden ein wichtiger Aspekt bei der Layouterzeugung. Auf der einen Seite kann die Schaltkreispartitionierung benutzt werden, um

einen Schaltkreis in mehrere kleinere Schaltkreise zu unterteilen, die ihrerseits auf jeweils

separaten Komponenten realisiert werden. Dies konnen beispielsweise mehrere Platinen

oder mehrere Mikrochips sein. In diesem Fall mu der ursprungliche Schaltkreis in mehrere Teilschaltkreise unterteilt werden, wobei fur jeden Teilschaltkreis eine feste maximale

Groe berucksichtigt werden mu. Die Leitungskomplexitat zwischen den einzelnen Komponenten ist dabei zu minimieren. Eine ubliche Art, den Begri der Leitungskomplexitat

zu formalisieren besteht hierbei darin, jedem Netz bestimmte Verbindungskosten zuzuordnen, um die Verbindungskosten aller Netze, die verschiedene Komponenten miteinander

verbinden, aufzuaddieren. Die Verbindungskosten eines Netzes konnen beispielsweise dazu genutzt werden, unterschiedliche Prioritaten fur Netze, die nicht uber die Grenzen

einer einzelnen Partition hinausgehen sollen, auszudrucken.

Eine zweite Anwendung der Schaltkreispartitionierung, die eigentlich groere Bedeutung

hat, besteht darin, einen Schaltkreis hierarchisch in Teile zu unterteilen. Dieser Proze

wird als Teil von divide-and-conquer Algorithmen zur Plazierung, fur das Floorplanning

und andere Layoutprobleme eingesetzt. Die Zielfunktionen, die dabei zu minimieren sind,

konnen variieren. In der Regel ahneln sie den genannten aufaddierten Verbindungsko-

3.1. DIE PLAZIERUNG

25

sten. Divide-and-conquer Strategien, die auf Schaltkreispartitionierung basieren, bieten

einen sehr nutzlichen Rahmen, um viele Layoutprobleme losen zu konnen und mehrere

Phasen des Layoutentwurfes integrieren zu konnen. Insofern sind gute Partitionierungsstrategien vielversprechende Hilfsmittel, um die Layoutentwurfstechnik auch in Zukunft

voranzutreiben.

Die Schaltkreispartitionierung lat sich als Operation auf Graphen und Hypergraphen

formalisieren. Damit ist die Partitionierungsoperation im Rahmen des Layoutentwurfes

nicht nur fur die Schaltkreispartitionierung interessant, sondern auch fur andere wichtige

Graphpartitionierungsaufgaben. Zum Beispiel um Verdrahtungsgraphen zu partitionieren. Bei dieser Anwendung reprasentiert der Verdrahtungsgraph die Topologie der Verdrahtungsregionen auf dem Chip. Anstatt alle Leitungen durch eine Verdrahtungsregion

nacheinander zu verlegen, versuchen die divide-and-conquer Algorithmen die Verdrahtungsregionen in Unterregionen zu unterteilen, um in jeder Unterregion alle vorkommenden Leitungssegmente quasi parallel zu verlegen. Am Ende mussen naturlich die berechneten Verdrahtungen aller Unterregionen zu einer Gesamtverdrahtung der ursprunglichen

Verdrahtungsregion zusammengestzt werden.

Das Schaltkreispartitionierungsproblem in seiner formalisierten Form als Partitionierung

von Graphen und Hypergraphen ist damit ein grundlegendes Problem, das an vielerlei

Stellen im Layoutentwurfsproze auftritt. Im folgenden werden Varianten des Schaltkreispartitionierungsproblems deniert, die interessant fur den Layoutentwurf sind. Dazu

werden Losungsverfahren erortert.

Zunachst wird auf bisher bekannte Komplexitatsergebnisse eingegangen. In den darauolgenden Abschnitten werden Algorithmen fur die Partitionierung in zwei Unterpartitionen

besprochen. Das Bipartitionierungsproblem spielt eine zentrale Rolle unter den verschiedenen Partitionierungsproblemen, die im Layoutentwurfsproze vorkommen. Bipartitionierung kann auch als eine Grundlage fur Heuristiken benutzt werden, die Graphen in

mehrere - also mehr als zwei - Komponenten unterteilen. In Abschnitt 3.1.1 wird ein

U berblick uber iterative Verbesserungsheuristiken fur Graph- und Hypergraphbipartitionierung gegeben. Diese Verfahren bilden zur Zeit die Basis fur die meisten in der Praxis

eingesetzten Partitionierungsverfahren.

2

3.1.3 Denitionen und Komplexitatsergebnisse

Alle hier besprochenen Varianten des Partitionierungsproblems zielen darauf ab, einen

Graphen oder Hypergraphen in mehrere Teile zu zerlegen. Dabei soll jeder Teil moglichst

wenige - am besten gar keine - Verbindungen mit den anderen Teilen haben. Der Graph

oder Hypergraph reprasentiert entweder einen Schaltkreis, wobei die Knoten Elemente reprasentieren und die Kanten bzw. Hyperkanten die verbindenden Netze darstellen. Diese

Anwendung wird im folgenden behandelt. Bei einer anderen Anwendung reprasentiert

der Hypergraph ein Verdrahtungsgebiet, wobei die Knoten switchboxes darstellen und die

Kanten fur Verdrahtungskanale stehen. Im zweiten Fall ist der Graph in der Regel planar.

Eine Formalisierung von Graph und Hypergraph ist im Anhang zu nden. Ein Hypergraph unterscheidet sich von einem Graphen dadurch, da seine Kanten mehr als zwei Knoten miteinander verbinden.

Sie entsprechen damit einem Mehrpunktnetz in einer Schaltung.

2

DEN PHYSIKALISCHEN ENTWURF

KAPITEL 3. ALGORITHMEN FUR

26

Die Partitionierung eines Graphen kann dadurch geschehen, da man entweder Knoten

(und die damit verbundenen Kanten) oder aber (Hyper-) Kanten des Graphen entfernt.

Die erste Variante kommt nur fur Graphen - nicht fur Hypergraphen - in Frage und wird

auch Graphseparierung genannt. Die Kosten einer Partitionierung werden dabei als die

gewichtete Summe der Zahl der entfernten Elemente bestimmt.

Bei der Partitionierung mussen haug verschiedene Einschrankungen berucksichtigt werden; z.B., da die Partitionen eines Schaltkreises festen Groenanforderungen genugen

mussen und die Zahl der Knoten jeder Partition ebenfalls in einem vorbestimmten Bereich liegen mu. Fur dieses Problem wird die Bipartitionierung besonders haug eingesetzt. Im folgenden werden die fur den Layoutentwurfsproze wichtigen Varianten des

Partitionierungsproblems deniert.

Zunachst soll das Problem der Multipartitionierung formal deniert werden.

Multipartitionierung

Instanz: Ein Hypergraph G = (V; E ) mit n Knoten und einer Knotengewichtsfunktion w : V ! N, einer Kantenkostenfunktion c : E ! N, einer Zahl r 2 N

von Partitionen, einer maximalen Partitionsgroe B (i) 2 N und einer minimalen

Partitionsgroe b(i) 2 N; i = 1; : : : ; r.

{ Kongurationen: Alle r-Partitionierungen = (VS; : : : ; Vr ) von V , mit Vi V ,

Vi =

6 ;, und Vi \ Vj = ; fur i; j 2 f1; : : : ; rg und ( ri Vi) = V .

Zulassige Losungen: Alle Partitionierungen = (V ; : : : ; Vr ) wobei

b(i) (Pv2V w(v)) B (i) fur alle i = 1; : : : ; r gilt.

{ Zu minimierende Kostenfunktion:

1

=0

1

i

Xr

c() := 12

i

=1

X c(e);

3

e2E ;i

ext

wobei

Eext;i = fe 2 E je \ Vi 6= ;; (e n Vi) 6= ;g die Menge aller externen Kanten der

Partition Vi ist. Siehe Abbildung 3.2.

Die Partitionierung mu die Beschrankung berucksichtigen, da die Groe der Partition

Vi zwischen bi und Bi liegt. Die Minimalpartitionsgroen sind erforderlich, um eine ausgeglichene Partitionierung zu erreichen, bei der alle Partitionen ungefahr von gleicher Groe

sind. Diese Forderung eignet sich besonders fur den Einsatz von Partitionierungsverfahren in divide-and-conquer Algorithmen. Die Groe einer Partition Vi ist die Summe ihrer

Knotengewichte. Dadurch kann Schaltkreisen mit Elementen unterschiedlicher Groe, wie

dies bei der Plazierung und dem Floorplanning vorkommt, Rechnung getragen werden.

Die Konstante 21 kann im Prinzip durch eine beliebige andere Konstante ersetzt werden.

gewahlt, um einen groenordnungsmassigen Bezug zu den `absoluten' Weglangen herzustellen.

3

1

2

wurde

3.1. DIE PLAZIERUNG

27

F

V

e2

G

e1

B

e 3H

E

D

A

C

J

I

G

e3

e4

F

J

V1

C

E

H

e1 B

A

e2

D

I

V2

V3

Abbildung 3.2: Erlauterung zur Denition der Multipartitionierung. Die unterschiedlichen Kosten von Hyperkanten werden durch die Strichbreite dargestellt. Zum Beispiel ist

e = fA; B; E; I g und e = fC; D; H g. Es gilt ferner Eext; = fe ; e ; e g. Eext;i ist die

Menge aller Hyperkanten, die Knoten sowohl innerhalb von Vi als auch auerhalb davon

enthalten.

1

2

1

2

3

4

DEN PHYSIKALISCHEN ENTWURF

KAPITEL 3. ALGORITHMEN FUR

28

Die Hyperkanten, die verschiedene Partitionen in verbinden, tragen zum Schnitt (cut)

bei. Die Kosten einer Partition c() wird auch die Schnittgroe genannt. Die Schnittgroe ist die Summe uber alle r Partitionen der gewichtete Summe aller Kanten, die eine

Partition verlassen.

Die Gewichte c(e) ermoglichen es, unterschiedliche Kosten fur unterschiedliche Kanten zu

veranschlagen. Dadurch konnen technisch bedingten Praferenzen (z.B. kritische Pfade)

fur die Verlegung eines Netzes innerhalb einer Partition Rechnung getragen werden.

Der Faktor von dient lediglich dazu, Kanten, die zwei Partitionen verbinden, mit c(e)

in die Gesamtsumme einieen zu lassen.

Hier wurden aber auch andere Denitionen der Schnittgroe vorgeschlagen. Donath [9]

schlagt beispielsweise vor, eine Kante e, die k Partitionen miteinander verbindet mit (k

1)c(e) in die Summe eingehen zu lassen. Die meisten popularen Partitionierungsverfahren

sind allerdings unabhangig von einer spezischen Schnittgroendenition.

Es ist festzuhalten, da Multipartitionierung NP-schwierig ist [15, 28]. Dies ist auch fur

eine ganze Reihe von eingeschrankten Problemvarianten der Fall. Zum Beispiel ist das

Multipartitionierungsproblem mit w = 1, c = 1, b(i) = 1 und B (i) = n fur alle i = 1; : : : ; r

immer noch NP-schwierig [28]. Das heit, selbst wenn praktisch keine Restriktionen fur

die Partitionsgroen bestehen und keine unterschiedlichen Kosten fur Kanten oder Knoten

berucksichtigt werden mussen.

1

2

Bipartitionierung

Der Sonderfall des Multipartitionierungsproblems, bei dem r = 2 gilt, wird Bipartitionierungsproblem genannt. Die Menge von Hyperkanten, die zum Schnitt beitragen wird hier

auch einfach Schnitt genannt. Die beiden zu bestimmenden Partitionen werden auch die

beiden Seiten des Schnitts genannt. Die Schnittgroe ist dabei die Summe der c(e) uber

alle Kanten e, die im Schnitt enthalten sind. Die Obergrenzen fur die Partitionsgr

oen

werden in der Regel gleichermaen wie folgt festgesetzt: B (1) = B (2) = Pv2V w(v) fur

ein gegebenes , mit < 1. (Siehe Abbildung 3.3.) Die Untergrenzen sind dann

b(1) = b(2) = 1. Die Zahl wird dabei auch der Balancefaktor genannt. Eine Partitionierung, deren Partitionsgroen innerhalb dieser Schranken liegen, wird auch -ausgeglichen

genannt. Falls die Zahl der Knoten n gerade ist und = gilt, so wird dieses Problem

auch das Bisektionierungsproblem genannt. Das Bisektionierungsproblem ist ebenfalls

NP-schwierig - selbst unter verschiedenen Einschrankungen bleibt es NP-schwierig [7].

1

4

2

1

2

3.1.4 Iterative Verbesserungsheuristiken fur Hypergraphbipartitionierung

Die kombinatorische Struktur von Partitionierungsproblemen ist bisher noch ziemlich wenig erforscht. Zur Zeit zahlen iterative Verbesserungsverfahren, die einzelne Knoten einer

gegebenen initialen Partitionierung verschieben, zu den erfolgreichsten Verfahren in der

Praxis. Obgleich es sehr schwer ist, theoretisch gesicherte Aussagen uber deren Leistungsfahigkeit zu machen, arbeiten diese Verfahren in der Praxis zufriedenstellend. Ein

4

Falls also = 21 gilt, so mussen beide Partitionen gleichgroe Knotenmengen enthalten.

3.1. DIE PLAZIERUNG

29

2

1

V

1

3

1

1

1

3

1

2

2

2

1

2

1

1

1

2

21

1

1 1

3

1

2

3

V1

1

1

V2

Abbildung 3.3: Das Balancekriterium bei der Bipartitionierung. Es gilt Pv2V w(v) =

1 + 1 + 1 + 2 + 2 + 2 + 3 = 12. Fur einen Balancefaktor

= 0; 75 ist die obige Partition

P

P

`balanciert'. Die Schnittkosten betragen c() = i e2E c(e) = ((1 + 3) + (1 +

3)) = 4

1

2

2

=1

1

ext;i

2

groer Vorteil dieser Verfahren ist, da sie sich auf vielerlei Varianten des Partitionierungsproblems anwenden lassen. So ist es kein Problem, unterschiedliche Kanten- oder

Knotengewichte zu berucksichtigen. Ob Graphen oder Hypergraphen partitioniert werden

sollen, macht fur diese Verfahren ebenfalls keinen wesentlichen Unterschied. Im folgenden

wird zunachst die Kernighan-Lin Heuristik dargestellt. Sie war historisch die erste einer

Reihe von verwandten und zunehmend verfeinerten Heuristiken zur Partitionierung und

im Besonderen auch zur Partitionierung fur das Plazierungsproblem.

Die Kernighan-Lin Heuristik

Zunachst soll das Problem der Graphbipartitionierung betrachtet werden. Ein einfaches

Verfahren dafur ist das folgende: Man beginnt mit irgendeiner initialen Partitionierung

und vertauscht anschlieend jeweils einen Knoten aus der einen Partition mit einem anderen Knoten aus der gegenuberliegenden Partition. Dadurch konnen alle Knoten, die

eigentlich in der gegenuberliegenden Partition sein muten, um eine minimale Schnittgroe zu erzielen, in die `richtige' Partition uberfuhrt werden. In Abbildung 3.4 ist ein

Beispielgraph zu sehen, der aus 18 Knoten und 34 Kanten besteht.

Bei 18 Knoten gibt es ( )=2 = 24310 verschiedene Bisektionen. Wenn man immer denjenigen Knoten aus beiden Partitionen auswahlt, deren Austausch die grote Schnittgroenreduzierung mit sich bringt, so besteht die Gefahr, in einem lokalen Minimum zu

landen. In Abbildung 3.4 zeigt die Schnittlinie S eine Bipartitionierung an, die ein lokales Minimum ist. Die Schnittgroe von S betragt 10. Einerlei, welche Knoten aus

jeder der beiden Partitionen in die jeweils andere Partition bewegt werden, die resultierende neue Schnittgroe ist in jedem Fall groer als die Schnittgroe von S . Um dies

zu vermeiden, schlagen Kernighan und Lin das folgende Verfahren vor. Es wird stets

dasjenige Knotenpaar bestimmt, deren Vertauschen die grote Schnittgroenreduzierung

oder aber die kleinste Schnittgroenerhohung mit sich bringt. In Abbildung 3.4 ist das

18

9

0

0

0

30

DEN PHYSIKALISCHEN ENTWURF

KAPITEL 3. ALGORITHMEN FUR

1

3

7

2

5

8

6

4

9

S opt

16

10

14

11

17

12

15

13

18

S0

Abbildung 3.4: Ein Beispielgraph fur die Bipartitionierung.

Knotenpaar f4; 10g ein Beispiel dafur. Das Vertauschen dieser beiden Knoten erhoht die

Schnittgroe um 2. Dieser Austausch wird zunachst nur vorlaug durchgefuhrt. Nach

dem Austausch werden beide Knoten in ihrer neuen Partition xiert. Das heit, sie stehen fur einen weiteren Austausch (eventuell mit einem anderen Knoten) nicht mehr zur

Verfugung. Anschlieend wird unter den verbleibenden noch nicht xierten Knoten ein

neues Knotenpaar fur den Austausch nach dem genannten Kriterium bestimmt. Im Beispiel von Abbildung 3.4 ist das Paar f2; 12g fur den zweiten Austausch geeignet. Dies

wird solange fortgesetzt, bis mindestens alle bis auf einen Knoten xiert sind. Dabei

wird nach jedem einzelnen Austausch die resultierende Schnittgroe und die dabei verschobenen Knoten gespeichert. Am Ende wird die kleinste in der Sequenz aufgetretene

Schnittgroe bestimmt und die dazugehorige Partitionierung rekonstruiert. Durch diese

Vorgehensweise konnen lokale Minima uberwunden werden. Die weitere Vorgehensweise

fur das Beispiel in Abbildung 3.4 ist in Tabelle 3.1 dargestellt.

Wie man sieht, fuhrt in diesem Fall das Verfahren von Kernighan und Lin dazu, da die

Knotenmengen f1; 2; 3; 4g und f10; 11; 12; 13g miteinander vertauscht werden, und dabei

ein globales Minimum fur die resultierende Schnittgroe erzielt wird.

Abbildung 3.5 zeigt einen Durchlauf der Kernighan-Lin Heuristik. Ein Durchlauf kann seinerseits wiederum in einem lokalen Minimum enden. Aus diesem Grund kann ein weiterer

Durchlauf, der als initiale Partitionierung das Ergebnis des vorhergehenden Durchlaufs

hat, eine weitere Verbesserung der Schnittgroe ergeben. In der Regel wird nach wenigen

solcher Durchlaufe - oft nicht mehr als funf - keine weitere Verbesserung mehr erzielt.

Die Laufzeitkomplexitat eines einzelnen Durchlaufs der Kernighan-Lin Heuristik wird im

wesentlichen durch die drei enthaltenen Schleifen bestimmt. Wenn alle Knotenpaare im

3.1. DIE PLAZIERUNG

Schritt Knotenpaar Schnittgroe A nderung

0

10

0

1

f4; 10g

12

2

2

f2; 12g

12

0

3

f1; 13g

8

-4

4

f3; 11g

2

-6

5

f7; 18g

6

4

6

f8; 17g

10

4

7

f5; 15g

12

2

8

f9; 16g

12

0

9

f6; 14g

10

-2

Tabelle 3.1: Die einzelnen Tauschoperationen der Kernighan-Lin Heuristik fur das

Beispiel aus Abbildung 3.4

(1) while vertauschbares Knotenpaar vorhanden do

(2)

while noch weiterer verschiebbarer Knoten vA in A do

(3)

while noch weiterer verschiebbarer Knoten vB in B do

(4)

Bestimme Schnittgroenreduzierung bei Vertauschen von vA und vB

(5)

if (Gewinn(vA; vB ) > Maxgewinn)

(6)

Speichere (vA; vB ) als Maxpaar

(7)

(8)

(9)

endif

endwhile

endwhile

Vertausche (vA; vB ) und xiere vA und vB

if (Neue Schnittgroe < Lokaler Bestschnitt)

Speichere momentane Partitionierung als lokale Bestpartitionierung

endif

endwhile

Abbildung 3.5: Die Kernighan-Lin Heuristik im U berblick

31

DEN PHYSIKALISCHEN ENTWURF

KAPITEL 3. ALGORITHMEN FUR

32

Minimisierungsproze berucksichtigt werden, ist der Zeitaufwand von der Groenordnung

O(n ). In der Praxis kann der Algorithmus etwas beschleunigt werden, aber typischerweise bleibt immer noch ein Zeitaufwand von O(n log n).

Bei Layoutproblemen kommt es vor, da beispielsweise Padanschlusse berucksichtigt werden mussen, d. h. da bestimmte Knoten einer festen Partition zugeordnet werden

mussen. Dies lat sich leicht bei der Kernighan-Lin Heursitik berucksichtigen, indem

einfach die Knoten, die den Padzellen entsprechen, bereits in der initialen Partitionierung als xiert markiert werden. Dadurch ist sichergestellt, da diese Knoten auch in der

resultierenden Partitionierung noch in der richtigen Partition liegen.

Abgesehen davon, da sich bisher noch keine theoretischen Aussagen uber die Qualitat des

Partitionierungsergebnisses beweisen lieen, hat die Kernighan-Lin Heuristik auch noch

weitere Nachteile:

3

5

2

1. Die Heuristik berucksichtigt nur Knoten, die ein einheitliches Gewicht haben. Unterschiedlichen Groen von Knoten, wie es bei der Schaltkreispartitionierung die

Regel ist, kann nicht ohne weiteres Rechnung getragen werden. Kernighan und Lin

schlagen fur dieses Problem vor, die Gewichte eines Knoten durch eine Clique von

mehreren Knoten zu reprasentieren. Dies wurde allerdings die Gesamtknotenanzahl

drastisch erhohen.

2. Die Heuristik erzielt nur Bisektionen. Beide Partitionen enthalten stets gleichviele Knoten. Diese Einschrankung kann eliminiert werden, indem Dummy-Knoten

eingefuhrt werden, die keine Kanten haben. Dadurch geht das Verschieben eines

Dummy-Knotens nicht in die resultierende Schnittgroe ein. Dies hat allerdings

den Nachteil, da die Heuristik keinen Unterschied zwischen einer mehr und einer

weniger ausgeglichenen Partitionierung macht, wenn beide die gleiche Schnittgroe

haben.

3. Die Heuristik kann keine Hypergraphen behandeln. Fur den Schaltkreisentwurf ist

dies jedoch eine wichtige Forderung, da Netze, die mehr als zwei Anschlupunkte

haben, in Graphen nicht angemessen dargestellt werden konnen.

4. Die Laufzeitkomplexitat eines Durchlaufs ist immer noch ziemlich gro (O(n ) bei

n Knoten).

5. Die Heuristik beinhaltet noch einen erheblichen Anteil an Nichtdeterminismus insofern, da das jeweils auszutauschende Knotenpaar nicht eindeutig bestimmt ist.

Zum Beispiel hatte in Abbildung 3.4 als erstes Knotenpaar auch das Paar f4; 5g

anstatt f4; 10g gewahlt werden konnen. In Diesem Fall hatte die Heuristik in der

Folge nicht das globale Optimum gefunden.

3

Die Zahl der Durchlaufe jeder Schleife hangt linear von der Zahl der insgesamt vorhandenen Knoten

ab. Da es sich um 3 ineinandergeschachtelte Schleifen handelt, ist der Rechenzeitaufwand also von der

Groenordnung n3 .

5

3.1. DIE PLAZIERUNG

33

Die Fuduccia-Mattheyses Heuristik

Fiduccia und Mattheyses fuhrten in [13] die folgenden neuen Ideen zur Kernighan-Lin

Heuristik ein:

1. Zu jedem Zeitpunkt wird immer nur ein einzelner Knoten von einer Partition zu der

jeweils gegenuberliegenden Partition verschoben. Durch diese Veranderung konnen

ungleich groe Partitionen erzeugt werden. Gleichermaen wird dadurch die Handhabung von unterschiedlich groen Knotengewichten ermoglicht.

2. Die Berechnung der Schnittgroenveranderung wird dahingehend erweitert, da anstatt Kanten nun auch Hyperkanten korrekt gehandhabt werden konnen. Die grundlegende Beobachtung hierzu wurde allerdings bereits von Schweikert und Kernighan

in [53] gemacht.

3. Einen beschleunigten Algorithmus mit geeigneten Datenstrukturen fur die Auswahl