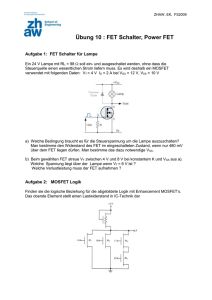

(Microsoft PowerPoint - FET_Lect10.ppt [Kompatibilit\344tsmodus])

Werbung

![(Microsoft PowerPoint - FET_Lect10.ppt [Kompatibilit\344tsmodus])](http://s1.studylibde.com/store/data/019764160_1-d55e77309077937b8232b93d955bd22b-768x994.png)

FET Switch & Power © Roland Küng, 2010 1 without quad. term ohmic resistor 2 Review Bias Verstärker Datenblatt: K = 2.5 mA/V2, Vt = 2 V, Wahl ID = 10 mA, VDS = 4 V, VDD = 12 V RS = 300 Ω, R1 = 500 kΩ, VGS > Vt iD = K( v GS − Vt )2 VG = VDD R2 R1 + R 2 FET Typ? VS = ? VGS = ? VG =? VD = ? RD = ? R2 = ? Check VDS > VGS - Vt Lösung: NMOS-E, 3 V, 4 V, 7 V, 7 V, 500, 700 k, 4 V > 2 V ok 3 FET als Schalter …heisst FET als niederohmigen Widerstand betreiben Bedingung: v DS < VGS − V t NMOS v DS > VGS − V t PMOS Gleichung: iD = 2 ⋅ K( v GS − Vt )v DS oder rDS = v DS 1 = iD 2 ⋅ K( v GS − Vt ) 4 FET als Schalter Bedingung Triode Range: VG v DS ≤ v GS − V t NMOS v DS ≥ v GS − V t PMOS Design: Wähle vDS (kleiner Wert) Berechne ID mit Vorgabe VDD und RD Berechne VGS mit FET Gleichung (ohmic region) Erzeuge VGS Gleichung: iD = 2 ⋅ K( v GS − Vt )v DS oder rDS = v DS 1 = iD 2 ⋅ K( v GS − Vt ) 5 FET als Schalter Bedingung v DS Triode Range : ≤ v GS − V t NMOS − D Beispiel: VG RD = 1 k, VDD = 5 V, VDS = 0.1 V, K = 10 mA/V2, Vt = 3 V ID = 4.9/1k = 4.9 mA rDS = 20.4 Ω, VGS – Vt = 2.45 V VGS = 5.45 V VG = VGS + VS = 5.45 V check Triode Range: 0.1 < 2.45 ok Gleichung: iD = 2 ⋅ K( v GS − Vt )v DS oder rDS = v DS 1 = iD 2 ⋅ K( v GS − Vt ) 6 FET als Schalter Bedingung Triode Range : v DS ≥ v GS − V t PMOS Beispiel: RD = 1k, VSS = 5 V, VDS = -0.1 V, K = 10 mA/V2, Vt = -3 V ID = 4.9/1k = 4.9 mA rDS = 20.4 Ω, VGS – Vt = -2.45 V VGS = -5.45 V VG = VGS + VS = -0.45 V check Triode Range: -0.1 > -2.45 ok Gleichung: iD = 2 ⋅ K( v GS − Vt )v DS oder rDS = v DS 1 = iD 2 ⋅ K( v GS − Vt ) 7 CMOS Schalter/Logik • Stufe invertiert den Eingangszustand • Immer einer der beiden Schalter FET ist off • Stromverbrauch im statischen Zustand praktisch NULL (10 nW) • Im dynamischen Fall müssen die Kapazitäten der FET und der Last umgeladen werden Stromverbrauch ca. 1mW/MHz • Versorgungsspannungen von 0.75 V bis 15 V sind herstellbar • Ausgang erreicht den maximalen Hub VDD • Eingang ist sehr hochohmig (MΩ) 8 P P NAND N N NOR 9 Analog Schalter Single Type Es muss sichergestellt sein, dass FET im Triode Range arbeitet. FET stellt dann Widerstand rDS dar rDS nur für kleine Signalpegel konstant (vGS variiert!) Dual Type (Transmission Gate) N und P leiten je nach Signalpegel verschieden stark insgesamt ausgeglichener rDS 10 Lineare Spannungsregler Linearer Spannungsregler mit Z-Diode (Längsregler) + VEIN + VAUS BJT: + Erlaubt grössere Lastströme als IZT - Nicht regelbar, nicht einstellbar - VBE ungenau - nur mit BJT empfohlen VAUS = VZ – 0.7 11 Lineare Spannungsregler Linearer Spannungsregler mit variabler Spannung (Längsregler): Familie 78xx VBE wird durch OpAmp ausgeglichen + VEIN VAUS = VZ R1 + R2 + R3 R2 + R3 VB < VOPmax < VEIN VE = VB -0.7 + VAUS • Statt BJT auch Enh. NMOS einsetzbar • Max. OpAmp Ausgangsspannung = Vein • VCE muss typ. ≥ 2 V sein (OpAmp Sättigung) • Auch PNP oder PMOS 12 (OP-Eingänge vertauschen) LDO LDO: Low Dropout Regler Für PNP, PMOS reicht die max. OpAmp Ausgangsspannung auch für • PNP-Transistor Betrieb im Sättigungsbereich • PMOS FET Betrieb in der Ohmic Region • Dropout typ. 0.3 – 0.7 V erreichbar E C VB = VEIN - 0.7 < VOPmax VC = VE -0.3 Low-Dropout PNP Regulator VOPmax = VInput S D VG = VEIN - Vt < VOPmax VD ≈ VS Low-Dropout P-Channel MOSFET Regulator 13 Längsregler 78XX (für negative Spannungen: 79X) 14 Längsregler Variabel IO < 1.5 A VREF = 1.25 V ± 50 mV IADJ = 50..100 µA, Voltage & Load Variation < 5 µA 15 Lab Längsregler Q1, Q2: 2N2219 OP: uA741 an VIN, GND D1: 4.7 V oder 5.1 V Messen: ∆Vout = f(Vin) ∆Vout = f(RL) VIN = 9…15 V, 10 µF on Board IZ = 10 mA @ Vin = 12 V R2 = 4.7 kΩ VOUT = 9 V RL = 22k, 2200, 820, 220 Ω Kurzschlussstrom: 50 mA Messen mit RL = 100 Ω, 0 Ω Q2 stiehlt Basisstrom von Q1 uA741 ist kurzschlussfest: Imax=20 mA 16 Schaltregler (Power) Linearer Spannungsregler haben geringen Wirkungsgrad, dafür ein Ausgangssignal ohne jeden Ripple Wirkungsgrad sind aber wichtig für: 17 Schaltregler engl. Switching Regulator, DC-DC Converter Ansatz: Anstelle des linear betriebenen Transistors einen Umschalter benutzten V0 VS Buck Converter (Abwärtsregler) VS Was ist zu erwarten? V0=D·VS Mittelwert der Rechteckspannung 18 Buck Converter V/I Verlauf Betrachtungsweise LC als Mittelwert-Filter 19 Buck Converter Betrachtung V/I in Schalterphasen Phase 1 Cap. Current Remember Diode ist in Sperrrichtung betrieben Spannung über L ist VS-V0 Strom durch L nimmt linear zu Energie wird in Induktivität gespeichert Der Kondensator wird geladen diL dt dv iC = C C dt vL = L 20 Buck Converter Betrachtung V/I in Schalterphasen Phase 2 Cap. Current Remember Strom durch L muss weiter fliessen in gleicher Richtung Diode ist im Flussbetrieb (Schottky Diode verwenden) Spannung über L springt von VS-V0 auf -V0-VD Strom durch L nimmt linear ab Induktivität gibt Energie an C weiter Note: Nutze Modell ideale Diode VD = 0 diL dt dv iC = C C dt vL = L 21 Buck Converter Betrachtung V/I in Schalterphasen Phase 2 Cap. Current Zeitlich parallel zum Laden: Sobald über C eine Spannung liegt fliesst ein Strom durch R Die Kapazität wird entladen Es stellt sich ein Gleichgewicht ein: Mittelwert der Rechteckspannung V0 = D·VS D = Tastverhältnis am Schalter, D = Ton/(Ton+Toff) V0 weist einen geringen Dreieck Ripple auf mit der Schatlfrequenz 22 Buck Converter Realisierung mit Power FET und Schottky Diode FET: Enh. PMOS (auch NMOS) VS V0 iL springt nicht ! Gleichgewicht: Mittelwert iL = Laststrom Io 23 Buck Converter V/I Verlauf VDiode VS Vo Vo = VDiode gemittelt 24 Buck Converter Praxis • Regelung der Spannung über das Tastverhältnis D • Ersetzen Diode durch zweiten Power FET P-CH N-CH fs: Schaltfrequenz Io: Laststrom ∆Vout: Ausgangs-Ripple ohne Herleitung (Richtwert) RF ⋅ ( Vin − Vout ) ⋅ D Lf = fs ⋅ Io RF = 2...10 D = Vout/Vin Cf = Reservefaktor RF bei Lf verhindert Lücken und Sättigung von IL und zu hohe Stromspitzen im Switch 1 Vout (1 − D) 8 ∆Vout fs 2L f 25 Buck Converter Beispiel Lf = RF ⋅ ( Vin − Vout ) ⋅ D fs ⋅ Io Cf = 1 Vout (1 − D) 8 ∆Vout fs 2L f Schaltfrequenz fs = 50 kHz Eingangsspannung Vin = 12 V Ausgangsspannung Vout = 3 V Wunsch Ripple ∆Vout = 0.1 V Min. Ausgangsstrom I0 = 2 A RF = 10 Lf = 10 ⋅ (12 − 3) ⋅ 0.25 = 225µH 50000 ⋅ 2 D = Vout/Vin = 0.25 (25%) Cf = 3 ⋅ 0.75 = 5µF 8 ⋅ 0.1⋅ 50000 2 ⋅ 225µ 26 Buck Converter: Regelung Prinzip Bild als Vergleich zu Linear Regler, Q1 ideal im Schalterbetrieb Hauptvorteil für Schaltregler: Wirkungsgrad erhöhen Hauptnachteil: Takt benötigt Puls-Breiten Modulator (PWM) Takt-Ripple überlagert an Last 27 Buck Converter: Regelung OpAmp in Gegenkopplung: Note: Q1, D1 ideal a) Vin sinkt: Vout versucht zu sinken Vout = Vref (R1+R2)/R2 = D Vin Praxis: Anstelle OpAmp wird ein komplexer Regler verwendet b) Vin steigt: Vout versucht zu steigen 28 Beispiel Buck Converter Chip L1 D1 C2 Buck IC 29 Boost Converter Wunsch nach Versorgungsspannung ab Batterie mit geringer Spannung VS << V0 Umbau VS Vo VS Vo 30 Boost Converter diL dt dv C iC = C dt vL = L Vo VS VS Vo v Strom steigt linear an iL = S t L L lädt Energie auf C liefert den gesamten Laststrom VS Vo Spannung über L springt auf VS-V0 Strom nimmt ohne Sprung linear ab 31 L entlädt Energie in C und R Boost Converter VS DTS (1-D)TS Endzustand ? VS - Vo Gleichgewicht erreicht wenn: Mittelwert iL = Laststrom Io d.h. wenn Wechselsignalanteil von iL über eine Periode gemittelt Null ist Ts iL = Io = Io + ∫ v L ( t )dt o = Io + VSDTS + ( VS − V0 )(1 − D)TS 0 V0 = VS 1− D 32 Boost Converter: V/I Verlauf Vswitch VS Vo Vo = VSwitch Spitzenwert 33 Boost Converter P-CH Nie ohne Last ! Vout ∞ N-CH fs: Schaltfrequenz Io: Laststrom ∆Vout: Ausgangs-Ripple ohne Herleitung (Richtwert) RF ⋅ Vin2 ⋅ D Lf = fs ⋅ Io ⋅V out RF = 2...10 1-D = Vin / Vout D ⋅ I0 Cf = fs ⋅ ∆Vout 34 Tool: http://www.daycounter.com/LabBook/BoostConverter/Boost-Converter-Equations.phtml Boost Converter Beispiel RF ⋅ Vin2 ⋅ D Lf = fs ⋅ Io ⋅ Vout Cf = D ⋅ I0 fs ⋅ ∆Vout Schaltfrequenz fs = 50 kHz Eingangsspannung Vin = 1.2 V Ausgangsspannung Vout = 5 V Wunsch Ripple ∆Vout = 0.2 V Min. Ausgangsstrom I0 = 50 mA RF = 10 10 ⋅ 1.22 ⋅ 0.76 Lf = = 876µH 50000 ⋅ 0.050 ⋅ 5 D = (Vout-Vin)/Vout= 0.76 (76%) Cf = 0.76 ⋅ 0.050 = 3.75µF 0.2 * 50000 35 Boost Converter Chip fs automatic adaptive up to 1 MHz 36 Boost Converter: Applikation Batteriespeisung Solarzellen + hoher Wirkungsgrad - Ripple mit Taktfrequenz überlagert 37 Klasse D Verstärker Vom Buck Converter zum Audio Verstärker Hohe Gleichspannung Lautsprecher Audiosignal Unterschiede: Tastverhältnis variabel Strom aus Cf abziehen durch Last und nachladen über Buck Lf, Cf als Filter für 20 kHz auslegen Taktrate so hoch wie möglich 38 Klasse D Verstärker N-CH und P-CH MOSFET 39 Klasse D Verstärker High Power mit Feedback Regelung für Pout 40 Zusammenfassung FET sind auch als Schalter vielseitig: Digital Logik (CMOS) und Schalter für Analogsignale |VDS| muss dafür viel kleiner VGS-Vt sein. Dimensionierung: VDS vorgeben, ID bestimmen, VGS berechnen. Lineare Spannungsregel zeigen ein sauberes Ausgangssignal, weisen aber meist einen schlechten Wirkungsgrad auf. Durch geschalteten MOSFET und Induktivität kann Energie von Eingangsquelle in Ausgangsquelle gewandelt werden. Tastverhältnis bestimmt Ausgangsspannung. typ. Wirkungsgrad > 90% Nachteil: Ausgangssignal enthält Ripple und spektrale Störungen Es gibt Abwärtswandler (Buck) und Aufwärtswandler (Boost) IC‘s bei denen nur L und C extern zugeschaltet werden müssen Ein Regelkreis sorgt für die korrekte Ausgangspannung bei variabler Quelle und Last 41 Buck & Boost Lab Berechnen und bauen sie nacheinander die folgenden getakteten Regler und messen die interessanten Grössen heraus: Variables D*, Vout, variable Last, Wirkungsgrad. Buck: 8 VDC auf 4 VDC, Laststrom 200 mA (4 R‘s parallel), fs = 5 kHz, Ripple 100 mV Boost: 1.5 V AAA Batterie auf 3 V, Last 1..2 LED parallel à 20 mA, fs = 5 kHz, Ripple 200 mV P N Takt: 0V/8V Rechteck 50 Ω Generator N *Einige Lab Geni erlauben nur fixes D= 0.5 P.S. Steckbrett schlecht geeignet, erlaubt nur fs = 5...20 kHz und qualitative Resultate. RF = 4 L- Wert: nur 10 mH und 20 mH vorhanden P-Enh MOSFET: IRF9540 (Vt -2...-4 V), N-Enh MOSFET: IRF 510 (Vt 2…4 V), Diode: Schottky Power:1N5818 42 http://www.daycounter.com/Calculators/Switching-Converter-Calculator.phtml