Dynamische Rekonfiguration von arithmetischen Einheiten auf

Werbung

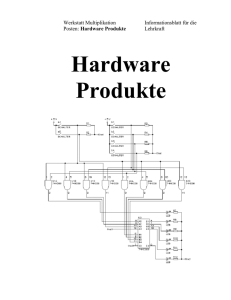

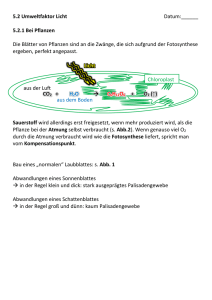

Advances in Radio Science, 3, 319–323, 2005 SRef-ID: 1684-9973/ars/2005-3-319 © Copernicus GmbH 2005 Advances in Radio Science Dynamische Rekonfiguration von arithmetischen Einheiten auf Bitebene O. A. Pfänder and H.-J. Pfleiderer Universität Ulm, Abt. Allgemeine Elektrotechnik und Mikroelektronik, Albert-Einstein-Allee 43, D-89081 Ulm, Germany Zusammenfassung. Im Hinblick auf Flexibilität und Effizienz beim modernen Schaltungsentwurf lohnt es sich oft, arithmetische Basiseinheiten mit passend gewählter fixer Wortlänge so zu erweitern, daß sich in Zusammenschaltung mit anderen Elementen eine übergeordnete Funktionalität mit erweiterter Bitbreite erreichen läßt. In diesem Beitrag soll die Multiplikation als konkretes Anwendungsbeispiel herangezogen werden. Dabei liegt das Hauptaugenmerk darauf, wie mit geringem Aufwand aus einer grundlegenden starren Struktur ein dynamisch rekonfigurierbarer Multiplizierer hervorgehen kann, der sowohl für vorzeichenlose als auch vorzeichenbehaftete Zahlen in den wichtigsten Zahldarstellungen geeignet ist. Die Vorgehensweise basiert auf dem Einsatz von Multiplexern auf Bitebene. 1 Einführung Rekonfigurierbare Hardware ist heute in verschiedenen Granularitäten bekannt, wovon sich einige der Varianten nicht nur einmalig, sondern auch zur Laufzeit konfigurieren lassen (Bondalapati and Prasanna, 2002). Auf diese Art sind etwa dynamisch veränderliche Multistandardoder Multiprotokoll-Chips realisierbar, von denen man sich zukünftig erhofft, dass hohe Masken- und andere Herstellungskosten besser amortisiert werden können. Außerdem kann das Layout einer überschaubaren Grundeinheit, die als Einzelteil zur Zusammenstellung eines komplexeren Systems dient, weitaus besser optimiert werden als ein unhandlicher Monolith. In vielen Einsatzgebieten wie z.B. bei der elektronischen Bildverarbeitung spielen komplexe arithmetische Operationen eine entscheidende Rolle und stellen hohe Anforderungen an Algorithmik und Hardware. Besonders häufig auftretende Operationen werden üblicherweise in die Hardwareseite verlagert (Oklobdzija, 2000), um die geforderte Rechengeschwindigkeit und den notwendigen Datendurchsatz erreichen zu können. Eine Multiplikation mit nicht konstanten Correspondence to: O. A. Pfänder ([email protected]) Faktoren gehört aus Sicht der Hardware-Entwicklung zu diesen komplexen arithmetischen Operationen und deren Realisierung kann sehr aufwendig und flächenintensiv werden. Obwohl in jüngster Zeit “Field-Programmable Gate Arrays” (FPGAs) immer leistungsfähiger werden und die Ressourcen zur zahlreichen und parallelen Implementierung solch aufwendiger Rechenschritte bieten, werden große Multiplizierer immer häufiger auch als eingebettete Strukturen im FPGA realisiert, wie etwa der 18×18 bit-Multiplizierer im XILINX Virtex II Pro (Xilinx, 2004). Durch die Verlagerung der komplizierten Multiplikation in einen optimierten Baustein steht ein Großteil der konfigurierbaren Logikblöcke wieder für andere Aufgaben zur Verfügung (Haynes et al., 1999). Bei eingebetteten Multiplizierer-Strukturen ist jedoch die Wahl der Wortbreite kritisch. Wenn diese zu hoch gewählt wird und der zu implementierende Algorithmus unter Umständen nur einen Bruchteil davon ausnutzt, sinkt die Effizienz. Andererseits darf sie auch nicht zu gering gewählt werden, um nicht von vornherein z. B. eine spätere Erhöhung der Genauigkeit unmöglich zu machen. Aus diesen Gründen erscheint es sinnvoll, die Wortbreite für die Multiplikation bewußt flexibel zu wählen, auch um wahlweise asymmetrische und symmetrische Strukturen realisieren zu können. 2 2.1 Konzept für Zusammenschaltung Grundlegende Struktur und Eigenschaften Die hier vorzustellende grundlegende Idee zur Realisierung der flexiblen Wortbreite bei der Multiplikation beruht darauf, einen übergeordneten Multiplizierer aus mehreren separaten Elementen zusammenzusetzen, die wiederum auch selbst individuelle und voll funktionsfähige Multiplizierer sind. Aus m1 ×m2 solchen Elementen mit jeweils n1 ×n2 bit Wortbreite kann somit eine Gesamtstruktur von (m1 ×n1 )×(m2 ×n2 ) bit entstehen; siehe Abb. 1. Die wesentlichen Anforderungen an ein solches Multiplizierer-Element sind Gleichförmigkeit, Skalierbarkeit und die Ausstattung mit geeigneten Schnittstellen. Aufgrund seiner besonders regulären Struktur weist ein iterativer Multiplizierer im Parallel-Parallel-Aufbau mit Carry-Ripple-Technik nach Hwang (1979) von Anfang an 0 320 O. A. Pfänder and H.-J. Pfleiderer: Dynamische Rekonfiguration von arithmetischen Einheiten auf Bitebene C_OUT(0) ) ) IN 0 (0 ) IN 0 (0 ) 0 (1 _S _A S_ IN (2 ) A (2 ) _V CT RL 0 A S_ (1 A S_ PSL_IN(0) CT RL Basiszelle CT RL _H A (2 B( ) 2) 0 n1 0 n2 C_OUT(1) 0 PSL_IN(1) B(0) C_IN(0) C_OUT(0) 0 m2 PSL_IN(0) B(1) C_IN(1) C_OUT(1) 0 PSL_IN(1) C_OUT(2) B(2) 0 0 C_IN(2) C_OUT(2) m1 0 PSL_IN(2) PSL_IN(2) CTRL_S_A CTRL_S_A CTRL_S_B CTRL_S_B CTRL_S_B von n1 ×n2 Abbildung 1. Eine m1 ×m2 Zusammenschaltung dung 1: Eine m1 × m2 Zusammenschaltung von n1 × n2 Basiszellen Basiszellen. M(5) M(4) M(2) M(3) M(1) M(0) V H Abbildung 3: M(4) Konfigurierbarer Multiplizierer für “Signed-Magnitude” Zahlen M(2) M(1) M(5) M(3) Abbildung 3. Konfigurierbarer Multiplizierer für “Signed1 2 2 3 Magnitude” Zahlen. 4 5 5 6 4 5 5 6 7 8 8 9 M(0) ) (0 ) N (0 A 0 S_ I N (1 ) A (1 ) 0 S_ I IN (2 ) A (2 ) 0 S_ RL _ CT CT RL _ Abbildungsolch 3: Konfigurierbarer Multiplizierer für “Signed-Magnitude” Z zur zahlreichen und parallelen Implementierung aufwendiger Rebieten, werden große Multiplizierer immer häufiger auch als eingebettete 1 2 2 3 4: Neun verschiedene m FPGA realisiert, wie etwa der 18×18 bit-Multiplizierer Abbildung im XILINX Vir-Positionen in einer zusammengeschalteten Matrix 4 5 6 Xilinx, 2004). Durch die Verlagerung der komplizierten Multiplikation in 5 zellen hinzuzufügen, vgl. Abb. 5. In einer Zusammenschaltung mehrerer Elemente zu einem übergeordneten Multiplizierer werden allerdings diese zusätzlichen Basiszellen erten Baustein steht ein Großteil der konfigurierbaren Logikblöcke wieder ausschließlich in den Randpositionen 1, 4 und 7 benötigt und liegen in allen anderen 4 6 gezeigt, 5 werden aus5 diesem 6Grund zudem zwei MultiPositionen brach. Wie in Abb. ufgaben zur Verfügung. (Haynes et al., 1999) plexer eingeführt und die Verdrahtung der Extrazellen verändert, um im Endeffekt die Wortbreite des Multiplikanden A um ist ein rekonfigu7 kri8 1 bit zu erhöhen. 8 Das Resultat 9 ebetteten Multiplizierer-Strukturen ist jedoch die Wahl der Wortbreite rierbares [(n + 1) × n ] Multiplizierer-Element mit dynamisch schaltbarer Vorzeichenerweiterung. diese zu hoch gewählt wirdMultiplizierer und der zu implementierende Algorithmus Die Aufdoppelung des Vorzeichens kann aber durch geeignete mathematische UmAbbildung 2: Konfigurierbarer für vorzeichenlose Zahlen formungen bei4. derNeun Durchführung der Multiplikation vermieden werden. In der K2Abbildung verschiedene Positionen in einer zusammengeAbbildung 2. Konfigurierbarer Multiplizierer für vorzeichenlose Abbildung 4: Effizienz. Neun Zahldarstellung verschiedene Positionen in einer zusammengeschaltete nden nur Zahlen. einen Bruchteil davon ausnutzt, sinkt die Andererseits wird dazu gemäß (Baugh and Wooley, 1973) und (Bermak et al., 1997) schalteten Matrix. ähnlicher Weise wird der Carry-Ausgangspfad auf der linken Seite der Matrix aufgeder Wert des Produktes M zweier Zahlen A and B wie folgt ausgedrückt: Eine doppelte Kette von Multiplexern sorgt um entweder für die Rückführung der nicht zu trennt: gering gewählt werden, nicht von vornherein z. B. eine späSignale in die jeweils darunterliegende Basiszelle oder für die Weiterleitung an ein benachbartes Multiplizierer-Element. Diese Multiplexer werden von zweiAus separatendiesen Konng der Genauigkeit unmöglich zu machen. Gründen M erscheint = 5. a Inb (siehe 2 + ∑ Abb. 2 und + T +können T ∑ a b 4) zellen hinzuzufügen, vgl. Abb. einer Zusammenschaltung E Zusammenschaltung auch z.(1)mehrerer B. die beiden zuerstmitgenannten Eigenschaften und wird trollsignalen angesteuert, Hilfe derer sowohl die horizontale als auf auch die vertikale à ! Schnittstelle des Elements rekonfiguriert werden können. Die Werte der Kontrollsignadie Wortbreite für die Multiplikation bewußt flexibel zu wählen, auch um von einem Konfigurationsspeicher geliefert werden. deswegen im folgenden genauer betrachtet. Die gefordereinem übergeordneten Multiplizierer werden+ 1allerdings diese zusätzlichen B le sind abhängig von der Position des Elements in der Zusammenschaltung (siehe auch T = 2 −2 + 2 + ∑ a b 2 (2) teAbb. Zusammenschaltbarkeit kann mit nur wenig zusätzlichem 4) und könnensymmetrische z. B. von einem Konfigurationsspeicher geliefert werden. symmetrische und Strukturen realisieren zu können. ausschließlich in den2.2Randpositionen 1, Zahlen 4 und 7 benötigt und liegen in all Vorzeichenbehaftete Schaltungsaufwand erreicht werden, auch sind alle weiteren 2.2 Vorzeichenbehaftete Zahlen Positionen brach. Maßnahmen zum Umgang mit vorzeichenbehafteten Zahlen Wie in Abb. 6 gezeigt, werden aus diesem Grund zudem z Das im vorigen Abschnitt beschriebene Multiplizierer-Element ist in seiner grundleDas vorigen Abschnitt beschriebene verändert, Multiplizierer-um im En stets Erweiterungen der grundlegenden Struktur mit einem und plexerZahlen eingeführt dieimVerdrahtung der 4Extrazellen genden Form in der Lage, die Multiplikation mit vorzeichenlosen durchzufühElement ist in seiner grundlegenden Form in der Lage, die unveränderten Kern. ren. EsZusammenschaltung soll nun mit möglichst wenig Schaltungsaufwand so erweitert werden, daß es zept für Wortbreite des Multiplikanden Amitum 1 bit zu erhöhen. Das Resultat ist ein wahlweise auch mit vorzeichenbehafteten Zahlen umgehen kann. Multiplikation vorzeichenlosen Zahlen durchzuführen. Alle arithmetischen Basiszellen des hier eingesetzten Eine naheliegende Herangehensweise beruht auf der Wahl der “Signed-Magnitude”rierbares n2soll ] Multiplizierer-Element mit dynamisch nun mit möglichst wenig Schaltungsaufwand so schaltbarer er1 + 1) ×Es Parallel-Parallel-Multiplizierers beinhalten jebeinhaltet einen[(n VolladZahldarstellung nach Vorzeichen und Betrag. In dieser Darstellung das höchstwertige Bit einer n bit breiten Zahl das Vorzeichen und die übrigen n − 1 bit ihren Bendlegende Struktur und Eigenschaften weitert werden, daß es wahlweise auch mit vorzeichenbehafdierer und ein UND-Gatter zur Berechnung des entsprechennerweiterung. trag. Damit kann das Schema der Berechnung auf die vorzeichenlose Multiplikation teten Zahlen umgehen kann. den auch die Basiszellen in Aufdoppelung der zurückoberen zweierPartialprodukts. n − 1 bit breiter Zahlen Da mit getrennter Verarbeitung des Vorzeichenbits Die des Vorzeichens kann aber durch geeignete mathema geführt werden. Das Resultat ist negativ, wenn Multiplikand A und Multiplikator B Reihe und der rechten Spalte identisch aufgebaut sind, exiEine naheliegende Herangehensweise beruht auf der Wahl zustellende grundlegende Idee zur Realisierung der flexiblen Wortbreite verschiedene Vorzeichen haben. Die Vorzeichenbehandlung benötigt also eine XORformungen bei der Durchführung der Multiplikationnach vermieden stieren hier bereits zwei der geforderten Schnittstellen, die der “Signed-Magnitude”-Zahldarstellung Vorzeichenwerden. I der beiden höchstwertigen Eingangsbits und kann entweder mit separater tiplikationVerknüpfung beruht darauf, einen übergeordneten Multiplizierer aus mehLogik außerhalb des Multiplizierer-Elements erfolgen oder auch mit Gattern, die ins der Einspeisung eines n bit breiten Partialsummensignals in und Betrag. In dieser Darstellung beinhaltet das Zahldarstellung wird dazu gemäß (Baugh and Wooley, 1973) höchstund (Bermak e 1 Element integriert sind und zwei zusätzlichen Kontrollsignalen, wie es in Abb. 3 verten Elementen zusammenzusetzen, die Wert wiederum auchwertige selbst individudie obere Reihe sowie n zusätzlicher Carry-Bits von außerBit einer n bit breiten Zahl das Vorzeichen und die anschaulicht wird. 2 der des Produktes M zweier Zahlen A and B wie folgt ausgedrückt: Wesentlich praxisrelevanter ist jedoch die Wahl der sogenannten K2-Zahldarstellung halb dienen. Wie in Abb. 2 ersichtlich wird, können Sumübrigen n−1 bit ihren Betrag. Damit kann das Schema der l funktionsfähige Multiplizierer sind. Aus mdie m2 solchen Elementen 1der× im Zweierkomplement, vor allem aufgrund der eindeutigen Repräsentierung Null meneingänge mit Hilfe von 1 bit-Multiplexern abgeschaltet Berechnung auf vorzeichenlose Multiplikation zweier (Bermak et al., 1997). Um allerdings der geforderten Vorzeichenerweiterung bei der n1 × n2 bit kann eine Gesamtstruktur vonbit(m ndie 1 ×Zahlen 1 ) ×mit getrennter Verarbeitung des VorWahlWortbreite einer Parallel-Parallel-Struktur mitsomit gleichförmigen Basiszellen gerecht zu werwerden. In ähnlicher Weise wird der Carry-Ausgangspfad n−1 breiter den (Parhami, 2000), ist dem Multiplizierer-Element eine zusätzliche Spalte an Basisn −2 n2 −2 t entstehen; siehe 1. Matrix Die wesentlichen anzurückgeführt ein solauf der linkenAbb. Seite der aufgetrennt: Eine Anforderungen doppelte zeichenbits werden.1Das Resultat ist i+ negativ, n1 +n2 −2 j M = a b 2 + a b 2 + T1 + T2 v n −1 n −1 i j ∑ ∑ Kette von Multiplexern sorgt entweder für die Rückführung wenn Multiplikand A und Multiplikator B verschiedene 2 3 izierer-Element sind Gleichförmigkeit, Skalierbarkeit und die1Ausstattung i=0 j=0 benötigt also der Signale in die jeweils darunterliegende Basiszelle oder Vorzeichen haben. Die Vorzeichenbehandlung à en Schnittstellen. Aufgrund besonders regulären Struktur weist ein der beiden höchstwertigen Ein-! für die Weiterleitung an seiner ein benachbartes Multiplizierereine XOR-Verknüpfung n2 −2 gangsbits mit separater Logik außerhalbj Element. Multiplexer werden von zwei mit separaten Konn1 −1und kann n2entweder n2 −1 ultiplizierer im Diese Parallel-Parallel-Aufbau Carry-Ripple-Technik nach T1 =des Multiplizierer-Elements 2 −2 + 2 erfolgen +1+ a 1 −1Gattern, bj 2 trollsignalen angesteuert, mit Hilfe derer sowohl die hooder∑ auch nmit 79) von Anfang an die beiden zuerst genannten Eigenschaften auf und j=0 rizontale als auch die vertikale Schnittstelle des Elements die ins Element integriert sind und zwei zusätzlichen Konen im folgenden genauer betrachtet. Die der geforderte trollsignalen, wie es in Abb. 3 veranschaulicht wird. rekonfiguriert werden können. Die Werte Kontrollsi- Zusammenschaltbargnale sind abhängig von der Position des Elements in der t nur wenig zusätzlichem Schaltungsaufwand erreicht werden, auch sind Maßnahmen zum Umgang mit vorzeichenbehafteten Zahlen stets Erwei4 grundlegenden Struktur mit einem unveränderten Kern. B(0) C_IN(0) C_OUT(0) 0 PSL_IN(0) B(1) C_IN(1) C_OUT(1) 0 PSL_IN(1) B(2) C_IN(2) C_OUT(2) 0 PSL_IN(2) M(5) M(4) M(3) M(2) M(1) M(0) 1 2 v n1 −1 n2 −1 n1 +n2 −2 n1 −2 n2 −2 i j i+ j 1 i=0 j=0 1 n1 −1 n2 n2 −1 n2 −2 n1 −1 j j=0 j 2 ) ) IN (0 ) ) IN (0 A 0 S_ ) IN (1 A S_ 0 (0 ) (1 ) (2 ) IN (2 A 0 S_ RL CT RL _I _V _1 _1 RL CT RL _C _H ) IN (0 A ) CT CT S_ S_ )A 0 (0 0 (1 IN 321 (0 ) (1 ) IN (1 S_ ) A (1 S_ ) IN 0 (2 A IN 0 A IN (2 S_ ) A S_ (2 0 ) (2 ) ig n) S_ ig n) 0 (s 0 S_ IN (s RL _V CT _V 0 RL CT CT RL _H CT RL _H O. A. Pfänder and H.-J. Pfleiderer: Dynamische Rekonfiguration von arithmetischen Einheiten auf Bitebene B(0) C_OUT(0) C_IN(0) B(0) 0 C_OUT(0) PSL_IN(0) C_IN(0) 0 PSL_IN(0) C_IN(1) B(1) 0 C_IN(1) 0 B(2) PSL_IN(1) C_OUT(2) 0 C_OUT(2) PSL_IN(2) 0 B(1) PSL_IN(0) C_OUT(1) C_OUT(1) PSL_IN(1) B(0) C_IN(0) C_OUT(0) 0 PSL_IN(2) S_OUT(sign) M(5) S_OUT(sign) M(5) M(4) M(3) M(4) M(2) M(3) M(1) M(2) M(1) 0 PSL_IN(1) C_IN(2) B(2) CTRL_C C_IN(2) CTRL_C CTRL_I C_OUT(2) CTRL_I CTRL_C_2 M(0) B(1) C_IN(1) C_OUT(1) B(2) C_IN(2) CTRL_I_2 0 PSL_IN(2) M(5) M(0) M(4) M(3) M(2) M(1) M(0) Abbildung 5: K2-Multiplizierer mit regulärer Vorzeichenerweiterung Abbildung 7: Modifizierter Baugh-Wooley K2-Multiplizierer mit schaltbaren Sonder- Abbildung 5: K2-Multiplizierer mit regulärer Vorzeichenerweiterung Abbildung 5. K2-Multiplizierer mit regulärer Vorzeichenerweiterung. zellen Abbildung 7. Modifizierter Baugh-Wooley K2-Multiplizierer mit schaltbaren Sonderzellen. à ! T2 = 2n2 −1 −2n1 + 2n1 −1 + 1 + n1 −2 ∑ ai bn2 −1 2i . (3) ) ) N (0 S_ I ) (0 A ) IN (0 S_ )A ) 0 (0 ) (1 S_ IN (1 0 (1 A ) (2 A )A 0 S_ IN ) (1 ) (2 0 (2 S_ IN S_ IN )A 0 (2 0 ig (s A 0 S_ IN (s S_ IN ( igA sign n)(s ig ) n) n) _V RL CT _V 0 RL CT CT CT RL _H RL _H i=0 B(0) C_OUT(0) C_IN(0) B(0) 0 C_OUT(0) PSL_IN(0) C_IN(0) 0 B(1) PSL_IN(0) C_OUT(1) C_OUT(1) PSL_IN(1) C_IN(1) B(1) 0 C_IN(1) 0 B(2) PSL_IN(1) C_OUT(2) C_IN(2) B(2) CTRL_C C_IN(2) 0 C_OUT(2) PSL_IN(2) PSL_IN(2) 0 CTRL_C CTRL_I S_OUT(sign) M(5) M(4) M(3) M(2) M(1) M(0) S_OUT(sign) M(5) M(4) M(3) M(2) M(1) M(0) CTRL_I Abbildung 6: K2-Multiplizierer mit schaltbarer Vorzeichenerweiterung Abbildung 6. 6:K2-Multiplizierer mit schaltbarer VorzeichenerweiAbbildung K2-Multiplizierer mit schaltbarer Vorzeichenerweiterung terung. 5 5 Wesentlich praxisrelevanter ist jedoch die Wahl der sogenannten K2-Zahldarstellung im Zweierkomplement, vor allem aufgrund der eindeutigen Repräsentierung der Null (Bermak et al., 1997). Um allerdings der geforderten Vorzeichenerweiterung bei der Wahl einer Parallel-ParallelStruktur mit gleichförmigen Basiszellen gerecht zu werden (Parhami, 2000), ist dem Multiplizierer-Element eine zusätzliche Spalte an Basiszellen hinzuzufügen, vgl. Abb. 5. In einer Zusammenschaltung mehrerer Elemente zu einem übergeordneten Multiplizierer werden allerdings diese zusätzlichen Basiszellen ausschließlich in den Randpositionen 1, 4 und 7 benötigt und liegen in allen anderen Positionen brach. Wie in Abb. 6 gezeigt, werden aus diesem Grund zudem zwei Multiplexer eingeführt und die Verdrahtung der Extrazellen verändert, um im Endeffekt die Wortbreite des Multiplikanden A um 1 bit zu erhöhen. Das Resultat ist ein rekonfigurierbares [(n1 +1)×n2 ] Multiplizierer-Element mit dynamisch schaltbarer Vorzeichenerweiterung. Die Aufdoppelung des Vorzeichens kann aber durch geeignete mathematische Umformungen bei der Durchführung der Multiplikation vermieden werden. In der K2Zahldarstellung wird dazu gemäß Baugh and Wooley (1973) und Bermak et al. (1997) der Wert des Produktes M zweier Zahlen A and B wie folgt ausgedrückt: Diese Zerlegung des ursprünglichen Terms findet sich in einer modifizierten Multipliziererstruktur nach (Baugh and Wooley, 1973) wieder, die grafisch in Abb. 7 dargestellt ist. Die Basiszellen in der linken Spalte sowie der unteren Zeile der Matrix nX nX besitzen einen zusätzlichen internen Inverter. Dieser ist durch ein Kontrollsignal steu1 −2 2 −2 n1 +nMultiplexer erbar=a und gleicht damit 2 einem Eingang, was der 2 −2 + mit einem invertierenden M b ai bj 2i+j +T v n −1 n −1 1 +T2 (1) 1 2 Funktion eines XOR-Gatters entspricht. In Abb. 7 wird dies aus Gründen der Überi=0 j =0 sichtlichkeit durch ein schwarzes Quadrat in der Zelle angedeutet. Ist das entsprechende Kontrollsignal CTRL_I auf ‘1’ gesetzt, wirdn das Partialprodukt in ! der Basiszelle 2 −2 X negiert,num−1 der Rechenvorschrift in−1 (2) bzw. (3) zu genügen. Die linkejuntere Basiszeln n 2 Tle1benötigt =2 1 diese Negation −2 2 + 2 + 1+ a b 2 (2) jedoch nur, wenn sich das Multiplizierer-Element in Position n1 −1 j 7 der Zusammenschaltung befindet. Dort muß das Partialprodukt regulär und ohne Inj =0 vertierung berechnet werden, deshalb kombiniert ein weiteres XOR-Gatter ! die beiden nX Signale CTRL_I_1 und CTRL_I_2. Um das korrekte 1 −2 Ergebnis bei der Multiplikatin −1 n n −1 i zu erhalten, muß and1+ Cash, 1986)aund (Bermak 2 1 +(Hatamian Ton2 =2 −2gemäß 2 1 + 2 et al.,. 1997) ein (3) i bn2 −1 Korrekturterm addiert werden, der den beiden +1 Anteilen in (2) und (3) entspricht, i=0 da eine K2-Zahl durch Umkehren aller Bits und Addieren einer 1 negiert wird. Bei einer Ergebniswortbreite von n1 + n2 hat dieser Korrekturterm X eine ‘1’ an den Stellen x(n1 + n2 − 1), x(n1 − 1) und x(n2 − 1). In der quadratischen Struktur in Abb. 7, die Diese Zerlegung des ursprünglichen Terms findet sich in den Sonderfall n1 = n2 = n zeigt, wurde dies auf zwei gesetzte Bits an den Positionen einer modifizierten Multipliziererstruktur nach Baugh and x(2n − 1) und x(n) zurückgeführt. (Pfänder et al., 2004) Wooley (1973) wieder, die grafisch in Abb. 7 dargestellt 2.3 Die Aufwandsvergleich ist. Basiszellen in der linken Spalte sowie der unteDer prozentuale Mehraufwand verschiedenen konfigurierbaren Multiplizierer-Eleren Zeile der Matrix derbesitzen einen zusätzlichen internen mente in Relation zur starren Grundstruktur ohne Schnittstellen wird anhand der Zahl Inverter. Dieser ist abgeschätzt durch ein Kontrollsignal und der benötigten Transistoren (Pfänder et al., 2004). Einesteuerbar grafische Gegenüberstellung ist in Abb. 8 gegeben. gleicht damit einem Multiplexer mit einem invertierenden Eingang, was der Funktion eines XOR-Gatters entspricht. In 6 Abb. 7 wird dies aus Gründen der Übersichtlichkeit durch ein schwarzes Quadrat in der Zelle angedeutet. Ist das entsprechende Kontrollsignal CTRL I auf ‘1’ gesetzt, wird das Partialprodukt in der Basiszelle negiert, um der Rechenvorschrift in Gl. (2) bzw. Gl. (3) zu genügen. Die linke untere Basiszelle benötigt diese Negation jedoch nur, wenn sich das Multiplizierer-Element in Position 7 der Zusammenschaltung befindet. Dort muß das Partialprodukt regulär und ohne Invertierung berechnet werden, deshalb kombiniert ein weiteres XOR-Gatter die beiden Signale CTRL I 1 und CTRL I 2. Um das korrekte Ergebnis bei der Multiplikation zu erhalten, muß gemäß Hatamian and Cash (1986) und Bermak et al. (1997) ein Korrekturterm addiert werden, der den beiden +1 Anteilen in (2) und (3) entspricht, da eine K2-Zahl durch Umkehren aller Bits und Addieren einer 1 negiert wird. Bei einer Ergebniswortbreite von n1 +n2 hat dieser Korrekturterm X eine ‘1’ an den Stellen x(n1 +n2 −1), x(n1 −1) und x(n2 −1). In der quadratischen Struktur in Abb. 7, die den Sonderfall n1 =n2 =n zeigt, wurde dies auf zwei gesetzte Bits an den Positionen x(2n−1) und x(n) zurückgeführt (Pfänder et al., 2004). 322 30 O. A. Pfänder and H.-J. Pfleiderer: Dynamische Rekonfiguration von arithmetischen Einheiten auf Bitebene % unsigned SM, ext. XOR SM, int. XOR 25 20 15 vgl. Abb. 8 (unten). Während aber bei größer werdendem n die Unterschiede zwischen regulärer und konfigurierbarer Vorzeichenerweiterung nahezu verschwinden, hat die alternative Baugh-Wooley-Variante stets einen deutlich erkennbaren Vorsprung und könnte z.B. bei n=8 mit fast 10% weniger Transistoren und damit flächensparender realisiert werden als mit der konfigurierbaren Vorzeichenerweiterung. 10 5 3 0 Zusammenfassung und Ausblick In diesem Beitrag wurde ein Konzept für den Aufbau einer zur Laufzeit rekonfigurierbaren Multiplizierer-Matrix vorgestellt, dessen Elemente jeweils erweiterte und mit Kontrollsi% gnalen dynamisch steuerbare Parallel-Parallel-Multiplizierer 70 sind. Diese Elemente sind selbst separate und voll funkK2, reg. VZE 60 tionsfähige Multiplizierer und weisen Schnittstellen auf, K2, konf. VZE 50 die mit Hilfe von Multiplexern realisiert wurden. MehK2, mod. B.-W. rere Varianten für vorzeichenlose und vorzeichenbehafte40 te Zahlen wurden diskutiert. Wenn als Zahldarstellung das 30 Zweierkomplement zum Einsatz kommt, bietet sich für 20 die Multiplizierer-Elemente die modifizierte Struktur nach 10 Baugh-Wooley an, die im Vergleich zur herkömmlichen Vorzeichenerweiterung um bis zu 12% weniger Transistoren 0 benötigt und damit eine höhere Flächeneffizienz bietet. 4 6 8 10 12 14 16 Ein mögliches Einsatzgebiet solcher zusammenschaltban [bit] rer Multiplizierer ist, wie eingangs erwähnt, das Einbetten in Form von fest geschalteten Blöcken innerhalb von Abbildung 8. Mehraufwand für Konfigurierbarkeit – prozentualer FPGA-Strukturen, um deren Logikressourcen bei der Imple8: Mehraufwand Konfigurierbarkeit – prozentualer Vergleich nach Vergleich nach für Pfänder et al. (2004). mentierung von Multiplikationen zu entlasten. Die Elemente al., 2004) können dann sowohl im separaten Betrieb als auch als dynamisch verbundener übergeordneter Multiplizierer für vie2.3 Aufwandsvergleich le iterative Algorithmen mit variabler Genauigkeit nützlich sein. n der zu Der implementierenden Anwendung die Multiplikationen häufig mit prozentuale Mehraufwand der verschiedenen konfiguGegenstand von aktuellen und zukünftigen Überlegunrierbaren Multiplizierer-Elemente in Relation zur starren osen Zahlen erfolgen und nur selten der Fall einer vorzeichenbehafteten Be- von verschiedenen Vorgehensgen ist die Gegenüberstellung Grundstruktur ohne Schnittstellen wird anhand der Zahl der weisen bei der Verdrahtung. Eine Möglichkeit ist die Nutuftritt, erscheint Verwendung benötigten die Transistoren abgeschätzteines PfänderSigned-Magnitude-Multiplizierers et al. (2004). Eizung von FPGA-typischen Routing-Ressourcen, wobei das ne grafische Gegenüberstellung ist in Abb. 8 gegeben. Hierbei steht zur Auswahl, die Vorzeichenbehandlung mit einem externen Multiplizierer-Element durch Hinzunahme z.B. von SchaltWenn in der zu implementierenden Anwendung die Multir oder durch dessen Integration ins Multiplizierer-Element zu realisieren. matrizen zur Anbindung an die Infrastruktur bereits als plikationen häufig mit vorzeichenlosen Zahlen erfolgen und spezialisiertes FPGA-Tile n Basiswortbreiten bis 8 bit ist der Berechnung prozentuale Mehraufwand je- betrachtet werden kann. Bei der nur selten der n Fallvon einer4vorzeichenbehafteten Plazierung der Elemente soll die geforderte Lokalität des auftritt,mit erscheint die internen VerwendungXOR eines Signed-Magnituderoß und kann einem sogar über 25% betragen. größerberücksichtigt werden, da ansonsten Carry-PfadesJe unbedingt Multiplizierers vorteilhaft. Hierbei steht zur Auswahl, die auftreten können. ortbreite wird, desto geringer wird der Einfluß der GatterTiming-Probleme und Multiplexer, Vorzeichenbehandlung mit einem externen XOR-Gatter oder Konfigurierbarkeit und Zusammenschaltbarkeit benötigt werden, auf die durch dessen Integration ins Multiplizierer-Element zu realisieren. Bei geringen Basiswortbreiten n von 4 bis 8 bit ist Literatur der Transistoren; z. B. nur noch knapp 5% bei n =der16, vgl. Abb. 8 (oben). prozentuale Mehraufwand jedoch sehr groß und kann mit eiZahldarstellung im XOR Zweierkomplement spiegeln sich mathematisch be- B. A.: A Two’s Complement Parallel C. R. und Wooley, nem internen sogar über 25% betragen. Je größer die dieBaugh, Array Multiplication Algorithm, IEEE Trans. Computers, C-22, Basiswortbreite wird,bzw. desto die geringer wird der Einfluß der zliche Basiszellenspalte modifizierten Basiszellen in der alternati1045–1047, 1973. Gatter und Multiplexer, die für die Konfigurierbarkeit und e noch deutlicher im prozentualen Mehraufwand wider, vgl. Abb. 8 (unten). Bermak, A., Martinez, D., und Noullet, J.-L.: High-Density 16/8/4Zusammenschaltbarkeit benötigt werden, auf die Gesamtzahl bit Configurable Multiplier, ber bei größer werdendem n die zwischen regulärer und kon- IEE Proc. Circuits Devices Systems, der Transistoren; z.B. nur nochUnterschiede knapp 5% bei n=16, vgl. 144, 272–276, 1997. Abb. 8 (oben). r Vorzeichenerweiterung nahezu verschwinden, hat die alternative Bondalapati, K. Baughund Prasanna, V. K.: Reconfigurable Computing Bei der Zahldarstellung im Zweierkomplement spiegeln Systems, Proc. iante stetssicheinen deutlich erkennbaren Vorsprung und könnte z. B. beiofnthe=IEEE, 8 90, 1201–1217, 2002. die mathematisch bedingte zusätzliche BasiszellenspalHatamian, M. und Cash, G. L.: A 70-MHz 7-bit×8-bit Parallel Pipe% wenigerteTransistoren und Basiszellen damit flächensparender realisiert werden mit CMOS, IEEE J. Solid-State Circuits, bzw. die modifizierten in der alternativen Varilined Multiplierals in 2.5-µm SC-21, 505–513, 1986. ante noch deutlicher im prozentualen Mehraufwand wider, rierbaren Vorzeichenerweiterung. 4 6 8 10 n [bit] 12 14 16 O. A. Pfänder and H.-J. Pfleiderer: Dynamische Rekonfiguration von arithmetischen Einheiten auf Bitebene Haynes, S. D., Ferrari, A. B., und Cheung, P. Y. K.: Flexible Reconfigurable Multiplier Blocks suitable for enhancing the Architecture of FPGAs, Proceedings of the IEEE 1999 Custom Integrated Circuits Conference, San Diego, CA, 191–194, 1999. Hwang, K.: Computer Arithmetic – Principles, Architecture, and Design, John Wiley & Sons, New York, 1979. Oklobdzija, V. G.: Design of High-Performance Microprocessor Circuits, chap. 10 – High-Speed VLSI Arithmetic Units: Adders and Multipliers, John Wiley & Sons/IEEE Press, New York, 2000. 323 Parhami, B.: Computer Arithmetic: Algorithms and Hardware Designs, Oxford University Press, New York, 2000. Pfänder, O. A., Hacker, R., und Pfleiderer, H.-J.: A Multiplexerbased Concept for Reconfigurable Multiplier Arrays, Proceedings of the FPL 2004, Antwerp, Belgium, 938–942, 2004. Xilinx: Virtex™-II Platform FPGAs and Product Specification, Xilinx Document DS031 (v3.3), 2004.