Centrino

Werbung

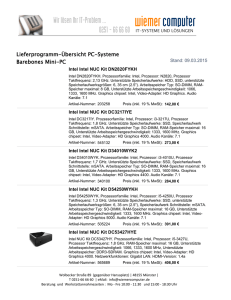

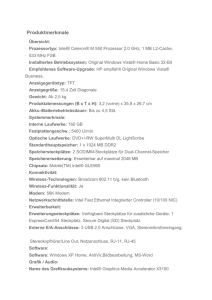

Zusammenfassung Thema: Centrino (Mobile Prozessor) Erstellt von: Boris Manyshev Datum: 05.03.2005 Inhaltsverzeichnis MicroOps Fusion 2 Dedicated Stack Engine 4 Enhanced SpeedStep 5 Quellen 6 1 MicroOps Fusion Intel vereinfacht beim Pentium-M die komplizierte Verwaltung der MicroOps in den Schedulern durch die MicroOps1-Fusion. Die neue MicroOps-Fusion-Technologie analysiert die Instruktionen des Programmablaufs. Wenn sich mehrere Operationen zusammenfassen lassen, werden sie zu einem Befehl verschmolzen. Erst für die Bearbeitung in den parallelen Ausführungseinheiten werden die gebündelten Befehle wieder in die einzelnen MicroOps aufgetrennt. Die Effizienz der Befehlsabarbeitung erhöht sich durch dieses Verfahren, weil der Scheduler weniger Einträge verwalten muss. Diese "Befehlsreduzierung" vor den Ausführungseinheiten steigert aber nicht nur die Performance, sondern reduziert gleichzeitig den Energiebedarf der Scheduler-Einheit. Durch die MicroOps-Fusion-Technologie muss der Pentium-M zehn Prozent weniger MicroOps in den Ausführungseinheiten berechnen. Diese PerformanceAngabe basiert auf Simulationen, die Intel während des Architektur-Designs durchgeführt hat. Um die Zahl der MicroOps weiter zu verringern, hat Intel der Pentium-M-Architektur einen dedizierten Ablaufmanager spendiert. Programm-Overhead wie die Stack-Befehle push, pop, call und ret führt der Pentium-M in einer dedizierten Hardware durch. Der Prozessor kann das eigentliche Programm in den Ausführungseinheiten damit ohne Unterbrechung abarbeiten. Die Zahl der MicroOps verringert sich durch den Stack Manager laut Intel um fünf Prozent, was für eine Performance-Steigerung sorgen soll. Bild1: Beispiel für MicrOps Fusion 2 Bild2: Beispiel für MicrOps Fusion 1. Micro-Op - Moderne PC-Prozessoren zerlegen die komplexen x86-Befehle in einfach zu handhabende Kommandos fester Länge. Intel nennt diese Risc-ähnlichen Befehle Micro-Ops, bei AMD heißen sie MacroOps. Schließen 3 Stack-Management-Einheit (Dedicated Stack Engine) Diese Anweisungsblöcke fasst der Prozessor zu einer Operation zusammen und spart sich somit das zeitaufwendige Handling mehrerer Instruktionen. Nach demselben Prinzip arbeitet eine Hardwareeinheit für Stack-Management. Der Stack ist ein Speicherbereich, in dem eine Funktion einer Anwendung zeitweise Daten, beispielsweise die Rücksprungadresse zur aufrufenden Funktion, ablegen kann. Da der Zugriff auf den Stack immer ähnlich abläuft, kann die CPU solche Anweisungen erkennen und der optimierten Stack-Management-Einheit zuführen. Ebenfalls der Performance zuträglich ist der 1 MByte große L2-Cache. In ihn lädt der Prozessor Daten zur weiteren Verwendung aus dem Arbeitsspeicher. Eine Zugriffsvorhersage lädt diejenigen Daten bereits im Voraus, die in den nächsten Taktzyklen am wahrscheinlichsten benötigt werden (Pre-Fetching). Dasselbe gilt für die Sprungvorhersage, die die wahrscheinlichsten Verzweigungen im Programmablauf erkennt (Branch-Prediction). Diese Techniken kommen zwar bereits seit etlichen CPU-Generationen zum Einsatz, im Pentium-M sollen sie jedoch um etwa 20 Prozent genauer als alle bisherigen Implementationen arbeiten. Bild3: Beispiel für Dedicated Stack Engine 4 Enhanced SpeedStep Intel führt mit dem Pentium-M die dritte Version der Stromspartechnologie SpeedStep ein. Die ersten beiden SpeedStep-Varianten kennen nur zwei Prozessorzustände, zwischen denen sie die Taktfrequenz und Core-Spannung wechseln können. SpeedStep II (offiziell Enhanced SpeedStep) des Pentium III-M und Pentium 4-M kann die miteinander gekoppelte Taktfrequenz und Core-Spannung auch dynamisch an die Prozessorauslastung anpassen. Bild 4: Der Pentium-M kann Taktfrequenz und Core-Spannung in mehreren Stufen variieren. Beim Pentium-M kann das neue SpeedStep III (Codename) die Taktfrequenz und Spannung nun in mehreren Schritten variieren. Transmetas LongRun-Technologie und AMDs PowerNow! verwenden dieses Verfahren schon lange. Intel hat beim Pentium-M Abstufungen von 200 MHz gewählt. Die minimale Taktfrequenz der Pentium-M-Prozessoren beträgt jeweils 600 MHz. Ein Pentium-M mit 1,8 GHz Taktfrequenz kann somit dynamisch mit 600, 800, 1000, 1200, 1400, 1600 und 1800 MHz Taktfrequenz arbeiten. Die Core-Spannung variiert beim Dothan mit der Taktfrequenz gekoppelt zwischen 0,988 und maximal 1,34 V. Der Pentium-M mit Banias-Core benötigt bei voller Taktfrequenz eine Core-Spannung von 1,484 V. Intel hat beim Pentium-M zudem die I/O-Voltage von der Core-Spannung über die IMVPTechnik der vierten Generation komplett entkoppelt. Dies erlaubt eine gezieltere Regulierung der Spannungs-Level. IMVP packt Intelligenz in die Stromversorgung und nutzt den zulässigen Spannungsbereich eines Prozessors zur Reduktion der Leistungsaufnahme aus. 5 Quellen 1. http://www.tecchannel.de/hardware/1141/1.html 2. http://www.tecchannel.de/hardware/1141/4.html 3.http://www.vnunet.de/testticker/Mobile/article.asp?ArticleID=20030518503& Page=2&Ref=testticker 4. Intel Technology Journal, Vol. 7, Issue 2, May 2003 5. Ronny Ronen Senior Principal Engineer Director of Architecture Research Intel Labs – Haifa Intel Corporation Technion EE, Haifa 6