DSP-Einführung

Werbung

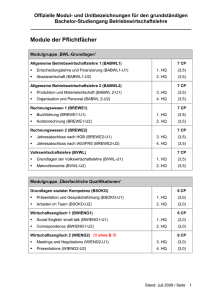

Signal-Prozessoren DSV1, 2009, Hhrt, 1 Mikro-Prozessor Digitaler Signal-Prozessor • Von Neumann-Architektur • Harvard-Architektur • Daten und Programmcode im gleichen Speicher => Sequenzieller Zugriff auf Code und Daten • Daten und Programmcode in getrennten Speichern => Paralleler Zugriff auf Code und Daten • Effizient für komplexe Operationen • Effizient für grosse Datenmengen • Multitasking-fähig mit Betriebssystem • MAC-Operation (multiply and accumulate) in einem Takt dank optimierter HW DSP-Hardware DSV1, 2009, Hhrt, 2 N M • MAC-Operation yn bk xn k ak yn k k 0 k 1 in Hardware • Unabhängige HW-Adressgeneratoren für den parallelen Zugriff auf Daten und Code • Ringbuffer-Adressierung (Delay-Lines) und bit-reversedAdressierung (FFT), sowie Schleifenzähler in HW • Dedizierter Stack-Speicher • Kein Multitasking • Dual-ported RAM und synchrone serielle Schnittstellen ermöglichen parallelen Zugriff durch CPU und Peripherie • Fixed-Point-DSP mit sättigender Arithmetik und GuardBits in HW implementiert DSV1, 2009, Hhrt, 3 TMS320VC5510 DSP CPU Diagram DSV1, 2009, Hhrt, 4 TMS320VC5510 DSP Instruction Buffer Unit I Unit DSV1, 2009, Hhrt, 5 TMS320VC5510 DSP Program Flow Unit P Unit DSV1, 2009, Hhrt, 6 TMS320VC5510 DSP Address Data Flow Unit A Unit Data Computation Unit, D Unit TMS320VC5510 DSP DSV1, 2009, Hhrt, 7 TMS320VC5510 DSP DSV1, 2009, Hhrt, 8 Feature(s) Benefit(s) A 32 x 16-bit Instruction buffer queue Buffers variable length instructions and implements efficient block repeat operations Two 17-bit x17-bit MAC units Execute dual MAC operations in a single cycle One 40-bit ALU Performs high precision arithmetic and logical operations One 40-bit Barrel Shifter Can shift a 40-bit result up to 31 bits to the left, or 32 bits to the right One 16-bit ALU Performs simpler arithmetic in parallel to main ALU Four 40-bit accumulators Hold results of computations and reduce the required memory traffic Twelve independent buses: – Three data read buses – Two data write buses – Five data address buses – One program read bus – One program address bus Provide the instructions to be processed as well as the operands for the various computational units in parallel to take advantage of the ’C55x parallelism. User-configurable IDLE Domains Improve flexibility of low-activity power management C5510 DSK (= DSP Starter Kit) DSV1, 2009, Hhrt, 9 Quelle aller Grafiken: TI-Hilfe zu C5510 DSK und TMS320VC5510 DSP C5510 Programmierung DSV1, 2009, Hhrt, 10 • TMS320C55x Technical Overview => spru393.pdf • Programmierung in C => spru281f.pdf Kapitel 5 • Programmierung in Assembler => spru281f.pdf Kapitel 6.5, spru280h.pdf, spru374g.pdf, spru375g.pdf • DSPLIB enthält handoptimierte Bibliotheken für die Signalverarbeitung => spru422i.pdf Hinweis: die iir-Funktionen der DSPLIB sind für Filterkoeffizienten |a1| > 1 unbrauchbar => iircas52.asm im Verzeichnis DSK5510_vorlage verwenden • Compiler-Intrinsics erlauben den effizienten Zugriff auf die speziellen Fähigkeiten des DSPs direkt aus einem CProgramm => spru281f.pdf Kapitel 6.5.4