Kein Folientitel

Werbung

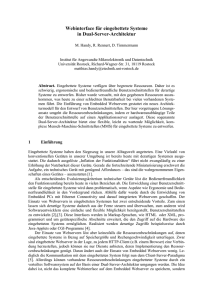

04EI C164CI Blockschaltbild C166-Core Data (C164 CI-8RM) CPU Instr./Data or OTP 32 Data 16 Dual Port 16 64 K ROM RAM 2 KByte (C164CI-8EM) Watchdog 0.5; 1; 1.5; 2; 2.5; 3; 4; 5 PEC 16 Port 0 P4.6/ CAN TxD Interrupt Controller RTC 13 ext. IR 16 Interrupt Bus Peripheral Data 16 External Bus 8/16 bit MUX only & XBUS Control Port 4 10-Bit USART Sync. GPT1 CAPCOM 2 CAPCOM6 Unit for PWM Generation Channel ADC T2 (SPI) 8-Channels 8-Channel ASC SSC T3 BRG BRG T4 Port 3 Port 5 Timer 13 Full-CAN Interface V2.0B active Timer 8 P4.5/ CAN RxD XBUS (16-bit NON MUX Data / Addresses) External Instr./Data Timer 7 XTAL PLL-Oscillator prog. Multiplier: 1 Comp. Channel Port 8 3/6 CAPCOM Channels Port 1 164 CL 6 8 Embedded Systems 9 25.9.2009 4 16 Seite 1 04EI CPU - Blockschaltbild STK UV CPU STK OV Exec. Unit MDH SP Instr. Ptr. MDL STK OV Instr. Reg. 32 4-Stage Pipeline On-Chip (EP)ROM PSW SYSCON Mul./Div.-HW 16 STK UV On-Chip Static RAM Bit-Mask Gen. ALU R15 R15 16-bit Barrel-Shifter General BUSCON 0 BUSCON 1 ADDRSEL 1 BUSCON 2 ADDRSEL 2 BUSCON 3 ADDRSEL 3 BUSCON 4 ADDRSEL 4 Data Page Pointer Context Ptr. Purpose Registers 16 R0 R0 Code Seg.Ptr SFR Embedded Systems 25.9.2009 Seite 2 04EI Vierstufige Befehls-Pipeline Fetch Decode 1. Instr. 2. Instr. 3. Instr. 4. Instr. Execute Time Write Back 1 Machine Cycle = 100 ns at 20 MHz CPU clock 100ns effektive Befehlsausführungszeit (20 MHz fCPU) Drei Pre-Fetch-Schritte in Wortbreite (Bus Controller) zur Unterstützung der Pipeline Optimierte Sprungausführung –Für Sprungbefehle (Jump, Cond. Jump, Call, Return,...) wird normaler Weise nur ein zusätzlicher Maschinenzyklus benötigt, um den Befehl an der Zieladresse zu holen Jump Cache –Für die Ausführung von Schleifen ist kein zusätzlicher Maschinenzyklus erforderlich Embedded Systems 25.9.2009 Seite 3 04EI Arithmetic Logic Unit A B Logic Operations: Cout Cin ALU flags op Z Shift / Rotate: Arithmetic Operations: add sub inc dec neg Embedded Systems and nand or nor exor exnor not sll sla rol srl sra ror s/ro : shift/rotate l/r : left/right l/a : logic (unsigned)/arithmetic (signed) 25.9.2009 Seite 4 04EI Barrel Shifter D0 D1 D2 D3 D15 1 1 1 0 0 0 1 1 1 0 0 0 1 1 1 0 0 0 1 1 1 0 0 0 1 1 1 0 0 0 S0 Embedded Systems S1 25.9.2009 Q0 Q1 Q2 Q3 Q15 S14 Seite 5 04EI General Purpose Register (GPR) 16 GPRs bilden eine Registerbank bestehend aus maximal – 8 Word-Registern und – 8 Word-Registern mit Bytezugriff auf das niederwertige und höherwertige Byte Die GPRs sind bit-addressierbar Die Registerbänke können beliebig im internen RAM angeordnet werden Der Platz der aktiven Registerbank wird durch den Context Pointer (CP) festgelegt CP kann leicht verändert werden um eine andere Registerbank auszuwählen - “Switch Context”-Befehl. Embedded Systems 25.9.2009 Seite 6 04EI 2 kByte internes RAM - Plazierung der Registerbänke und des Stack RH7 RH6 RH5 RH4 RH3 RH2 RH1 RH0 Stackpointer Underflow Stackpointer Stackpointer Overflow RL7 RL6 RL5 RL4 RL3 RL2 RL1 RL0 R15 R14 R13 R12 R11 R10 R9 R8 R7 R6 R5 R4 R3 R2 R1 R0 2KBytes internal RAM 0FDFE R15 R0 Context pointer 0FC00 STKUV STKUV SP STKOV 0F600 STKOV Embedded Systems 25.9.2009 Seite 7 04EI Adressraum Gesamter Adressraum: – 64 kByte nicht-segmentierter Adressraum – bis zu 4(16) MBytes segmentierter Adressraum: 64 kBbyte Code-Segmente und 16 kByte Daten-Pages – “von Neumann”-Architektur, die intern mit Mehrfach-BUS-Strukturen zur Vermeidung des BUS-Bottlenecks ausgestattet ist Interner Adressraum – 2 KByte RAM – 64 KBytes Flash/OTP ROM (C164CI-8FM) Flexible externe BUS-Konfigurationen – bis zu 22-Bit Adress-BUS / 8-Bit Daten-BUS (gemultiplexed) – bis zu 22-Bit Adress -BUS / 16- Bit Daten-BUS (gemultiplexed) – 5 völlig unabhängige Konfigurations-Register – 4 programmierbare “Chip Selects” und programierbare BUSKontrollsignale helfen externe Logik zu vermeiden. Embedded Systems 25.9.2009 Seite 8 04EI Interner und externer Adressplan des C164CI Segment 0 beinhaltet den internen Speicher 7 0.5k 0 512 Bytes SFR’s Internes RAM 2k Internes RAM Reserviert 0.5k 512 Bytes ESFR’s Full -CAN Reserviert 0x010000 Code Segmente Daten Pages 0x040000 0x00FE00 15 14 0x00FA00 3 0x030000 0x00F600 0x00F200 13 12 11 2 10 9 0x00F000 0x020000 8 7 0x00E800 1 Bit-adressierbarer Bereich X-Bus Peripheral Bis zu 4 MBytes 6 5 Externer Speicher 0x010000 4 Internal ROM/ FLAS H 2*32k 3 0x008000 32k Internes ROM / Flash E²PROM (kann auf Segm. 1 liegen) Embedded Systems 0 2 1 0x000000 25.9.2009 0x000000 0 Seite 9 04EI Die Programmiersprache C für den Mikrocontroller C164 C166 ist die Realisierung von ANSI-C für die Mikrocontroller-Familie C166. Der C166-Compiler sieht eine Reihe von Erweiterungen des ANSI-C Standards vor. Speziell solche, die direkt der Unterstützung der 166-Architektur dienen: C166-Bezeichnung Erläuterung memory types Als Ergänzung zur "Speicherklasse" kann zu jeder Variablenvereinbarung ein "Speichertyp" mit angegeben werden. Dies erlaubt eine vom aktuellen "Speichermodell" unabhängige Adressierung von Variablen in verschiedenen Adressräumen des 166-Systems. Folgende Typen sind definiert: near, idata, bdata, sdata, far, huge, xhuge. sfr Dient der Deklaration von "Special-Function-Register" (SFR) der 166-Familie sbit Deklaration von Bits innerhalb von SFR's. bit Datentyp bit. Rückgabewert, Übergabeparameter von Funktionen können vom Typ bit sein. bit-addressable Variable im bitadressierbaren Bereich können mittels bdata als Speichertyp vereinbart werden. Embedded Systems 25.9.2009 Seite 10 04EI Die Programmiersprache C für den Mikrocontroller C164 C166-Bezeichnung Erläuterung registerbank (using) Jede Funktion kann eine Vereinbarung enthalten, in der die zu benutzende Registerbank angegeben wird. interrupt Funktionen können als Interrupt-Service-Routinen vereinbart werden durch Angabe des Interruptnamens bzw. –vektors. register mask Der C166-Compiler erzeugt für jede C-Funktion eine Registermaske, in der die durch die Funktion verwendeten Register aufgeführt werden. Diese können für Funktionsprototypen verwendet werden, um die Registerausnutzung zu optimieren. RTX166 tasks Durch das Schlüsselwort _task_ werden Funktionen als Tasks des Betriebssystems RTX166 spezifiziert. Neue Schlüsselwörter (Keywords): Speicherarten: near, idata, bdata, sdata, far, huge, xhuge Datentypen: bit, sfr, sbit Funktionen: interrupt, _task_, using Embedded Systems 25.9.2009 Seite 11 04EI Die Programmiersprache C für den Mikrocontroller C164 Speicherarten (Memory Types) Auswahl Adressraum near 16-Bit Adressen bis zu 64 kBytes idata On-chip RAM (schnellster Zugriff) bdata Bit-adressierbares On-chip-RAM sdata System Page (0xC000-0xFFFF) inklusive SFR‘s far 32-Bit Pointer mit 16-Bit Adressberechnung, die Objektgröße beträgt 16 kByte. huge 32-Bit Pointer mit 16-Bit Adressberechnung, die Objektgröße beträgt 64 kByte. xhuge 32-Bit Pointer mit 32-Bit Adressberechnung, die Objektgröße beträgt 16 MByte. Embedded Systems 25.9.2009 Seite 12 04EI Die Programmiersprache C für den Mikrocontroller C164 Entsprechend den Speicherarten können Speichermodelle als Voreinstellungen vorgegeben werden, die immer dann Anwendung finden, wenn bei der Variablen- oder Funktionsdefinition keine Speicherart explizit angegeben wird. Dies erfolgt mittels der Preprozessordirektive: # pragma speichermodell Speichermodell Variable Funktionen Segmentierung Codeumfang TINY SMALL COMPACT HCOMPACT MEDIUM LARGE HLARGE near near far huge near far huge near near near near far far far nein ja ja ja ja ja ja 64k 64k 64k 64k unbegrenzt unbegrenzt unbegrenzt Embedded Systems 25.9.2009 Seite 13 04EI Die Programmiersprache C für den Mikrocontroller C164 Datentypen: Speicherumfang und Wertebereich Datentyp Speicherumfang Wertebereich bit # signed char unsigned char signed int unsigned int signed long unsigned long float double pointer 1 Bit 1 Byte 1 Byte 2 Bytes 2 Bytes 4 Bytes 4 Bytes 4 Bytes 8 Bytes 2/4 Bytes 0 oder 1 -128 bis +127 0 bis 255 -32768 to + 32767 0 bis 65535 -2147483648 bis +2147483642 0 bis 4294967295 1.176E-38 bis 3.40E+38 1.7E-308 bis 1.7E+308 Adresse des Objects Datentypen für den Zugriff auf Special Function Registers (SFR) sbit # sfr # 1 Bit 2 Bytes 0 or 1 0 to 65535 # spezielle Datentypen in C166, die in ANSI-C nicht definiert sind. Embedded Systems 25.9.2009 Seite 14 04EI Integrierte Entwicklungsumgebung – µVision2 Editor / Project Management MacroAssembler ANSI C Compiler CLibrary RTX Tiny Library Real Time Operating System Manager Linker / Locater – Debugger – Simulator Emulator & PROM Programmer CPU & Peripheral Simulator Embedded Systems Monitor Target Debugging 25.9.2009 Ab ins Praktikum Seite 15 04EI Code-Adressierung mittels Segmentierung im 4 MByte Adressraum Code Segment Pointer (CSP) zur Code-Adressierung 15 14 13 8 7 6 0 5 Code Seg. Pointer 15 14 13 8 7 0 16-Bit Instr. Pointer 6-Bit Segmentnummer 16-Bit 22-Bit physikalische Code-Adresse (C164) Der Instruction Pointer (IP) wird nach jeder Befehlsholphase inkrementiert Der Code Segment Pointer (CSP) wird nur durch absolute Sprünge, bzw. indirekt beim Rücksprung aus Unterprogrammen vom Stack verändert. Embedded Systems 25.9.2009 Seite 16 04EI Adressierung von Daten mittels Seitenauswahl (Paging) innerhalb des 4 MByte Adressraumes Daten-Adressierung über Data Page Pointer (DPP) 15 14 13 16-bit Adresse 0 Auswahl eines Data Page Pointer DPP3 DPP2 DPP1 DPP0 10-bit 14-bit Seitennummer Physikalische 24-Bit Daten-Adresse (bis zu 22 aussen verfügbar beim C164) SFR Embedded Systems 25.9.2009 Seite 17 04EI External Bus Controller Ermöglicht variables Timing von CPU-Steuersignalen mittels Software Realisiert bis zu 4 Chip-Select-Signale Auswahl von 4 Adressbereichen möglich Special Function Register BUSCON0..4 Programmierbare Zeiten. Festlegung von CS# - Signalen. Auswahl der Breite des Daten-BUS 8 / 16 Bit. Special Function Register ADDRSEL1..4 Programmierbare Ausschnitte aus dem Adressraum für den Zugriff auf externe Komponenten mit den Eigenschaften der zugeordneten BUSCONx- Register. Embedded Systems 25.9.2009 Seite 18 04EI Gemultiplexter Adress- und Daten-BUS Verlängern des AdressSetups Speicherzugriffszeit A16..A21 Tri-State - Zeit Address ALE CS# A0..A15 D0..D15 (7) Address Data RD# RD-Delay A0..15 D0..15 (7) Address Data WR# WR-Delay Embedded Systems 25.9.2009 SFR Seite 19 04EI Integrierte Chip Select - Signale CS0# CS1# CS2# CS3# P6.0 P6.1 P6.2 P6.3 BUSCON0 BUSCON1 BUSCON2 BUSCON3 Aktiv für jenen Adressraum der nicht durch CS1#..CS3# abgedeckt wird. ADDRSEL1 ADDRSEL2 ADDRSEL3 Die Basisadresse ist stets ein Vielfaches des Adressbereiches. (d.h. der Chip Select mit einem Adressbereich von 128kByte beginnt an einer 128kByte Grenze) C164 A21 A20 A19 C B A CS3# CS2# CS1# G CS11 CS10 CS9 CS8 CS7 CS6 CS5 CS4 0xB80000 0xB00000 0xA80000 0xA00000 0x980000 0x900000 0x880000 0x800000 74ACT138 C164 P3.9 P3.8 P3.6 C B A CS3# CS2# CS1# G CS11 CS10 CS9 CS8 CS7 CS6 CS5 CS4 0xF00000 0xE00000 0xD00000 0xC00000 0xB00000 0xA00000 0x900000 0x800000 74ACT138 Extra Memory-Mapped Chip-Selects Extra IO-Mapped Chip-Selects Alle mit gleichem Bus-Mode, Waitstates, usw. Embedded Systems 25.9.2009 Seite 20 04EI Anschluß von externen Speicherbausteinen mit 8 Bit- Organisation RAM RAM WE# OE# CE# D0-7 A0-16 C164 [20 MHz] MT5LC128K8D4 WE# OE# CE# D0-7 A0-16 MT5LC128K8D4 MT5LC128K8D4 Fa. Micron SRAM 128k x 8 Zugriffszeit 25 ns ADDRSEL1 = 0x0406 BUSCON1 = 0x04CF WRL# WRH# RD# D0-15 A16-19 EN OE# CS# D0-7 A0-18 ALE A1-15 15-Bit D-Latch Embedded Systems OE# CS# D0-7 A0-18 CS1# CS0# ROM ROM AM27C040 Fa. AMD Eprom 512k x 8 Zugriffszeit 120 ns BUSCON0 = 0x04CE AM27C040 AM27C040 25.9.2009 Seite 21 04EI Anschluß von externen Speicherbausteinen mit 16 Bit- Organisation IDT71016 WE# BLE# BHE# OE# CE# D0-15 A0-15 RAM C164 [20 MHz] WR# IDT71016 Fa. IDT (Integrated Device Technology) SRAM 64k x 16 Zugriffszeit 20 ns ADDRSEL1 = 0x0405 BUSCON1 = 0x04CF BHE# RD# D0-15 A16-17 OE# CS# D0-15 A0-16 EN CS1# CS0# ALE A0 A1-15 ROM 16-Bit D-Latch Embedded Systems M27C202 Fa. ST Microelectronics ST Eprom 128k x 16 Zugriffszeit 100 ns BUSCON0 = 0x04CE M27C202 25.9.2009 Seite 22 04EI Sich überdeckende Adressbereiche Inaktiver Bereich Höchste Priorität Aktiver Bereich XBCON0 Überlappen nicht zulässig BUSCON4 BUSCON2 BUSCON1 BUSCON3 BUSCON0 0xFFFFFF 0x000000 Embedded Systems 25.9.2009 Seite 23 04EI Interrupt System Interrupt Controller – Kurze Interrupt-Reaktionszeiten: Min. 250ns, typisch 400ns (@20 MHz) – Geringer Overhead für ISR’s – Leistungsfähige Priorisierung in 15 Prioritätsstufen, zu je 4 Gruppen – Hardware Traps detektieren Laufzeitfehler – Software Traps Peripheral Events Controller (PEC) – Entlastet die CPU von einfachen und häufig auftretenden ISR’s – Interruptgesteuerter “DMA-ähnlicher” Datentransfer ohne CPUEingriff – Reaktionszeiten: Min. 150ns, typisch 300ns mit einer CPU-Belastung von 100ns (@20 MHz) Embedded Systems 25.9.2009 Seite 24 04EI Interrupts und PEC - Priorisierung PEC 7 PEC 6 group 3 group 2 PEC 5 group 1 Level 15 PEC 4 Group group 0 3 2 1 0 PEC 3 PEC 2 group 2 Level 14 group 3 group 2 Level 1-13 group 3 (Level 0) Embedded Systems group 2 PEC 1 group 0 group 1 group 0 group 1 PEC 0 group 1 Level group 3 group 0 25.9.2009 15 64 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 1 Seite 25 04EI Interrupt Processing INTR Service: Interrupt Control Register des auslösenden Peripherie-Elementes Retten: PSW, CSP, IP INTR Flag ist gesetzt Periph. Interrupt Prioritäts-Check Periph. Interrupt Vergleich der Interruptpriorität mit der Laufzeit-Priorität der CPU falls höhere Priorität Gruppen Check Neue CPU-Prio. im PSW. CSP und IP aus Peripherie-Vector oder Trap-Nummer Lösche INTR Flag Periph. Interrupt Externer Interrupt* Periph. Interrupt External Interrupt* PEC Service 16 Prioritäts-Stufen 4 Gruppen * Externe Interrupts sind z.B. statt des “Capture” Eingangs möglich 32 Peripherie Interrupts 13 ext. Interrupts (+ NMI) einschließlich 4 “schnelle” Interrupts Vektoren Embedded Systems 25.9.2009 SFR Dave Seite 26 04EI Peripheral Events Controller (PEC) Interrupt hat den Prioritäs- und Gruppen-Check erfüllt Interrupt Priorität 14 oder 15 und Data Counter > 0 Interrupt Priorität < 14 Interrupt Service PEC Service Memory Segment 0 0xFFFF Peripheral Events Contoller Contr. Reg. INTR Service: 8 PEC Kanäle Retten: PSW, CSP, IP Neue CPU-Prio. im PSW. CSP und IP aus Peripherie-Vector oder Trap-Nummer Prioritäts- & GruppenCheck Data Counter Byte bzw. Word Transfer SRC Pointer DEST Pointer 0x0000 Interrupt falls Data Counter = 0 SFR Embedded Systems 25.9.2009 Seite 27