Laborbericht: Versuch Differenzverstärker

Werbung

Halbleiterschaltungstechnik

Laborversuch

Bericht

Differenzverstärker

Teilnehmer:

...

Tong Cha, Matrikelnr.: ... (Autor)

Datum der Simulation: 11.11.2008

Datum der Messung: 25.11.2008

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

1

Inhalt

Seite

3.2.1 npn- Differenzstufe ohne RE .............................................. 3

Vorbereitung .................................................................................................. 3

.1 Berechnung der Spannung Vminus............................................................... 3

.2 Excel Tabelle.............................................................................................. 3

Simulation ....................................................................................................... 4

1.A Schaltungsaufbau........................................................................................4

1.B Ermittlung von Vminus..................................................................................4

1.C DC-Simulation IC1 und IC2.............................. ............................................5

1.D Übertragung von IC1 und IC2 in die Excel- Tabelle/Messsung.....................5

3.2.2 npn- Differenzstufe mit RE ...................................................7

Vorbereitung .................................................................................................... 7

2.1 Berechnung der Spannung I01 und I02, sowie VMINUS ...................................7

2.2 Berechnung der Steilheit SDV und ADV .........................................................8

Simulation ....................................................................................................... 10

2.A Ermittlung von Vminus1 und Vminus2..............................................................10

2.B/C Simulation von VOUT./Vergleich mit Messung........................................11

2.D Vergleich ADVOUT – Simulation und Rechnung..........................................15

3.2.3 Begrenzungsverhalten der Differenzstufe...........................17

Vorbereitung ....................................................................................................17

3.1 Berechnung von Vplus...................................................................................17

3.2 Fallanalyse....................................................................................................18

3.3 Verlaufsskizze von VC1, VC2 und VOUT.......................................................20

Simulation ........................................................................................................ 21

3.A Simulation von VC1, VC2 und VOUT..............................................................21

3.B Simulation/Messung von VC1, VC2 und VOUT (Vplus-Parametrik)................22

3.2.4 Betrieb der Differenzstufe als Steilheitsmultiplizierer.......25

Vorbereitung .....................................................................................................25

4.1 Berechnung der Verstärkung ADV ohne RE...................................................25

4.2 Erstellen einer Excel-Tabelle zur Rechung, Simulation und Messung.........26

Simulation ......................................................................................................... 27

4.A Ermittlung von Vminus...................................................................................27

4.B Sinusspannung VEIN......................................................................................27

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

2

4.C Transientensimulation von VOUT (Vminus-Parametrik)...................................28

4.D Vergleich - Simulation, Rechnung und Messung........................................29

Vorwort

In diesem Bericht werden im Rahmen des Halbleiterschaltungstechnik- Labors die

verschiedenen Begebenheiten der Differenzstufe untersucht. Dabei werden für die Analyse

theoretische Überlegungen und Berechnungen, die entsprechenden Simulationen und zuletzt

die Ergebnisse der Messungen gegenübergestellt. Hintergründe zum Messvorgang werden

lediglich dann erläutert, wenn sie für die Darstellung des Sachverhalts notwendig sind,

ansonsten fließen die Messergebnisse in die Aufgabenteile der Vorbereitung und Simulation

hinein.

3.2.1 npn- Differenzstufe ohne RE

Vorbereitung

.3 Berechnung der Spannung Vminus

Der Basisstrom am Transistor QA in der Stromquelle wird zu null gesetzt. Diese

Vereinfachung liefert folgende Formel:

Damit kann Vminus durch Umstellen errechnet werden:

.4 Excel Tabelle

Eine Excel-Tabelle zur Darstellung der Ströme Ic1 und Ic2 wurde erstellt. Dabei wurden

Spalten für die errechneten, simulierten und gemessenen Werte vorbereitet:

Tabelle

3.1

i0 / mA

1

VT / V

0,026

beta

200

alpha

0,99502488

Zähler

{Ic1/2}

0,99502488

Vein

Vin

Ic1 (rech) Ic2 (rech)

Ic1 (sim)Ic2 (sim)

Ic1 (mess) Ic2 (mess)

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

3

/V

/V

/ mA

/ mA

/ mA

/ mA

/ mA

/ mA

3.2.1 npn- Differenzstufe ohne RE______________________________________________________________________________________________

Simulation

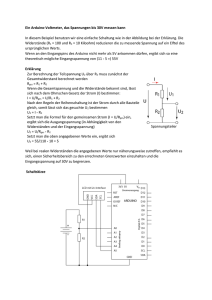

1.A Schaltungsaufbau

Die Schaltung des Verstärkers wird in SCHEMATICS erstellt und als Transistor das npnModell CA3046 gewählt. Dabei werden die Widerstände RA und RB mit den Werten

und

versehen.

1.B Ermittlung von Vminus

In PROBE wird der Strom I0 in Abhängigkeit von Vminus dargestellt. Hier beträgt der Wert für

Vplus = 12V – damit ist eine Sättigung der Transistoren Q1 und Q2 ausgeschlossen.

Die Kennlinie I0(Vminus) zeigt, dass sich bei dem Strom I0 = 1 mA eine Spannung von

V0 = -10,845 V einstellt. Man vergleiche dieses Ergebnis mit dem in 1.1 berechneten Wert.

IC(QA) stellt in PROBE den Strom dar, der in den Kollektor des Transistors QA, also in die

Stromquelle führt → IC(QA) = I0.

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

4

3.2.1 npn- Differenzstufe ohne RE______________________________________________________________________________________________

1.C DC-Simulation IC1 und IC2

Nun wird VIN als Variable zur Darstellung der Kollektorströme von Q1 und Q2 eingestellt.

Dazu wird ein DC-Sweep mit der Spannungsquelle VEIN gefahren und in PROBE die x-Achse

mit VEIN*0,2 eingestellt. So können die Kennlinien Ic1 und Ic2 direkt in Abhängigkeit von VIN

dargestellt werden.

Der Spannungsteiler mit RA und RB an der Basis von Q1 drosselt die Eingangsspannung VEIN

auf das 0,2 fache: VIN = VEIN · 0,2.

Ein interessantes Ergebnis stellt sich ein, wenn die Eingangsspannung VIN mit

-200mV < VIN < +200mV direkt durch eine Spannungsquelle eingespeist und nicht mit

einem Spannungsteiler auf den geforderten Spannungsbereich komprimiert wird: Die

Kennlinien von Ic1 und Ic2 sind leicht verkantet, bei der Schaltung mit Spannungsteiler und

-2V < VEIN < +2V verlaufen sie dagegen „sauber“. Es kann also ausgesagt werden, dass

Abweichungen auftreten, wenn die Spannungsquelle nicht abgeschlossen ist.

1.D Übertragung von IC1 und IC2 in die Excel- Tabelle (Rechnung, Simulation, Messung)

Die in Examine Output gewonnenen, sowie die errechneten und gemessenen Werte werden in

die vorbereitete Excel-Tabelle eingefügt und in einem Diagramm als Kennlinien dargestellt.

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

5

Hier ist gut zu erkennen, dass die errechneten Werte für Ic1 und Ic2 nur minimal von den

simulierten Ergebnissen abweichen. Auch die Messpunkte stimmen fast mit den Werten der

Rechnung und Simulation überein (ggf. zoomen).

Die entsprechende Abbildung am Oszilloskop:

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

6

3.2.2 npn- Differenzstufe mit RE

Vorbereitung

2.1 Berechnung der Spannung I01 und I02, sowie VMINUS

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

7

Der Spannungsabfall an RE von VRE1= 26 mV und VRE2= 104 mV ist vom Strom I0 abhängig,

der wiederum durch VMINUS eingestellt wird. Folgende Berechnungen sind nötig, um diese

Bedingungen zu erfüllen:

3.2.2 npn- Differenzstufe mit RE______________________________________________________________________________________________

2.2 Berechnung der Steilheit SDV und ADV

Folgende Berechnungen werden zur Ermittlung der Steilheit SDV und der daraus folgenden

Verstärkung ADV durchgeführt. Zunächst mit RE = 330 Ω und dann mit RE = 0 Ω (also ohne

RE).

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

8

2.2 Berechnung der Steilheit SDV und

ADV_______________________________________________________________________________________

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

9

_________________________Zusammenfassung_______________________________

Die Berechnungen liefern einen wichtigen Aspekt: Die Steilheit verkleinert sich,

wenn die Emitterwiderstände RE1 = RE2 = RE in der Schaltung vorhanden sind.

2.3 Vorbereitung der Excel-Tabelle

Es wurde eine Excel-Tabelle vorbereitet, in der die Größen I0, VIN, VOUT/mit/rech, VOUT/ohne/

rech, VOUT/mit/sim, VOUT/ohne/sim, VOUT/mit/mess, VOUT/ohne/mess, SDV/mit, SDV/ohne, ADV/mit, ADV/ohne

für jeweils VRE=26mV und VRE=104mV aufgeführt werden (Eingangsspannungsbereich:

-0,4V < VIN < +0,4V).

3.2.2 npn- Differenzstufe mit

RE___________________________________________________________________________________________________

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

10

Simulation

2.A Ermittlung von Vminus1 und Vminus2

Mit dem selben Verfahren wie in 1.B wird die Spannung VMINUS für beide Ströme

I01=157,6µA und I02=630,3µA ermittelt:

Für VMINUS stellt sich jeweils ein:

VMINUS1 (I01=157,6µA) = -2,7252V

VMINUS2 (I02=630,3µA) = -7,3036V

2.B/C Simulation von VOUT – Rechnung, Simulation und Messung im Vergleich

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

11

Mit den beiden in 2.A ermittelten Spannungen VMINUS1 und VMINUS2 wird nun eine

Simulation durchgeführt und die Ausgangsspannung VOUT als Funktion von VIN in

PROBE dargestellt. Um die Funktion des Jumpers zu simulieren, wird RE parametrisch

auf RE = 330 Ω und RE ≈ 0 Ω eingestellt. Die Werte aus Examine Output werden der

vorbereiteten Exel-Tabelle beigefügt, so dass die Simulation mit der Rechnung, sowie den

Messergebnissen verglichen werden kann.

Mit VMINUS1 = -2,7252V erhält man im Excel-Diagramm:

(Legende: MIT/OHNE → mit/ohne RE)

Darstellung am Oszilloskop:

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

12

Für VMINUS1 = -2,7252V, d.h. I01=157,6µA zeigt das Oszilloskop jeweils für JE offen und

JE geschlossen folgende Verläufe:

2.A Simulation von

VOUT______________________________________________________________________________________________________

Mit VMINUS2 = -7,3036V erhält man im Excel-Diagramm:

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

13

Die Werte von VDVOUT wurden jeweils linear berechnet. Deswegen beschreibt die

Kennlinie von VDVOUT(rech) lediglich das Verhalten der Steigung bei VIN0=VIN=0V in Form

einer Tangente. Das Ergebnis ist dennoch repräsentativ: Die sehr geringe Abweichung der

Steigungen im Arbeitspunkt VIN0 aus Rechnung und Simulation, sowie Messung zeigt,

dass die Excel-Tabelle korrekt eingerichtet wurde.

Darstellung am Oszilloskop:

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

14

Für VMINUS2 = -7,3036V, d.h. I02=630,3µA zeigt das Oszilloskop jeweils für JE offen und

JE geschlossen folgende Verläufe:

__________________________Zusammenfassung______________________________

Die Diagramme und Messungen bestätigen die Rechnungen aus 2.2: Die Anwesenheit

von RE erwirkt eine Reduktion der Steilheit in allen Fällen. Die Verstärkung bei

vorhandenen Emitterwiderständen vergrößert sich nur um das 1,6-fache, wenn der

Strom I0 auf das 4-fache erhöht wird. Bleiben die Emitterwiderstände fern,

vervierfacht sich dagegen die Verstärkung. Die Verstärkung verhält sich dann

proportional zum Eingangstrom, wenn die Emitterwiderstände nicht mitwirken:

2.D Vergleich ADVOUT – Simulation und Rechnung

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

15

Die Verstärkung ADVOUTsim aus der Simulation wurde wie folgt ermittelt:

Dieser Auszug aus der Excel-Tabelle liefert die Werte der Simulationskennlinie am

Arbeitspunkt VIN0 = 0V:

Ermittlung von ADVOUTsim für RE=330Ω, I01=157,6µA:

Zwei signifikante Werte um den Arbeitspunkt VIN0 = 0V aus VDVOUTsim werden verwendet,

um die Differenz ΔVOUTsim zu errechnen und daraus die Steigung, bzw. die simulierte

Verstärkung ADVOUTsim zu ermitteln:

Der errechnete Wert für die Verstärkung aus 2.2 beträgt

ADVOUTrech = 15,078.

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

16

2.D Vergleich ADVOUT – Simulation und

Rechnung___________________________________________________________________

Nach dem selben Verfahren werden nun die simulierten Verstärkungen aus der Variation

von I0 und RE errechnet und jeweils mit den Ergebnissen aus 2.2 verglichen:

Für RE=0Ω, I01=157,6µA:

ADVOUTsim = 29,0

ADVOUTrech = 30,0156

Für RE=330Ω, I01=630,3µA:

ADVOUTsim = 24,0

ADVOUTrech = 24,121

Für RE=0Ω, I01=630,3µA:

ADVOUTsim = 116,0

ADVOUTrech = 120,61

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

17

3.2.3 Begrenzungsverhalten der Differenzstufe

Vorbereitung

3.1 Berechnung von Vplus

Im Folgenden wird die Spannung Vplus berechnet, die eingestellt werden muss, um eine

Sättigung der Transistoren Q1 und Q2 zu vermeiden. Aufgrund der Symmetrie von Q1 und Q2

braucht dabei nur ein Transistor betrachtet werden, der mit der höchsten Spannung im

gegebenen Eingangsspannungsbereich -200mV < VIN < +200mV eingespeist wird, also

VINmax = VIN = 200mV. Prinzipiell müsste der Emitterstrom an einem einzelnen Transistor

betragen. Die Rechnung zeigt jedoch, dass mit „ungeteiltem“ Vplus der Fehler wieder

aufgehoben wird.

Im Ersatzschaltbild für den Sättigungsfall wird eine Maschengleichung aufgestellt (α=0,995):

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

18

-Vin + VBE0 – VCEsat – VC + Vplus = 0

3.1 Berechnung von

Vplus____________________________________________________________________________________________________________

Vplus = Vin – VBE0 + VCEsat + VC = Vin – VBE0 + VCEsat + (Rc · α · I0)

Vplus = 0,2V – 0,7V + 0,2V + (10kΩ · 0,995 · 1mA)

Vplus = 9,65 V

→ Für Vplus > 9,65V sättigen beide Transistoren Q1 und Q2 nicht.

----------------------------------------------------------------------------------------------------------------3.2 Fallanalyse

Eine Situation mit gegebenen Einstellungen soll analysiert und anschließend ausgesagt

werden, in welchem Eingangsspannungsbereich keiner der beiden Transistoren sättigt.

Gegeben:

Vplus = 8V, I0 = 1mA , RE = 0Ω , Rc = 10k Ω , VCEsat = 0,2V

Zunächst wird am Ersatzschaltbild im Sättigungsfall für einen Transistor die

Eingangsspannung VIN ausgerechnet (vgl. 3.1).

-Vin + VBE0 – VCEsat – VC + Vplus = 0

Vin = VBE0 – VCEsat – VC + Vplus = VBE0 – VCEsat – (Rc · α · I0) + Vplus

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

19

Vin = 0,7V – 0,2V – (10k Ω · 0,995 · 1mA) + 8V

Vin = -1,45V ≈ -1,5V

3.2

Fallanalyse___________________________________________________________________________________________________________________

Im Sinne der Kleinsignalbetrachtung werden die Emitteranschlüsse als virtuelle Masse und

die Eingangsspannung VIN jeweils zur Hälfte und mit entgegengesetztem Vorzeichen an der

Basis beider Transistoren festgelegt. Dieser Ansatz ist nur bei symmetrischer Anordnung

zulässig (Q1 und Q2 haben die gleichen Eigenschaften und RC1=RC2)!

Somit gilt für beide Transistoren:

Für den Eingangsspannungsbereich gilt damit:

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

20

3.2

Fallanalyse___________________________________________________________________________________________________________________

Die zugehörige Simulation in PROBE bestätigt dieses Ergebnis:

Hier ist deutlich zu erkennen, dass die Transistoren für VIN = ±50mV aktiv sind, bzw. im

Eingangsspannungsbereich -50mV < VIN < +50mV keine Sättigung stattfindet.

3.3 Verlaufsskizze von VC1, VC2 und VOUT

Qualitative Verlaufsskizze von VC1 (blau), VC2 (orange) und VOUT (rot)

(Vplus=8V):

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

21

3.2.3 Begrenzungsverhalten der Differenzstufe____________________________________________________________________________

Simulation

3.A Simulation von VC1, VC2 und VOUT

Für die Simulation in PROBE wird Vminus = -10,8V eingestellt, so dass sich ein Strom I0 von

I0 = 1mA ergibt. Für Vplus = 8V und einem Eingangsspannungsbereich von

-200mV < VIN < +200mV lassen sich folgende Verläufe für VC1, VC2 und VOUT abbilden:

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

22

(VC2 - VC1 = VOUT )

Man vergleiche diese Darstellung in PROBE mit der Skizze in 3.3.

3.B Simulation/Messung von VC1, VC2 und VOUT (Vplus-Parametrik)

Die Versorgungsspannung Vplus wird nun parametrisch eingestellt:

Vplus = 7V → 7,5V → 8 V → 8,5 V → 9 V → 9,5 V → 10 V → 10,5 V → 11 V

Man erhält folgende Kennlinien:

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

23

Durch Abzählen (unteres Diagramm) erhält man den Wert für Vplus, bei dem gerade noch nicht

die Sättigung eintritt: Beginnend mit der Linie, die dem Nullpunkt am nächsten ist, zählt man

von 7,0V in 0,5V-Schritten aufwärts die Linien nach außen ab. Die 6. Kennlinie stellt die

Erste dar, bei der keine Sättigung ersichtlich ist, somit ergibt sich der Wert Vplus = 9,5 V, bei

dem gerade noch nicht die Sättigung eintritt.

Man vergleiche dies mit der Rechnung in 3.1:

V plus (rech) = 9.65V

Darstellung am Oszilloskop

Es wurden Messungen von VC1 und VC2 durchgeführt und dabei die Versorgungsspannung

Vplus mit folgenden Werten variiert:

Vplus = 7V → 8 V → 9 → 10 V

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

24

Die Messungen liefern folgende Ergebnisse: Bei den Versorgungsspannungen

Vplus = 7 V, 8 V und auch noch bei 9 V sind die Verläufe im „unteren“ Bereich ähnlich wie

sie in der Simulation ersichtlich sind. Im „oberen“ Bereich treten jedoch starke

Abweichungen im Vergleich zur Simulation auf.

Der Hintergrund für dieses zunächst verwirrendes Resultat wird im Folgenden erläutert.

3.B Messung von VC1, VC2 und VOUT (Vplus-Parametrik)

______________________________________________________________________

Um Störsignale weitgehend fernzuhalten verfügt die Laborplatine über einen Widerstand nach

Masse an der Basis von Q2 mit einem Wert von RB2 = 10 Ω. Dieser wird in der Simulation

nicht berücksichtigt.

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

25

Die wesentliche Ursache für die Abweichung ist jedoch der Aufbau der Transistoren im

Transistorarray-Chip, der sich auf der Laborplatine befindet.

Die Anordnung der n-p-n- Schichten erzeugt durch die Vereinigung zweier npn-Transistoren

zusätzlich eine Substrat- p-n-p-Wirkung, so dass sich die reale Schaltung wie folgt

zusammensetzt:

Durch das zusätzliche Einwirken von Q3 und Q4 (parasitäre pnp) werden die Kollektorströme

von Q1 und Q2 in erheblichem Maße beeinflusst. Aus diesem Grund nehmen die Spannungen

VC1 und VC2 im Sättigungsfall den oben gezeigten Verlauf an

Beim sog. Latch-Up- Effekt tritt ein ähnliches Verhalten auf, bei dem parasitäre Thyristoren

die Performance der Schaltung beeinflussen.

3.2.4 Betrieb der Differenzstufe als Steilheitsmultiplizierer

Vorbereitung

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

26

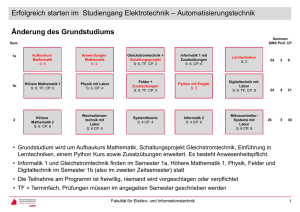

4.1 Berechnung der Verstärkung ADV ohne RE

Die Verstärkung ADV wird für 6 verschiedene Ströme I0n berechnet:

I01 = 100 µA, I02 = 200 µA, I03 = 400 µA, I04 = 600 µA, I05 = 800 µA, I06 = 1000 µA

( RC = 10kΩ , α = 0,995 , VT = 26mV )

Folgende Formel zur Berechnung der Verstärkung ADV im Arbeitspunkt (RE=0Ω) wird

verwendet (Kleinsignalberechnung):

Damit erhält man die verschiedenen Verstärkungen ADVn:

4.1 Berechnung der Verstärkung ADV ohne RE____________________________________________________________________________

Die entsprechenden Ausgangsspannungen VDVOUTn zu den jeweiligen Strömen betragen

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

27

(VINrms = 10mV):

4.2 Erstellen einer Excel-Tabelle zur Rechung, Simulation und Messung

Es wurde eine Excel-Tabelle vorbereitet, in der die Größen I0, Vminus, VDVOUT/rech, VDVOUT/sim,

VDVOUT/mess, ADV/rech, ADV/sim, ADV/mess aufgeführt werden (Eingangsspannung konstant mit

VIN=10mV).

zugehörige Parameterliste:

Parameter:

R3 / Ohm

4700

Vbe0 / V

0,7

Rc / Ohm

10000

Vin / V

0,01

Beta

200

Alpha

0,99502488

VT / V

0,026

Vorbereitung

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

28

4.A Ermittlung von Vminus

Nach dem selben Verfahren wie in 1.B sowie 2.A werden für die gegebenen Ströme I01 bis I06

die zugehörigen Spannungen Vminus1 bis Vminus6 anhand einer PROBE-Simulation ermittelt.

Der Kollektorstrom ICQA wird dabei in Abhängigkeit von Vminus simuliert und die Werte

abgelesen, bei denen sich die entsprechenden Ströme I0n einstellen.

Man erhält folgende Werte für VMINUSn :

I01 = 100 µA

I02 = 200 µA

I03 = 400 µA

I04 = 600 µA

I05 = 800 µA

I06 = 1000 µA

→

→

→

→

→

→

Vmin1

Vmin2

Vmin3

Vmin4

Vmin5

Vmin6

= -2.15 V

= -3.15 V

= -5.08 V

= -7.01 V

= -8.93 V

= -10,80 V

4.B Sinusspannung VEIN

In SCHEMATICS wird die bisherige DC-Quelle mit einer Sinusförmigen Spannungsquelle

ersetzt. Sie erhält folgende wesentliche Einstellungen: f = 1kHz, VAMP = 50mV. Mit einer

Amplitude von 50 mV kann an der Basis von Q1 eine Effektivspannung von VINrms=10mV

gemessen werden (s. Erläuterungen in 1.C).

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

29

4.C Transientensimulation von VOUT (Vminus-Parametrik)

Die Ausgangsspannung VOUT der Differenzstufe als Steilheitsmultiplizierer wird in

Abhängigkeit der eingespeisten Sinus-Spannungsquelle VIN in PROBE simuliert und dabei

VMINUS parametrisch mit den in 4.A ermittelten Werten variiert.

Man erhält damit die zugehörigen Amplituden VOUT(peak), die sich für die verschiedenen Werte

von VMINUS ergeben:

n. VMINUSn → VOUT(peak)n

1. - 2,15 V

2. - 3,15 V

3. - 5,08 V

4. - 7,01 V

5. - 8,93 V

6. - 10,8 V

→

→

→

→

→

→

187.26 mV

375.00 mV

739.12 mV

1098.9 mV

1450.6 mV

1786.4 mV

Die Messergebnisse von VOUT(peak) werden in die vorbereitete Excel-Tabelle eingefügt und aus

jedem die Verstärkung ADV berechnet:

Damit ergeben sich die Spalten für VOUT(sim) und ADV(sim) :

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

30

4.D Vergleich - Simulation, Rechnung und Messung

Die Verläufe ADVrech(I0) und ADVsim(I0), sowie ADVmess(I0), lassen sich in Excel wie folgt

darstellen (ggf. zoomen):

Hier ist eine leichte Abweichung von Simulation und Rechnung beobachtbar: PSpice

berücksichtigt bei dem Schaltungsaufbau mit CA3046-Transistoren den EARLY-Effekt, der

die Performance von realen Transistoren verschlechtert und sich dadurch die Verstärkung um

einen kleinen Teil erniedrigt. Die Messergebnisse lassen dies ebenfalls erkennen.

Die Ergebnisse der Rechnung mit

Idealfall ab.

bilden die Verstärkung dagegen für den

________________________________________________________________________________________

Labor Halbleiterschaltungstechnik Differenzverstärker; Tong Cha,...

31