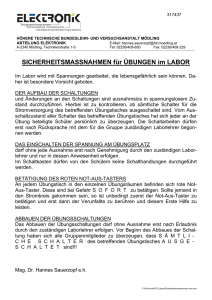

Maßnahmen zur Steigerung der Zuverlässigkeit

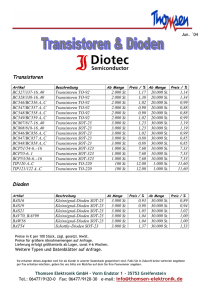

Werbung