PowerPoint-Präsentation

Werbung

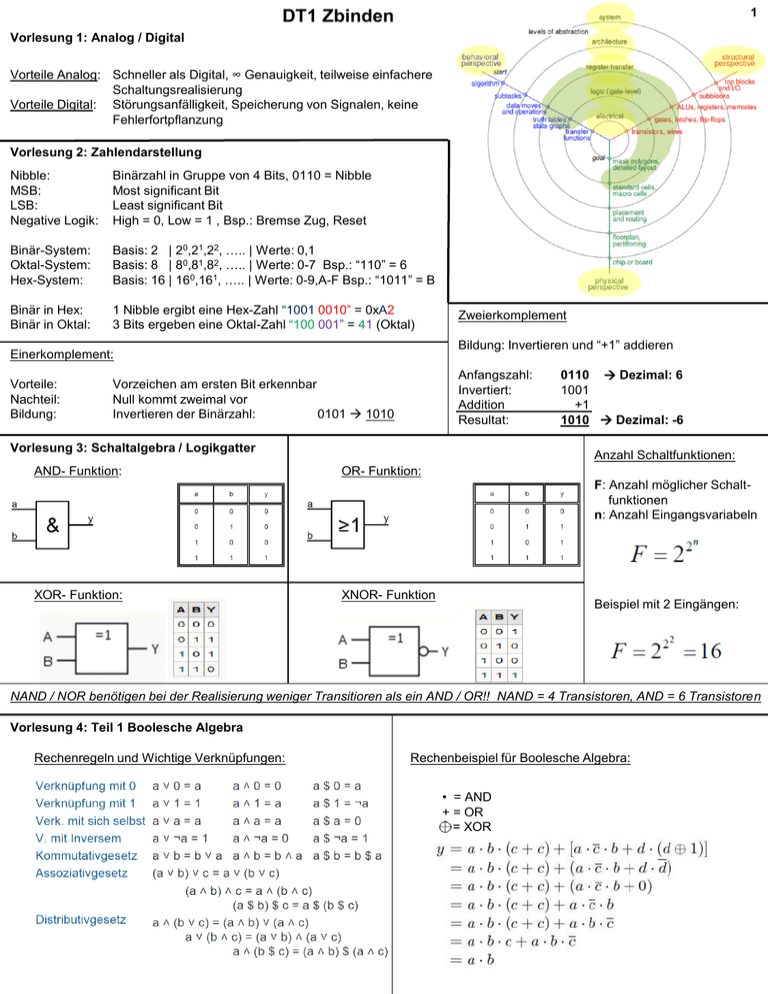

1 DT1 Zbinden Vorlesung 1: Analog / Digital Vorteile Analog: Schneller als Digital, ∞ Genauigkeit, teilweise einfachere Schaltungsrealisierung Vorteile Digital: Störungsanfälligkeit, Speicherung von Signalen, keine Fehlerfortpflanzung Vorlesung 2: Zahlendarstellung Nibble: MSB: LSB: Negative Logik: Binärzahl in Gruppe von 4 Bits, 0110 = Nibble Most significant Bit Least significant Bit High = 0, Low = 1 , Bsp.: Bremse Zug, Reset Binär-System: Oktal-System: Hex-System: Basis: 2 | 20,21,22, ….. | Werte: 0,1 Basis: 8 | 80,81,82, ….. | Werte: 0-7 Bsp.: “110” = 6 Basis: 16 | 160,161, ….. | Werte: 0-9,A-F Bsp.: “1011” = B Binär in Hex: Binär in Oktal: 1 Nibble ergibt eine Hex-Zahl “1001 0010” = 0xA2 3 Bits ergeben eine Oktal-Zahl “100 001” = 41 (Oktal) Bildung: Invertieren und “+1” addieren Einerkomplement: Vorteile: Nachteil: Bildung: Zweierkomplement Anfangszahl: Invertiert: Addition Resultat: Vorzeichen am ersten Bit erkennbar Null kommt zweimal vor Invertieren der Binärzahl: 0101 1010 Vorlesung 3: Schaltalgebra / Logikgatter AND- Funktion: 0110 Dezimal: 6 1001 +1 1010 Dezimal: -6 Anzahl Schaltfunktionen: OR- Funktion: F: Anzahl möglicher Schaltfunktionen n: Anzahl Eingangsvariabeln XOR- Funktion: XNOR- Funktion Beispiel mit 2 Eingängen: NAND / NOR benötigen bei der Realisierung weniger Transitioren als ein AND / OR!! NAND = 4 Transistoren, AND = 6 Transistoren Vorlesung 4: Teil 1 Boolesche Algebra Rechenregeln und Wichtige Verknüpfungen: Rechenbeispiel für Boolesche Algebra: • = AND + = OR = XOR Vorlesung 4: Teil 2 Karnough Diagramm 2 Systematisches Vorgehen zur Herstellung einer logischen Schaltung 1.) Logische Variabeln einfügen Bsp.: Eingang 1 = A 2.) Zuordnung der physikalischen Zustände auf Werte Bsp.: Motor an = “1” 3.) Wahrheitstabelle aus Eingängen bilden Bsp.: Siehe Tabelle rechts 4.) Für jede Eingangskombination entscheiden, ob Ausgang “0”, “1” oder “d” (d = Don’t care) sein muss 5.) KNF bzw. DNF auf Wahrheitstabelle anwenden 6.) Vereinfachung mit Boolescher Algebra oder KV- Diagramm (In der Tabelle rechts sind Schritt 3, 4 und 5 dargestellt) KDNF: KKNF: Kanonisch disjunktive Normalform Kanonisch konjuktive Normalform KV- Diagramm für 2 Eingänge KV- Diagramm für 3 Eingänge KV- Diagramm für 4 Eingänge Vereinfachung mit dem Karnough- Diagramm 1.) Alle Werte von Wahrheitstabelle im KV- Diagram eintragen 2.) Wahl zwischen KNF und DNF | KNF, wenn mehr “1” als “0” 3.) “1” bzw, “0” in 2er, 4er, 8er,… Päckchen zusammenfassen 4.) Durch vergleichen der Eingänge herausfinden, welche Variabeln verschwinden 5.) Resultat aufschreiben Vorlesung 5: Teil 1 Aufbau logischer Gatter Wichtiger Begriff: - Gatteräquivalent: 1 Gatteräquivalent entspricht einem 2-Input NAND Gate = 4 Transistoren - Mass der Komplexität einer Schaltung wird durch die Anzahl der Gatteräquivalent angegeben - Die folgenden Gatter bestehen aus n-Mos-FET bzw. P-Mos-FET (FET = Feldeffekt Transistor) Inverter: NAND- Funktion: NOR- Funktion AND und OR werden aus einem „NAND“ + „Inverter“ hergestellt. Es werden Deshalb 6 Transistoren benötigt Pegelbereich von Logik-Gatter: Vorteile: Solange ein gewisser Pegel nicht unter- bzw. Überschritten wird, haben Störungen keinen Einfluss. Die entsprechenden Pegelwerte können aus dem zugehörigem Datenblatt gelesen werden. Vorlesung 5: Teil 2 Transition Time von Gatter 3 Verzögerungszeit (Propagation delay) Die Verzögerungszeit wird bei 50% vom Ein- und Ausgangssignal gemessen Transition Time Die Transition time ist die Zeit, welche ein Gatter benötigt um zwischen zwei stabilen Zuständen zu wechseln. Gemessen wird von 10% bis 90% des Signals. Abb.: Verzögerungszeit Vorlesung 6: Realisierungsformen Moore’s Law Alle 2 Jahre verdoppelt sich die Anzahl Transistoren auf einem Chip. (Stimmt relativ genau) Beispiel: “4x AND Gatter” Standart Bauteil: - Komopnenten mit Fixer Funktion - Werden in grossen Stückzahlen hergestellt ROM- Typ: - Nichtflüchtiger Speicher - Ideal zur Realisierung von Look-Up Table (LUT) - Einsatzgebiet: Rein kombinatorische Schaltungen, Einfache übersetzung der Wahrheitstablle in LUT - ROM: “Read Only Memorie” - PROM: “Programmable Read Only Memorie” - EPROM: “Eraseable Programmable Read Only Memorie” - EEPROM: “Electrical Eraseable Programmable Read Only Memorie “ PLD- Typen: - PLD: - Einsatzgebiet: - CPLD: - Einsatzgebiet: FPGA-Typ: FPGA: Semi-Custom ASIC - Vorteile: - Nachteile: - Einsatzgebiet: Full-Custom ASCIS - Vorteile: - Nachteile: - Einsatzgebiet: “Programmable Logic Device” || Programmierbarer Baustein, welcher aus einer ANDMatrix(Konjuktion) und einer OR-Matrix(disjunktion) besteht. Eine von beiden Matrizen ist programmierbar. Schaltungen die in DNF vorliegen, einfache “Glue-Logic” prototypen “Complex Programmable Logic Device” || CPLD setzt sich aus vielen kleinen PLD’s zusammen Zur Lösung komlexer, paralleler kombinatorischer AND/OR-Logik, welche viele Ein- und Augänge benötigt. “Field Programmable Gate Array” Mehr Infos in Vorlesung 8 Regelmässig angeordnete Matrixzellen, die durch Verdrahtungskanäle oder über die Zellen hinweg verbunden werden können. Grundstruktur kann in hohen Stückzahlen gefertigt werden. Häufig schlechte Ausnützung, da die Abstufung der Grundstrukturen recht grob. Bei Mittleren Stückzahlen. Zur Kostenreduktion und Ablösung von FPGA nach Markteinführung. Struktur frei wählbar. Ein Chip, welcher spezifisch für den Kunden hergestellt wird. Kaum Grenzen der Machbarkeit, Kunden spezifische Herstellung, Tiefe Stückkosten Hohe NRE Kosten, Sehr langer Designprozess, Viel Expertenwissen erforderlich In Extrembereichen bezüglich Stromverbrauch, Geschwindligkeit, Chipgrösse,… Zusammenfassung aller Realisierungstypen (NRE: Entwicklungskosten) Vorlesung 7: VHDL 4 - VHDL ist eine Hardware- Beschreibungssprache und keine Programmiersprache. - Es gibt zwei Arten um eine Hardware zu beschreiben. 1.) Behavior Es wird das Verhalten der Schaltung beschrieben 2.) Structure Es wird die Struktur der Schaltung beschrieben Was ist VHDL genau? VHDL ist eine beschreibung von elektrischen Verbindungen und Modellierung von elektrischen Phänomenen -Vorteile: Ermöglicht nebenläufige Prozesse - Entity: Schnittstellenbeschreibung - Architecture: Beschreibt Verhalten oder Struktur der Schaltung Vorlesung 8: FPGA Xilinx Spartan 3 Folgende Blöcke beinhaltet die Makrozellen (blau markiert) 1.) Kombinatorische Multiplizierer (18bit x 18 bit) 2.) Block RAM (18k bit SRAM, konfigurierbar) 3.) Digitales Clock Management (DCM, kontrolliert Clockfrequenz und Phasenversatz) 4.) I/O Blöcke: Interface zwischen interner Logik und diversen externen Konfigurationen. Zusätzliches: 2 logic cells = 1 Slice FPGA = Zweidimensionales Array von Logikblöcken, die über Routing Kanäle und Schaltmatrizen miteinander und mit I/O verbunden werden. ASIC FPGA Trend Abb.: Kosten / Stückzahl Diagramm Design Flow: Abb.: Aufbau des Xilinx Spartan 3 Übersicht aller Realisierungsformen Hinweis: VHDL Kurzreferenz nicht vergessen!!