A/D und D/A Wandler

Werbung

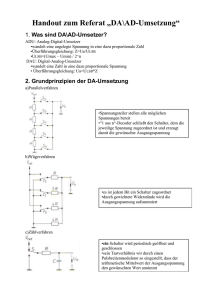

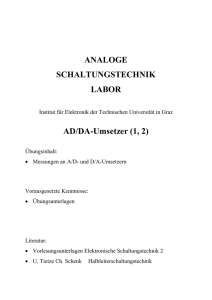

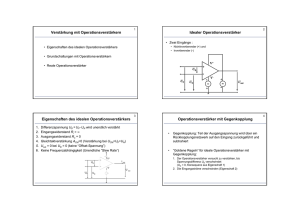

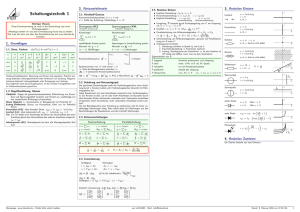

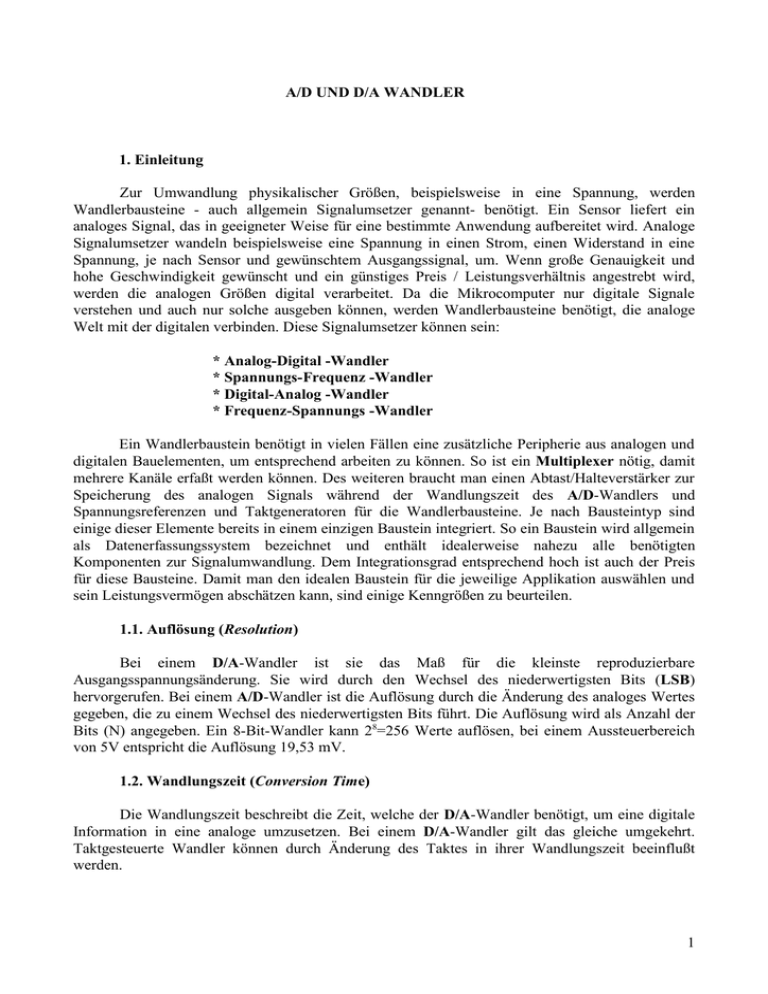

A/D UND D/A WANDLER 1. Einleitung Zur Umwandlung physikalischer Größen, beispielsweise in eine Spannung, werden Wandlerbausteine - auch allgemein Signalumsetzer genannt- benötigt. Ein Sensor liefert ein analoges Signal, das in geeigneter Weise für eine bestimmte Anwendung aufbereitet wird. Analoge Signalumsetzer wandeln beispielsweise eine Spannung in einen Strom, einen Widerstand in eine Spannung, je nach Sensor und gewünschtem Ausgangssignal, um. Wenn große Genauigkeit und hohe Geschwindigkeit gewünscht und ein günstiges Preis / Leistungsverhältnis angestrebt wird, werden die analogen Größen digital verarbeitet. Da die Mikrocomputer nur digitale Signale verstehen und auch nur solche ausgeben können, werden Wandlerbausteine benötigt, die analoge Welt mit der digitalen verbinden. Diese Signalumsetzer können sein: * Analog-Digital -Wandler * Spannungs-Frequenz -Wandler * Digital-Analog -Wandler * Frequenz-Spannungs -Wandler Ein Wandlerbaustein benötigt in vielen Fällen eine zusätzliche Peripherie aus analogen und digitalen Bauelementen, um entsprechend arbeiten zu können. So ist ein Multiplexer nötig, damit mehrere Kanäle erfaßt werden können. Des weiteren braucht man einen Abtast/Halteverstärker zur Speicherung des analogen Signals während der Wandlungszeit des A/D-Wandlers und Spannungsreferenzen und Taktgeneratoren für die Wandlerbausteine. Je nach Bausteintyp sind einige dieser Elemente bereits in einem einzigen Baustein integriert. So ein Baustein wird allgemein als Datenerfassungssystem bezeichnet und enthält idealerweise nahezu alle benötigten Komponenten zur Signalumwandlung. Dem Integrationsgrad entsprechend hoch ist auch der Preis für diese Bausteine. Damit man den idealen Baustein für die jeweilige Applikation auswählen und sein Leistungsvermögen abschätzen kann, sind einige Kenngrößen zu beurteilen. 1.1. Auflösung (Resolution) Bei einem D/A-Wandler ist sie das Maß für die kleinste reproduzierbare Ausgangsspannungsänderung. Sie wird durch den Wechsel des niederwertigsten Bits (LSB) hervorgerufen. Bei einem A/D-Wandler ist die Auflösung durch die Änderung des analoges Wertes gegeben, die zu einem Wechsel des niederwertigsten Bits führt. Die Auflösung wird als Anzahl der Bits (N) angegeben. Ein 8-Bit-Wandler kann 28=256 Werte auflösen, bei einem Aussteuerbereich von 5V entspricht die Auflösung 19,53 mV. 1.2. Wandlungszeit (Conversion Time) Die Wandlungszeit beschreibt die Zeit, welche der D/A-Wandler benötigt, um eine digitale Information in eine analoge umzusetzen. Bei einem D/A-Wandler gilt das gleiche umgekehrt. Taktgesteuerte Wandler können durch Änderung des Taktes in ihrer Wandlungszeit beeinflußt werden. 1 2. D/A Wandler Ein idealer D/A Wandler liefert aus dem binär anliegenden Eingangscode die analoge Ausgangsspannung Ua: U a = U FS (B 1 ⋅2 −1 + B 2 ⋅2 −2 + . . .+ B n ⋅ 2 −n ) B1: MSB (Most Significant Bit); Bn: LSB (Least Significant Bit); FS:Full Scale; Die Bits B1, B2, ... Bn können die Werte "0" und "1" annehmen. Die analoge Ausgangsspannung läßt sich in Stufen des LSB ändern. 1 LSB = UFS 2-n. Die maximale Ausgangsspannung (alle Bits gleich "1") ergibt sich zu: U a max = U FS ( 2n − 1 ) = U FS − 1LSB 2n Beim Anlegen jeder der 8 möglichen digitalen Eingangswerte erhält man die entsprechende analoge Ausgangsgröße, dargestellt durch einen Punkt auf der Übertragungskennlinie. 2.1. Wandlerfehler Abweichungen vom idealen Umsetzer ergeben sich durch Widerstandstoleranzen, der Offsetspannung an den analogen Schalter durch die Temperaturkoeffizienten der genannten Bauelemente und der Referenzspannung. Monotonie (Montonicity) Monotonie ist für einen Wandler gegeben, wenn die Übertragungsfunktion kontinuierlich ansteigt. Eine Änderung des Eingangssignals um 1LSB muß eine Erhöhung des Ausgangssignals zur Folge haben, sonst ist der Wandler nicht monoton. Ein Wandler ist z.B. nicht monoton (Bild 2), wenn bei einer Änderung des Eingangssignals um 1LSB (z.B. 010 auf 011) sich das Ausgangssignal nicht erhöht. 2 Offsetfehler (Offset Error) Der Offsetfehler zeigt sich als Abweichung im Nullpunkt der Übertragungskennlinie. Ist der Offsetfehler nicht auf 0 abgeglichen, tritt ein konstanter, absoluter Fehler für die Übertragungskennlinie auf. Offsetfehler entstehen durch die Übergangswiderstände der Gehäuseanschlüsse, der Bond-Anschlüsse und die Offsetspannung der analogen Schalter (Bild 3). Skalenfaktorfehler (Scale Factor Error oder Gain Error) Die Abweichung wird durch unterschiedliche Verstärkungswerte und die Temperaturkoeffizienten der Bauelemente hervorgerufen und ist die Abweichung zwischen der tatsächlichen und der idealen Übertragungsgeraden. Der Fehler wird meistens in ppm/°C angegeben (Bild 3). Nichtlinearität (Linearity Error) Der Offset- und Skalenfaktorfehler können durch Abgleich eliminiert werden. Nicht abgleichbar ist die Nichtlinearität eines Wandlers. Unter der Nichtlinearität versteht man die maximale Abweichung der idealen Geraden durch den Null- und den Endpunkt. Ist dieser Fehler innerhalb ±1/2 LSB spezifiziert, dann ist die Umsetzung innerhalb des schraffierten Bereichs zulässig. Liegt ein Übertragungspunkt außerhalb, dann erfüllt der Wandler die Spezifikation nicht. Ein Wandler kann bezüglich der Nichtlinearität außerhalb der Spezifikation liegen und erfüllt, wie in Bild 4 gezeigt, trotzdem noch die Anforderung der Monotonie. Differentielle Linearity) Nichtlinearität (Differential Angegeben wird hiermit die Abweichung zweier benachbarter Stufen gegenüber der tatsächlichen Übertragungsfunktion. Die Abweichung wird, wie meistens auch bei der Nichtlinearität, über das LSB spezifiziert (Bild 5). Bei der Darstellung der Übertragungskennlinie wurde von der Annahme ausgegangen, daß der Umsetzer mit nachfolgenden Fehlern behaftet ist: Bit 1 (MSB): -1/2 LSB; Bit 2: +1/4 LSB; Bit 3 (LSB): +1/4 LSB 3 Um den Unterschied zwischen Nichtlinearität und differentieller Nichtlinearität nochmals zu verdeutlichen, sind die Fehler der einzelnen Punkte der Übertragungskennlinie in der folgenden Tabelle festgehalten: Digitaler Code differentielle Nichtlinearität 000 001 010 011 100 101 110 111 +1/4 LSB 0 +1/4 LSB -1 LSB +1/4 LSB 0 +1/4 LSB Nichtlinearität 0 +1/4 LSB +1/4 LSB +1/2 LSB -1/2 LSB -1/4 LSB -1/4 LSB 0 3. A/D Wandler 3.1. Idealer A/D -Umsetzer Unter der Voraussetzung, daß am Eingang eine Unipolare Spannung anliegt und am Ausgang der Binärkode vorliegt, gilt: U FS (B 1 ⋅2 −1 + B 2 ⋅2 −2 + . . .+ B n ⋅2 −n )=U in ± 1 LSB 2 Die Übertragungskennlinie für einen idealen 3 Bit A/D-Umsetzer ist im Bild 6 dargestellt. Die Entscheidungsunsicherheit ist für jede digitale Ausgangsgröße mit Ausnahme der zwei abgeglichenen Werte (000 auf 001 und 110 auf 111) ±1/2 LSB. Nochmals verdeutlicht ist dies für die analoge Eingangsgröße 3/8 FS. Das bedeutet, daß die analoge Eingangsspannung, die zu einem bestimmten digitalen Kode gehört, nur mit einer Unsicherheit von ±1/2 LSB bestimmt werden kann. Diese Tatsache wird als Quantisierungsfehler 4 bezeichnet. Der Quantisierungsfehler ist kein echter Fehler, sondern er ist durch die Bandbreite des digitalen Kodes bestimmt. 3.2. Verfahren der Analog-Digital-Wandlung 3.2.1. Der Parallel- oder Flashwandler Das Prinzip werde anhand der Messung der unbekannten Länge X einer Latte erläutert, wobei der kleinste Quantisierungsschritt den normierten Wert q=1 habe. Auf einem Maßstab der Länge mq sind alle Werte gleichzeitig vorhanden und man liest in einem Meßschritt den nächstliegenden vollen Wert ab. Es genügt also i=1 Vergleichsschritt, man benötigt aber, was für die elektrische Realisierung von Wichtigkeit ist, insgesamt mindestens (m-1) Vergleichsnormale im Abstand q=1 und hat gleichzeitig den Vergleich mit allen möglichen Werten vorzunehmen, ein erheblicher Aufwand. Da eine Messung zur Bildung aller Stellen des Codewortes ausreicht, ist im angelsächsischen Sprachraum auch die Bezeichnung "word-at-a-time" für das Verfahren üblich. Parallelumsetzer mit Spannungsvergleich Ein elektrisches "Lineal" mit linear abgestuften Vergleichswerten im Abstand einer Quantisierungsstufe kann man sich durch eine Kette von gleichen Widerständen R verschaffen, welche an eine Refferenzspannung UREF angeschlossen sind und somit vom gleichen Strom durchflossen werden. Wie in Bild 7 gezeigt, ist der Vergleichseingang einer Kette von Komparatoren K1 bis Km-1 an die Abgriffe zwischen den Widerständen gelegt, die anderen Eingänge sind parallel geschaltet und über einen Trennverstärker mit der unbekannten Spannung Ux verbunden. Die Ausgänge der Komparatoren, deren Vergleichsspannung am Abgriff der Widerstandskette kleiner ist als die zumessende Spannung, zeigen eine logische "1", alle anderen eine "0". Zu den durch die Abtastimpulse gegebenen Zeiten werden diese Werte über die am Ausgang der Komparatoren angeschlossen "UND"-Gatter in die Flip-Flops übernommen und von der darauf 5 folgenden Dekodierlogik auf den gewünschten Code umsetzt. Beim Dualcode ist die Zahl der Stellen n=1. Der Aufwand zeigt sich in der großen Zahl der notwendigen Komparatoren, Gatter und Speicherstufen. Bei großer Stufenzahl wachsen außerdem die Anforderungen an den Verstärker, der sowohl statisch als auch dynamisch die parallelen Eingänge der Komparatoren zu speisen hat, wie auch an die Komparatoren, die bei gegebenem Aussteuerbereich eine immer größere Empfindlichkeit aufweisen müssen, bzw. umgekehrt bei gegebener Empfindlichkeit einen größeren Hub des Signals erforderlich machen und in Verbindung damit auch entsprechende hohe Gleichtaktaussteuerbarkeit besitzen müssen. Wird der Umsetzer mit davorgeschaltetem Abtasthalteglied betrieben, so ist der prinzipielle Fehler des Parallelverfahrens durch die monoton ansteigenden Vergleichsspannungen der Widerstandskette rein statisch vermieden, dynamisch muß eine genügend große Verzögerung zwischen der Entnahme der Signalstichprobe durch das Abtasthalteglied und der Übernahme der Komparatorausgangszustände in die Speicherstufen sein, damit die Einstellung aller Komparatoren mit Sicherheit beendet ist. Wird die Schaltung ohne analoges Abtasthalteglied vor dem Verstärker betrieben und die Abtastung des Signals über den Abtatsimpuls an den UND-Gattern vorgenommen, so sind besondere Vorkehrungen zu treffen, um Fehler durch die unterschiedliche Einstellzeit der Komparatoren zu vermeiden. 3.2.2. Das Wägeverfahren (Sukzessive Approximation) Im Prinzip besteht ein A/D -Wandler in der Praxis aus einem D/A-Wandler und einigen Zusatzfunktionen. Hier im Fall der schrittweisen Approximation benötigt man zusätzlich zum D/AUmsetzer einen Komparator, etwas Logik und ein Register. Am Ausgang (Bild 8) des D/AUmsetzers steht in Abhängigkeit der anliegenden Information die Spannung Uout. Dieser Wert wird an den Eingang des Komparators gegeben und mit der analogen Eingangsspannung Uin = Uout., dann stoppt der Komparator den fest programmierten Ablauf der Logik. Bei der schrittweisen Annäherung beginnt man mit der höchsten Stelle (MSB)-dieses Bit 1 wird dann an den D/AUmsetzer angelegt. Damit erhält man am Ausgang des D/A-Umsetzers, mit der Annahme: Uin = (3/8)FS U out = U ref ⋅ 2 − 2 Dieser Wert wird am Komparator mit Uin verglichen; Uin > Uout. damit bleibt Bit 2 im Register usw. bis der gesuchte Endwert 011 nach drei Schritten erreicht ist und zur Weiterverarbeitung zur Verfügung steht. Der Ablauf für einen 3 Bit A/D-Wandler nach der sukzessiven Approximation ist im Detail für eine Eingangsspannung Uin = (3/8)FS im Bild 9 dargestellt. 6 3.2.3. Das Nachlaufverfahren (Tracking Converter) Der Fenster-Komparator (Bild 10) vergleicht die analoge Eingangsspannung UIn mit der analogen Ausgangsspannung Uout des D/A-Umsetzers. Ist Uin mindestens 1/2 LSB größer als Uout, läuft der Zähler mit der Taktfrequenz in Vorwärtsrichtung. Die analoge Größe Uout erhöht sich entsprechend der einlaufenden Impulse. Jeder anlaufende Impuls erzeugt eine Spannungserhöhung von Uout um 1 LSB. Es kommt zum Zählerstillstand, wenn Uin = Uout ist. Der Zählerstand entspricht dem gesuchten digitalen Wert. Eine Abweichung zwischen Uin und Uout um 1/2 LSB wird vom Fenster-Komparator registriert, der den Zähler aktiviert (+1/2 LSB in Vorwärtsrichtung , -1/2 in Rückwärtsrichtung ). Den Zusammenhang zwischen der analogen Eingangsspannung und des digitalen Ausgangs zeigt Bild 11. Nimmt man an, daß die Taktfrequenz 1 MHz ist, dann dauert ein Schritt 1 µs. Nach 4 µs hat hier der Wandler die analoge Eingangsgröße FS(1/2) in den digitalen Kode 100 umgesetzt; dabei wurde vorausgesetzt, daß am Ausgang 000 anlag. 3.2.4. Das Stufenumsetzverfahren Beim Stufenumsetzverfahren handelt es sich um eine vereinfachte Version des Nachlaufsverfahrens. Liegt die Taktfrequenz an und ist der Startbefehl zur Umsetzung des Analogsignals gegeben, dann läuft der Vorgang wie folgt ab (Bild 12): Die Taktfrequenz wird vom Zähler gezählt und liegt im Binärkode am Eingang des D/A-Umsetzers an. Die Spannung Uout steigt solange an, bis der Wert von Uout gleich der Analogspannung Uin ist. Zu diesem Zeitpunkt ändert der Komparator seinen Zustand. Dies hat zur Folge, daß weitere Taktimpulse nicht mehr an den Zähler gegeben werden. Die am Ausgang des Zählers vorliegende digitale Information entspricht der Analogspannung Uin. Soll der Vorgang von neuem ablaufen, so wird über den 7 Resetimpuls der Zähler auf Null gesetzt und die Umsetzung kann von neuem beginnen. Ebenso wie D/A-Wandler sind auch A/D-Wandler mit Fehler behaftet. Da die meisten A/D-Umsetzer einen D/A-Umsetzer als Referenz verwenden, sind zum großen Teil auch die Fehlerquellen dieselben. 3.2. Der Spannungs-Frequenz-Umsetzer Der Spannungs-Frequenz-Umsetzer (u/f - Umsetzer) hat als Eingangsgröße die zu messende Spannung und eine ihr proportionale Frequenz als Ausgangsgröße. Beim Erreichen von 0 V am Ausgang des Integrators (Bild 13), der mit dem Plus-Eingang des Komparators verbunden ist, löst der Komparator das Monoflop aus. Das Monoflop hat für eine konstante Zeit logisch 1 am Ausgang. Während dieser konstanten Impulsdauer T1 wird eine negative Referenzspannung -Uref am Eingang des Integrators über R zugeschaltet, wobei sich der Kondensator auf eine positive Spannung U1 auflädt. Die Ausgangsspannung des Integrators beträgt am Ende der Impulsdauer T1. U1 = − 1 C ∫ (i T1 0 1 + i2 ) dt = 1 U ref U ⋅ T1 − M ⋅ T1 C R1 R2 Anschließend sinkt UC bis auf 0 V, da über UM integriert wird. 4. Versuchsdurchführung Zur Verfügung steht eine Versuchsschaltung mit 3 Wandler. 8 4.1. D/A-Wandler Typ DAC 08 (ein 8-bit-Wandler). Fühlen Sie die folgende Tabelle ein: N N (BCD) (Dezimal) Nm (binär) b7 b6 b5 b4 b3 Um [V] b2 b1 ε [%] Ub [V] b0 64 32 wobei: ε = ((Uout m - Uout b )/Uout max)100 [%]; Uout= (Uref /255)N; Uref = 2 V; Hier ist N die Binäreingangscode 4.2. A/D -Wandler nach dem Wägeverfahren. Fühlen Sie die folgende Tabelle ein! U in (V) Nm (binär) b7 b6 b5 b4 b3 b2 Nm (dezimal) b1 Nb (dezimal) ε[%] b0 1 2 ... wobei: ε = ((Nm - Nb )/255)100 [%]; Nb=U in/K; K = U in max/255 [V/Bit] 4.3. A/D -Wandler nach dem Nachlaufverfahren. Fühlen Sie die folgende Tabelle ein! U in (V) Nm (binär) b7 b6 b5 b4 b3 b2 Nm (dezimal) b1 Nb (dezimal) ε[%] b0 4 2 ... wobei: ε = ((Nm - Nb )/255)100 [%] K = U in,max/(255/2); Uref = 10 V Nb =128 - (U in/K) 4.4. Oszillographieren Sie die Ausgangssignale für einen u/f Umsetzer und dann fühlen Sie die folgende Tabelle ein: Uxm V 1 ... fxm kHz fxb kHz εN % wobei: εN = ((fxm - fxb)/10)100 [%]; fxb = (Uxm /K); K= (Uxmax /fxmax) [V/Hz] 9