Folien

Werbung

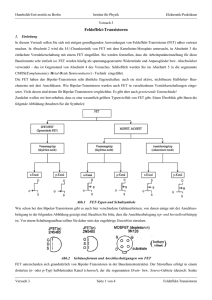

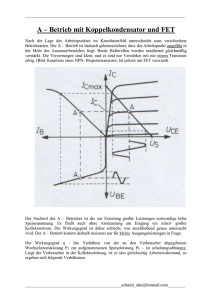

Transistor FET © Roland Küng, 2010 1 Transistor: FET • Im Gegensatz zu den stromgesteuerten Bipolartransistoren sind Feldeffekttransistoren spannungsgesteuerte Schaltungselemente. • Die Steuerung erfolgt über die Gate-Source-Spannung, welche zur Regulation des Kanalquerschnittes bzw. der Ladungsträgerdichte dient, um so die Stärke eines elektrischen Stromes zu schalten oder zu steuern. Der FET verfügt über drei Anschlüsse: Source (engl. für „Zufluss“, „Quelle“) Gate (engl. für „Tor“, „Gatter“) Drain (engl. für „Senke“, „Abfluss“) 2 MOS FET P-Channel Enhanced Depletion N-Channel Bulk Einfache Herstellung: ▪ Miniaturisierung Prozessoren, Logik ▪ Grosse Geometrien Leistungselektronik 3 MOS FET Alternative Symbole in Schemas Norm …… Distinguish S-D…… Simplified 4 MOSFET Operation • • • • • Mit VGS > 0 werden die Löcher im p-Substrat weggestossen es entsteht eine Verarmung an freien Ladungsträgern Gleichzeitig werden Elektronen aus Source und Drain vom positiven Gate angezogen. Je höher VGS desto mehr Elektronen werden angereichert es entsteht ein leitender n-Kanal FET heisst deshalb Enhancement N-Channel MOSFET FET wird auch als selbstsperrend bezeichnet: Bei VGS = 0 fliesst kein Strom: iD = 0 5 MOSFET Operation Verhält sich wie ein Spannungs-gesteuerter Widerstand • Mit VGS > 0 wird ein n-Kanal unter dem Gate induziert dessen Widerstand rDS abhängig von VGS ist, solange die angelegte Spannung VDS klein ist . • Es fliesst ein Strom iD 6 MOSFET Operation Widerstand vGS>Vt Verstärker • Wird VDS bei fixem VGS erhöht, so flacht die Stromzunahme ab und bleibt über grossen Bereich von VDS konstant. • Grund: n-Kanal verformt sich trapezartig und erreicht eine minimale Dicke am Drain. Der Ausgangswiderstand wird hoch und bleibt konstant Verhält sich wie spannungsgesteuerte Stromquelle • 2 Kennlinienbereiche: (Triode, Linear oder Ohmic Region) und (Saturation Region) 7 Enh. N-MOSFET Kennlinie Regionengrenze bei VGD = Vt Für Saturation Region ID(on) VGS(th) • Grenzspannung Vt oder Vth heisst Threshold Voltage • Ist VGS ≤ Vt so ist der FET ausgeschaltet: Cutoff Region 8 • VGS –Vt heisst auch Excess Voltage MOSFET Kennlinie Verstärker Für FET betrieben in Saturation Region gilt iD = K( v GS − Vt )2 Für Saturation Region ID(on) Bsp.: Ein FET habe Vt = 1 V. Im Datenblatt stehe für VGS = 10 V sei ID(on) = 500 mA (vgl. 2N 7002) Gesucht: K und ID für VGS = 5 V Bestätige: K = 6.12 mA/V2 , ID = 99 mA vgl. beim BJT gilt: iC = βiB VGS(th) 9 Datenblatt FET 10 Regions-Grenze Enhancement NMOS Threshold > VS Betrieb: VGS muss min. Vt betragen Saturation: VD darf max. Vt unter VG sein 3 Grenze 4 2 1 Lernprogramm: http://olli.informatik.uni-oldenburg.de/weTEiS/weteis/transistor2.htm 11 Depletion NMOS FET • Aufbau wie Enhancement FET aber ein leitender N-Kanal wird durch Dotierung bereits eingebaut. FET leitet bereits bei VGS = 0 selbstleitend • Um den FET abzustellen muss eine negative Spannung VGS ≤ Vt anliegen Der Kanal verarmt N-Channel Enhancement selbstsperrend N-Channel Depletion selbstleitend 12 Depletion NMOS FET Kennlinie • FET leitet bereits bei VGS = 0 den Strom IDSS selbstleitend • Um den FET abzustellen muss eine negative Spannung VGS ≤ Vt anliegen Für Saturation Region 13 Regions-Grenze Depletion NMOS Threshold < VS Betrieb: VGS muss min. Vt betragen Saturation: VD muss min. |Vt | über VG sein Grenze 4 3 1 2 Lernprogramm: http://olli.informatik.uni-oldenburg.de/weTEiS/weteis/transistor4.htm 14 PMOS FET • Dasselbe gibt es alles auch mit PMOS! P- und N- Schichten tauschen • P-Kanal zwischen Source und Drain wird genutzt. • VDS muss negativ sein, (vgl. pnp Transistor) Simplified P Channel Enhancement Simplified P Channel Depletion 15 Ansteuerung aller MOS FET Vergleich der 4 MOSFET Typen bezüglich Ansteuerkennlinie 16 Junction FET (N-Kanal) 17 N-Channel JFET • JFET ist selbstleitend: Bei VGS = 0 fliesst IDSS • Wird vGS negativ gemacht, so baut sich eine Sperrschicht in der pn Diode auf • Kanal kann abgewürgt werden durch Spannung VGS ≤ VP: (engl. Pinch off) • vGS darf nicht positiv werden, da sonst die pn Diode leitet 18 N-Channel JFET IDSS: Max. Current, Saturation Current ID = IDSS 2 ( V − V ) GS p Vp2 VGS(V) Auch mit VP für Pinchoff Spannung bezeichnet Achtung: VGS darf + 0.3 V nicht übersteigen sonst leitet die PN-Diode GS 19 P-Channel JFET P-Kanal JFET: Einfach Speisung negieren: Polarität für VDS, VGS vertauschen IDSS ID = 2 ( VGS − Vp )2 Vp Achtung: VGS darf - 0.3 V nicht unterschreiten sonst leitet die PN-Diode SG 20 N-Kanal JFET 21 Feldeffekt Transistor FET MIS = Metall-Insulator-Semiconductor NIG = Non Insulating Gate 22 without quad. term ohmic resistor 23 Verstärker NMOS FET Unterschiede zu BJT: • id durch Spannung vgs gesteuert statt Strom ib • Steuerkennline ist quadratisch statt exponentiell weniger Verstärkung 24 Steuerbarer Widerstand Schalter 1/rDS am Bsp. N-JFET Q1 1/RD 25 FET Gleichungen Vereinfachung: Idealer Ausgangswiderstand (VA = ∞) Ideal isolierendes Gate: IG = 0 Grenze: iD = K( v GS − Vt ) 2 v GS = v DS − Vt iD = 2 ⋅ K( v GS − Vt )v DS rDS = v DS 1 = iD 2 ⋅ K( v GS − V26 t) FET Arbeitspunkt Verstärker I Datenblatt: K, Vt gegeben (K aus Punktepaar ID,VGS berechnen) iD = K( v GS − Vt )2 Bsp. Depletion NMOS, d.h. Vt negativ : Einfachste Form IG = 0 VGS = 0 RG typ. MΩ ID = K Vt2 VDS > VGS – Vt = -Vt (Wahl) RD = (VDD – VDS) / ID Nachteil: kein Freiheitsgrad für Wahl ID 27 FET Arbeitspunkt Verstärker II Datenblatt: K, Vt gegeben (K aus Punktepaar ID,VGS berechnen) iD = K( v GS − Vt )2 Bsp Enhancement NMOS, Vt positiv : Gate Spannung mit Spannungsteiler IG = 0 VG = VDD R2 R1 + R 2 ID = K (VGS – Vt)2 = K (VG – Vt)2 VDS > VGS – Vt = VG - Vt (Wahl) RD = (VDD- VDS) / ID Nachteil: ID hängt stark von Vt ab 28 Bsp. FET Arbeitspunkt Verstärker iD = K( v GS − Vt )2 Bsp Enhancement NMOS, Vt positiv : K = 1 mA/V2 Vt = 3 V, VDD = 15 V ID = K (VGS – Vt)2 = 16 mA Vorgabe ID ID = 16 mA VGS = VG = ID + Vt = 7 V K VDS > VGS – Vt = 4 V Wahl: 7 V RD = (15-7) / 16m = 500 Ω R1 = 800 k und R2 = 700 k Nachteil: ID hängt stark von Vt ab: Ist Vt = 6 V ID = K*(7-6)2 = 1 mA 29 FET Arbeitspunkt Verstärker III iD = K( v GS − Vt )2 Bsp Enh. N-MOS: Datenblatt: - K, Vt gegeben - K aus Punktepaar ID,VGS berechnen Gate Spannung mit Spannungsteiler, Source-Feedback durch RS: ID weniger abhängig von FET IG = 0 VG = VDD R2 R1 + R 2 z.B. RS und ID wählen ID = K (VGS – Vt)2 = K (VG – IDRS – Vt)2 VDS > VGS – Vt = VG – IDRS – Vt oder VD > VGS – Vt + VS = VG – Vt RD = (VDD - VD) / ID (Solver) ( Wahl VDS) Beachte ! VDS = VD - VS 30 Bsp. FET Arbeitspunkt Verstärker Datenblatt: K = 2.5 mA/V2, Vt = 2 V, Wahl ID = 10 mA, VDS = 4 V, VDD = 12 V RS = 300 Ω, R1 = 500 kΩ, VGS > Vt iD = K( v GS − Vt )2 VG = VDD R2 R1 + R 2 FET Typ? VS = ? VGS = ? VG =? VD = ? RD = ? R2 = ? Check VDS > VGS - Vt Lösung: 3 V, 4 V, 7 V, 7 V, 500, 700 k 4 V > 2 V ok 31 Bsp. FET Arbeitspunkt Verstärker Datenblatt: K = 0.5 mA/V2, Vt = 1 V gegeben Enh. NMOS iD = K( v GS − Vt )2 *Hilfreich: Ströme in mA und Widerstände in kΩ VG ID VD VDS check 32 L: FET Arbeitspunkt Verstärker Datenblatt: K = 0.5 mA/V2, Vt = 1 V gegeben * ID = 0.5 (5 – 6ID – 1)2 Solver: ID = 0.5 mA Vs = 3 V VD= 7 V Check Saturation Region: VDS > VGS - Vt *Hilfreich: Ströme in mA und Widerstände in kΩ 33 FET Arbeitspunkt Synthese N-Channel 1. Max. Amplitude vo des Ausgangsignal wählen 2. VDD und ID wählen 3. VGS – Vt berechnen für ID VGS = VG - VS 4. Wähle VDS = vo + (VGS - Vt) 5. Wähle VS = (VDD – VDS) / 2 6. Aus VG Gate Spannungsteiler berechnen 7. RS = VS/ID 8. VRD = VRS 9. Kontrolle VRD > vo 10. Eventuell VDD Speisung erhöhen VDD (VDD-VDS)/2 VDS= vo+ (VGS-Vt) VGS (VDD-VDS)/2 34 FET und ESD 35 Zusammenfassung 2 Technologien: MOS und Junction FET 2 Typen MOS: Enhancement (selbstsperrend) und Depletion (selbstleitend) Je N-Channel und P-Channel Typ verfügbar Für P einfach Betriebsspannung mit umgekehrtem Vorzeichen (VDS,VGS) Steuerung des Drain-Stroms durch die Gate-Source Spannung Kennlinie quadratisch Triode- und Saturation-Region für Schalter- bzw. Verstärkerbetrieb Spezifikation durch Spannung Vt (Threshold) bzw. VP (Pinch off) und K Alternativ: K Berechnen aus Punktepaar ID/VGS Für Arbeitspunktberechung Verstärker FET Tabelle und vereinfachte Formel i D = K ( v GS − Vt ) 2 benutzen. IG = 0 Analyse: Hypothesenmethode. Berechnen Spannungen und Ströme. Prüfen mit Bedingung gemäss FET Tabelle 36 Labor MIC Vorverstärker Verstärker für ID = 20 mA, FET BS170, Vt = 1.7 V, K = 40 mA/V2, VDD = 15 V Berechnen: Bauelemente, Wahl VDS = VRD, RS = 220 Ω, (R1 + R2) = 150 kΩ Aufbauen: und Arbeitspunkt messen und dokumentieren, ev. Verbesserung Arbeitspunkt durch Anpassung R2 (FET Streuung) Experimente: D und G getrennt speisen, Rs = 0 ▪ VGS = 3 V, und via VDD VDS variieren 0V – 6 V: Kennlinien Ast ID (VDS) messen ▪ VDD = 15 V und VGS variieren 0 V – 3.3 V: ID(VGS) und Vt, K bestimmen ▪ Schaltung nach Schema: Verstärkung bestimmen mit 1…10 kHz Signal, 50 mV Sinus C1 = 100 nF C2, C3 = 10 µF Messwiderstand Vout: 22 kΩ f = 1 …10 kHz Vin = 50 mV VGS = 2.4 V VG = 6.8 V VD = 9.7 V RD = 270 R2 = 68 k Av gemessen ca. 16 37 Enh. N-MOSFET Kennlinie Regionengrenze bei VGD = Vt Für Saturation Region ID(on) VGS(th) • Grenzspannung Vt oder Vth heisst Threshold Voltage • Ist VGS ≤ Vt so ist der FET ausgeschaltet: Cutoff Region 38 • VGS –Vt heisst auch Excess Voltage

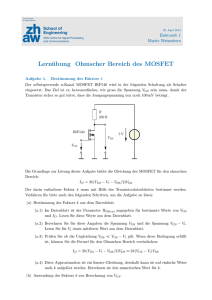

![(Poster SETAC 2010) [ PDF 0.2 MB ]](http://s1.studylibde.com/store/data/001524199_1-1d130fdd978bf8f5901792a5acb5c314-300x300.png)