Übung Integrierte Schaltungen - Mixed Signal Circuit Design (MSC)

Werbung

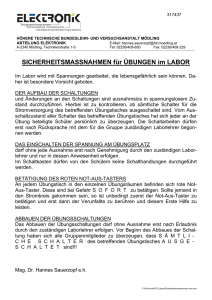

Übung Integrierte Schaltungen 7. Übung: Latch und Register, Logikgatter Dr. Norman Wolf Organisatorisches • Termine: 01.11.2013 15.11.2013 29.11.2013 13.12.2013 10.01.2014 24.01.2014 14.02.2014 • Klausurvorbereitungsstunde: Fr. 28.02.2014 – Raum siehe Internet • http://www.meis.tu-berlin.de/menue/studium_und_lehre/ lehrangebot_ws/is_ue/ • [email protected] Dr. Norman Wolf Aufgabe 1: Latch / Register • Ein Latch oder ein Register haben die Eigenschaft, Informationen in Form von Ladung zu speichern. Bei dynamischen im Gegensatz zu statischen Schaltungen können die Information nur kurzzeitig gespeichert werden. Aufgabe: a) b) c) Um welche Art Latch handelt es sich im rechten Bild? Zeichnen Sie für dieses Latch das Transistorschaltbild! Entwerfen Sie ein Register unter Verwendung des gezeigten Latches! Hinweis: Zeichnen Sie das Schaltbild mit Gatter- und Invertersymbolen. d) e) Entwickeln Sie das Zeitverlaufsdiagramm (Timing Diagramm) (auch der internen Signale) unter Berücksichtigung der Verzögerungen innerhalb des Registers bei einem Datenwechsel mittig von CLK=0. Welchen störenden Effekte verursacht die Inverterverzögerung im Taktpfad. Dr. Norman Wolf Latch • Latch in Current-Mode-Logic (CML): Eigenschaft: sehr schnell • Herleitung des statischen Latches: S Q Q R RS-Flipflop D-Latch Dr. Norman Wolf Aufgabe 2: Logikgatter • Für die Entwicklung von Logikgattern muss ein UND-Funktionalität realisiert werden. Mit Hilfe einer Serienschaltung von Transistoren wird diese Funktionalität umgesetzt: Nur wenn alle Transistoren leiten fließ durch die Serienschaltung ein Strom. • Für die Analyse dieser Serienschaltung wird eine Kapazität von UDD mit Hilfe von 3 in Serie geschalteten n-Kanal Transistoren entladen, siehe rechtes Bild Aufgabe: a) b) c) In welchen Arbeitsbereichen befinden sich die Transistoren zu Beginn des Entladevorgangs? Diese Schaltung soll die gleiche Stromergiebigkeit haben wie unter Verwendung nur eines Transistors zum Entladen der Kapazität. Wie groß müssen die Weiten der drei Transistoren im Vergleich zu einem Einzeltransistor gewählt werden. Welche Auswirkungen hat dies auf die treibende Stufe? Wie sehen die Schaltbilder für ein 3fach-NAND Gatter in der NMOS-, Pseudo-NMOS-, CMOS-Logik und als einfaches dynamisches Gatter aus. Zeigen Sie ebenfalls die Schaltbilder dieses Gattertyps für die DCVS und für die differentielle Domino-Logik? Dr. Norman Wolf Dynamische CMOS-Logik • Kaskadierung dynamischer Logik: Z1 Z1 Z2 Z2 A2 CLK Nicht möglich CLK Domino-Logik CLK CLK erweiterte Domino-Logik (Nora-Logik) Dr. Norman Wolf Teilklausur „Integrierte Schaltungen“ Termin: Fr, 28. März 2014 von 10:00 - 12:00 Uhr Raum: EMH 225 Dauer: 75 min Zugelassene Hilfsmittel: Schreibzeug Achtung: Änderung der Prüfungsmodalitäten! – – – – – Die Prüfung wurde zu EINER prüfungsäquivalenten Studienleistung aus "Physik und Technologie der Halbleiterbauelemente" und "Integrierte Schaltungen" zusammengelegt (durch das Prüfungsamt). Die Klausuranmeldung für Bachelor Absolventen muss elektronisch in QISPOS bis zum 25.02.2014 erfolgen. ACHTUNG: Wer sich bei QISPOS anmeldet MUSS definitiv an beiden Teilprüfungsterminen teilnehmen. Die Note wird aus den Ergebnissen beider Teilklausuren (IS, HBL) bestimmt. Für ein Bestehen der Klausur ist es notwendig eine Mindestpunktzahl für jede der einzelnen Lehrveranstaltungen zu erreichen. Für alle anderen Fälle muss eine schriftliche Anmeldung 7 Tage vor der Prüfung für die Teilklausur IS im Raum E 222 (Sekr. E3) erfolgen (Eintrag in die ausliegende Anmeldeliste). Diplomanden tragen sich bitte in die im Raum E 222 (Sekr. E3) ausliegende Anmeldeliste ein. Dr. Norman Wolf Weiterführende Lehrveranstaltungen: • High Frequency Devices and Circuits for Mobile Communications I (Vorlesung) Block-VL: 26.02.2014 - 28.02.2014 – • Integrierte Analog-Schaltungen (Vorlesung) SS 2014 – • "Simulation und Entwurf von analogen integrierten Schaltungen" - Die Teilnehmer entwerfen im Laufe des Projektes eine selbstgewählte oder vorgegebene Analogfunktion. Die Schaltungsentwicklung beginnt mit der Simulation und endet mit dem Layout. Die Schaltungen werden anschließend gefertigt und aufgebaut und stehen zum Messen zur Verfügung. Test Integrierter Schaltungen (Vorlesung) SS 2014 – • In der Lehrveranstaltung wird der Entwurf von integrierter, analoger Schaltungen behandelt. Nach der Signaldarstellung werden die wichtigsten Grundschaltungen, wie Differenzstufe und Operationsverstärker, besprochen. A/D- und D/A-Wandler und Schalterkondensatorfilter gehören ebenfalls zum Stoff der Vorlesung. Analog Chip Projekt (Praktikum) SS 2014 – • "Integrated Analog Circuits for wireless communication" - Architekturen für die Sender- und Empfangsteile von Mobilstationen (Handy, homodyne-hetorodyne, Überabtastung), Rauschpegel, Nichtlinearität, Induktivitäten auf einem IS, Verstärker, Mischer, Filter, VCO. Testprobleme komplexer Schaltungen wie Speicher, Logiknetzwerke - Zufallstest - Fehlermodelle - Fehlersimulation - testfreundlicher Entwurf - Selbsttest - Ausbeutemodelle - Lebensdauertest Test Integrierter Schaltungen (Praktikum) SS 2014 – – – – – Ergänzung und Vertiefung des Vorlesungsstoffes: Messungen an typ. Prozeßmonitoren für Schichtwiderstände, Transistorparameter, Schaltverzögerungszeiten Fehlererkennung mit Signaturregistern Einführung in die Programmierung eines VLSI Testers Aufbau eines Testprogrammes Dr. Norman Wolf Lösung Aufgabe 1 a) Dynamisches positives Latch Information wird nur zeitlich begrenzt gespeichert (CGS Inverter) Datumsübernahme wenn CLK high ist b) Transistorschaltbild des Latches: CLK CLK D c) Q Schaltbild des Registers: Dr. Norman Wolf Lösung Aufgabe 1 d) Zeitverlaufsdiagramm des Registers: e) Beide Transmissiongates gleichzeitig transparent: 1-1-Überlappung: wenn tp,INV3>tp,TG1+tp,INV1+tp,TG2 wird nachfolgendes Datum übernommen Vermeidung: thold muss ausreichend groß gewählt werden. 0-0-Überlappung: wenn tp,INV3>tp,TG1+tp,INV1+tp,TG2 wird D nach Q bei fallender Flanke durchgeschaltet = Fehlfunktion. Vermeidung: tp,INV3<tp,TG1+tp,INV1+tp,TG2 Dr. Norman Wolf Lösung Aufgabe 2 a) UGS1>UT; UGD1=0 : T1 Sättigung UGS2>UT; UGD2>UT : T2 Triode UGS3>UT; UGD3>UT : T3 Triode b) Durch alle Transistoren fließt der gleiche Strom: Dr. Norman Wolf Lösung Aufgabe 2 b) Für gleiche Stromerergiebigkeit im Vergleich zu einem Transistor folgt: also: Die Weite muss entsprechend mit der Anzahl in Serie geschalteter Transistoren multipliziert werden, damit die Stromergiebigkeit gleich bleibt. Dr. Norman Wolf Lösung Aufgabe 2 c) Implementierungsformen für ein 3-fach NAND Pseudo-NMOS NMOS Z CMOS dynamisch Z A A B B C C Dr. Norman Wolf Lösung Aufgabe 2 c) Implementierungsformen für ein 3-fach NAND Differenzielle Domino-Logik DCVS UDD UDD Z Z A B A B C C USS Dr. Norman Wolf