6665.attach - Bombentrichter.de

Werbung

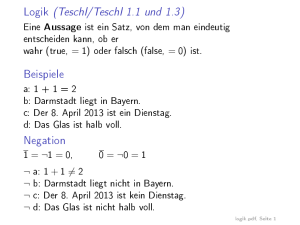

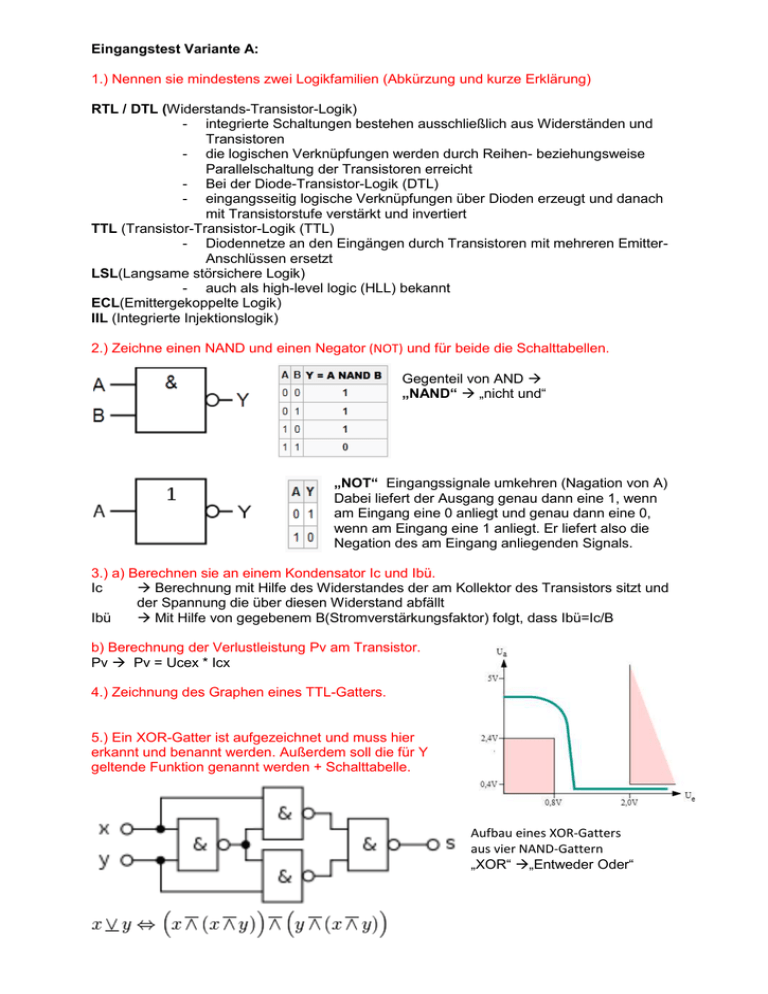

Eingangstest Variante A: 1.) Nennen sie mindestens zwei Logikfamilien (Abkürzung und kurze Erklärung) RTL / DTL (Widerstands-Transistor-Logik) - integrierte Schaltungen bestehen ausschließlich aus Widerständen und Transistoren - die logischen Verknüpfungen werden durch Reihen- beziehungsweise Parallelschaltung der Transistoren erreicht - Bei der Diode-Transistor-Logik (DTL) - eingangsseitig logische Verknüpfungen über Dioden erzeugt und danach mit Transistorstufe verstärkt und invertiert TTL (Transistor-Transistor-Logik (TTL) - Diodennetze an den Eingängen durch Transistoren mit mehreren EmitterAnschlüssen ersetzt LSL(Langsame störsichere Logik) - auch als high-level logic (HLL) bekannt ECL(Emittergekoppelte Logik) IIL (Integrierte Injektionslogik) 2.) Zeichne einen NAND und einen Negator (NOT) und für beide die Schalttabellen. Gegenteil von AND „NAND“ „nicht und“ „NOT“ Eingangssignale umkehren (Nagation von A) Dabei liefert der Ausgang genau dann eine 1, wenn am Eingang eine 0 anliegt und genau dann eine 0, wenn am Eingang eine 1 anliegt. Er liefert also die Negation des am Eingang anliegenden Signals. 3.) a) Berechnen sie an einem Kondensator Ic und Ibü. Ic Berechnung mit Hilfe des Widerstandes der am Kollektor des Transistors sitzt und der Spannung die über diesen Widerstand abfällt Ibü Mit Hilfe von gegebenem B(Stromverstärkungsfaktor) folgt, dass Ibü=Ic/B b) Berechnung der Verlustleistung Pv am Transistor. Pv Pv = Ucex * Icx 4.) Zeichnung des Graphen eines TTL-Gatters. 5.) Ein XOR-Gatter ist aufgezeichnet und muss hier erkannt und benannt werden. Außerdem soll die für Y geltende Funktion genannt werden + Schalttabelle. Aufbau eines XOR-Gatters aus vier NAND-Gattern „XOR“ „Entweder Oder“ Eingangstest Variante B: 1.) Nennen Sie die beiden Theoreme von De Morgan und überprüfen Sie eines davon durch Aufstellen der vollständigen Schaltbelegungstabelle. NICHT (A UND B) = NICHT A ODER NICHT B NICHT (A ODER B) = NICHT A UND NICHT B. 2.) Geben Sie die Schaltbelegungstabelle für die logische Funktion. Wie kann diese Funktion mit NAND- Gattern realisiert werden? 3.) a) BCD 0111 1000 1001 in Dezimalzahl umwandeln 789 b) 51 als BCD Zahl darstellen 0101 0001 4.) Berechnen Sie für den gegebenen Transistorschalter a) den Kollektorstrom ICx und den zugehörigen Basisstrom IBx ICx IBx 16,6mA(Icx) Masche Icx = Uq / Rc 0.166mA(Ibx) B = Icx / Ibx Ib = Ic / B b) wie groß muss der Widerstand Rb gewählt werden, damit zur Erhöhung der Schaltsicherheit der Basisstrom IBx = 3 IBü fließt? zunächst eine Masche für die Spannung über Rb auf, z.B. Urb = Ub - Ubex Dann ohmsches Gesetz für den Widerstand auf Urb = Rb * Ibx gleichsetzen umgestellt Rb = (Ub - Ubex) / Ibx Der Index „x“ bezieht sich auf den EIN- Zustand des Transistorschalters. Der Faktor bei IBü; hier 3; heißt auch Übersteuerungsfaktor! 5.) Gegeben ist folgende Schaltung. Es gilt: Schalter geschlossen Si= 1 bzw High (H) Schalter geöffnet Si= 0 bzw Low (L) Geben Sie die logische Funktion Y für das Leuchten der Lampe an. y = s.3 n (s.1 u s.2) = 1 6.) Erläutern Sie am Beispiel des BCD-codes die Darstellung des Wertes 5 als 4-stelliges Digitalwort (Tetrade). Kennzeichnen Sie MSB und LSB. [0101]bcd = [5] 0101 msb 0101 lsb M: MSB ist immer 1 wenn keine Limitierung vorgegeben ist. Limitierung = zB. 4 stellige BCD Zahl 1 ( = 0001 , also MSB = 0 und LSB =1) LSB ist die 2^0 Stelle! Welche typischen Störungen können diese Darstellung bei der Verarbeitung verfälschen? Bitfehler Eingangstest Variante D: 1.) Zeigen dass NOR und AND mit invertierendem Eingang dieselbe Schaltfunktion besitzen + Schaltbelegungstabelle 2.) Y=(A+B)quer + A*Bquer + Aquer*B bzw. Y=Negiert(AvB) + A v negiert(B) +negiert(A) v B mit De Morgan vereinfachen Ich hab das mal mit einem KV Diagramm vereinfacht und komme auf negiert(Aund B) Schaltung lässt sich daraus mit einem NAND Gatter realisieren Lösung: Y =(A+B)quer + A*Bquer + Aquer*B = Aquer*Bquer + A*Bquer + Aquer*B =Aquer*Bquer + A*Bquer + Aquer*B + Aquer*Bquer (hier einfach mit Aquer*Bquer erweitern, da sich dadurch nichts an der Gleichung ändert) =Aquer*(Bquer+B)+Bquer*(Aquer+A) (Aquer+A) ist immer wahr dadurch kürzt sich das weg = Aquer+Bquer =(A*B)quer ==> NAND alternativ: Y = (A+B)quer + A*Bquer + Aquer*B = Aquer*Bquer + A*Bquer + Aquer*B = (Aquer+ A)*Bquer + Aquer*B X1 = Bquer+(Aquer*B) X2 = (Aquer+Bquer)*(Bquer+B) X3 = Aquer+Bquer = (A*B)quer ==> NAND X1: (Aquer+A) ist immer 1(high) Lösung bei einer "und"- Verknüpfung immer gleich dem anderen Glied (kann man sich auch am Logikplan vorstellen: da wo eine eins bei Y ist wird bei der "und"- Verknüpfung auch im Ergebnis eine Eins herauskommen, da wo eine Null ist eine Null): (X+Xquer)*Y=1*Y=Y So gilt natürlich auch für (X*Xquer)=0 und somit (X*Xquer)+Y=0+Y=Y X2: ausmultipliziert X3: wie bei X1, halt nur mit B 1.) Theorem De Morgan NOR Fkt, und mit NAND realisieren Hintereinander realisiert diese Schaltung die gewünschte NOR Funktion 2.) NAND und Negation (aus nand basteln), Schaltbild zeichnen und Schaltbelegungstabelle zu beiden Sprich einfach einen NAND mit Schalttabelle und eine Negation realisiert durch einen NAND(wobei sich einfach eine Eingangsspannung auf die beiden Eingänge des eines NAND austeilt) mit Schaltungstabelle 3.) y=x1+x2quer Schaltbelegungstabelle OR X1 0 1 0 1 X2 0 0 1 1 X2 (quer) 1 1 0 0 Y 1 1 0 1 4.) Ausgangskennlinienfeld mit einer Arbeitsgerade für eine ohmsche Last gegeben. Wir sollten die 3 Arbeitspunkte der Gerade erläutern. 6.) AND mit NAND-Gattern realisieren 7.) Schaltbelegungstabelle aufstellen Einige Beispiele für Realisierungen mit NAND-Gattern: