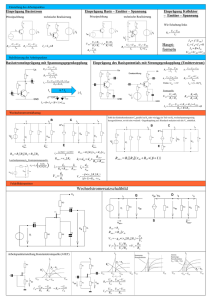

Unipolare Transistoren

Werbung

8.

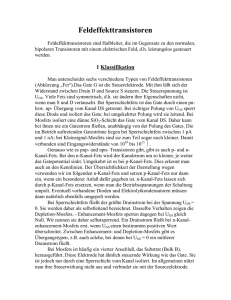

Unipolare Transistoren

Bei Feldeffekttransistoren (FET) wird der Strom nur von den Ladungsträgern getragen, die in

dem betreffenden Kristallgebiet in der Mehrzahl vorhanden sind (Majoritätsladungsträger). In der

N-Zone sind es die Elektronen und in der P-Zone die Löcher oder Defektelektronen.

8.1 Sperrschicht-Feldeffekttransistoren

Der Sperrschicht-FET wird nach dem Planarverfahren hergestellt. Bei N-Kanaltypen wird in

mehreren Herstellungsschritten in das P-leitende Substrat der N-leitende Kanal eingebettet. Die

Enden des Kanals erhalten hochdotierte N+-Zonen (Sourcezone und Drainzone). Die mit diesen

Halbleiterzonen sperrschichtfrei verbundenen Metallanschlüsse werden als Source- und Drainelektrode bezeichnet.

Oberhalb des Kristalls liegt

DrainGate mit P-Substrat

Sourcezwischen der Source- und

elektrode

verbunden

elektrode

Drainzone eine hoch dotierte P-leitende KristallSiO2

zone, die mit dem P-Substrat leitend verbunden ist.

Diese beiderseits des NN+

P+

N+

Kanals liegende P-Zone

bildet zusammen mit dem

Kanalbreite Kanal einen PN-Übergang.

N

Die P-Zone wird mit der

P-Substrat

Steuerelektrode, der Gateelektrode verbunden.

Kristallschnitt eines N-Kanal-Sperrschicht-FET

Drain Wird an den N-leitenden Kanal eine Spannung angelegt, so

Gate

fließt ein Elektronenstrom von S nach D. Die Größe dieses

Elektronenstromes wird bestimmt durch die angelegte

Source Spannung und den Bahnwiderstand des Kristalls.

Schaltzeichen des Sperrschicht-FET

Die N-leitende Kristallstrecke hat positive Spannungswerte (Potentiale) gegenüber jeder P-Zone.

Es bilden sich zwei Sperrschichten (Raumladungszonen) aus. Diese Sperrschichten sind um so

breiter, je größer die in Sperrrichtung wirksame Spannung ist. Die Sperrschichtbreite nimmt also

in Richtung von S nach D zu.

Gerät ein Elektron in eine Sperrschicht, so wird es aus dieser Sperrschicht in Richtung zum

neutralen N-Kristallbereich herausgedrängt. Die Sperrschichten sind für die Elektronen

"verbotene Gebiete".

Bei der Steuerspannung Null besitzt der Kanal seine höchste Leitfähigkeit.

Wird das Potential des Anschlusspunktes G bezogen auf S negativer gemacht, so bedeutet das,

dass die Spannungen in Sperrrichtung größer werden. Je negativer die Spannung UGS, desto

breiter die Sperrschichten, desto geringer der Kanalquerschnitt und desto kleiner der Strom ID.

Der Strom ID wird durch die Spannung UGS nahezu leistungslos gesteuert.

Bei einem bestimmten negativen Spannungswert UGS stoßen die beiden Sperrschichten

zusammen. Der Kanal hat jetzt den Querschnitt Null. Der Transistor ist gesperrt.

G. Schenke, 1.2008

Bauelemente der Elektrotechnik

FB Technik, Abt. E+I 89

Die Spannung UGS muss beim N-Kanal-Sperrschicht-FET immer negativ sein. Bei positiven

Spannungswerten von UGS werden die Sperrschichten abgebaut, und es fließt über die P-Zonen

ein Strom.

D

+ 12 V

n

~ 10 V

n

p

Kraft F

~6V

G

0V

p

p

Elektronenbahn

n

Richtung der elektr.

Feldstärke

vergrößerter Ausschnitt

aus der Sperrschicht

0V

S

Sperrschichten eines Sperrschicht-FET

Grundschaltung

Die drei Grundschaltungen sind die Sourceschaltung (entspricht der Emitterschaltung bei

bipolaren Transistoren), die Drainschaltung (Kollektorschaltung) und die Gateschaltung (Basisschaltung). Die Sourceschaltung ist eine häufig verwendete Grundschaltung mit Feldeffekttransistoren. Die folgenden Kennwerte beziehen sich auf diese Schaltung.

Die Betriebsspannung Ub treibt den Drainstrom ID durch den Arbeitswiderstand RD. Die Größe

des Drainstroms ist abhängig von der Gate-Source-Spannung -UGS. Die Eingangssignalspannung

Ue ändert den Drainstrom ID und damit die Ausgangsspannung Ua.

ID

RD

D

G

S

RG

Ue

Ub

UDS

Der Feldeffekttransistor

entspricht in seiner Arbeitsweise einem annähernd leistungslos steuerbaren Widerstand. Die

Sourceelektrode dient als

Bezugspunkt für die Eingangs- und Ausgangsschaltung. Der Eingangswiderstand ist hochohmig

(106 ... 109 Ω).

Ua

-UGS

Sourceschaltung

G. Schenke, 1.2008

Bauelemente der Elektrotechnik

FB Technik, Abt. E+I 90

Eingangskennlinie

Die Abhängigkeit des Drainstroms ID von der Gate-SourceSpannung UGS (ID = f{UGS})

wird ab der Gate-Source-Abschnürspannung UGS(P), bei der

der Kanal zwischen Drain und

Source praktisch abgeschnürt

wird, in der Eingangskennlinie

dargestellt.

20

∆UDS = 15 V

15

ID / mA

A

10

∆ID

∆UGS

5

Eingangskennlinie eines NKanal-Sperrschicht-FET

(ID = f{UGS} mit UDS als

Parameter)

∆UDS = 5 V

-7

-6

UGS(P)

-5

-4

-3

UGS / V

-2

-1

0

0

Die Steilheit S kennzeichnet das Steuerverhalten des FET. Sie kann der Eingangskennlinie im

Arbeitspunkt A als Tangente entnommen werden.

∆I D

(8.1)

S =

∆U GS

Ausgangskennlinie

Die Ausgangskennlinie

zeigt den Zusammenhang

zwischen Drainstrom ID

und Source-Drain-Spannung UDS mit UGS als

Parameter.

Wird die Drain-SourceSpannung UDS von Null

ausgehend erhöht, steigt

der Drainstrom zunächst

nach dem Ohmschen Gesetz an. Man spricht hier

vom ohmschen Bereich

des FET.

Ausgangskennlinie

eines N-KanalSperrschicht-FET

(ID = f{UDS} mit UGS als

Parameter)

G. Schenke, 1.2008

UGS(P) = -5 V

20

UGS = 0 V

ohmscher

Bereich

Abschnürbereich

15

-1 V

ID / mA

-2 V

10

A

∆UDS

-3 V

UDSsat

5

0

∆ID

-4 V

0

5

Bauelemente der Elektrotechnik

UDS / V

10

15

FB Technik, Abt. E+I 91

Nimmt UDS über die Abschnürgrenze hinaus zu, knickt die Kennlinie bei der Drain-SourceSättigungsspannung UDSsat ab. Im Abschnürbereich steigt der Drainstrom mit der weiteren

Zunahme von UDS nur gering an.

Der differentielle Ausgangswiderstand rds kann der Ausgangskennlinie im Arbeitspunkt A als

Tangente entnommen werden.

∆U DS

rds =

(8.2)

∆I D

Die Verlustleistung Ptot ergibt sich aus dem Produkt von Drain-Source-Spannung UDS und

Drainstrom ID.

Ptot = U DS ⋅ I D

(8.3)

Grenzwerte von Sperrschicht-Feldeffekttransistoren sind:

maximale Drain-Source-Spannung UDSmax,

maximale Gate-Source-Spannung UGSmax,

maximaler Drainstrom IDmax,

maximale Verlustleistung Ptot,

höchste Sperrschichttemperatur ϑj (Tj).

8.2 MOS-Feldeffekttransistoren

MOS-Feldeffekttransistoren (Metal-Oxide-Semiconductor) gehören zu der Gruppe der Isolierschicht-Transistoren oder kurz IG-FET genannt.

Der aktive Teil des MOS-FET besteht aus einem P-Substrat (Kristall). In dieses Substrat werden

zwei N-Zonen eindotiert. Das ganze Kristall erhält eine Abdeckschicht aus Siliziumdioxid (SiO2).

Zwei Fenster für die Anschlüsse von Source und Drain werden ausgespart. Die SiO2-Schicht ist

hochisolierend (1010 ... 1014 Ω) und verhältnismäßig spannungsfest. Auf diese Isolierschicht wird

eine Aluminiumschicht (Al) als Gateelektrode aufgedampft. Das Substrat erhält einen besonderen

Anschluss (Bulk). Dieser Anschluss ist im Allgemeinen direkt mit dem Sourceanschluss

verbunden oder wird aus dem Gehäuse herausgeführt.

UDS

S

G

D

S

G

UGS = 0

B

P-Substrat

D

UGS

ID

N

ID

UDS

l

N

N

B

E

N

P-Substrat

Grundaufbau und Arbeitsweise eines MOS-FET (N-Kanal-Anreicherungstyp)

Bei der Gate-Source-Spannung UGS = 0 besteht keine Leitfähigkeit zwischen der Drain- und

Sourcezone, die angelegte Spannung UDS sperrt jeweils einen der beiden zwischen den N-Zonen

und dem P-Substrat vorhandenen PN-Übergänge.

Wird an die Gateelektrode eine gegenüber dem Substrat positive Spannung gelegt, werden durch

die Wirkung des elektrischen Feldes innerhalb des Substrats Elektronen herausgelöst. Diese

G. Schenke, 1.2008

Bauelemente der Elektrotechnik

FB Technik, Abt. E+I 92

bewegen sich entgegen der Richtung des elektrischen Feldes in den Bereich zwischen Drain- und

Sourcezone und bilden einen N-leitenden Kanal. Bei angelegter Drain-Source-Spannung UDS

fließt der Drainstrom ID über den Kanal.

Mit der Gate-Source-Spannung UGS kann die Leitfähigkeit des Kanals und damit der Drainstrom

ID leistungslos gesteuert werden. Ein Steuerstrom ist praktisch nicht erforderlich. Während des

Schaltvorganges fließt kurzzeitig (rd. 1 µs) ein kapazitiver Umladestrom.

Anreicherungstyp

Bei Gatespannung Null oder bei offenem Gate ist die Strecke von Source nach Drain gesperrt. Da

der Transistor sich bei fehlender Gatespannung selbst sperrt, wird er auch selbstsperrender MOSFET genannt.

Ein leitfähiger Kanal entsteht durch Anreicherung der Zone in der Nähe der SiO2-Schicht (Anreicherungstyp). Die englischen Bezeichnungen sind enhancement-type und normally-off-type.

Verarmungstyp

Bei Gatespannung Null oder bei offenem Gate ist die Strecke von Source nach Drain leitfähig.

Der Kanal erhält eine schwache Dotierung wie Drain und Source. Man nennt Transistoren dieser

Art selbstleitende MOS-FET.

Ein selbstleitender MOS-FET kann sowohl durch negative als auch durch positive Gatespannung

UGS gesteuert werden. Beim N-Kanal-MOS-FET wird bei positiver Gatespannung der Kanal

leitfähiger; bei negativer Gatespannung wird der Kanal hochohmiger.

Da die Steuerung mit negativer Gatespannung häufiger angewendet wird, nennt man Transistoren

dieser Art Verarmungstyp. Die englischen Bezeichnungen sind depletion-type und normally-ontype.

D

G

S

D

D

G

N- Kanal

S

G

S

N- Kanal

P- Kanal

Schaltzeichen des Anreicherungs-IG-FET

D

G

S

P- Kanal

Schaltzeichen des Verarmungs-IG-FET

Schaltungen zur Arbeitspunktstabilisierung

R1

Die Arbeitspunktstabilisierung

bei FET erfolgt durch Spannungs- oder Stromgegenkopplung. Schaltungen mit Stromgegenkopplung entsprechen der

Arbeitspunkteinstellung bei bipolaren Transistoren.

RD

ID

Ck

UDS

Ub

Schaltung zur

Arbeitspunktstabilisierung

beim N-KanalAnreicherungs-IG-FET mit

Stromgegenkopplung

UGS

R2 UG0

RS

CS

(0)

G. Schenke, 1.2008

Bauelemente der Elektrotechnik

FB Technik, Abt. E+I 93