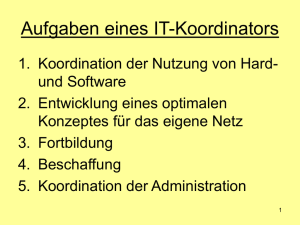

Virtual Interface Architecture

Werbung

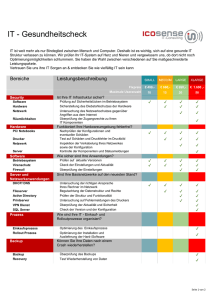

Current Implementations of the Virtual Interface Architecture (VIA) Seminarvortrag von Thorsten Backhaus im Rahmen des Seminars des Lehrstuhls Rechnerarchitektur der Universität Mannheim im Wintersemester 2003/2004 Inhalt • Vernetzung im Allgemeinen • Userlevel Netzwerke abgegrenzt zur naiven Vernetzung • Interessantes aus der VIA Spezifikation • Zusammenfassung VIA • Verschiedene Implementierungen im Vergleich • Zusammenfassung Implementierungen 2 Vernetzung im Allgemeinen • Grundlage jeglicher Kommunikation • Verschiedene Ausprägungen – – – – Topologie Zugriffsverfahren LAN / SAN / WAN “typische Netzwerke”, “User Level Netzwerke” 3 Vernetzung im Allgemeinen • „Sprung“ ins Betriebssystem nötig um eine Anforderung zu bearbeiten. • „Unterbrechung“ des sich momentan auf dem Prozessor befindlichen Prozesses • Kostet Zeit Möglichkeit suchen diesen „Sprung“ ins Betriebssystem zu umgehen. 4 Stack Time vs. Hardware Execution Time [8] 5 Relativ zur Prozessorgeschwindigkeit Userlevel Netzwerke • User Prozess kann direkt auf einen Kommunikations-Endpunkt zugreifen • Multiplexing und Demultiplexing wird direkt vom NIC übernommen – „Intelligentere“, mächtigere NICs notwendig • Nur noch bei „grundlegenden“ Operationen Sprung ins Betriebssystem notwendig 6 VIA – ein Userlevel Netzwerk • Idee: Vereinheitlichung eines Userlevel Standards • Compaq, Intel & Microsoft arbeiteten Standard aus • Definition schon relativ alt: Ende 1997 7 VI Consumer & Provider • Der VI Consumer ist derjenige Teil des Systems, der kommunizieren möchte. – Besteht also aus Anwendung und einer „VI Provider Library“ • Der VI Provider ist derjenige Teil des Systems, der Kommunikation ermöglicht. – Also die Netzwerkkarte und ein “Kernel Agent” 8 VI Architecture [5] 9 Das “Virtual Interface” [5] 10 Queues • Jedes VI: Send und Receive Queue – Darin stehen Deskriptoren • Eine Completion Queue für mehrere VI‘s auf einem Knoten. – Sammeln mehrerer “Completion-Ereignisse” möglich – Damit kann Polling und Interrupting auf ein Minimum reduziert werden. 11 Der Deskriptor • Eine Datenstruktur, die den Ort und die Größe eines Daten Puffers enthält und die Anweisung, was mit diesen Daten geschehen soll. • Setzen von „Completion“-Bits um Erfolg / Misserfolg anzuzeigen. • Komplett asynchrone Kommunikation • Polling / Interrupts 12 „Doorbells“ • Jedes VI hat eine send- und eine receiveDoorbell – An dieser wird „geläutet“, wenn Anwendung neuen Deskriptor in eine Queue geschrieben hat.[5] – Speicher auf NIC wird in User Space gemapped [1] • u.U. oft „pollen“ um alle Doorbells zu überprüfen – Über Kernel gehen / zentralisierter Ansatz [1] 13 Kernel Agent • Stellt Schnittstelle zum Betriebssystem dar • Speicher muss beim Betriebssystem angefordert werden. (sehr teuer) – Das erledigt der KernelAgent. – Da DMA Transfers erwünscht sind darf die Seite im Speicher nicht „ausgelagert“ werden. • Übernimmt alle Aufgaben, die die Hardware nicht übernehmen kann 14 Speicherverwaltung • Deskriptoren: virtuelle Adressierung, Periph. Bus: physikalische Adressierung – Betriebssystem erledigt die Adressumsetzung mit einem Kernel Trap – NIC erledigt Adressumsetzung • Tabelle im Hauptspeicher • Bestenfalls hat NIC eigenen Speicher 15 Data Transfer Modes [5] • • • • Send Receive RDMA Write RDMA Read (optional) 16 Ebenen der Verlaesslichkeit [5] 17 Beispiel fuer eine Anwendung • • • • • • Öffne die Netzwerkkarte Registriere benötigten Speicher Erzeuge benötigte VI‘s ... Programm ... Lösche VI‘s Schliessen der Netzwerkkarte 18 Die VIPL (VI Provider Library) • Wichtige Funktionsgruppen: – – – – – – – – Hardware Connection Endpoint Creation and Destruction Connection Management Memory Protection and Registration Data Transfer and Completion Operations Completion Queue Management Querying Operations Error Handling 19 Zusammenfassung VIA • Richtig Sinn macht eine Implementierung von VIA erst dann, wenn es genügend „Hardware Support“ fuer die VIA Funktionen gibt. – – – – Umsetzung Virtuelle - Physikalische Adresse Doorbells Send/Receive Queues Completion Queues 20 Zusammenfassung VIA • Dies ist nur möglich, wenn man auf genügend Speicher und einen Prozessor oder sonstigen programmierbaren Baustein auf der NetzwerkKarte zurückgreifen kann. • Aktuelle Implementierungen, die VIA in „Hardware“ implementieren benutzen dazu eine spezielle Firmware für den jeweiligen Netzwerk Prozessor 21 Übersicht über aktuelle VIA Implementierungen • Software Implementierungen – M-VIA – VI-GM (Myri) – ServerNet VIA • “Hardware” Implementierungen – – – – Firm VIA Giganet VIA (cLAN) Berkley’s VIA Project Servernet II (Compaq) 22 Übersicht über verschiedene VIA Implementierungen [1] Abbildung aus [1]; somit beziehen sich die Anmerkungen in dieser Tabelle nicht auf den Anhang dieser Präsentation 23 M-VIA: A High Performance Modular VIA for Linux • Typ: Software Emulation – VIPL, Kernel Agent – Fast/Gigabit Ethernet Drivers • • • • • Kann parallel zu TCP/IP laufen Strikt Intel-Konform Sehr effektiv auf SMP Maschinen MPI Implemetierung (MVICH) existiert Final official Release: M-VIA 1.2 24 M-VIA • Da kein spezieller HW Support: – Zero-copy beim Senden – One-copy beim Empfangen 25 M-VIA Network Packet Engines GNIC II Packet Engines GNIC II Tulip Fast Ethernet Tulip Fast Ethernet Protoco l TCP M-VIA TCP M-VIA Latency (us) 59 19 65 23 Bandwidth (MB/s) 31 60 11.4 11.9 26 VI-GM [9] • Typ: Userlevel Library (SW) – Läuft als “middleWare” auf GM 1.X • GM 2.0 wird nicht mehr unterstützt – – – – – Komplett Threadsafe Strikt Intel-Konform Unterstützung aller Reliability Levels Kein RDMA Read Unterstützt 64k Knoten 27 VI-GM • Leider keine echten Messergebnisse GM1.6.4 hat folgende Werte: NIC: Bandbreite: Latenz: Host CPU: PCI64C 421 MByte/s (bidir) 6.7 µs min 0.54 µs 28 Myricom Ausblick • Myricoms LanAI Prozessoren: – Ab Version 7 “Doorbell-tauglich” – Minimale Latenzzeiten von: • 3,5 us (LanAI 2XP) mit MX, kein GM oder VI-GM • 950 Mbyte/s Durchsatz (bidir) – Es wird auf der SC2003 ein Cluster vorgestellt » Allerdings kein VIA » Auch keine Performance-Daten für VIA vorhanden 29 Berkley VIA • Typ: Firmware Austausch für LanAI 4.x • Latenz 23-26 us • Bandbreite 30-60 Mbyte/s – Damals PCI mit 33 MHz – Oder S-Bus mit 25 MHz • Keine vollständige Implementierung 30 „FirmVIA“ Die Register des TBIC2 sind in den Adressraum des PPCs gemapped. Die Netzwerkkarte an sich kommuniziert mit dem Host über den SRAM, der in den User/Kernel Adressraum gemapped wird, oder es wird ein Interrupt ausgelöst. Die DMA Controller sorgen fuer die entsprechende IO Performance Bidirektionale 150 Mbyte/S 31 „FirmVIA“ • Firmware des NICs leicht abgewandelt • Latenz von 18 – 20 us 32 Giganet cLAN VIA • Typ: „Hardware“ Implementation von VIA • Latenz von 24 us, Durchsatz von 70 Mbyte/s [4] • Es existiert eine Implementierung für Microsoft SQL Server 2000 (cLAN1000) [8] 33 Latenz von cLAN [4] 34 Bandbreite von cLAN [4] 35 ServerNet VIA Typ: Software Emulation Latenz von 100 us Tandem hat zwar eine Hardware Version von VIA angekuendigt [4] aber Mittlerweile ist www.servernet.com nicht mehr im Netz. 36 Weiteres • Compaqs Servernet II: – Hardware Implementierung – Latenz 7.4 us, 180 Mbyte/s Durchsatz [7] – Leider auch hier Informationen nicht nachprüfbar, da Homepage nicht mehr verfügbar. 37 Weiteres • Auf Dolphins Homepage findet sich auch nichts aktuelles über VIA (1998) • myVIA: am 10.10.2002 letzter Eintrag. 38 Zusammenfassung Implementierungen • Es scheint fast, als ob sich niemand mehr für VIA interessiert. • Die meisten Projekte liegen in der Zeit von 1998 – 2001 • Viele Anbieter haben bei ihren neusten Produkten gar keine Unterstützung für VIA (weder implementiert, noch angedacht) 39 Zusammenfassung Implementierungen • Eine „echte“ Hardware Lösung existiert bisweilen nicht für VIA. • Da keine wirkliche Begrenzung der Anzahl der VIs gemacht wird: – Schwierig so etwas komplett in Hardware zu realisieren. – Es wird wohl immer eine „Emulationsebene“ geben, die die VIs auf die benutzte Hardware abbildet. (Multiplex) 40 References [1] Banikazemi, Abali, Herger, Panda: Design Alternatives for Virtual Interface Architecture (VIA) and an Implementation on IBM Netfinity NT Cluster [2] Bounadonna, Geweke, Culler: An Implementation and Analysis of the Virtual Interface Architecture [3] Rangarajan, Iftode: Software Distributed Shared Memory over Virtual Interface Architecture: Implementation and Performance [4] Speight, Abdel-Shafi, Bennet: Realizing the Performance Potential of the Virtual Interface Architecture [5] Intel, Compaq, Microsoft: Virtual Interface Architecture Specification. Draft Version 1.0. December 4, 1997 [6] http://www.nersc.gov/research/FTG/via/ [7] Begel, Bounadonna, Culler, Gay: An Analysis of VI Architecture Primitives in Support of Parallel and Distributed Communication [8] Dell Whitepaper January 2001: Virtual Interface Architecture and Microsoft SQL Server 2000 [9] http://www.myri.com bzw. http://www.myri.com/news/02213/ 41