Codegenerierung für digitale Signalprozessoren: Erweiterung eines

Werbung

Universität Karlsruhe (TH)

Codegenerierung für digitale

Signalprozessoren:

Erweiterung eines

Codegeneratorgenerators

basierend auf

Graphersetzungsmethoden

Diplomarbeit

Institut für Programmstrukturen und Datenorganisation

Prof. Dr. Gerhard Goos

Fakultät für Informatik

Universität Karlsruhe (TH)

von

cand. inform.

Hannah Schröter

Betreuer:

Dr. Sabine Glesner

Boris Boesler

Verantwortlicher:

Prof. Dr. Gerhard Goos

Februar 2003

Ich versichere, die vorliegende Diplomarbeit selbständig angefertigt zu haben. Alle

dabei verwendeten Hilfsmittel, Werkzeuge und Quellen wurden vollständig aufgeführt.

Karlsruhe, den 28. Februar 2003

(Hannah Schröter)

Inhaltsverzeichnis

1 Einleitung

1

1.1 Problemstellung, Anforderungen . . . . . . . . . . . . . . . . . . . . .

1

1.2

Lösungsansatz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

1.3

Motivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

1.4

Gliederung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

2 Verwandte Arbeiten

2.1 Ansätze zur Phasenkopplung . . . . . . . . . . . . . . . . . . . . . . .

2.2

2.3

5

5

2.1.1

Integer Linear Programming . . . . . . . . . . . . . . . . . . .

5

2.1.2

Constraint Logic Programming . . . . . . . . . . . . . . . . .

7

2.1.3

Genetische Algorithmen . . . . . . . . . . . . . . . . . . . . .

8

2.1.4

Dynamisches Programmieren . . . . . . . . . . . . . . . . . .

9

2.1.5

Heuristische Suche . . . . . . . . . . . . . . . . . . . . . . . .

9

2.1.6

Mutation Scheduling . . . . . . . . . . . . . . . . . . . . . . . 10

2.1.7

Software-Pipelining . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1.8

Prozessorregister als Funktionseinheiten . . . . . . . . . . . . 12

2.1.9

Der TM-1000-Compiler . . . . . . . . . . . . . . . . . . . . . . 12

Auswahl von DSP-Befehlen . . . . . . . . . . . . . . . . . . . . . . . 13

2.2.1

Vektorisierung . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.2.2

Musterersetzung auf Quelltextebene . . . . . . . . . . . . . . . 14

2.2.3

Integer Linear Programming . . . . . . . . . . . . . . . . . . . 14

Zusammenfassung und Bewertung . . . . . . . . . . . . . . . . . . . . 15

ii

Inhaltsverzeichnis

3 Grundlagen

19

3.1 Die SSA-Darstellung Firm . . . . . . . . . . . . . . . . . . . . . . . . 19

3.2

3.3

BURS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2.1

Kostenbehaftete Termersetzungssysteme . . . . . . . . . . . . 21

3.2.2

Übertragung auf BURS . . . . . . . . . . . . . . . . . . . . . . 23

Heuristische Suche . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3.1

Suchproblem . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3.2

Grundalgorithmus

3.3.3

Heuristische Suchverfahren . . . . . . . . . . . . . . . . . . . . 26

. . . . . . . . . . . . . . . . . . . . . . . . 24

3.4

Befehlsanordnung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.5

Erkennung von SIMD-Befehlen . . . . . . . . . . . . . . . . . . . . . 28

4 Effiziente Phasenkopplung mit zustandsbehafteter Termersetzung 29

4.1 Zustandsbehaftete Termersetzung . . . . . . . . . . . . . . . . . . . . 29

4.2

Maschinensimulation . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.2.1

Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.2.2

Phasengekoppelte Codeerzeugung . . . . . . . . . . . . . . . . 31

4.2.3

Identifikation von SIMD-Befehlen . . . . . . . . . . . . . . . . 32

4.3 Äquivalenz von Suchknoten . . . . . . . . . . . . . . . . . . . . . . . 33

4.4

Suboptimales Suchverfahren . . . . . . . . . . . . . . . . . . . . . . . 34

5 Implementierung

37

5.1 Anbindung der Maschinensimulation . . . . . . . . . . . . . . . . . . 37

5.1.1

Schnittstellen . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.1.2

Regeln mit Befehlsmustern . . . . . . . . . . . . . . . . . . . . 39

5.1.3

Anbindung an die Suche . . . . . . . . . . . . . . . . . . . . . 40

5.2 Äquivalenzklassen von Suchknoten . . . . . . . . . . . . . . . . . . . 40

5.3

Parametrisierbare Suche . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.4

Sonstige Laufzeitverbesserungen . . . . . . . . . . . . . . . . . . . . . 43

5.4.1

Verwaltung der Menge offener Knoten . . . . . . . . . . . . . 43

5.4.2

Iteration über Nachfolger eines Suchknotens . . . . . . . . . . 44

5.4.3

Menge der noch zu bearbeitenden Programmgraphknoten . . . 44

5.5 Übersicht über den Codegenerator . . . . . . . . . . . . . . . . . . . . 44

Inhaltsverzeichnis

6 Ergebnisse

iii

47

6.1 Testumgebung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

6.1.1

Idealisierte Prozessorarchitektur . . . . . . . . . . . . . . . . . 47

6.1.2

Codegeneratorspezifikation . . . . . . . . . . . . . . . . . . . . 48

6.1.3

Maschinensimulation . . . . . . . . . . . . . . . . . . . . . . . 48

6.1.4

Testgraphen . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6.1.5

Varianten des Codegenerators . . . . . . . . . . . . . . . . . . 49

6.2

Messergebnisse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6.3

Auswertung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

6.3.1

Auswirkung der Phasenkopplung . . . . . . . . . . . . . . . . 52

6.3.2

Äquivalenzen von Suchknoten . . . . . . . . . . . . . . . . . . 53

6.3.3

One-Then-Best-Suche . . . . . . . . . . . . . . . . . . . . . . . 53

6.3.4

Laufzeitabhängigkeit von den Eingabegraphen . . . . . . . . . 54

7 Zusammenfassung und Ausblick

57

7.1 Ergebnisse dieser Arbeit . . . . . . . . . . . . . . . . . . . . . . . . . 57

7.2

Offene Probleme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Literaturverzeichnis

61

Index

65

1. Einleitung

1.1

Problemstellung, Anforderungen

Es werden auch heute noch signifikante Teile der Software für eingebettete Systeme und digitale Signalprozessoren (Digital Signal Processor – DSP) manuell in der

Assemblersprache der jeweiligen Architektur geschrieben. Dies liegt daran, dass der

Qualitätsunterschied zwischen handgeschriebenen Assemblerprogrammen und von

Übersetzern erzeugtem Code bisher oft zu groß ist. Weil diese manuelle Anpassung

jedoch viel Arbeitszeit in Anspruch nimmt und fehleranfällig ist, ist es nötig, künftig

auch mit Übersetzern eine bessere Codequalität zu erzielen.

Wir konzentrieren uns in dieser Arbeit auf die folgenden Probleme: Zum einen bearbeiten wir das Problem der Phasenkopplung zwischen Befehlsauswahl und Befehlsanordnung. Zum anderen wollen wir im Rahmen dieser Phasenkopplung auch

automatisch Single-Instruction-Multiple-Data-Befehle (SIMD) auswählen, wo dies

möglich und effizient ist.

Die Codeerzeugung soll direkt aus graphbasierten Darstellungen mit statischer Einmalzuweisung (Static Single Assignment – SSA) erfolgen, damit wir uns hier möglichst viele Spielräume erhalten.

Da für eingebettete Systeme oft die Anwendungssoftware und die Hardware gemeinsam entworfen werden, ist es besonders interessant, wenn die Übersetzer leicht

an Änderungen der Prozessoren angepasst werden können. Dadurch ist es nämlich

schneller möglich, die Auswirkungen dieser Änderungen auf die Effizienz der zu entwickelnden Anwendungen zu erproben. Daher wollen wir erreichen, dass man ein

Backend für einen neuen Prozessor mit unserem Verfahren erstellen kann, indem

man möglichst nur Parameter und/oder Prozessorspezifikationen anpassen muss.

Auch wenn im Bereich der Codeerzeugung für eingebettete Systeme etwas höhere

Übersetzerlaufzeiten akzeptiert werden können, müssen wir dennoch teilweise einen

Kompromiss zwischen der Qualität des erzeugten Codes und der Laufzeit des Codegenerators eingehen. Wir wollen unser Verfahren so entwickeln, dass dieser Kompromiss durch Parameter gesteuert werden kann, die beim Start der Codeerzeugung

2

1. Einleitung

gesetzt werden. Das Problem, optimalen Code aus einer graphbasierten Zwischensprache zu erzeugen, ist nämlich im Allgemeinen NP-vollständig (zur Befehlsauswahl aus DAGs, siehe [GaJo90]; zur Befehlsanordnung, siehe [HeGr83], zitiert nach

[ErKr91]; zur Registerallokation, siehe [FaLi97]; siehe auch [Seth75]).

1.2

Lösungsansatz

Unsere Methode basiert auf einer Kombination von Bottom Up Rewrite Systems

(BURS) und heuristischer Suche [NyKa97]. An unserem Institut wurde der Codegenerator-Generator cggg erstellt, in dem diese Kombination in der Praxis umgesetzt,

in der Laufzeit verbessert und zur Anwendung auf SSA-Graphen erweitert wurde

[Boes98]. In den genannten Arbeiten werden den Befehlen feste Kosten zugeordnet. Damit decken sie nur die Befehlsauswahl aus Bäumen [NyKa97] bzw. Graphen

[Boes98] ab. Boesler [Boes98] deutet jedoch schon die Möglichkeit an, die heuristische Suche auch dynamischer zu steuern, um eine Maschinensimulation zu integrieren, und schlägt ein Verfahren vor, dies umzusetzen. Wir greifen diese Idee in dieser

Arbeit auf, arbeiten sie genauer aus und setzen sie praktisch um.

Auf diese Weise erreichen wir eine Codeerzeugung aus SSA-Graphen, die die Phasen

der Befehlsauswahl und Befehlsanordnung koppelt. Dies hilft uns, die Parallelität

auf Befehlsebene (Englisch: Instruction Level Parallelism – ILP) auszunutzen, die

von Prozessoren mit Pipeline, superskalaren Prozessoren, Architekturen mit langen

Befehlswörtern (Very Large Instruction Word – VLIW) und digitalen Signalprozessoren angeboten werden. Es können desweiteren Teilbefehle von SIMD-Befehlen ausgewählt werden, wenn sie in einer einfachen Nachbearbeitung zu den SIMD-Befehlen

selbst kombiniert werden können.

Die Retargierbarkeit erreichen wir, indem wir den Codegenerator weiterhin wie in

[Boes98] aus wiederverwendbaren sowie von dem Codegenerator-Generator erzeugten Modulen konstruieren.

Den teilweise nötigen Kompromiss zwischen Codequalität und Generatorlaufzeiten

stellen wir her, indem wir ein alternatives Suchverfahren entwickeln. Wir bieten nun

eine Wahlmöglichkeit am Anfang der Codegenerierung an, ob die bisher verwendete

A∗ -Suche oder unser alternatives Suchverfahren verwendet werden soll. Bei unserem

neuen Suchverfahren, das schneller, aber nicht unbedingt optimal ist, kann man die

Codequalität bzw. Codegeneratorlaufzeit durch zusätzliche Parameter steuern.

1.3

Motivation

In traditionellen Übersetzern erfolgt die Codeerzeugung meist so, dass aus einer Zwischendarstellung in getrennten Phasen die Befehlsauswahl, Befehlsanordnung und

Registerzuteilung mit eventuellem Zwischenspeichern von Werten stattfindet. Zwar

gibt es auch in diesen traditionellen Codegeneratoren teilweise unterschiedliche Anordnungen dieser Phasen und teilweise werden Phasen wiederholt durchgeführt. Dennoch wird dies gerade bei der Codeerzeugung für eingebettete Systeme den dort sehr

hohen Anforderungen nicht gerecht. Die unterschiedlichen Phasen verfolgen nämlich

oft einander entgegengesetzte Ziele.

1.4. Gliederung

3

Zum Beispiel kann der Übersetzer bei getrennter Befehlsauswahl und -anordnung

nicht unterscheiden, ob je nach Belegung von Funktionseinheiten oder Prozessorregistern für den Ausdruck 2 · x entweder ein Multiplikationsbefehl, eine Addition von

x mit sich selbst oder ein Schiebebefehl am günstigsten ist.

Desweiteren bieten moderne Architekturen oft SIMD-Befehle an. Beispiele sind

sowohl digitale Signalprozessoren wie der TriMedia TM-1300 als auch Media-Befehlssätze in Allzweckprozessoren, zum Beispiel Intels MMX und SSE, Suns VISBefehlssatz oder die AltiVec-Befehle in der PowerPC-Architektur. Diese werden von

gängigen Übersetzern nicht automatisch ausgenutzt, sondern höchstens als Erweiterungen der übersetzten Programmiersprache(n) zur manuellen Verwendung angeboten. Wenn ein Softwareentwickler diese Erweiterungen jedoch verwendet, ergibt

sich daraus der Nachteil, dass eine Anpassung an andere Architekturen zusätzlichen

Aufwand bedeutet.

Ein anderes Hindernis für die Erzeugung von effizientem Maschinencode ist, dass

einerseits in der Forschung bevorzugt SSA-Darstellungen verwendet werden, andererseits jedoch der Code üblicherweise erzeugt wird, indem zuerst eine Transformation in eine traditionellere Baum- oder DAG-Darstellung erfolgt. Durch solche

Zwischenschritte verliert man jedoch einen Teil der Spielräume für optimierende

Codegenerierung.

Daher haben wir uns entschieden, die hier formulierte Problemstellung zu bearbeiten,

nämlich die Phasen der Befehlsauswahl und -anordnung zu koppeln, hiermit auch

SIMD-Befehle automatisch auszuwählen und diese Codeerzeugung direkt aus SSAGraphen durchzuführen.

1.4

Gliederung

In Kapitel 2 stellen wir verwandte Arbeiten zur Phasenkopplung und Codeerzeugung

für digitale Signalprozessoren vor. Dann erläutern wir die hier verwendeten Grundlagen, vgl. Kapitel 3. In Kapitel 4 entwickeln wir eine Theorie zustandsbehafteter

Termersetzung, die wir einsetzen, um eine Maschinensimulation in die Codegenerierung einzubinden. Dort erarbeiten wir auch eine Methode, um den Suchraum der

A∗ -Suche, wie sie bereits von Boesler [Boes98] verwendet wird, zu verkleinern, und

einen alternativen Suchalgorithmus, der es erlaubt, schnell guten, wenn auch nicht

garantiert optimalen, Code zu erzeugen. Die Implementierung dieser Verfahren beschreiben wir in Kapitel 5. Danach zeigen wir anhand von Experimenten, wie das hier

entwickelte Verfahren die gesetzten Ziele der verbesserten Codequalität bei gleichzeitig akzeptablen Laufzeiten des Übersetzers erreicht, vgl. Kapitel 6. Abschließend

fassen wir die Arbeit zusammen und skizzieren mögliche Weiterentwicklungen.

4

1. Einleitung

2. Verwandte Arbeiten

Zur Codegenerierung für DSPs gibt es bereits viele Ansätze. Zum einen existieren Methoden zur engeren Kopplung der traditionell meist getrennt behandelten

Phasen der Codeerzeugung, vorgestellt in Abschnitt 2.1. Zum anderen gibt es auch

Arbeiten, die zum Ziel haben, automatisch DSP-spezifische Befehle zu erzeugen, vgl.

Abschnitt 2.2.

Abschließend fassen wir die verwandten Arbeiten zusammen und bewerten sie anhand unserer Anforderungen.

2.1

2.1.1

Ansätze zur Phasenkopplung

Integer Linear Programming

In [WGHB95] ([MaGo95], Kapitel 6) wird ein Ansatz vorgestellt, der auf der Basis von ganzzahliger linearer Programmierung (Integer Linear Programming – ILP)

eine simultane Lösung für die Befehlsauswahl, -anordnung und Registerzuteilung

einschließlich der Entscheidung über eventuelles Zwischenspeichern (Spilling) erreicht. Ein Frontend übersetzt eine Programmiersprache namens C+− (C ohne

Zeigerarithmetik, dafür mit zusätzlichen Ausdrucksmitteln, um z.B. Muster der

Verwendung von Reihungen darzustellen) in eine Zwischendarstellung (Symboltabellen, Daten- und Kontrollflussgraphen). Danach folgen Optimierungen auf dieser

Zwischendarstellung, die entweder manche Entscheidungen komplett vorwegnehmen

oder Entscheidungsmöglichkeiten lediglich markieren, damit sie später in die ILPFormulierung der phasengekoppelten Codegenerierung einfließen können. Anschließend wird ein ganzzahliges lineares Programm aufgestellt, das folgende Teilaufgaben

simultan löst:

• Kombination von generischen Operationen im Datenflussgraphen zu komplexeren Maschinenbefehlen, z.B. + und ∗ zu einem Multipliziere-und-AddiereBefehl,

• Anordnung der Befehle,

6

2. Verwandte Arbeiten

• globale Registerzuteilung,

• Zwischenspeichern von Werten (Spilling) und

• Kompression (Kombination von Teilbefehlen zu endgültigen Maschinenbefehlen).

Laut [Käst01], Seite 3, soll dieses Verfahren jedoch aufgrund der Komplexität der

ILP-Formulierung zu exzessiven Laufzeiten des Codegenerators führen.

Das System PROPAN [Käst01, Käst00, Käst97] arbeitet als Nachbearbeitung auf

bereits generiertem Assembler-Code. Es werden verschiedene Graphen hergestellt

([Käst00], Seite 47 ff.), wie der Ressourcengraph (Zuordnung aller Befehle zu den

Prozessorressourcen, die alternativ zur Ausführung verwendet werden können) und

der Registergraph (Zuordnung der Anweisungen zu möglichen Registern, in die das

Ergebnis der jeweiligen Instruktion geschrieben werden kann). Daraus wird eine der

beiden folgenden ILP-Formulierungen erstellt und dann gelöst.

In der SILP-Form ( Scheduling and allocation with Integer Linear Programming“)

”

ist der Hauptteil der Entscheidungsvariablen eine Angabe von Reihenfolgen (xkij = 1

⇔ Befehl j wird direkt nach Befehl i auf einer Funktionseinheit des Typs k ausgeführt). Es wird für jede Art von Ressource ein Ressourcenflussgraph erstellt, der den

Fluss“ jeder Ressource durch alle Befehle, die diese Ressource verwenden, model”

liert. Daraus werden Beschränkungen für das resultierende ILP abgeleitet. Insgesamt

gelten als Beschränkungen:

• Die Gesamtlaufzeit ist das Maximum der Zeitpunkte, zu denen die einzelnen

Befehle abgesetzt werden. Die Variable Gesamtlaufzeit“ kann so als zu mini”

mierende Zielfunktion verwendet werden.

• Datenabhängigkeiten müssen erfüllt sein.

• Im Ressourcenflussgraphen muss jede Ressource die Befehle auch verlassen, die

sie betritt.

• Jeder Befehl muss von genau einer Ressource ausgeführt werden.

• Die Anzahl der vorhandenen Ressourcen darf nicht überschritten werden.

• Jede Instanz einer Ressource kann gleichzeitig nur einen Befehl ausführen.

Durch die Modellierung von Registerflussgraphen (Fluss der Register durch die Befehle) kann die Registerzuteilung integriert werden. Diese Formulierung hat O(n2 )

Entscheidungsvariablen und Beschränkungen (siehe [Käst00], Seiten 61 f.), wobei n

die Anzahl der Befehle ist.

Im OASIC-Modell ( Optimal Architectural Synthesis with Interface Constraints“)

”

gibt es hauptsächlich Entscheidungsvariablen xkjn , die besagen, dass Befehl j zum

Zeitpunkt n von einer Funktionseinheit des Typs k ausgeführt wird (zeitindizierte

Form). Beschränkungen werden für folgende Sachverhalte erzeugt:

2.1. Ansätze zur Phasenkopplung

7

• Befehle werden genau einmal innerhalb der Gesamtausführungszeit des Grundblocks ausgeführt.

• Es können nie mehr Befehle auf einem Ressourcentyp ausgeführt werden als

Instanzen dieses Typs vorhanden sind.

• Datenabhängigkeiten müssen erfüllt sein.

Auch hier können zusätzliche Beschränkungen die Registerzuteilung einbeziehen. Die

Anzahl der Variablen hat die Größenordnung O(n · m2 ) mit O(k 3 ) Beschränkungen,

wobei n die Anzahl der Ressourcentypen, m die Anzahl der Befehle und k die Anzahl

der Knoten des Datenflussgraphen ist.

In der Praxis ist SILP für die Integration der Registerzuteilung besser geeignet,

während OASIC seine Vorteile hauptsächlich bei hoher Parallelität auf Befehlsebene

ausspielen kann ([Käst00], Seiten 79 f.).

Bei größeren Programmstücken werden Approximationen benutzt, um die Laufzeiten in Grenzen zu halten. So können auch größere Grundblöcke oder Superblöcke“ –

”

das sind Kontrollstrukturen mit genau einem Eingangsblock und genau einem Ausgangsblock (für die genaue Definition, vgl. [Käst00], Seiten 12 und 97) – mit nahezu

optimalen Lösungen und akzeptablen Laufzeiten des Optimierers bearbeitet werden. Damit werden in Beispielen Laufzeiten im Bereich von Sekunden bis Minuten

erreicht (siehe [Käst01], Seite 16 bzw. 17, detaillierter in [Käst00], Kapitel 10, Seiten

183 ff.).

2.1.2

Constraint Logic Programming

Bashford und Leupers stellen in [BaLe99b, BaLe99a] einen Ansatz zur phasengekoppelten Codeerzeugung auf der Basis von Constraint Logic Programming vor.

Als Zwischensprachen werden Baumdarstellungen oder azyklische Datenflussgraphen

verwendet. Es werden zuerst Überdeckungen von Datenflussgraphen mit Mustern gefunden. Die Muster, die die Autoren mit dem Begriff Factored Register Transfer“

”

(FRT) bezeichnen, sind definiert mit

• der Operation,

• den möglichen Speicherressourcen (Register, Speicherzugriffe, virtuelle Ressourcen zur Darstellung komplexerer Muster) für den definierten und die verwendeten Werte,

• zusätzlichen Ressourceninformationen, nämlich Funktionseinheiten zur Ausführung, Kosten und Maschinenbefehlstyp zur Steuerung der eventuell möglichen parallelen Ausführung, sowie

• sonstigen Beschränkungen.

In den Beschränkungen können Zusammenhänge zwischen der konkreten Wahl von

Speicherressourcen oder zwischen Speicherressourcen und Funktionseinheiten usw.

dargestellt werden. Bei der Graphüberdeckung mit diesen Mustern werden zusätzlich

Beschränkungen erzeugt, die darstellen, dass das Ergebnis eines Operandenknotens

8

2. Verwandte Arbeiten

eventuell von der Ergebnis-Speicherressource in die Operanden-Speicherressource des

verwendenden Knotens übertragen werden muss. Die Komplexität der Überdeckung

wird mit O(N ·D2 ) angegeben, wobei N die Anzahl der Knoten im Datenflussgraphen

und D das Maximum der Anzahlen von Funktionseinheiten, Speicherressourcen und

Befehlstypen ist. Anschließend wird mit Hilfe des Systems ECLiPSe eine optimale

bzw. bei größeren Problemen eine heuristisch nahezu optimale Lösung gesucht, die

die Kosten (als Summe der einzelnen Muster- und Transferkosten) minimiert und

dabei die vorhandenen Beschränkungen erfüllt. Hierbei werden die Entscheidungen

über die Bindung von Befehlen an Speicherressourcen und Funktionseinheiten aufgeschoben. Während einer listenbasierten Befehlsanordnung werden gegebenenfalls

zusätzliche Beschränkungen für diese Entscheidungen erzeugt. Erst am Ende werden

die Zuweisungen unter Berücksichtigung aller dieser Beschränkungen festgelegt. Dadurch wird die Phasenkopplung zur Befehlsanordnung erreicht. Laut [BaLe99b], Seite 28, werden für Bäume generell gute Laufzeiten des Codegenerators bei optimaler

Codeauswahl erzielt. Bei Graphen ist allerdings ein Ausweichen auf die heuristische,

suboptimale Strategie nötig.

2.1.3

Genetische Algorithmen

In [LLMD+ 01] stellen Lorenz, Leupers, Marwedel, Dräger und Fettweis eine Methode

vor, um möglichst energiesparenden Code für DSPs aus azyklischen Datenflussgraphen zu erzeugen. Dabei wird ein genetischer Algorithmus verwendet. Mögliche Lösungen werden als Chromosomen“ betrachtet, die wiederum aus einzelnen Genen“

”

”

bestehen. Es soll eine gute Kombination von Allelen“ (konkrete Werte für die ein”

zelnen Gene) gefunden werden. Dazu werden auf eine Population von Chromosomen

die Operationen der Selektion, der Mutation und des Crossover angewendet. Es wird

eine Startpopulation erzeugt (Initialisierung) und bewertet. Dann werden wiederholt

eine Selektion (probabilistisch anhand der Bewertung auswählen, welche Individuen ihre Information an die nächste Generation vererben“), Crossovers (Austausch

”

von Genen zwischen Individuen) und Mutationen (Veränderung einzelner Allele)

durchgeführt. Die Ergebnisse werden wieder bewertet. Anschließend wird entweder

zur Selektion zurückgesprungen oder der Algorithmus beendet, je nachdem, ob eine Abbruchbedingung erfüllt ist. Konkret wird zur Initialisierung eine Menge von

Individuen geschaffen, indem jeweils in einer listenbasierten Befehlsanordnung probabilistisch ein nächster ausführbarer Befehl ausgewählt wird. Jedes Gen entspricht

einer möglichen Überdeckung eines Graphknotens mit Annotation der zuzuteilenden Ressourcen (Register/Speicherstellen, Funktionseinheiten). Die Befehlsauswahl

wird hierbei integriert, indem jeweils erst nach der Auswahl des nächsten ausführbaren Graphknotens ein Befehl ausgewählt wird. Die Bewertungsfunktion kann dem

jeweiligen Optimalitätskriterium angepasst werden (z.B. Geschwindigkeit, Echtzeitverhalten oder Energieverbrauch). Der Crossover erfolgt durch zufälligen Austausch

von Genen. Die Mutation ähnelt etwas der Initialisierung und enthält zusätzlich

eine Korrektheitsprüfung, da durch den willkürlichen Austausch im Crossover gegebenenfalls Inkonsistenzen auftreten können. Im Experiment wurde mit akzeptablen

Laufzeiten im Schnitt relativ guter Code produziert (siehe [LLMD+ 01], Tabelle 2).

Es wurden für n Knoten im Graph 20 · n Generationen mit einer Populationsgröße

von 30 verwendet. Die Verbesserungen gegenüber klassischer baumbasierter Codeerzeugung waren im Bereich von ca. 30 % weniger Befehlen, ca. 30 bis 40 % weniger

Speicherzugriffen und ca. 20 bis gut 30 % geringerem simulierten Energieverbrauch.

2.1. Ansätze zur Phasenkopplung

9

Die Laufzeiten bewegten sich von 3 Sekunden einer 333 MHz-Ultra-10-CPU bei 12

Graphknoten bis zu 256 Sekunden bei 80 Graphknoten.

2.1.4

Dynamisches Programmieren

In [KeBe01] stellen Keßler und Bednarski eine Methode zur Phasenkopplung zwischen Befehlsauswahl und -anordnung auf Grundblockebene für Architekturen mit

einem beschränkten Satz von Allzweckregistern vor. Die Grundidee ist eine topologische Sortierung eines DAG, der die Abhängigkeiten zwischen Operationen beschreibt. Damit ist dieses Verfahren entlang der Befehlsanordnung organisiert, die

Befehlsauswahl erfolgt verzahnt während der Anordnung. Bei gewöhnlicher listenbasierter Befehlsanordnung wird an jeder Stelle, an der eine Entscheidungsmöglichkeit

besteht, sofort anhand einer Heuristik eine Entscheidung getroffen und festgelegt.

Im vorliegenden Ansatz dagegen geht man als Idee von dem Suchbaum der möglichen topologischen Sortierungen aus. An jeder Stelle im Baum wird als Information

die Menge der DAG-Knoten, die zur Auswahl zur Verfügung stehen (d.h. keine Vorgänger oder alle Vorgänger bereits ausgewählt), und der Maschinenzustand (d.h.

Vorgeschichte der Belegung der Funktionseinheiten durch die bisher ausgewählten

Befehle) mitgeführt. Desweiteren werden die Knoten attributiert mit der Anordnung

der bisher ausgewählten Befehle und der Zahl der für diese benötigten Prozessortaktzyklen. Aus dem Suchbaum wird ein Suchgraph, indem Knoten zusammengelegt

werden, die sich nur in der Anordnung, aber nicht in der Menge der ausgewählten

Befehle und/oder dem Zeitverbrauch unterscheiden. Dabei wird lediglich die bislang beste Anordnung der Befehle und der zugehörige beste Zeitverbrauch belassen.

Dies beeinträchtigt die Optimalität nicht, siehe Satz 1 auf Seite 5 von [KeBe01].

Die Graphknoten werden in eine Matrix einsortiert, die durch die Anzahl der bereits ausgewählten Befehle und die bisher nötigen Taktzyklen indiziert ist. Damit

kann letztlich ein dem dynamischen Programmieren entsprechender Algorithmus die

Suche implementieren, wobei die äußere Schleife über den Zeitindex und die innere

über die Anzahl der bereits gewählten Befehle läuft. Im Gegensatz zur simplen Aufzählung aller möglichen topologischen Sortierungen, die bis zu ca. 15 Graphknoten

praktikabel ist, ist mit dem vorliegenden Ansatz eine Optimierung für bis zu ca. 50

Graphknoten praktikabel, allerdings schon in der Größenordnung von CPU-Stunden

([KeBe01], Seite 7).

2.1.5

Heuristische Suche

Hanono stellt einen Ansatz namens AVIV vor, der eine phasengekoppelte Codegenerierung für Grundblöcke mittels heuristischer Suche auf Ausdrucks-DAGs erreicht [Hano99, HaDe98]. Das Frontend erzeugt eine Sammlung von gewöhnlichen

Datenflussgraphen sowie Information über den Kontrollfluss zwischen diesen. Im

Codegenerator wird daraus zuerst eine so genannte Split-Node DAG“-Darstellung

”

erzeugt. Bei allen Knoten des ursprünglichen DAG werden als Vorgänger sogenannte Split-Knoten ( split nodes“) eingefügt, deren Vorgänger die Vorgänger aus dem

”

ursprünglichen Graphen sind. Dieser Vorgänger wird dupliziert (der Split-Knoten

hat in dem Fall also mehrere Vorgänger), wenn er auf verschiedenen Funktionseinheiten des Prozessors ausgeführt werden kann. Falls zwischen diesen Vorgängern und deren Verwendung noch Transfers nötig sind, werden noch dazu Transferknoten eingefügt. Aus einer Kante Use → Def wird also eine Reihe von Pfaden

Use → Split → Transfer1 → Def1 , . . . , Use → Split → Transfern → Defn . Auf

10

2. Verwandte Arbeiten

dieser Darstellung werden mittels Graphüberdeckung in einer ersten Phase simultan

die Befehlsauswahl, die Zuteilung von Funktionseinheiten und Registersätzen, die

Gruppierung in Instruktionen und die Befehlsanordnung durchgeführt. Es wird zuerst der Suchraum der Entscheidungsmöglichkeiten an jedem Split-Knoten mit einer

heuristischen Kostenbewertung beschnitten, die berücksichtigt, wieviel Parallelität

(z.B. durch VLIW) durch Entscheidungen aufgegeben wird und wieviele zusätzliche

Transfers (Transferknoten) nötig sind. Dann werden für die übrigen Auswahlmöglichkeiten (mit (∗) bezeichnet) die nötigen Transferknoten hinzugefügt. Dies führt

wieder zu einer heuristischen Auswahl, wenn die Datenpfade beschränkt sind; hier

basiert die Heuristik nur auf dem Grad der möglichen Parallelität. Dann werden

maximale Gruppierungen von parallel ausführbaren Graphknoten gefunden (nicht

voneinander abhängig, nicht im Konflikt um Funktionseinheiten). Da es zu lange

dauern würde, alle diese Gruppierungen zu erzeugen, wird wieder eine heuristische

Beschränkung eingeführt: Es werden nur Graphknoten kombiniert, deren Tiefe (Abstand zur Wurzel des Graphen) bzw. Höhe (Abstand zu den Blättern) nicht zu weit

voneinander abweichen. Eventuell auf der Zielarchitektur aus besonderen Gründen

ungültige Gruppierungen werden verworfen. Jetzt wird tatsächlich eine möglichst

kostengünstige Anordnung gesucht: Unter den Gruppierungen, deren Vorgänger alle

bereits ausgewählt sind, wird eine möglichst große Gruppe ausgesucht. Wenn mehrere maximal große Gruppen existieren, wird geschätzt, wieviele weitere Gruppen (d.h.

Befehlsworte) noch gebraucht werden, wenn die betreffende Gruppe gewählt wird,

und danach entschieden. Dabei werden Zähler über die Registerverwendung (Anzahl

lebendiger Werte je Registersatz) mitgeführt und laufend Entscheidungen über das

Zwischenspeichern von Werten gefällt. Falls dieses nötig ist, wird der ursprüngliche

Transferknoten an dieser Stelle durch Speicher- und Ladeknoten ersetzt, die Gruppierungen für die Graphknoten, die noch nicht ausgewählt wurden, neu berechnet

und die Auswahl von Gruppierungen fortgesetzt. Nachdem dies für alle Auswahlen

(∗) durchgeführt worden ist, wird die günstigste dieser Wahlmöglichkeiten als generierter Code festgelegt. In einer abschließenden Phase werden die Register vollends

zugeteilt und Guckloch-Optimierungen ausgeführt. Die Laufzeiten des Codegenerators auf einer Sun Ultra-30/300 sind im Bereich von bis zu 10 Sekunden für DAGs

von 16 Knoten (106 Knoten in der Split-Node DAG“-Darstellung). Ohne heuris”

tische Beschränkungen liegt die Laufzeit bei denselben Beispielen bei bis zu 120

Sekunden.

2.1.6

Mutation Scheduling

In [NoNi95, NoND95] stellen Novack, Nicolau und Dutt eine Methode zur Integration der Befehlsauswahl in die Befehlsanordnung dar. In der Zwischendarstellung, die eine modifizierte SSA-Form ist, wird zu jedem Wert (SSA-Knoten) eine

Annotation erzeugt, auf welche verschiedene Weisen der Wert berechnet werden

kann ( Mutations“)1 , z.B. Synonyme (Zuweisung = Addition mit 0 = Multiplikati”

on mit 1 etc.), zusammengesetzte Befehle (z.B. Multiplikation und Addition oder

auch explizites Bypassing z.B. beim Intel i860) oder Reduktion der Höhe eines

(Teil)ausdrucksbaumes. Wenn dann während der Befehlsanordnung Ressourcenkonflikte festgestellt werden, wird versucht, einen Befehl, der bereits ausgewählt ist,

1

Zu beachten ist, dass der hier verwendete Begriff Mutations“ nicht mit den Mutationen in

”

einem genetischen Algorithmus zusammenhängt.

2.1. Ansätze zur Phasenkopplung

11

durch andere Varianten derselben Berechnung auszutauschen ( Mutation“), um die”

sen oder andere Befehle dann günstiger anordnen zu können und/oder den Registerdruck zu verringern. Laut [NoNi95], Seiten 11 ff., werden signifikante Verbesserungen

gegenüber der Verwendung genau desselben Codegenerators ohne Mutation erzielt.

Über die Laufzeit des Codegenerators wird in [NoNi95, NoND95] keine Aussage getroffen.

2.1.7

Software-Pipelining

Mesman, Strik, Timmer, van Meerbergen und Jess stellen einen Ansatz zur Kopplung

der Registerzuteilung und Befehlsanordnung vor [MSTM+ 97], der aus einer besonderen Form von Abhängigkeitsgraphen eine Befehlsanordnung und Registerzuteilung

berechnet. Der Graph besteht aus Knoten für jeden Befehl und Pseudobefehlen für

den Anfang und das Ende des zu bearbeitenden Codestücks. Die Kanten sind gerichtet und mit minimalen Latenzen sowie gegebenenfalls Namen für die entlang

der Kanten transportierten Werte bezeichnet. Zusätzliche Eingaben sind Ressourcenkonflikte zwischen Operationen, die Bindung der Werte an Registerbänke, eine

Gesamtlatenz l und ein Initialisierungsintervall ( initialization interval“) für die ent”

haltende Schleife (II).2 Dieses beschränkt die maximale Lebensdauer von Werten in

Registern und muss bei der Beachtung von Ressourcenkonflikten berücksichtigt werden: Befehl B kann nicht genau II Zyklen nach Befehl A ausgeführt werden, wenn

diese auf derselben Funktionseinheit laufen, da sonst die erste Ausführung von B mit

der zweiten von A in Konflikt gerät. Diese werden in den Graphen eingearbeitet, indem Rückwärtskanten vom Endeknoten zum Startknoten mit der Bezeichnung −l

(d.h. der Start kann frühestens −l Zyklen nach, also l Zyklen vor dem Ende erfolgen) und von Verwendungen von Werten zu deren Produktion mit der Bezeichnung

−II eingefügt werden. Anschließend wird eine initiale Registerzuteilung gewählt.

Dieser entsprechend werden zusätzliche Beschränkungen (Kanten) in den Graphen

eingearbeitet: Wenn z.B. ein Befehl A einen Wert für die Verwendung B produziert und ein Befehl C für Verwendung D und wenn beide Werte im selben Register

platziert werden sollen, muss entweder B vor C oder D vor A ausgeführt werden.

Wenn durch zusätzliche Beschränkungen schon klar ist, dass D nach A oder C nach

A ausgeführt wird, kann ohne Verlust von möglichen Anordnungen also eine Kante

von B nach C eingefügt werden. Danach wird geprüft, ob mit diesen zusätzlichen

Beschränkungen eine Anordnung möglich ist. Wenn ja, wird diese ausgegeben und

der Algorithmus terminiert. Wenn nein, wird eine möglichst kleine Menge von durch

die Registerzuteilung generierten Beschränkungen erzeugt, die für die Unmöglichkeit

der Anordnung verantwortlich ist. Diese Analyse ist nach Aussage der Autoren in

O(E) (E = Anzahl der Kanten im Graphen) möglich. Mit dieser Information wird

dann die Registerzuteilung revidiert und von vorn angefangen. Die Gesamtlaufzeit

wird nach den auf Seite 372 genannten Ergebnissen hauptsächlich von der Zahl der

nötigen Iterationen bestimmt. In den genannten Beispielen sind dies bis zu 20, mit

einer Laufzeit von 25 Sekunden.

In [PiME99] wird ein ähnlicher Ansatz vorgestellt. Solange bei einer Abschätzung

mit den vorhandenen Zeitabhängigkeiten im Abhängigkeitsgraphen die Anzahl der

2

Diese und die unten genannte Arbeit bezieht sich speziell auf Schleifencode, auf dem ein

Software-Pipelining durchgeführt wird. Das Initialisierungsintervall bezeichnet die Periode der

Schleife im Ergebnis, die Gesamtlatenz den Zeitabstand zwischen der i-ten Ausführung des ersten Befehls bis zur i-ten Ausführung des letzten Befehls.

12

2. Verwandte Arbeiten

sich überlappenden Lebensdauern (also von dem frühestmöglichen Zeitpunkt eines

Produzenten bis zum spätmöglichsten Zeitpunkt des letzten Konsumenten) zu groß

für die jeweiligen Registerbänke ist, werden Lebensdauern durch das Einfügen zusätzlicher Abhängigkeiten sequenziert, die einander zwar nach bisheriger Informationslage überlappen können, sich aber nicht zwingend überlappen. Für die genaue

Auswahl, welche Lebensdauern sequenziert werden, wurden in der Arbeit unterschiedliche Heuristiken erprobt. Von einer Menge von 60 Beispielprogrammstücken

wurden jedoch bei allen diesen Heuristiken nur für 44 bis 50 Stück Lösungen gefunden. Der Zeitaufwand bewegt sich im Bereich von 225 bis 720 Sekunden auf einem

Pentium II mit 233 MHz.

2.1.8

Prozessorregister als Funktionseinheiten

In [ZeWe01] wird eine Kombination von der Registerzuteilung mit der Befehlsanordnung vorgestellt. Zuerst wird entschieden, welche Werte in Registern gehalten

werden, und nötigenfalls Code zur Zwischenspeicherung erzeugt. Dann werden die

zugeteilten Register als Verwendung von virtuellen Ressourcen modelliert. Die Knoten des Abhängigkeitsgraphen sind den Ressourcen zugeordnet, die zur Ausführung

notwendig sind (Funktionseinheiten, Busse usw.), und die Kanten werden virtuellen

Ressourcen zugeordnet, die den möglichen Registerzuteilungen entsprechen. Wenn

mit diesen Zuordnungen eine Befehlsanordnung möglich ist, ist garantiert, dass dann

in einem getrennten Schritt die Zuweisung der konkreten Register auf jeden Fall möglich ist. Es werden bei N verschiedenen Registersätzen höchstens 2N − 1 virtuelle

Ressourcen benötigt.

2.1.9

Der TM-1000-Compiler

Im TriMedia-TM-1000-Compiler wird die Befehlsanordnung auf bewachten Entscheidungsbäumen (guarded decision trees) durchgeführt [HoAu99]. Diese sind Bäume

von Grundblöcken, in denen die Wurzel der einzige Punkt ist, an dem diese Menge von Grundblöcken betreten werden kann. Alle anderen Grundblöcke in diesen

Entscheidungsbäumen dürfen nur einen Vorgänger haben. Die Grundblöcke werden

in ihrer Ausdrucksmöglichkeit erweitert, indem sie konditionelle Befehle (predicated

instructions) enthalten dürfen. Die Registerzuteilung wird integriert, indem globale Lebensdauern, die einen einzelnen bewachten Entscheidungsbaum überspannen,

konventionell auf Register zugeteilt werden (Graphenfärbung). Lokale Lebensdauern

werden Registern zugewiesen, sobald in der Befehlsanordnung der erste Befehl davon ausgegeben wird. Der Registerdruck wird dabei heuristisch kontrolliert, indem

dieser auf die Anordnungspriorität Einfluss hat und flexible Anweisungen“ ( floa”

”

ters“) so spät wie möglich ausgegeben werden. Solche flexiblen Anweisungen sind

Blätter des betrachteten DAG und Anweisungen, die nur von genau einem solchen

Blatt abhängen. Bis auf diese Modifikationen wird ein relativ konventioneller Ansatz zur Befehlsanordnung realisiert: Innerhalb des bewachten Entscheidungsbaumes

wird grundblockweise vorgegangen und innerhalb der Grundblöcke wird eine listenbasierte Befehlsanordnung durchgeführt. Es wird in [HoAu99] nicht speziell auf die

Auswirkung der Phasenkopplung eingegangen, da sich die Autoren bei der Auswertung hauptsächlich auf die Befehlsanordnung als solche konzentrieren.

2.2. Auswahl von DSP-Befehlen

2.2

13

Auswahl von DSP-Befehlen

Neben der Phasenkopplung gibt es als weiteres Ziel die Nutzung der bei DSPArchitekturen oft vorhandenen besonderen Befehle für typische DSP-Anwendungen.

Auch wenn diese zum Teil auch bei den oben genannten Methoden zur Phasenkopplung ausgewählt werden (z.B. Multipliziere-und-Addiere-Anweisungen), gibt es

weitere gezielte Ansätze hierfür.

2.2.1

Vektorisierung

Eine typische Klasse von DSP-Befehlen sind datenparallele Berechnungen, z.B. vierfache Addition. Diese Befehle zeigen eine Ähnlichkeit zu den Möglichkeiten von Vektorprozessoren. Von daher ist es prinzipiell möglich, die Optimierungsmethoden für

diese auch für die Auswahl datenparalleler DSP-Befehle zu verwenden. Die Vektorisierung ist bereits lange bekannt, siehe z.B. [Lamp73, Lamp74]. In [Wolf96] sind

die dafür nötigen Grundlagen behandelt: Abhängigkeitsanalyse in Kapitel 5 bis 8,

Schleifenrestrukturierung in Kapitel 9 und automatische Vektorisierung in Kapitel

12.

In [ChLa97] stellen Cheong und Lam exemplarisch für den VIS-Befehlssatz von

Sun eine automatische Codegenerierung für DSP-Befehlssätze vor. Sie verwenden

einen vorhandenen SUIF-basierten Vektorisierer ([KLMT+ 96]), der den ursprünglichen Code auf eine abstrakte Vektormaschine (unbeschränkt viele, unbeschränkt lange Vektorregister; Befehle: Vektor laden, Vektorvergleich, Vektorarithmetik, Vektor

speichern) übersetzt. Daraus wird dann der eigentliche Code erzeugt, indem Streifen

von für den DSP-Befehlssatz passender Größe geschnitten werden und dann die abstrakten Vektorbefehle konkret umgesetzt werden. Dabei werden gegebenenfalls Anpassungen erzeugt, wie die Behandlung von Randbedingungen (Anzahl der Schleifendurchläufe nicht durch die Streifengröße teilbar) oder ungünstiger Datenausrichtung

sowie Formatanpassungen. Wenn aus irgendwelchen Gründen keine DSP-Befehle verwendet werden können, werden wieder konventionelle Schleifen erzeugt.

Auch in [SrGo00] wird als Grundlage SUIF benutzt und damit Code für Intels

Multimedia-Befehlssatzerweiterung MMX erzeugt. Zuerst wird mit Hilfe von Abhängigkeitsanalysen identifiziert, welche Teile überhaupt vektorisierbar sind. Danach

werden die Schleifen in passende Streifen geschnitten. Skalare werden nötigenfalls expandiert und Reduktionen (z.B. Bildung von Summen) transformiert, um die Abhängigkeitsstruktur zu verbessern. Anschließend wird die Schleifenkontrolle neu verteilt

(Loop Distribution) und abschließend wieder C-Code mit eingebettetem Assemblercode ausgegeben. In Benchmarks werden oft deutliche Verbesserungen erreicht.

In [LoWD02] stellen Lorenz, Wehmeyer und Dräger einen Codegenerator vor, der unter Einbeziehung des oben bereits dargestellten genetischen Algorithmus [LLMD+ 01]

(siehe Abschnitt 2.1.3) zusätzlich noch durch Schleifenoptimierungen SIMD-Befehle

und besondere Schleifenkonstrukte von DSPs ausnutzen kann. Es wird zwar eine Methode zur Vektorisierung auf Grundblockebene beschrieben, bei der die auf

Grundblockebene verfügbare Parallelität durch das Ausrollen von Schleifen erhöht

wird und anschließend im Grundblock zu SIMD-Befehlen kombinierbare Einzelbefehle identifiziert werden (nach [Leup00], siehe auch Abschnitt 2.2.3). Die Autoren

14

2. Verwandte Arbeiten

entscheiden sich jedoch gegen diese Methode, weil sie zum einen zu hohe Codegeneratorlaufzeiten erwarten, zum anderen auch die Codegröße durch das Ausrollen

der Schleifen zu groß wird, falls die Vektorisierung auf Grundblockebene für das gegebene Programmstück nicht möglich ist, vgl. [LoWD02], Abschnitt IV A. Daher

entscheiden sich die Autoren von [LoWD02] gegen diesen Ansatz und für klassische

Vektorisierung: Zuerst werden Schleifen analysiert (Identifikation der Grundblöcke

einer Schleife, Induktionsvariablen und Schleifengrenzen). Dann wird durch Abhängigkeitsanalysen festgestellt, ob eine Vektorisierung möglich ist, und diese gegebenenfalls durch Transformationen (z.B. Skalarexpansion, Schleifenteilen) ermöglicht.

Abschließend wird die Vektorisierung in der verwendeten Zwischensprache annotiert.

Die Nutzung von spezifischen Schleifenkonstrukten ist einfach: Wenn die Zahl der

Iterationen einer Schleife statisch bekannt ist, wird die Schleifenkontrolle durch Befehle zur Initialisierung und zum Abschluss der Schleife ersetzt und anschließend

toter Code (Induktionsvariablen) entfernt.

2.2.2

Musterersetzung auf Quelltextebene

In [MaKC99] wird vorgestellt, wie Code für DSP-Befehlssätze (exemplarisch wieder

Suns VIS-Befehlssatz) durch Musterersetzung auf Quelltextebene ausgewählt wird.

Es wird ein programmierbares Codetransformationswerkzeug für ANSI C namens

ctt verwendet. Dieses erlaubt, Muster zu definieren, die in einem Quelltext erkannt

werden. Es können auch weitere Bedingungen angegeben werden. Wenn ein Muster

erkannt und dessen Bedingungen erfüllt sind, wird der Code durch ein in der Regel

angegebenes Fragment ersetzt. In der Beispielanwendung werden z.B. Schleifen zur

Berechnung von Skalarprodukten ersetzt durch eine transformierte Fassung, in der

den VIS-Befehlen entsprechende Funktionsaufrufe generiert werden. Diese werden

dann als Inline-Assembler-Funktionen definiert und damit zu echten DSP-Befehlen

übersetzt. In Benchmarks wurden mittels der Muster laut [MaKC99], Seite 7, 85 %

der SIMD-geeigneten Schleifen tatsächlich erkannt und transformiert.

2.2.3

Integer Linear Programming

In [Leup99] werden zwei Optimierungstechniken für Media-Prozessoren vorgestellt:

Ausnutzung von konditionellen Befehlen (predicated instructions) sowie Verwendung von Multimedia“-Befehlen. Ersteres wird mit dynamischer Programmierung

”

erreicht: Bei geschachtelten Bedingungen gibt es zwei Entscheidungsmöglichkeiten,

nämlich ob konditionelle Anweisungen oder bedingte Sprünge verwendet werden und

ob zusätzlicher Code nötig ist, um äußere Bedingungen immer korrekt einzubeziehen, wenn für diese das Übersetzungsmodell mit konditionellen Anweisungen gewählt

wurde. Es werden zuerst von den inneren Verzweigungen nach außen die Kosten für

die 4 Entscheidungsmöglichkeiten geschätzt. Danach wird von außen nach innen

die Entscheidung endgültig gefällt. Zur Ausnutzung von Multimedia-Befehlen wird

Code aus Datenflussgraphen erzeugt. Diese werden zuerst in Ausdrucksbäume zerschnitten. Jedoch wird für diese dann nicht eine Überdeckung, sondern Mengen von

alternativen Überdeckungen berechnet. Danach wird für alle Teilbäume des Datenflussgraphen simultan ein ganzzahliges lineares Programm konstruiert. Dieses soll die

Verwendung von DSP-Befehlen maximieren. Als Beschränkungen werden erzeugt:

• Die passenden Einzelbefehle müssen vorliegen.

2.3. Zusammenfassung und Bewertung

15

• Abhängigkeiten müssen eingehalten werden.

• Bei Speicherzugriffen müssen die Operanden im Speicher so angeordnet sein,

dass die Lade- oder Speicheroperationen kombiniert werden können und dadurch eine korrekte Platzierung im Register erreicht wird.

Die ILP-Modellierung ist in [Leup00] genauer beschrieben: Für jeden Knoten im

Datenflussgraphen ni gibt es mögliche anzuwendende Regeln rj . Die Entscheidungsvariable xij ∈ {0, 1} besagt, dass an Knoten ni Regel rj ausgewählt wird. Jeder

P

Knoten darf letztlich nur von einer Regel überdeckt werden: ∀i : j xij = 1. Desweiteren müssen die Auswahlen zueinander passen: Wenn nach Auswahl der Regel rj an

Knoten ni in davon abhängigen Knoten nd die Auswahl eingeschränkt wird, wird das

P

von Ungleichungen der Form xij ≤ k xdk , wobei k nur über die nach Auswahl der

Regel rj möglichen Regeln für nd läuft. Desweiteren müssen an gemeinsamen Teilausdrücken die Wahlen der Registerart (gesamtes Register, obere/untere Hälfte, usw.)

konsistent sein, was zu weiteren Gleichungen führt. Weiter gibt es Entscheidungsvariablen yij für die Kombination von SIMD-Teilbefehlen für alle möglicherweise kombinierbaren Paare von Knoten (ni , nj ). Diese werden in Beziehung gesetzt damit,

dass falls yij = 1 für ni eine Regel ausgewählt sein muss, die die obere Registerhälfte

berechnet, und dass für nj eine Regel ausgewählt sein muss, die die untere Registerhälfte berechnet. Auch können Knoten höchstens in ein solches Paar eingeordnet

werden. Desweiteren werden zyklische Abhängigkeiten für die Befehlsanordnung vermieden: Falls ni → nj , nk → nl , können nicht gleichzeitig Paare (ni , nl ) und (nj , nk )

gebildet werden. Dies kann auch für andere Arten von SIMD-Befehlen erweitert werden. In [LeBa00] wird zu dieser Methode ausgesagt, dass die Rechenzeiten für größere

Probleme lange werden und als Lösung vorgeschlagen, große Datenflussgraphen in

kleinere zu zerteilen und getrennt zu behandeln. In [Leup00], Seite 5 sind genauere

Ergebnisse genannt. Die Laufzeiten der Codegenerierung gehen bis zu einer halben

Minute für Graphen mit 95 Knoten.

2.3

Zusammenfassung und Bewertung

Die vorgestellten verwandten Arbeiten zur Phasenkopplung fassen wir in Tabelle 2.1,

die zur Identifikation von SIMD-Befehlen in Tabelle 2.2 zusammen. In Tabelle 2.1

bedeutet Aus“ die Befehlsauswahl, An“ die Anordnung und Reg“ die Registerzu”

”

”

teilung. In einigen Arbeiten ist nicht klar ersichtlich, wie gut die Anpassung auf neue

Architekturen (Retargierung) unterstützt wird. In diesem Falle geben wir ein ?“ an,

”

während wir −“ angeben, wenn eine Arbeit sich von vornherein auf eine bestimmte

”

Architektur konzentriert hat. In der Spalte Zeit“ fassen wir das Laufzeitverhalten

”

zusammen. Wir sehen Laufzeiten im Bereich von Sekunden oder Minuten als akzeptabel an und bezeichnen dies mit +“, wesentlich längere Laufzeiten dagegen mit

”

−“. Wo in den Arbeiten keine Aussage über die Codegeneratorlaufzeiten getroffen

”

wird, geben wir ein ?“ an.

”

Die meisten Arbeiten werden der Anforderung, direkt aus möglicherweise zyklischen

Graphdarstellungen, insbesondere SSA-Graphen, Code zu erzeugen, nicht gerecht, da

sie auf baumbasierten oder DAG-Darstellungen arbeiten. Bei der ILP-basierten Arbeit von Wilson et. al. [WGHB95] sind die Laufzeiten der Codegenerierung zu groß.

Im Mutation-Scheduling [NoNi95] wird zwar auf einer modifizierten SSA-Darstellung

16

2. Verwandte Arbeiten

Arbeit

ILP [WGHB95]

PROPAN [Käst97]

CLP

[BaLe99b, BaLe99a]

Genetisch [LLMD+ 01]

DP [KeBe01]

AVIV [Hano99, HaDe98]

Mutation [NoNi95]

SW-Pipelining

[MSTM+ 97]

SW-Pipelining [PiME99]

Register als Funktionseinheiten [ZeWe01]

TM-1000 [HoAu99]

Phasen

Aus+An+Reg

An+Reg

Aus+An+Reg

zykl. Graph

+

−

−

Retargierbarkeit

?

+

+

Zeit

−

+

+

Aus+An+Reg

Aus+An

Aus+An+Reg

Aus+An+Reg

An+Reg

−

−

−

+

(+)

?

?

?

?

?

+

−

+

?

+

An+Reg

An+Reg

(+)

−

?

?

+

?

An+Reg

−

?

?

Tabelle 2.1: Arbeiten zur Phasenkopplung

Arbeit

Vektorisierung für VIS [ChLa97]

Vektorisierung für MMX [SrGo00]

Vektorisierung [LoWD02]

Musterersetzung [MaKC99]

ILP [Leup99, Leup00]

zykl. Graph

−

−

−

−

−

Retargierbarkeit

−

−

?

+

?

Zeit

?

?

?

?

+

Tabelle 2.2: Identifikation von SIMD-Befehlen

gearbeitet, jedoch nicht genau angegeben, wie die Zyklen behandelt werden. Die

Techniken auf der Basis von Software-Pipelining ([MSTM+ 97] und [PiME99]) behandeln zwar Zyklen, aber nur auf innere Schleifen spezialisiert. Daher kann nur

eingeschränkt davon die Rede sein, dass sie zyklische Graphen behandeln.

Bisher erfolgt die Auswahl von SIMD-artigen Befehlen entweder auf Quelltext- bzw.

Zwischensprachebene (Vektorisierung, Musterersetzung auf Quelltextebene) oder es

werden besondere Techniken im Rahmen der Codegenerierung eingesetzt (Abschnitt

2.2.3).

Auch wenn die Identifikation von SIMD-Parallelität auf höherer Abstraktionsebene

wie z.B. im Quelltext (bzw. im abstrakten Syntaxbaum) oder in der Zwischensprache notwendig ist, um komplexere Analysen durchführen zu können, erwarten wir,

dass sich auch weitere Möglichkeiten der SIMD-Parallelität erst auf der Ebene der

Codeerzeugung ergeben.

Die Methode von Leupers [Leup99] (s. Abschnitt 2.2.3) ist spezialisiert auf die Erkennung von SIMD-Befehlen. Sie integriert dies jedoch nicht mit den allgemeineren

Aufgaben der Befehlsauswahl. Hierfür wird auf traditionelle Baumüberdeckung zurückgegriffen.

2.3. Zusammenfassung und Bewertung

17

Wir wollen im weiteren Verlauf dieser Arbeit zeigen, wie wir die zwei Teilprobleme

der Phasenkopplung zwischen Befehlsauswahl und -anordnung und der Identifikation

von SIMD-Befehlen in einem integrierten Ansatz lösen können.

18

2. Verwandte Arbeiten

3. Grundlagen

Im Folgenden stellen wir vor, auf welche Grundlagen wir zurückgreifen konnten, um

die für diese Arbeit gesteckten Ziele zu erreichen. Dies umfasst auch die Ergebnisse

von Boesler [Boes98], der bereits das Problem der Codegenerierung aus graphbasierten SSA-Darstellungen gelöst hat.

Zuerst beschreiben wir die verwendete Zwischensprache Firm, eine graphbasierte

SSA-Darstellung, vgl. Abschnitt 3.1. Dann erklären wir das Prinzip der Befehlsauswahl aus Graphen mit Hilfe von Bottom Up Rewrite Systems (BURS). Die Graphersetzung steuern wir mit heuristischer Suche, deren Grundlagen wir im Abschnitt 3.3

erläutern. Dann gehen wir auf die Maschinensimulation zur Befehlsanordnung ein,

siehe Abschnitt 3.4. Dieses Kapitel schließen wir mit einer kurzen Darstellung über

einen Algorithmus zur Erkennung von SIMD-Befehlen. Dessen Grundidee greifen wir

auf, setzen sie aber anders um.

3.1

Die SSA-Darstellung Firm

SSA-Darstellungen erlauben, interessante Optimierungen auf Zwischensprachebene effizient durchzuführen. Daher wurden an unserem Institut eine graphbasierte

Zwischendarstellung in SSA-Form namens Firm (Firm Intermediate Representation Mesh) [TrLB99] und eine Bibliothek zur Erzeugung und Bearbeitung derselben

[Lind02] entwickelt.

Die bezeichnende Eigenschaft von SSA-Darstellungen ist die statische Einmalzuweisung: Jede Variable wird genau an einer Stelle des Zwischenprogrammcodes zugewiesen. Wenn im Quelltext mehrere Zuweisungen an eine Variable auftreten, so muss

diese bei der Herstellung der SSA-Form an jeder dieser Zuweisungen umbenannt

werden. Die Verwendungen der Variable werden dann entsprechend angepasst.

Als Beispiel betrachten wir den Ausschnitt aus dem Euklidischen Algorithmus:

20

3. Grundlagen

if x < y

then

y := y − x

else

x := x − y

Verwendung von x und y . . .

Da x und y schon am Eingang dieses Codestücks Werte haben, müssen wir diesen

Werten auch eigene Namen geben. Damit ergibt sich:

if x1 < y1

then

y2 := y1 − x1

else

x2 := x1 − y1

Verwendung von x und y . . . ← ???

Jedoch können bei der Verwendung in der letzten Zeile verschiedene Versionen von

x bzw. y gültig sein, je nachdem, welcher Zweig der bedingten Verzweigung gewählt

wurde. Damit kann bei der Verwendung bis jetzt nicht angegeben werden, welcher

Name hier stehen soll.

Daher wird in einem solchen Fall, wenn zwei oder mehrere verschiedene Versionen

einer Variable einen Grundblock erreichen können, eine neue Operation eingefügt, die

sogenannte Phi-Auswahlfunktion. Die Operanden dieser Phi-Funktion entsprechen

den Werten in den Vorgängern des Grundblocks, der die Phi-Operation enthält. Das

Ergebnis wird einer neuen Version der Variablen zugewiesen, die dann im Rest des

Grundblocks einheitlich verwendet werden kann:

if x1 < y1

then

y2 := y1 − x1

else

x2 := x1 − y1

x3 := Φ(x1 , x2 )

y3 := Φ(y2 , y1 )

Verwendung von x3 und y3 . . .

Hiermit wird also dieses Problem behoben, es kann immer x3 bzw. y3 verwendet

werden.

In [CFRW+ 91] sind Algorithmen angegeben, wie man eine solche Darstellung effizient konstruieren und später zur Codeerzeugung die Phi-Operationen korrekt behandeln kann.

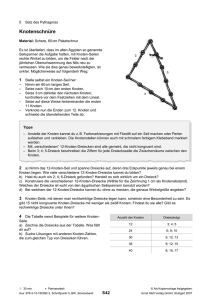

Die Darstellung Firm ist eine SSA-Darstellung, die Kontroll- und Datenfluss gemeinsam als Graph darstellt. Für das oben verwendete Codebeispiel hat der Graph die

in Abbildung 3.1 gezeigte Form.

Im Zusammenhang mit Schleifen wird der Graph zyklisch. Und zwar entstehen sowohl Kontrollflusszyklen, die aus Blockknoten sowie Sprung- oder Verzweigungsknoten (Jmp bzw. Cond) bestehen, als auch gegebenenfalls Datenflusszyklen, die jeweils

mindestens einen Phi-Knoten enthalten.

3.2. BURS

21

Block

Cmp

x(in)

y(in)

ProjLT

Cond

Block

Block

Sub

Sub

Jmp

Jmp

Block

Phi

x(out)

Phi

y(out)

Abbildung 3.1: SSA-Beispielgraph

Auch Abhängigkeiten, die durch Speicherzugriffe entstehen, werden ausdrücklich

dargestellt, indem ein besonderer Wert, der Speicherzustand, als zusätzliche Einund Ausgabe der Lade- und Speicheroperationen fungiert.1

3.2

BURS

Ein modernes Verfahren zur Codeerzeugung ist die Anwendung von Bottom Up

Rewrite Systems (BURS) [Pele88, NyKa97, NKWA96]. Boesler hat dieses Verfahren

auf Graphen erweitert, vgl. [Boes98], Seiten 39 ff.

3.2.1

Kostenbehaftete Termersetzungssysteme

Die Grundlage für BURS sind kostenbehaftete Termersetzungssysteme, siehe auch

die Darstellung in [Boes98], Seiten 19 f. Hierfür wird zunächst der Begriff von Termen

definiert.

Definition 3.1 (Alphabet mit Rang) Ein Alphabet mit Rang ist ein Paar Σ =

(S, r) mit einer endlichen Menge von Symbolen S und einer Funktion r : S → IN .

Die Menge S wird auch die Menge der Operatoren genannt. Zu einem Operator

a ∈ S gibt die Zahl r(a) dessen Rang (Stelligkeit) an. Wir bezeichnen Alphabete

mit Rang auch kurz mit dem Begriff Alphabet.

1

Durch Aliasanalysen kann der Speicherzustand tatsächlich noch differenziert werden, damit die

Reihenfolge voneinander unabhängiger Speicherzugriffe nicht zu früh festgelegt wird.

22

3. Grundlagen

Wenn man hierzu noch eine Menge V von Symbolen (Variablen), die zu S disjunkt

ist, wählt, kann man Terme definieren:

Definition 3.2 (Terme) Für ein Alphabet Σ und eine Menge von Variablen V ist

die Menge der Terme TΣ (V ) wie folgt induktiv definiert:

1. Jede Variable v ∈ V ist ein Term, d.h. V ⊂ TΣ (V ).

2. Jeder Operator a ∈ S mit r(a) = 0 ist ein Term, d.h. {a|a ∈ S, r(a) = 0} ⊂

TΣ (V ).

3. Für jeden Operator a ∈ S mit r(a) > 0 und Terme t1 , . . . , tr(a) ∈ TΣ (V ) ist

auch a(t1 , . . . , tr(a) ) ∈ TΣ (V ).

4. Außer den so definierten Termen hat TΣ (V ) keine weiteren Elemente.

Die Menge der in einem Term t tatsächlich auftretenden Variablen wird mit V ar(t)

bezeichnet.

Definition 3.3 (Grundterm) Ein Term ohne Variablen, also mit V ar(t) = ∅,

heißt Grundterm.

Im weiteren betrachten wir nur Grundterme, d.h. V = ∅, und kürzen ab: TΣ := TΣ (∅).

Definition 3.4 (Positionen) Eine Position in einem Term ist eine möglicherweise leere Folge von positiven ganzen Zahlen. Die leere Folge schreiben wir , die Konkatenation bezeichnen wir mit ·. Damit ist die Menge der Positionen eines Terms

P os(t) wie folgt definiert:

1. Für t = a mit r(a) = 0: P os(t) := {}

2. Für t = a(t1 , . . . , tr(a) ): P os(t) := {} ∪ 1 · P os(t1 ) ∪ . . . ∪ r(a) · P os(tr(a) ).

Definition 3.5 (Teilterme) Zu einem Term t ist der Teilterm an der Position p,

t|p , wie folgt definiert:

1. t| := t

2. Für t = a(t1 , . . . , tr(a) ) ist t|k·p0 := tk |p0

Damit kann man kostenbehaftete Grundtermersetzungssysteme wie folgt definieren.

Definition 3.6 (Kostenbehaftetes Termersetzungssystem) Ein kostenbehaftetes Grundtermersetzungssystem, kurz mit kostenbehaftetes Termersetzungssys”

tem“ bezeichnet, ist ein Tripel (Σ, R, C) mit

1. einem nicht leeren Alphabet Σ,

3.3. Heuristische Suche

23

2. einer Menge von Regeln R ⊂ TΣ × TΣ , so dass für alle Regeln (t, t0 ) ∈ R gilt

t 6= t0 , und

3. einer Kostenfunktion C : R → IR≥0 .

Eine Regel r = (t, t0 ) ∈ R kann auf einen Term t0 angewendet werden (Ersetzung),

indem ein Teilterm von t0 , der gleich zu t ist, durch t0 ersetzt wird. Der Rest von t0

bleibt hierbei unverändert. Wenn der Teilterm an Position p ersetzt wird, kann dies

so geschrieben werden: hr, pit0 = t1 .

Durch wiederholte Regelanwendungen können ganze Ersetzungssequenzen definiert

werden. Die Kosten werden als die Summe der Kosten der einzelnen Regeln definiert.

3.2.2

Übertragung auf BURS

BURS wird durch eine Einschränkung dieser Grundtermersetzungssysteme definiert:

Nach der Ersetzung eines bestimmten Teilterms dürfen die darin enthaltenen Teilterme nicht weiter bearbeitet werden, die Ersetzung erfolgt also von unten“ nach

”

oben“. Anders ausgedrückt: Wenn eine Regelanwendung hr1 , p1 i vor einer Regelan”

wendung hr2 , p2 i kommt, ist entweder p1 = p2 oder p1 ist kein Präfix von p2 . Im

ersten Fall müssen auch alle dazwischen liegenden Regelanwendungen an derselben

Position stattfinden. Desweiteren muss eine obere Schranke k existieren, so dass für

jeden Eingabeterm an jeder Position höchstens k Ersetzungen möglich sind.

Die Codeerzeugung erfolgt, indem an die Termersetzungsregeln zusätzlich Befehlsmuster gekoppelt werden, die bei der Anwendung einer Regel in das Maschinenprogramm ausgegeben werden.

Die Erweiterung auf gerichtete azyklische Graphen (DAGs) ist einfach ([Boes98],

Seiten 42 f.). Zyklen werden bei der Berechnung der möglichen Ersetzungssequenzen

an bestimmten Stellen (Block-Knoten für Kontrollflusszyklen, Phi-Knoten für Datenflusszyklen) aufgebrochen, was in [Boes98], Seiten 43 ff. beschrieben wird. Damit

wird die Codeerzeugung direkt aus SSA-Graphen ermöglicht.

3.3

Heuristische Suche

Während Pelegrı́-Llopart [Pele88] aus BURS-Spezifikationen Automaten vorberechnet, die letztlich die tatsächlich verwendeten Ersetzungen berechnen, haben Nymeyer

und Katoen [NyKa97, NKWA96] stattdessen einen Ansatz verfolgt, der zunächst alle

möglichen Ersetzungssequenzen berechnet und dann mit Hilfe heuristischer Suche

die günstigste auswählt. Auch Boesler [Boes98] hat diese Methode gewählt und dabei gegenüber der Arbeit von Nymeyer und Katoen noch einige Verbesserungen

vorgenommen.

3.3.1

Suchproblem

Viele Probleme lassen sich als Suchprobleme darstellen. Ein Suchproblem besteht

darin, in einem sogenannten Suchgraphen einen möglichst guten“ Pfad von einem

”

definierten Initialknoten zu einem Zielknoten zu finden. Dies stellt sich formal so

dar:

24

3. Grundlagen

Definition 3.7 (Suchgraph) Ein Suchgraph ist ein Tupel

(N, E, n0 , Ng , C)

mit folgenden Eigenschaften:

1. (N, E) ist ein verbundener gerichteter azyklischer Graph.

2. Der Initialknoten n0 ∈ N ist die Wurzel des Graphen, d.h. für jedes n ∈ N

existiert ein gerichteter Pfad von n0 nach n, aber es existiert kein Pfad von

einem n ∈ N \ {n0 } nach n0 .

3. Die Menge der Zielknoten Ng ⊂ N ist nicht leer.

4. Es gibt keine Kanten, die von Zielknoten ausgehen:

∀ n ∈ Ng : ¬ ∃ m ∈ N : (n, m) ∈ E.

5. Die Kostenfunktion C : E → IR≥0 bildet jede Kante auf die ihr zugeordneten

Kosten ab. Die Kostenfunktion wird additiv auf Pfade erweitert.

6. Es gibt keine unendlich langen Pfade mit endlichen Kosten.2

In der Anwendung auf BURS repräsentiert ein Knoten im Suchgraphen (Suchknoten)

einen Zustand des Graphen, auf den BURS angewendet wird. Der Initialknoten

n0 entspricht also dem Eingabegraphen. Zielknoten entsprechen den gewünschten

Ergebnissen der Graphersetzung, also üblicherweise dem Zustand, wenn der Graph

auf einen einzelnen Knoten reduziert ist. Eine Kante im Suchgraphen entspricht der

Anwendung einer Ersetzungsregel und damit der Ausgabe eines Maschinenbefehls.

Definition 3.8 (Suchproblem) Das Problem, in einem Suchgraphen einen Knoten ng ∈ Ng und einen Pfad von n0 nach ng nach finden, so dass die Kosten dieses

Pfades minimal sind, nennt man Suchproblem.

Da dieses Problem oft schwierig ist, können auch Approximationen vorgenommen

werden. Dann wird ein Knoten ng ∈ Ng und ein Pfad von n0 nach ng gesucht, jedoch

wird gegebenenfalls hingenommen, dass die Kosten nicht minimal sind.

3.3.2

Grundalgorithmus

Die meisten Suchalgorithmen haben folgende grundlegende Struktur:

Algorithmus 3.1 (Suchalgorithmus)

Eingabe:

Suchgraph wie oben definiert

Ausgabe:

Gefundener Zielknoten ng ∈ Ng ,

ein Pfad von n0 nach ng .

Lokale Variablen: Menge offener Knoten NO ⊂ N ,

Menge geschlossener Knoten NC ⊂ N ,

partielle Abbildung prev : N → N

2

Diese Beschränkung schließt Suchgraphen aus, in denen die Kosten auf einem Pfad z.B. die

Folge ( 12 , 14 , 18 , . . .) darstellen und so trotz Vorhandenseins zum Beispiel einer Lösung mit Kosten 2

in endlicher Tiefe auch eine A∗ -Suche gegebenenfalls nie terminiert.

3.3. Heuristische Suche

25

1. Der Initialknoten wird in die Menge offener Knoten aufgenommen (NO :=

{n0 }). Die Menge geschlossener Knoten ist anfangs leer (NC := ∅) und die

Funktion prev nirgends definiert.

2. In einer Schleife werden folgende Schritte durchlaufen:

(a) Wähle einen Knoten n aus NO aus. Wenn die Menge offener Knoten leer

ist, ist die Suche fehlgeschlagen.

(b) Wenn n ∈ Ng ist, wird diese Lösung (Zielknoten und der gefundene Pfad

vom Initialknoten zum Zielknoten, letzterer mit Hilfe von prev) ausgegeben. Falls mehrere Lösungen gesucht werden, kann der Algorithmus dann

fortgesetzt werden, sonst terminiert er hier.

(c) Verschiebe n aus NO nach NC .

(d) Für alle Nachfolger m von n:

• Falls m ∈ NC : Wenn der neu gefundene Pfad von n0 nach m günstiger als der durch prev spezifizierte ist, dann setze prev(m) := n und

verschiebe m aus NC wieder nach NO ; sonst tue nichts.

• Falls m ∈ NO : Wenn der neu gefundene Pfad von n0 nach m günstiger als der durch prev spezifizierte ist, dann setze prev(m) := n;

sonst tue nichts.

• Sonst: Setze prev(m) := n und füge m in NO ein.

Falls n ∈ Ng , bewirkt dieser Schritt nichts, da solche n keine Nachfolger

haben (Eigenschaft 4 in Definition 3.7).

Es wird angenommen, dass ein Knoten nur endlich viele Nachfolger hat. Damit ist

die Menge der Knoten in dem Suchgraphen aufzählbar.

Vergleiche auch die Darstellung in [Gins93], Seite 22.

In der Praxis wird meist dynamisch nur der Teil des Suchgraphen berechnet, der

während der Suche auch betrachtet wird: Der Initialknoten wird in Schritt 1 berechnet und in Schritt 2d werden zu dem gerade betrachteten Knoten die Nachfolger

und die Kanten zu diesen Nachfolgern bestimmt und dem Graphen hinzugefügt.

Die einzelnen Suchverfahren unterscheiden sich hauptsächlich durch die Wahl des

nächsten zu bearbeitenden Knotens in Schritt 2a und dadurch, ob mehrere Lösungen

bestimmt werden (Schritt 2b).

Bei uninformierten Suchverfahren wird diese Wahl nur durch die Position des Knotens im Suchgraphen und/oder die Reihenfolge des Einfügens in die Menge offener

Knoten bestimmt. Zum Beispiel ist eine Breitensuche so aufzufassen, dass die Menge

offener Knoten als Schlange organisiert ist. Bei einer Tiefensuche dagegen wird sie

als Keller verwendet.

Bei informierten Suchverfahren dagegen fließt Wissen aus dem Anwendungsgebiet

in die Auswahl in Schritt 2a ein. Dieses Wissen wird oft als Heuristik bezeichnet,

die Suchverfahren als heuristische Suche.

26

3. Grundlagen

3.3.3

Heuristische Suchverfahren

Für einen Knoten n ∈ N werden folgende Bezeichnungen eingeführt:

• g(n) sind die Kosten eines günstigsten Pfades von n0 nach n.

• h(n) sind die Kosten eines minimalen Pfades von n zu einem günstigsten von

n aus erreichbaren Zielknoten ng ∈ Ng .

• h∗ (n) ist eine heuristische Abschätzung von h(n).

• f (n) := g(n) + h(n) und f ∗ (n) := g(n) + h∗ (n).

Ein einfaches Beispiel heuristischer Suche wird von h∗ (n) gesteuert: In der Best”

first“-Suche wird als Nächstes ein n ∈ NO mit minimalem h∗ (n) bearbeitet ([Gins93],

Seite 71).3

Algorithmen des Typs A ([Farr88], Seiten 22 ff.) steuern die Suche dagegen, indem

bei der Auswahl eines Knotens n aus NO die Summe von g(n) und h∗ (n), also f ∗ (n),

minimiert wird.

Falls die Heuristik die tatsächlichen Kosten nie überschätzt, also für alle n ∈ N gilt:

h∗ (n) ≤ h(n), spricht man von einem Algorithmus des Typs A∗ ([Farr88], Seite 25).

Die Heuristik h∗ (n) nennt man in diesem Falle zulässig oder auch optimistisch.4

Satz 3.1 Wenn ein Zielzustand ng ∈ Ng existiert, für den es einen Pfad endlicher

Länge von n0 nach ng gibt, terminiert ein Suchalgorithmus vom Typ A∗ und findet

eine Lösung mit minimalen Kosten.

Zum Beweis verweisen wir auf die Literatur, z.B. [Gins93], Seiten 78 f.

Mit h∗ (n) = 0 für alle n wird die Suche zu einer Art von Breitensuche.5 Wenn dagegen h∗ (n) = h(n) für alle n und bei gleichen f ∗ (n) tiefer im Graphen gelegene n

bevorzugt werden, findet der A∗ -Algorithmus direkt den Weg zu einer optimalen Lösung. Gibt es dagegen n ∈ N mit h∗ (n) > h(n), ist es möglich, dass der Algorithmus

einen Knoten ng ∈ Ng mit nicht minimalem Pfad findet.

Es gibt weiterhin die Varianten Ae∗ , wo nur h∗ (n) ≤ h(n) + e (e > 0) gefordert wird

und Aα∗ , wo nur h∗ (n) ≤ h(n) · (1 + α) (α > 0) gefordert wird. Ein Ae∗ -Algorithmus

findet eine Lösung, deren Kosten das Optimum um höchstens e übersteigen. Bei

einem Aα∗ -Algorithmus liegen die Kosten höchstens um einen Faktor von (1 + α)

über dem Optimum.

In den Arbeiten von Nymeyer und Katoen [NyKa97] sowie von Boesler [Boes98]

wird ein A∗ -Algorithmus eingesetzt und damit, in den Grenzen der jeweils zugrunde

liegenden Modellierung, eine optimale Lösung gefunden. Die Heuristikfunktion h∗ (n)

3

Zu beachten ist, dass der hier verwendete Begriff von Best-first“-Suche, der von [Gins93]

”

abgeleitet ist, etwas anderes bedeutet als der Begriff Best-first“-Suche in [NyKa97] oder [Boes98].

”

4

Heuristiken, die die Kosten nie unterschätzen, also pessimistisch sind, verwenden wir in dieser

Arbeit nicht.

5

Dieser Fall ist der, der in [NyKa97, Boes98] als Best-first“-Suche bezeichnet wird. Die Suche

”

wird allein durch g(n) gesteuert.

3.4. Befehlsanordnung

27

wird aus den Kosten (bzw. bei variablen Kosten aus Angaben der minimalen Kosten)

der einzelnen Befehle berechnet. Das Verfahren hierfür ist in [Boes98] auf Seite 49

angegeben.

Dagegen verfolgen wir in dieser Arbeit auch eine alternative Suchstrategie, die es

ermöglicht, Approximationen zu berechnen. Dafür ist dieses Suchverfahren oft wesentlich schneller. So können wir einen Kompromiss zwischen der Geschwindigkeit

des Codegenerators und der Qualität des erzeugten Codes wählen.

Als Grundlage hierfür haben wir das Verfahren ein Weg, dann vom Besten aus“

”

(One-Then-Best-Backtracking, siehe [Bund97], Nr. 186) herangezogen. Hierbei wird

vom Startzustand aus in einem gierigen Verfahren in die Tiefe gegangen, bis entweder

eine Lösung oder eine Sackgasse (d.h. ein Knoten, der keine Nachfolger hat, aber auch

kein Zielknoten ist) gefunden wird. Dann wird irgendeiner der dabei auch erzeugten

Knoten (d.h. Geschwister der bereits besuchten Knoten) ausgewählt. Im Gegensatz

zu einfacheren Verfahren mit Zurücksetzen (Backtracking) wird diese Auswahl aber

heuristisch gesteuert. Die Details arbeiten wir in Abschnitt 4.4 aus.

Es ist zu beachten, dass dieses Suchverfahren bei unendlich großen Suchgraphen

möglicherweise auch dann nicht terminiert, wenn eine Lösung in endlicher Tiefe existiert. Dies ist für uns jedoch wegen der BURS-Eigenschaft, dass an jeder Position

nur beschränkt viele Ersetzungsschritte möglich sind, nicht der Fall: die Suchgraphen sind zwar oft sehr groß aber endlich. In endlichen Suchgraphen findet jede

Instantiierung des Grundalgorithmus 3.1 natürlich eine Lösung.

3.4

Befehlsanordnung

Für die Erzeugung guten Maschinencodes ist es nötig, die Befehle gut anzuordnen.

Zum Beispiel kann so dafür gesorgt werden, dass Prozessorpipelines gut gefüllt bleiben und dabei Strukturkonflikte, wie z.B. der zu frühzeitige Zugriff auf einen Wert,

der aus dem Speicher gelesen wird, vermieden werden. Auch sollen mehrfach vorhandene Funktionseinheiten möglichst gut ausgenutzt werden.

Daher koppeln wir in dieser Arbeit die Befehlsauswahl, die bereits Boesler [Boes98]

für SSA-Graphen realisiert hat, mit der Befehlsanordnung. Außerdem zeigen wir, wie

mit Hilfe dieser Phasenkopplung auch SIMD-Parallelität identifiziert werden kann.

Boesler hat in seiner Diplomarbeit bereits näher beschrieben, wie diese Kopplung

stattfinden kann ([Boes98], Seiten 28 f.), dies jedoch nicht implementiert. Die von

Boesler vorgeschlagene Klassenbildung von Befehlen ([Boes98], Seite 48) verfolgen

wir hier nicht weiter, da eine solche Klasseneinteilung gerade in Hinblick auf die

Behandlung von Lade- und sonstigen Ergebnislatenzen, aber auch bei der Abhängigkeitsprüfung für die Identifikation von SIMD-Befehlen nicht haltbar ist. Es kann

während der Suche (Abschnitt 3.3) bei den Knoten im Suchgraphen zusätzlich zum

Zustand des Programmgraphen noch ein Maschinenzustand gehalten werden, der den

Zustand der Pipeline bzw. Funktionseinheiten sowie Informationen zur Identifikation von Strukturkonflikten darstellt. Dadurch kann die Kostenfunktion so bemessen

werden, dass sie Verzögerungen und Gewinne durch die Befehlsanordnung aufzeigt.

Zum Beispiel entstehen höhere Kosten durch Strukturkonflikte, sei es, dass der Prozessor die Ausführung verzögert oder dass NOP-Befehle eingefügt werden müssen,

um überhaupt eine korrekte Programmausführung zu erreichen. Gewinne entstehen,

28

3. Grundlagen

indem Parallelität auf Befehlsebene ausgenutzt wird, wozu auch SIMD-Befehle zählen.

Diese Kostenfunktion wird durch eine Maschinensimulation berechnet, siehe z.B.

[Müll95]. Es gibt eine Menge von Maschinenzuständen Q und eine Menge von Maschinenbefehlen I. Die Simulation besteht aus einem Paar von Funktionen cost :

Q × I → IR≥0 und δ : Q × I → Q.6 Die Funktion cost bestimmt, welche Kosten es

verursacht, in dem gegebenen Maschinenzustand den angegebenen Befehl abzusetzen. Der sich dadurch ergebende neue Maschinenzustand wird von δ berechnet. Dies

fassen wir später in Definition 4.3 noch einmal formal.

3.5

Erkennung von SIMD-Befehlen

In [GlGB02] stellen Glesner, Geiß und Boesler einen Algorithmus zur automatischen

Erzeugung von SIMD-Befehlen vor. Sie verwenden dabei Beschränkungen erzeugende Graphersetzungssysteme ([GlGB02], Abschnitt 3). Den Ersetzungsregeln werden

zusätzlich zu dem Code, der erzeugt wird, Beschränkungen (Variablen und Prädikate) zugeordnet, wobei für jede Regelanwendung durch Umbenennung frische Variablen erzeugt werden. Es werden Teilbefehle von SIMD-Befehlen (z.B. die einzelne

Addition einer Vierfach-Addition) erkannt. Diese werden durch eine Kostenfunktion bevorzugt, die solche Teilbefehle besonders günstig bewertet, in der Erwartung,

dass diese zu effizienten SIMD-Befehlen kombiniert werden können. Zugleich werden Beschränkungen ausgegeben, die sicher stellen, dass diese Teilbefehle entweder

gleichzeitig als Teil desselben SIMD-Befehls oder sequentiell ausgeführt werden und

dass die Maximalzahl der Teilbefehle eines SIMD-Befehls nicht überschritten wird.

In einer Nachbearbeitung, die mit der Befehlsanordnung zusammen ausgeführt wird,

werden die Teilbefehle unter Beachtung dieser Beschränkungen zu SIMD-Befehlen

kombiniert. Es wird angedeutet, dass man die Zuteilung der entsprechenden Teile

der SIMD-Register bzw. Vektorregister mit einer ähnlichen Methode lösen kann: Es

werden weitere Variablen und Beschränkungen erzeugt, die bei der Registerzuteilung

ausgewertet werden. In [GlGB02], Abschnitt 5, stellen die Autoren weiterhin einen

Checking-Algorithmus zur Verifikation dieser Übersetzung vor.

Im Weiteren zeigen wir, wie wir die in diesem Kapitel erläuterten Grundlagen verwenden und anpassen, um mit Hilfe von zustandsbehafteten Grundtermersetzungssystemen eine Maschinensimulation in die Codeerzeugung einzubinden.

6

Die verwendeten Funktionssymbole sind in [Müll95] andere. Wir verwenden das Symbol δ, das

für Zustandsübergangsfunktionen üblich ist, und den anschaulichen Namen cost.

4. Effiziente Phasenkopplung mit

zustandsbehafteter

Termersetzung

In diesem Kapitel erarbeiten wir die theoretischen Grundlagen für die Phasenkopplung zwischen Befehlsauswahl und -anordnung. In Abschnitt 4.1 erweitern wir die

kostenbehafteten Grundtermersetzungssysteme zu zustandsbehafteten Grundtermersetzungssystemen. Wir entwickeln dann ein Verfahren, wie wir mit diesem Instrument eine Maschinensimulation anbinden und damit die gewünschte Kopplung

erreichen, siehe Abschnitt 4.2.