Versuch EL-V8: Aufbau einer Phasenregelschleife für Mobilfunkgeräte

Werbung

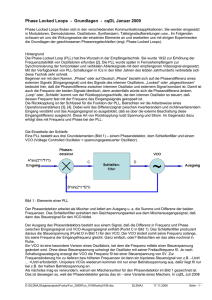

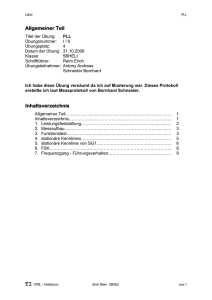

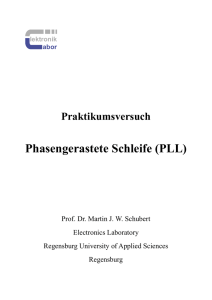

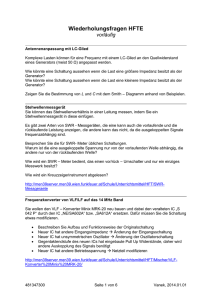

Versuch EL-V8: Aufbau einer Phasenregelschleife für Mobilfunkgeräte Inhaltsverzeichnis 1 2 3 Einführung 1.1 Aufgabe einer Phasenregelschleife . 1.2 Aufbau und Funktionsweise . . . . 1.3 Modellierung . . . . . . . . . . . . 1.4 Schleifenordnung und Schleifentyp . . . . . . . . . Komponenten von Phasenregelschleifen 2.1 Spannungsgesteuerter Oszillator (VCO) 2.2 Frequenzteiler . . . . . . . . . . . . . . 2.3 Phasen-Frequenz-Detektor (PFD) . . . 2.4 Ladungspumpe (CP) . . . . . . . . . . 2.5 Schleifenfilter . . . . . . . . . . . . . . Messaufgaben 3.1 Messaufgabe VCO . . . . . 3.2 Messaufgabe Teiler . . . . . 3.3 Messaufgabe PFD mit CP . . 3.4 Messaufgabe Schleifenfilter . 3.5 Messaufgabe PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Literaturverzeichnis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 2 2 4 7 . . . . . 8 8 13 14 18 18 . . . . . 23 23 25 27 28 30 31 EL-V8 - 1 PLL 1 1 EINFÜHRUNG Einführung 1.1 Aufgabe einer Phasenregelschleife Eine Phasenregelschleife (PLL, phase locked loop) dient im Allgemeinen zur Erzeugung einer stabilen, einstellbaren Frequenz. Prinzipiell könnte man für diese Aufgabe lediglich einen spannungsgesteuerten Oszillator (VCO, voltage controlled oscillator) verwenden, der je nach angelegter Spannung eine bestimmte Ausgangsfrequenz erzeugt. Dabei tritt jedoch das Problem auf, dass die Frequenz eines freilaufenden, ungeregelten Oszillators nicht präzise ist, sondern aufgrund von äußeren Einflüssen wie z.B. Temperatur, Alterung oder Bauelementtoleranzen Schwankungen von einigen Prozent aufweist. Die Aufgabe der PLL besteht darin, diese Frequenzschwankungen auszuregeln und dadurch die Schwingung des spannungsgesteuerten Oszillators zu stabilisieren. 1.2 Aufbau und Funktionsweise Im Allgemeinen besteht eine PLL aus einem Phasen-Frequenz-Detektor (PFD, phase frequency detector), einer Ladungspumpe (CP, charge pump), einem Schleifenfilter, einem VCO und einem Frequenzteiler. Ein typisches Blockschaltbild ist in Abb. 1 dargestellt. XCO Schleifenfilter f ref Phasen−Frequenz− Detektor Ladungs− pumpe VCO f aus f aus N Frequenzteiler 1/N Abb. 1: Blockschaltbild einer Phasenregelschleife Die folgende Betrachtung wird anhand der Eingangs- und Ausgangsfrequenz durchgeführt. Dabei ist zu beachten, dass die Frequenz als Ableitung der Phase definiert ist, d.h. es gilt ω = ∂Φ . ∂t Am Eingang der PLL liegt ein Referenzsignal fref an. Dieses Eingangssignal wird in der Regel von einem externen Quarz-Oszillator (XCO) hoher Güte erzeugt und zeichnet sich durch eine hohe Stabilität und Genauigkeit aus. Der VCO erzeugt an seinem Ausgang ein hochfrequentes Signal faus . Dieses Signal wird in der Rückkoppelschleife zunächst zum programmierbaren Frequenzteiler geleitet, welcher die hohe Frequenz durch einen ganzzahligen Faktor N teilt. Das geteilte VCO-Signal faus /N wird anschließend dem Phasen-Frequenz-Detektor zugeführt. Der PFD vergleicht das Ausgangssignal des Teilers bezüglich seiner Phase mit dem Referenzsignal fref des Quarz-Oszillators und erzeugt an seinem Ausgang ein Signal, das proportional zu deren Phasendifferenz ist. Eilt die Phase des geteilten VCO-Signals faus /N der Phase des Referenzsignals fref voraus, so erzeugt der PFD an seinem Ausgang ein negatives Signal, welches den VCO verlangsamt und somit die Ausgangsfrequenz vermindert. Dies geschieht so lange, bis die Phase des VCO-Signals faus wieder mit der Phase des Referenzsignals fref übereinstimmt. Liegt hingegen der umgekehrte Fall vor, dass die Phase des Signals faus /N dem EL-V8 - 2 PLL 1 EINFÜHRUNG Referenzsignal fref nacheilt, so erzeugt der PFD an seinem Ausgang ein positives Signal, welches die Ausgangsfrequenz des VCOs so lange erhöht, bis beide Signale wieder phasengleich sind. Am Ausgang des Phasen-Frequenz-Detektors befindet sich die Ladungspumpe. Sie hat die Aufgabe, das rechteckförmige Ausgangssignal des Phasen-Frequenz-Detektors in einen äquivalenten Strom umzuwandeln. Bei einem positiven PFD-Signal fließt ein positiver, bei einem negativen Signal entsprechend ein negativer Strom in das Schleifenfilter . Das Schleifenfilter dient dazu, den Ausgangsstrom der Ladungspumpe in eine Spannung umzuwandeln und gleichzeitig hochfrequente Störanteile herauszufiltern. Dadurch wird eine möglichst glatte VCO-Steuerspannung erzielt. Dies ist wichtig, da sich Schwankungen oder Sprünge in der Steuerspannung des VCOs direkt auf das Ausgangssignal faus auswirken. Die Wahl des Schleifenfilters und seine korrekte Auslegung sind deswegen für das Verhalten und die Stabilität der PLL von großer Bedeutung. Auf die Berechnung des Filters wird daher in einem späteren Kapitel genauer eingegangen. Im eingeschwungenen Zustand stellt sich am Ausgang des VCOs eine Frequenz faus ein, die einem ganzzahligen Vielfachen der Referenzfrequenz entspricht. Es gilt dann: faus = N · fref (1) Durch eine Änderung des Teilungsfaktors N am Frequenzteiler kann die Ausgangsfrequenz der PLL in einem bestimmten Bereich variiert werden. Beträgt die Referenzfrequenz fref zum Beispiel 1 MHz und wird ein Teilungsfaktor N = 270 gewählt, so erzeugt die PLL eine Ausgangsfrequenz faus von 270 MHz. Wird hingegen der Faktor N auf 290 erhöht, so erhöht sich entsprechend auch die Ausgangsfrequenz der PLL auf 290 MHz. Die Referenzfrequenz fref wird dabei nicht verändert, sondern bleibt konstant bei 1 MHz. Allerdings ist die Ausgangsfrequenz der PLL nicht beliebig variierbar, da neben dem Einstellbereich des Teilers vor allem der Verstimmbereich des VCOs und die Referenzfrequenz fref berücksichtigt werden müssen. Weist der VCO beispielsweise einen Verstimmbereich von 250 MHz bis 350 MHz auf, so kann die PLL Frequenzen innerhalb dieses Bereiches erzeugen. Der Teilungsfaktor, die Referenzfrequenz, und der Verstimmbereich des VCOs müssen daher aufeinander abgestimmt werden. Der Nachteil dieser PLL ist, dass die Ausgangsfrequenz nur um ganzzahlige Vielfache der Referenzfrequenz verändert werden kann. Aufgrund dieser Eigenschaft bezeichnet man diese Variante als Integer-N-Architektur. Frequenzen, die gebrochene Vielfache der Referenzfrequenz sind können beispielsweise mit einer Fractional-N-PLL erzeugt werden. In diesem Praktikum werden wir uns mit der Integer-N-PLL beschäftigen. Bei einer Integer-N-PLL richtet sich die Referenzfrequenz fref nach dem vorgegebenen Kanalabstand. Wird z.B. ein Kanalabstand von 100 kHz festgelegt, so muss für die Referenzfrequenz N·fref = 100 kHz gelten. Daher wird bei einer Integer-N-Architektur mit der Referenzfrequenz gleichzeitig die maximale Frequenzauflösung festgelegt, da fref die kleinste Schrittweite angibt, mit der die Ausgangsfrequenz verstimmt werden kann. Wird beispielsweise eine Referenzfrequenz von 200 kHz gewählt, so beträgt die minimale Schrittweite der Ausgangsfrequenz ebenfalls 200 kHz. Möchte man unter Beibehaltung der Referenzquelle eine kleinere Schrittweite erzielen, kann man im einfachsten Fall die Frequenz der ursprünglichen Quelle mit einem Teiler auf die gewünschte, neue Referenzfrequenz teilen. Ein weiteres Kriterium einer PLL ist die sogenannte Einschwingzeit. Diese Zeit benötigt die PLL beim Einschalten, oder bei einem Kanalwechsel, um ihren stationären Zustand zu erreichen. Maßgeblich für die Einschwingzeit ist die Schleifenbandbreite. Diese kann anhand des Bodediagramms der Übertragungsfunktion ermittelt werden. Sie ist definiert als die Frequenz, bei welcher der Betrag der Übertragungsfunktion die 0-dB-Achse schneidet. Für ein schnelles EL-V8 - 3 PLL 1 EINFÜHRUNG Einschwingen der PLL, muss die Schleifenbandbreite möglichst groß gewählt werden. Dadurch ergibt sich jedoch ein wesentlicher Nachteil. Eine große Bandbreite beschleunigt zwar das Einschwingen, vermindert aber gleichzeitig die Dämpfung der Störkomponenten. Wird die Bandbreite in Bezug zur Referenzfrequenz zu groß gewählt, kann dies aufgrund der geringen Dämpfung zu einem instabilen Verhalten der PLL führen. Auf diese Aspekte wird in Kapitel 2.5 zur Berechnung des Schleifenfilters ausführlicher eingegangen. 1.3 Modellierung Eine Phasenregelschleife ist ein rückgekoppeltes System. Aus diesem Grund folgt zunächst eine allgemeine Beschreibung von rückgekoppelten Systemen. Im Anschluss daran wird die Theorie auf die Phasenregelschleife angewendet. 1.3.1 Rückgekoppelte Systeme und Regelkreise Bei einem rückgekoppelten System wird ein Teil der Ausgangsgröße auf den Eingang zurückgeführt. Negative Rückkopplung bedeutet, dass die zurückgeführte Größe dem Eingangssignal entgegenwirkt. In einer elektronischen Schaltung sind das die Größen Strom und Spannung. Bei einer Phasenregelschleife wird dazu die Phase bzw. die Frequenz betrachtet. Die negative Rückkopplung entsteht durch Subtraktion der zurückgeführten Größe von der Eingangsgröße. Im Rückkoppelpfad kann sich zusätzlich noch ein Block befinden, der die Ausgangsgröße zurückführt. Ein negativ rückgekoppeltes System bildet im Allgemeinen einen Regelkreis. Abbildung 2 zeigt ein System mit einer negativen Rückkopplung [4]. Der Einkoppelfaktor A, X(s) A(s) R(s) V(s) Y(s) K(s) Abb. 2: Blockschaltbild eines allgemeinen rückgekoppelten Systems der Rückkoppelfaktor K und die Verstärkung V stehen dabei für Übertragungsfunktionen im Frequenzbereich. Es ergibt sich: R(s) = A(s) · X(s) − K(s) · Y (s) (2) Für das Ausgangssignal Y (s) folgt: Y (s) = V (s) · R(s) (3) Betrachtet man die Wirkung der Eingangsgröße X(s) auf den Ausgang Y (s) im offenen Regelkreis, d.h. für R(s) = X(s) erhält man die Übertragungsfunktion des offenen Regelkreises Ho (s): Ho (s) = A(s) · V (s) (4) Die Ringverstärkung Vr (s) ist die Wirkung des Ausgangs auf sich selbst: Vr (s) = K(s) · V (s) EL-V8 - 4 (5) PLL 1 EINFÜHRUNG Durch Einsetzen der Gleichung (2) in Gleichung (3) und anschließendem Auflösen nach erhält man die Übertragungsfunktion H(s) des (geschlossenen) Regelkreises: H(s) = A(s) · V (s) Ho (s) Y (s) = = X(s) 1 + K(s) · V (s) 1 + Vr (s) Y (s) X(s) (6) Wichtig für rückgekoppelte Systeme bzw. Regelkreise sind Betrachtungen zur Stabilität. Ein solches System wird instabil (oszilliert), wenn: |Vr (s = jω)| ≥ 1 und ∠Vr (jω0 ) = 180◦ (7) (8) Wenn eine Frequenz ω0 existiert, für die diese Bedingungen erfüllt sind („Mitkopplung“), schwingt das System bei ω0 . Die Frequenz, bei welcher der Betrag der Ringverstärkung des geschlossenen Regelkreises gleich eins ist, bezeichnet man als Durchtrittsfrequenz oder Bandbreite des Regelkreises. Als Phasenreserve bezeichnet man die Differenz von 180◦ und der Phase der Ringverstärkung bei dieser Frequenz. In der Praxis muss die Phasenreserve häufig größer als 30◦ sein, damit das System stabil ist. 1.3.2 Phasenregelschleife als rückgekoppeltes System Eine Phasenregelschleife kann, unter der Voraussetzung, dass sich das System im eingeschwungenen Zustand befindet, durch ein linearisiertes Modell beschrieben werden [1]. Das Blockdiagramm in Abbildung 3 ist daher vergleichbar zu einem Kleinsignal-Ersatzschaltbild, welches aus der Vorlesung „Elektronische Bauelemente“ bekannt ist. Im eingeschwungenen Zustand, was als Arbeitspunkt bezeichnet wird, werden daher nur noch kleine Änderungen um diesen herum betrachtet. PFD mit Ladungspumpe Schleifenfilter F in(s) F e(s) + - VCO UVCO(s) I CP KPFD Z(s) KVCO F out(s) s Frequenzteiler F out,N 1/N Abb. 3: Linearisiertes Modell einer Phasenregelschleife Vergleicht man das Blockdiagramm der PLL mit dem Blockdiagramm des allgemeinen rückgekoppelten Systems (Abb. 2), so ergeben sich folgende Eigenschaften: X(s) = Φin (s) Y (s) = Φout (s) EL-V8 - 5 (9) (10) PLL 1 R(s) = Φe (s) A(s) = 1 K(s) = 1/N EINFÜHRUNG (11) (12) (13) Φin stellt dabei die Phase des Eingangssignals und Φout die Phase des VCO-Ausgangssignals dar. Um nun die Verstärkung V (s) des allgemeinen rückgekoppelten Systems auf die PLL übertragen zu können, müssen alle Blöcke im Vorwärtskreis (PFD/CP, Schleifenfilter und VCO) zusammengefasst werden. Die Betrachtung soll zunächst im Zeitbereich erfolgen. Der Ausgangsstrom der Ladungspumpe ICP (t) kann durch die Gleichung ICP (t) = KP F D · Φe (t) (14) beschrieben werden. KP F D bezeichnet den Verstärkungsfaktor des Phasen-Frequenz-Detektors und ist definiert als ICP KP F D = . (15) 2π Die Einheit von KP F D ist [A/rad]. Durch Anwendung der Laplace-Transformation auf Gleichung (14) folgt: ICP (s) = KP F D · Φe (s) (16) Das Schleifenfilter wandelt den Ausgangsstrom der Ladungspumpe ICP in eine äquivalente Spannung um und dämpft zugleich die hochfrequenten Störanteile, so dass sich am Ausgang des Filters eine geglättete VCO-Steuerspannung UV CO ergibt. Es folgt: UV CO (s) = Z(s)ICP (s) (17) Z(s) stellt dabei die Übertragungsfunktion des Schleifenfilters dar und weist die Einheit [Ω] auf. Durch Einsetzen der Gleichung (16) in Gleichung (17) ergibt sich: UV CO (s) = Z(s)KP F D Φe (s) (18) Die Ausgangsphase Φout (t) des spannungsgesteuerten Oszillators berechnet sich im Zeitbereich aus dem Integral über die Steuerspannung UV CO (t). Daher gilt nach [2]: Z Φout (t) = 2πKV CO UV CO (t)dt (19) KV CO bezeichnet dabei die Verstimmsteilheit des VCOs. Diese gibt die Änderung der Ausgangsfrequenz faus in Bezug auf eine Änderung der Steuerspannung UV CO an. Die Einheit von KV CO ist [Hz/V]. Wendet man auf die Gleichung (19) die Laplace-Transformation an, d.h. transformiert man das System vom Zeit- in den Frequenzbereich, so ergibt sich nach [2] folgender Zusammenhang: 2πKV CO UV CO (s) (20) Φout (s) = s Setzt man nun Gleichung (18) in Gleichung (20) ein erhält man: Φout (s) = 2πKV CO Z(s)KP F D · Φe (s) s (21) Die Verstärkung V (s) ist nun direkt ablesbar: V (s) = Φout (s) 2πKV CO Z(s)KP F D = Φe (s) s EL-V8 - 6 (22) PLL 1 EINFÜHRUNG Die Übertragungsfunktion des offenen Regelkreises ergibt sich nach Gleichung (4) zu: Ho (s) = A(s) · V (s) = 1 · 2πKV CO Z(s)KP F D s (23) Die Ringverstärkung Vr (s) erhält man mit Gleichung (5): Vr (s) = K(s) · V (s) = 1 2πKV CO Z(s)KP F D 2πKP F D KV CO Z(s) · = N s sN (24) Auch bei einer Phasenregelschleife müssen die Stabilitätsbedingungen entsprechend geprüft werden. Die Übertragungsfunktion des geschlossenen Regelkreises kann man mit Hilfe von Gleichung (6) angeben: 2πKV CO Z(s)KP F D s 2πKP F D KV CO Z(s) sN Ho (s) = H(s) = 1 + Vr (s) 1+ 1.3.3 = 2πN KP F D KV CO Z(s) sN + 2πKP F D KV CO Z(s) (25) Überprüfung der Stabilität: Bode-Diagramm einer PLL Das Bodediagramm der Übertragungsfunktion der Ringverstärkung Vr liefert Informationen zur Stabilität der Phasenregelschleife. So findet man dort die Parameter Durchtrittsfrequenz ωD (bzw. fD = ω2πD ) und Phasenreserve φM wieder. In Abb. 4 beträgt die Durchtrittsfrequenz fD ≈ 20 kHz. Bei dieser Frequenz ist die Verstärkung |Ho | = 0 dB = 1. Die Phase φ(fD ) beträgt bei dieser Frequenz ungefähr −120°. Die Phasenreserve ergibt sich aus dem Abstand der −180° - Linie zum Phasenverlauf. In diesem Beispiel erhält man somit eine Phasenreserve φM von ca. 60°. Daraus kann gefolgert werden, dass die PLL in diesem Beispiel stabil ist. Die Dämpfung αdB von |Ho | beträgt bei der Referenzfrequenz fref = 106 Hz ungefähr −63 dB. Bei einer realen Schaltung kann so das Designziel überprüft werden. 1.4 Schleifenordnung und Schleifentyp Die Schleifenordnung gibt die Anzahl der Polstellen der Übertragungsfunktion des offenen Regelkreises an, wobei die Polstellen des Filters und die Polstelle des VCOs summiert werden müssen [3]. Bei einer Schleife erster Ordnung wird auf das Filter verzichtet, und es gilt Z(s) = 1. Dadurch vereinfacht sich die Übertragungsfunktion H(s) des geschlossenen Regelkreises zu: 2πN KP F D KV CO (26) H(s) = sN + 2πKP F D KV CO Anhand der Gleichung (26) kann man erkennen, dass eine PLL erster Ordnung nur eine Polstelle aufweist. Dieser Pol entsteht durch das in den Gleichungen (19) und (20) beschriebene Integrationsverhalten des VCOs. Verwendet man eine „PLL mit Ladungspumpe“, „so muss mindestens ein Filter erster Ordnung eingesetzt werden“ [1]. Dadurch erhöht sich die Schleifenordnung der Phasenregelschleife auf zwei. Ein weiteres Kriterium einer PLL ist der Schleifentyp. Dieser gibt die Anzahl der „idealen Integratoren“ in der Übertragungsfunktion des offenen Kreises an [1]. Der VCO stellt dabei immer einen idealen Integrator dar. Verwendet man in der PLL kein Filter, d.h. Z(s) = 1, so ergibt sich die Ringverstärkung zu: 2πKP F D KV CO Vr (s) = (27) sN EL-V8 - 7 2 arg(Vr(f)) [Grad] |Vr(f)| [dB] PLL 200 150 100 50 0 -50 -100 -150 -200 100 -120 -140 -160 -180 -200 -220 -240 -260 -280 100 KOMPONENTEN VON PHASENREGELSCHLEIFEN a dB 101 102 103 5 104 fD 10 Frequenz [Hz] 106 107 108 109 F (fD) + 180° M= F 101 102 103 104 105 106 107 108 109 Frequenz [Hz] Abb. 4: Bodediagramm der Übertragungsfunktion einer PLL 4. Ordnung Der niedrigste Schleifentyp, der möglich ist, ist somit eins, wobei die Polstelle bei s = 0 durch den VCO entsteht. 2 Komponenten von Phasenregelschleifen Im ersten Kapitel wurden das Prinzip, der Aufbau und die grundlegenden Eigenschaften einer Phasenregelschleife anhand eines linearisierten Modells (Blockschaltbild) dargestellt. Im folgenden Kapitel sollen die einzelnen Komponenten der Phasenregelschleife mit Ihren Eigenschaften und der schaltungstechnischen Realisierung in diesem Praktikumsversuch vorgestellt werden. 2.1 Spannungsgesteuerter Oszillator (VCO) Ein elementarer Bestandteil einer Phasenregelschleife ist der spannungsgesteuerte Oszillator. Er wird in der Regel in Sende- und Empfängerschaltungen eingesetzt und dient dazu, die Trägerfrequenzen der einzelnen Übertragungskanäle zu erzeugen. Eine wichtige Eigenschaft des VCOs ergibt sich somit direkt aus seiner Funktion. Um möglichst viele verschiedene Kanäle einstellen zu können, muss der VCO in der Lage sein, alle erforderlichen Frequenzen zu erzeugen [3]. Demzufolge muss der VCO über einen ausreichend großen Verstimmbereich ∆ω verfügen. Der Verstimmbereich gibt die Differenz zwischen der höchsten und der niedrigsten EL-V8 - 8 PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN Frequenz an, die der VCO erzeugen kann. Es gilt daher ∆ω = 2π · (fmax − fmin ). Ein weiteres Kriterium eines VCOs ist die Verstimmsteilheit KV CO . Diese ergibt sich aus der Ableitung der Ausgangsfrequenz nach der Steuerspannung: KV CO = 2π ∂faus ∂UV CO (28) Da die Steuerkennlinie eines VCOs in der Regel keinen linearen Verlauf besitzt, ist die Verstimmsteilheit KV CO nicht konstant, sondern weist eine Änderung über der Steuerspannung UV CO auf. Daher muss die Verstimmsteilheit des VCOs für mehrere Arbeitspunkte einzeln berechnet werden. Dies kann geschehen, indem man an verschiedenen Punkten der Steuerkennlinie eine Tangente anlegt und dadurch die Steilheit in jedem einzelnen Arbeitspunkt bestimmt. Abbildung 5 zeigt eine typische VCO-Steuerkennlinie. 380 360 Frequenz [MHz] 340 320 300 280 260 240 220 0 1 2 3 4 5 6 7 8 9 10 Tune-Spannung [V] Abb. 5: Gemessene VCO-Steuerkennlinie 2.1.1 Grundlegende Beschreibung eines Oszillators Ein Oszillator kann im Allgemeinen - wie schon die PLL - durch ein rückgekoppeltes System beschrieben werden. Während bei einem rückgekoppelten Verstärker (z.B. bei der PLL) darauf geachtet werden muss, dass das System stabil ist, wird bei einem Oszillator bewusst ein instabiler Zustand erzeugt, der zur Oszillation des Systems führt. Ein Oszillator kann demzufolge EL-V8 - 9 PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN als ein instabiler Verstärker angesehen werden [4]. Wie schon im Abschnitt „rückgekoppelte Systeme“ erwähnt, sind die Bedingungen für Instabilität (Oszillation): |Vr (s = jω)| ≥ 1 ∠Vr (jω0 ) = 180◦ (29) (30) Beschreibt man einen Oszillator durch ein rückgekoppeltes System, welches im Wesentlichen aus zwei Blöcken besteht, nämlich einer verstärkenden Komponente G(s) und einer frequenzselektierenden Komponente H(s) mit s = jω erhält man das in Abbildung 6 gezeigte Blockschaltbild [3]. Die Ringverstärkung ergibt sich hier zu: Vr (jω) = H(jω) · G(jω) G(s) (31) H(s) + − Abb. 6: Allgemeines Blockschaltbild eines Oszillators 2.1.2 Realisierung Es gibt eine große Anzahl unterschiedlicher Oszillatorarten und -konzepte. Sie unterscheiden sich im Wesentlichen in ihrer „Architektur“, ihrem „Aufwand“ und in den „erreichbaren Gütekriterien“ [3]. Je nach Anwendungsgebiet ist es demnach vorteilhaft, entweder das eine oder das andere Konzept auszuwählen. Für niederfrequente Anwendungen, bei denen die Güte keine große Rolle spielt, eignen sich z.B. Ringoszillatoren sehr gut. Sie sind einfach aufgebaut und lassen sich gut auf einem Chip integrieren. Für hochfrequente Anwendungen, wie z.B. den Einsatz in Mobilfunkschaltungen, bei denen Frequenzen im Gigahertz-Bereich benötigt werden, ist der Einsatz von Ringoszillatoren jedoch nicht möglich. Für diese Zwecke werden Oszillatoren mit einem LC-Schwingkreis verwendet. Aufgrund des internen Resonators weisen LC-Oszillatoren im Vergleich zu Ringoszillatoren eine höhere Güte und ein deutlich niedrigeres Phasenrauschen auf. In LC-Oszillatoren bilden LC-Schwingkreise die frequenzselektive Komponente. Eine mögliche Art der Verstärkung ist, den Schwingkreis mit Hilfe eines aktiven Bauelements, z.B. einem Transistor, zu entdämpfen. Dieser „aktive Schaltungsteil“ wird als „NIC“ (Negative Impedance Converter) bezeichnet. Abbildung 7 zeigt das entsprechende Modell eines LC-Oszillators, welches auch als Eintormodell bezeichnet wird [4]. Aufgrund des parallelen Widerstands Rp würde die Schwingung des LC-Resonators allmählich abklingen, wenn dem System von außen keine zusätzliche Energie zugeführt wird. Der NIC EL-V8 - 10 PLL 2 Cp KOMPONENTEN VON PHASENREGELSCHLEIFEN Lp Rp NIC − Rp Abb. 7: Eintormodell eines LC-Oszillators gleicht die Verluste, die durch den parallelen Widerstand Rp entstehen, aus und erhält dadurch die Schwingung des LC-Resonators aufrecht. Dabei kann der NIC quasi als ein negativer Widerstand -Rp angesehen werden, der parallel zu dem Widerstand Rp des LC-Schwingkreises geschaltet wird. Der daraus resultierende Gesamtwiderstand (Rp || − Rp ) strebt gegen unendlich und kann als Leerlauf betrachtet werden. Die ohmschen Verluste des Schwingkreises werden somit kompensiert, wodurch die Schwingung dauerhaft aufrecht erhalten wird. Die Resonanzfrequenz ω0 eines LC-Schwingkreises wird bestimmt durch: ω0 = √ 1 LC (32) Anhand dieser Gleichung kann man erkennen, dass für eine einstellbare Resonanzfrequenz entweder der Wert der Kapazität oder der Wert der Induktivität veränderlich sein muss. Da der Wert einer Spule von der Anzahl ihrer Windungen und den Materialparametern abhängt und nach der Herstellung elektrisch nicht mehr geändert werden kann, muss daher die Kapazität variabel ausgelegt werden. Dazu kann eine Varaktordiode verwendet werden. Die Kapazität einer solchen Diode weist eine Spannungsabhängigkeit auf und kann durch Anlegen einer Steuerspannung in einem bestimmten Bereich verändert werden. Aufgrund der Kapazitätsänderung ergibt sich anhand der Gleichung (32) auch eine Änderung der Resonanzfrequenz ω0 . Möchte man z.B. eine hohe Frequenz erreichen, muss die Kapazität der Varaktordiode verringert werden. Im umgekehrten Fall muss für eine niedrige Frequenz die Kapazität der Diode entsprechend erhöht werden. Ein bipolarer Varaktor, auch Kapazitätsdiode genannt, ist eine in Sperrrichtung betriebene pnDiode. Dadurch ergibt sich eine Sperrschichtkapazität Csperr , deren Wert durch Variation der Sperrspannung Usperr verändert werden kann. Es gilt daher nach [3] Csperr ∼ 1 (1 + Usperr m ) UD (33) mit 0, 33 ≤ m ≤ 0, 5. Der Wert des Exponenten m hängt davon ab, ob ein „linearer“ oder ein „abrupter“ pn-Übergang vorliegt. Eine Erhöhung der Sperrspannung Usperr am pn-Übergang hat eine Verbreiterung der Raumladungszone (RLZ) zur Folge. Dadurch entfernen sich die pund n-dotierten Gebiete weiter voneinander, wodurch die Sperrschichtkapazität Csperr abnimmt. Umgekehrt wird durch eine Verringerung der Sperrspannung Usperr die Kapazität Csperr entsprechend erhöht. Anschaulich kann dieses Prinzip mit einem Plattenkondensator verglichen werden, bei dem der Abstand zwischen den beiden Kondensatorplatten veränderlich ist. Wird EL-V8 - 11 PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN der Abstand d vergrößert, so nimmt aufgrund der Gleichung C= 0 r A d (34) die Kapazität C ab. Im umgekehrten Fall nimmt die Kapazität C entsprechend zu. VCO-Platine In diesem Praktikumsversuch wird der MAXIM MAX2620 als VCO eingesetzt. Er benötigt einen externen LC-Resonanzkreis (LC tank circuit) und arbeitet als NIC. Der Kondensator im Resonanzkreis ist eine Varaktordiode. Die Anschlüsse „TANK“ und „FEEDBACK“ des Chips sind kapazitiv gekoppelt und durch einen kapazitiven Spannungsteiler mit dem LC-Resonanzkreis verbunden. Abbildung 8 zeigt das Schaltbild dieses Oszillators. VCC OUT TANK OUT FDBK BIAS MAX 2620 VEE Abb. 8: Beschaltung des MAX2620 MAX 2620 Vtune MC100EL16 MC10EL89 LC Abb. 9: Blockschaltbild der VCO-Platine Zur weiteren Verstärkung des differentiellen VCO-Signals ist im Signalpfad noch ein Verstärker (MC100EL16) und ein Treiber-IC, der aus einem differentiellen Signal zwei differentielle Signale erzeugt (MC10EL89) nötig. Die differentiellen Signale werden am Ausgang mit Hilfe eines Baluns zu einem unipolaren Signal transformiert. Es stehen am Ausgang dadurch zwei Signale zur Verfügung. Für eine Messung in diesem Versuch werden beide Ausgänge benötigt. Abbildung 9 zeigt das Blockschaltbild der VCO-Platine. EL-V8 - 12 PLL 2.2 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN Frequenzteiler In diesem Praktikum wird ein einstellbarer Frequenzteiler verwendet, wodurch verschiedene Teilungsfaktoren N eingestellt werden können. Dadurch kann die Ausgangsfrequenz faus der PLL in einem bestimmten Bereich ∆f variiert werden. Da es sich hierbei, wie bereits erwähnt, um eine Integer-N-Architektur handelt, kann die Ausgangsfrequenz faus nur ganzzahlige Vielfache der Referenzfrequenz annehmen. faus = N · fref 2.2.1 (35) Zähler als Teiler Mit Hilfe eines Rückwärts-Zählers kann ein Teiler realisiert werden. Dazu wird der Zähler zu Beginn auf einen Wert M eingestellt. Mit jedem Taktimpuls wird dieser Wert nun um eins verringert und anschließend von einer Vergleichslogik geprüft, ob dieser Wert gleich null ist. Die Vergleichslogik gibt das Ergebnis S := (M == 0) aus. clk cnt 3 2 1 0 3 2 1 0 S S‘ Abb. 10: Timing-Diagramm des Zählers Nach M +1 Takten wird für die Dauer eines Taktes das Signal S zu 1, für die restliche Zeit ist das Signal 0. Um den Vorgang fortlaufend zu wiederholen, wird im M. Takt der Zähler erneut auf den Wert M geladen, der M. Takt entspricht somit dem Ersten. Abbildung 10 zeigt beispielhaft das Timing-Diagramm für M = 3. Dort ist auch das Problem dieser Struktur ersichtlich: Es wird zwar die Anzahl der Taktflanken geteilt, die Grundfrequenz jedoch nicht - das Ausgangssignal S ist zunächst ein ebenso schnelles Signal wie der Takt, jedoch in einem anderen Tastverhältnis - statt 50% ist das Tastverhältnis nun M1+1 . Andererseits ist das Signal S periodisch. Nach N = M + 1 Takten wiederholt sich das Signal. N = M + 1 ist der gewünschte Teilungsfaktor. Teilt man das Signal S mit Hilfe eines „:2“-Teilers, der seinen Ausgang bei jeder positiven Flanke von S ändert, erhält man das Signal S’, welches das gewünschte Tastverhältnis von 50% hat. 2.2.2 Teilerplatine Auf der Teilerplatine sind zwei 6-bit-Zähler (MC100E136) in Reihe geschaltet. Im Signalpfad nach diesen beiden Zählern befindet sich ein „:2“-Teiler, der am Ausgang ein Signal mit einem Tastverhältnis von 50% bereitstellt. EL-V8 - 13 PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN Jede einzelne MC100E136 - Teilerzelle besitzt 6 Eingangsbits, D0 bis D5 . Über diese 6 Bits können Teilungsfaktoren von 2 bis 64 eingestellt werden. Tabelle 1 zeigt die Zuordnung zwischen den Eingangsbits und den entsprechenden Teilungsfaktoren [9]. Teilerverhältnis 2 3 4 5 . . 36 37 38 . . 62 63 64 D5 L L L L . . H H H . . H H H D4 L L L L . . L L L . . H H H Eingangsbits D3 D2 D1 L L L L L H L L H L H L . . . . . . L L H L H L L H L . . . . . . H H L H H H H H H D0 H L H L . . H L H . . H L H Tab. 1: Zuordnung zwischen Eingangsbits und Teilerverhältnis Durch die Reihenschaltung der MC100E136 - Teilerzellen entsteht ein programmierbarer 12Bit-Frequenzteiler. Bedingt durch die Verschaltung ergibt sich der Gesamt-Teilungsfaktor zu N = N1 · N2 . Die Einstellung der Teilungsfaktoren erfolgt über zwei 6-Bit-DIP-Schalter D0 bis D5 und D6 bis D11 , wobei jeder DIP-Schalter eine MC100E136 - Teilerzelle ansteuert. Um eine Teilung durch Ni zu realisieren, muss mit den DIP-Schaltern der Wert Ni − 1 in die Teilerzelle geladen werden. Möchte man z.B. eine Teilung durch 64 realisieren, so muss mit den Schaltern ein Wert von 63 eingestellt werden. Der Teilungsfaktor N1 des ersten Teilers ergibt sich zu N1 = d5 · 25 + d4 · 24 + d3 · 23 + d2 · 22 + d1 · 21 + d0 · 20 + 1 (36) Für den zweiten Teiler gilt entsprechend N2 = d11 · 25 + d10 · 24 + d9 · 23 + d8 · 22 + d7 · 21 + d6 · 20 + 1 (37) Der Gesamt-Teilungsfaktor Nges ergibt sich aufgrund der Reihenschaltung der beiden Teilerzellen und dem nachfolgenden „:2“-Teiler zu Nges = 2 · N1 · N2 (38) N1 , N2 ∈ [2, 3, ..., 63, 64] (39) mit 2.3 Phasen-Frequenz-Detektor (PFD) Ein Phasen-Frequenz-Detektor (PFD) dient dazu, Phasen- und Frequenzunterschiede zweier Eingangssignale zu detektieren. Dabei erzeugt der PFD an seinem Ausgang Signale, die Informationen über die Phasendifferenz der Eingangssignale enthalten. Abbildung 11 zeigt das Schaltsymbol eines Phasen-Frequenz-Detektors. EL-V8 - 14 PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN A QA PFD B QB Abb. 11: Schaltsymbol eines Phasen-Frequenz-Detektors Der Phasen-Frequenz-Detektor besitzt zwei Eingangssignale A und B und zwei Ausgangssignale QA und QB . Die Funktionsweise des PFDs kann durch das folgende Zustandsdiagramm beschrieben werden. Zustand 2 B B QA = 0 QB = 1 Zustand 0 A QA = 0 QB = 0 A Zustand 1 QA = 1 QB = 0 A B Abb. 12: Zustandsdiagramm eines Phasen-Frequenz-Detektors Es wird zunächst angenommen, dass sich das System im Zustand 0 befindet, wobei gilt QA = QB = 0. Eilt beispielsweise das Signal A dem Signal B voraus, so wechselt das System beim Auftreten der positiven Flanke an A vom Zustand 0 in den Zustand 1. Der Ausgang QA nimmt dabei den Wert 1 an, während der Ausgang QB den Wert 0 beibehält. Der Zustand 1 wird so lange gehalten, bis die positive Taktflanke des Signals B auftritt. Daraufhin wird der Ausgang QA auf 0 zurückgesetzt und das System kehrt wieder in den Anfangszustand zurück. Eilt im umgekehrten Fall das Signal B dem Signal A voraus, so wechselt das System vom Zustand 0 in den Zustand 2. Mit dem Auftreten der positiven Flanke an A kehrt das System wieder in den Anfangszustand zurück. Bei der folgenden Betrachtung müssen zwei Fälle unterschieden werden. Zunächst wird davon ausgegangen, dass beide Signale A und B dieselbe Frequenz besitzen und lediglich eine Phasenverschiebung aufweisen [4]. Dieser Fall ist in Abbildung 13 dargestellt. Die Signale A und B besitzen dieselbe Frequenz, allerdings eilt das Signal A dem Signal B etwas voraus. Es gilt daher ΦA 6= ΦB . Am Ausgang QA ergeben sich dadurch kontinuierliche Pulse, deren Breite ein Maß für die Phasendifferenz ΦA − ΦB darstellt. Da die Frequenz beider Signale gleich ist, ändert sich die Phasenlage der Signale zueinander nicht. Daher bleiben die Phasendifferenz und somit auch die Breite der Ausgangspulse von QA konstant. Der Ausgang QB bleibt kontinuierlich auf Null, weil das Signal B dem Signal A zu keinem Zeitpunkt vorauseilt. Betrachtet man hingegen zwei Signale unterschiedlicher Frequenz, so ändert sich die Phasenlage beider Signale ständig. In Abbildung 14 weist das Signal A eine etwas höhere Frequenz auf, als das Signal B. Es gilt ωA > ωB . Dadurch nimmt die Phasendifferenz ΦA − ΦB und damit EL-V8 - 15 PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN A B QA QB Abb. 13: ΦA 6= ΦB auch die Pulsweite am Ausgang QA stetig zu. A B Q A Q B Abb. 14: ωA > ωB EL-V8 - 16 PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN Ein einfacher Phasen-Frequenz-Detektor kann aus zwei D-Flipflops mit Reset-Eingang und einem AND-Gatter aufgebaut werden [5]. Abbildung 15 zeigt die Realisierung eines solchen digitalen PFDs. 1 A D CLK Reset 1 B QA Q D AND QB Q CLK Abb. 15: Blockschaltbild eines PFDs Die Funktionsweise ist dabei folgende: Tritt an einem der beiden Eingänge A oder B eine positive Taktflanke auf, so wird der Ausgang des entsprechenden Flipflops auf 1 gesetzt. Erst wenn an dem anderen Eingang ebenfalls eine positive Taktflanke detektiert wird, nimmt auch der Ausgang des anderen Flipflops den Wert 1 an. Haben beide Ausgänge QA und QB den Wert 1, so erzeugt das AND-Gatter einen Reset-Impuls, der die Ausgänge beider Flipflops wieder auf Null zurücksetzt. Am Ausgang des PFDs wird somit ein Impuls erzeugt, der genau dem Phasenunterschied beider Signale entspricht. Je nachdem welches Signal voreilt, wird entweder der Ausgang QA oder der Ausgang QB geschaltet. Der Ausgang QA wird dabei auch als Upund der Ausgang QB als Down-Ausgang bezeichnet. Beide Ausgänge dienen zur Ansteuerung der Ladungspumpe. EL-V8 - 17 PLL 2.4 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN Ladungspumpe (CP) Abbildung 16 zeigt den Phasen-Frequenz-Detektor (PFD) zusammen mit der Ladungspumpe und dem Schleifenfilter [5]. UDD I1 QA A PFD B QB S1 Schleifenfilter U VCO S2 I2 Ladungs− pumpe Abb. 16: PFD mit Ladungspumpe und Schleifenfilter Die Ladungspumpe kann im einfachsten Fall durch ein Modell bestehend aus zwei Stromquellen I1 und I2 und zwei Schaltern S1 und S2 beschrieben werden. Die Ansteuerung erfolgt durch die beiden Ausgangssignale QA und QB des Phasen-Frequenz-Detektors (PFD). Die Aufgabe einer Ladungspumpe besteht darin, die Ausgangssignale des Phasen-FrequenzDetektors in einen äquivalenten Strom umzuwandeln. Im Ausgangszustand sind beide Schalter S1 und S2 geöffnet, d.h. es fließt zunächst kein Strom. Nimmt eines der beiden Signale QA oder QB den Wert 1 an, so wird der entsprechende Schalter geschlossen und das Schleifenfilter wird entweder durch die obere Stromquelle geladen, oder durch die untere Stromquelle entladen. Besitzt beispielsweise der Ausgang QA den Wert 1 und QB den Wert 0, so wird der Schalter S1 geschlossen. Der Schalter S2 bleibt weiterhin geöffnet. In diesem Zustand fließt ein positiver Strom I1 von der oberen Stromquelle in das Schleifenfilter hinein. Dadurch werden die Kapazitäten des Filters aufgeladen und die Steuerspannung UV CO am Ausgang des Filters steigt an. Im umgekehrten Fall wird der obere Schalter S1 geöffnet und der untere Schalter S2 geschlossen. Das Filter wird dann durch die untere Stromquelle entladen und die Spannung UV CO am Ausgang des Filters nimmt wieder ab. Dieses Modell kann allerdings nur als vereinfachte Darstellung der Ladungspumpe angesehen werden. Die Schalter S1 und S2 , sowie die beiden Stromquellen I1 und I2 werden auf Schaltungsebene durch MOSFETS oder BipolarTransistoren realisiert. 2.5 Schleifenfilter Das Schleifenfilter sorgt dafür, dass die Pulse des Phasen-Frequenz-Detektors geglättet werden. Dadurch wird verhindert, dass sich die Steuerspannung des VCOs sprunghaft verändert, EL-V8 - 18 PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN was sich negativ auf das Ausgangssignal UV CO auswirken würde. Durch die Wahl der Filterordnung und der Bauelementwerte kann das Verhalten der Schaltung beeinflusst werden: Stabilität, Einschwingzeit und Störfrequenzunterdrückung sind dabei die wichtigsten Parameter. In diesem Abschnitt werden die Bauelementwerte des Filters als Funktion der Parameter der PLL berechnet. Verwendet man eine PLL mit Ladungspumpe, so muss mindestens ein Filter 1. Ordnung eingesetzt werden, da der Strom für eine glatte VCO-Steuerspannung integriert werden muss. Zunächst soll ein Filter 2. Ordnung betrachtet werden. 2.5.1 Filter 2. Ordnung (PLL 3. Ordnung) I in R2 C1 Uaus C2 Abb. 17: Filter 2. Ordnung Die Übertragungsfunktion des Filters ergibt sich zu Z(s) = Mit den Zeitkonstanten Uaus s · R2 C2 + 1 = Iin C1 C2 R2 s2 + C1 s + C2 s C1 C2 C 1 + C2 τ2 = R2 C2 τ1 C1 = τ2 C1 + C2 τ1 = R2 · (40) (41) (42) (43) wird Gleichung (40) zu Z(s) = τ2 s + 1 1 τ1 · C1 τ2 s(τ1 s + 1) (44) Damit erhält man als Übertragungsfunktion der Ringverstärkung nach Einsetzen in Gleichung (24): Vr (s) = 2πKP F D KV CO Z(s) 2πKP F D KV CO τ1 τ2 s + 1 = · · 2 sN N · C1 τ2 s (τ1 s + 1) (45) Um nun die Durchtrittsfrequenz ωD und die Phasenreserve φM berechnen zu können, betrachtet man Vr (s = jω): Vr (jω) = 2πKP F D KV CO τ1 τ2 jω + 1 2πKP F D KV CO τ1 jωτ2 + 1 · · =− · · 2 (46) 2 N · C1 τ2 (jω) (τ1 jω + 1) N · C1 τ2 ω (jωτ1 + 1) EL-V8 - 19 PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN Um die folgende Berechnung zu erleichtern, werden alle frequenzunabhängigen Faktoren zusammengefasst: 2πKP F D KV CO τ1 K=− · (47) N · C1 τ2 1 jωτ2 + 1 ⇒ Vr (jω) = K · 2 · (48) ω jωτ1 + 1 Mit Hilfe der Beziehung für komplexe Zahlen z = zz12 φ(z) = φ(z1 ) − φ(z2 ) (49) kann man nun die Phase der Ringverstärkung angeben: φ(jω) = φ( K · (1 + jωτ2 )) − φ(1 + jωτ1 ) = arctan(ωτ2 ) − arctan(ωτ1 ) ω2 (50) Die Phasenreserve φM kann wie folgt berechnet werden: φM (jω) = φ(jω) + π = arctan(ωτ2 ) − arctan(ωτ1 ) + π (51) Aus Stabilitätsgründen ist es sinnvoll, die Phasenreserve zu maximieren. Das Maximum der Phasenreserve (vgl. Bode-Diagramm einer PLL, Abb. 4) kann aus der Ableitung von φM (jω) bestimmt werden: τ2 τ1 dφM = − =0 (52) 2 dω 1 + (ωτ2 ) 1 + (ωτ1 )2 r 1 ⇒ ωM = (53) τ1 τ2 Um die Bauelemente bemessen zu können, wählt man als Durchtrittsfrequenz ωD die zuvor berechnete Frequenz ωM : ! (54) ωD = ωM Damit ist sichergestellt, dass bei der maximalen Phasenreserve die Ringverstärkung |Vr (jω)| = 1 ist. Es gilt also: 2πKP F D KV CO Z(jωD ) 2πKP F D KV CO = |Vr (jωD )| = 1 = · |Z(jωD )| (55) jωD N N · ωD 2πKP F D KV CO 1 τ1 jωD τ2 + 1 = · · · (56) N · ωD C1 τ2 jωD (jωD τ1 + 1) s 2 2 2πKP F D KV CO 1 τ1 1 ωD τ2 + 1 = · · · · (57) 2 2 N · ωD C1 τ2 ωD ωD τ1 + 1 Somit kann für die Kapazität C1 der Wert angegeben werden: s 2 2 2πKP F D KV CO τ1 1 ωD τ2 + 1 C1 = · · 2 · 2 2 N τ2 ω D ωD τ1 + 1 (58) Wählt man die Schleifenbandbreite ωD und die Phasenreserve φM als feste Parameter, lassen sich τ1 und τ2 als Funktion der Parameter ausdrücken: τ2 = 1 · τ1 2 ωD EL-V8 - 20 (59) PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN 1 1 − sin φM · (60) ωD cos φM Hierbei kann Gleichung (60) aus den Gleichungen (51) und (59) hergeleitet werden (vgl. [8]). Sind beide Zeitkonstanten bekannt, kann mit Hilfe der Gleichung (58) der Wert des Kondensators C1 berechnet werden, und mit Gleichung (43) der Wert des Kondensators C2 τ1 = C2 = τ2 τ1 τ2 · C1 · (1 − ) = C1 · ( − 1) τ1 τ2 τ1 (61) R2 folgt direkt aus Gleichung (42): τ2 (62) C2 Damit sind die Bauelementwerte des Schleifenfilters 2. Ordnung aus den vorgegebenen Designparametern der PLL bestimmt worden. Betrachtet man eine fast eingerastete Phasenregelschleife (fref und faus,N unterscheiden sich also nur minimal), so zeigt sich, dass der Phasen-Frequenz-Detektor sehr kurze Impulse erzeugt. Diese kurzen Impulse sind sehr hochfrequent und stören die Ausgangsfrequenz. Die Filtersteilheit ist mit -40 dB/Dekade zu gering. Es ist daher nötig, hohe Frequenzen stärker zu unterdrücken. Ein weiteres Tiefpassfilter 1. Ordnung (RC-Glied) hilft, die Flankensteilheit zu erhöhen. Ein einfacher Ansatz für eine PLL 4. Ordnung ist, einen Tiefpass zwischen dem bisherigen Schleifenfilter und dem VCO zu schalten und die Eckfrequenz mindestens eine Dekade über der Durchtrittsfrequenz zu wählen. Das zusätzliche RC-Glied wird die Filtersteilheit bei hohen Frequenzen auf -60 dB/Dekade erhöhen. R2 = 2.5.2 Filter 3. Ordnung (PLL 4. Ordnung) I in R R C1 C 3 2 C3 Uaus 2 Abb. 18: Filter 3. Ordnung Als Designparameter eignet sich die gewünschte zusätzliche Dämpfung der Referenzfrequenz. Die Übertragungsfunktion des RC-Gliedes lautet: F (jω) = 1 1 + jωR3 C3 (63) Daraus ergibt sich der Betrag zu |F (jω)|dB = −10 log(1 + (ωR3 C3 )2 ) EL-V8 - 21 (64) PLL 2 KOMPONENTEN VON PHASENREGELSCHLEIFEN und somit die zusätzliche Dämpfung bei der Referenzfrequenz fref zu ξref = 10 log(1 + (2πfref τ3 )2 ) (65) τ3 = R3 C3 (66) mit der Zeitkonstanten Wird Gleichung (65) nach τ3 umgestellt, so ergibt sich eine Funktion, die nur noch von Designparametern abhängt: q ξref 1 · 10 10 − 1 τ3 = (67) 2πfref Durch das zusätzliche Filter verschiebt sich das Maximum der Phasenreserve zu einer etwas geringeren Frequenz. Das muss bei der Berechnung der Bauelementwerte berücksichtigt werden. Nach [8] gilt: s ! 2+τ τ (τ + τ ) tan(φ ) · (τ + τ ) 1 3 1 3 M 1 3 ∗ 1+ · ωM = −1 (τ1 + τ3 )2 + τ1 τ3 [tan(φM ) · (τ1 + τ3 )]2 p 1 2 + cos2 φ · (τ + τ ) · (τ τ ) − sin φ · (τ + τ ) = 1 3 M 1 3 M 1 3 cos φM · [(τ1 + τ3 )2 + τ1 τ3 ] (68) Auch die Zeitkonstante τ2 ändert sich geringfügig: τ2 = ∗ 2 ωM 1 · (τ1 + τ3 ) (69) ∗ Der Wert für die Kapazität C1 wird mit Hilfe von ωM berechnet und durch einen Korrekturfaktor ergänzt, der die zusätzliche Polstelle einbezieht: s 1 C1 = C1,F ilter2.Ordnung · ∗ 1 + (ωM τ3 )2 s s ∗ 2πKP F D KV CO τ1 1 + (ωM τ2 )2 1 1 = · · ∗ 2· · (70) ∗ ∗ N τ2 ω M 1 + (ωM τ1 )2 1 + (ωM τ3 )2 Gleichungen (61) und (62) gelten weiterhin, so dass bereits drei der fünf Bauelementwerte bekannt sind. Die Gleichungen (65) und (66) sind ausreichend, um die Werte von C3 und R3 1 zu berechnen. Obwohl hier eigentlich noch ein Freiheitsgrad besteht, sollte C3 ≤ 10 C1 und R3 ≥ 2R2 gewählt werden, da sonst die zusätzliche Polstelle großen Einfluss auf die beiden Polstellen des dominierenden Filters hat. Je nach Aufbau der Phasenregelschleife muss die Eingangskapazität des VCO (Varaktordiode) berücksichtigt werden. In diesem Versuch ist das Filter vom VCO durch einen Buffer getrennt, dessen Eingangskapazität an dieser Stelle vernachlässigt wird. EL-V8 - 22 PLL 3 3 MESSAUFGABEN Messaufgaben 3.1 Messaufgabe VCO Messen Sie die Tunekurve des VCOs und bestimmen Sie daraus die Verstimmsteilheit KV CO für die Frequenz fres,0 = ___________ . +5V R&S 0V SA rot schwarz VCO 50W Vtune Abb. 19: Messaufbau zur Charakterisierung des VCOs Material: - Spannungsquelle 5V (rot) Spannungsquelle 0 · · · 10V diverse Kabel Multimeter - VCO - Platine - Spektrumanalysator (SA) - Adapter Bananenstecker - SMA 1. Vervollständigen Sie die folgende Tabelle und zeichnen Sie die Tunekurve! Verwenden Sie zur Kontrolle der Tune-Spannung Vtune ein Multimeter. Vtune [V] 0 1 2 3 4 fres [MHz] Tab. 2 EL-V8 - 23 5 6 7 8 9 10 PLL 3 MESSAUFGABEN 380 360 Frequenz [MHz] 340 320 300 280 260 240 220 0 1 3 2 5 4 6 7 8 9 10 Tune-Spannung [V] 2. Vervollständigen Sie die folgende Tabelle und berechnen Sie die drei VCO-Steilheiten in Tabelle 4. ∆Vtune,0 −0.3 V −0.2 V −0.1 V 0V +0.1 V +0.2 V +0.3 V Vtune [V] fres [MHz] fres,0 Tab. 3 fres,0+0.1V −fres,0−0.1V Vtune,0+0.1V −Vtune,0−0.1V KV CO,01 [MHz/V] fres,0+0.2V −fres,0−0.2V Vtune,0+0.2V −Vtune,0−0.2V KV CO,02 [MHz/V] fres,0+0.3V −fres,0−0.3V Vtune,0+0.3V −Vtune,0−0.3V KV CO,03 [MHz/V] Tab. 4 3. Berechnen Sie den Mittelwert KV CO,0 mit Hilfe der folgenden Gleichung: KV CO,0 = 1 i P i KV CO,i = _____________ EL-V8 - 24 PLL 3 3.2 MESSAUFGABEN Messaufgabe Teiler Verschalten Sie das Teilermodul und den VCO gemäß Abbildung 20! R&S SA +5V 0V Power Combiner rot schwarz VCO rot schwarz Teiler Vtune Abb. 20: Messaufbau zur Charakterisierung des Teilermoduls Material: - Spannungsquelle 5V (rot) Spannungsquelle 0 · · · 10V diverse Kabel Multimeter Power Combiner - VCO-Platine - Teiler-Platine - Spektrumanalysator (SA) - Adapter Bananenstecker - SMA 1. Ermitteln Sie den Teilungsfaktor N des Teilermoduls mit Hilfe des Spektrumanalysators! fT eiler · N = fV CO ⇒ N = ______ 2. Ermitteln Sie die Teilungsfaktoren N1 und N2 für die Schalterstellungen DIP 1 und DIP 2 mit Hilfe der Formeln aus Kapitel 2.2.6. Der Gesamt-Teilungsfaktor ergibt sich zu Nges = 2 · N1 · N2 : N1 = d5 · 25 + d4 · 24 + d3 · 23 + d2 · 22 + d1 · 21 + d0 · 20 + 1 (71) N2 = d11 · 25 + d10 · 24 + d9 · 23 + d8 · 22 + d7 · 21 + d6 · 20 + 1 (72) EL-V8 - 25 PLL 3 Teiler Schalterstellung DIP 1 000110 DIP 2 111101 Teilungsfaktor Nx MESSAUFGABEN Nges = 2 · N1 · N2 Tab. 5 3. Welche Teilungsfaktoren N1 und N2 werden benötigt, damit der VCO bei einer Referenzfrequenz von fref = 1 MHz bei der Resonanzfrequenz fres,0 oszilliert? Teiler Schalterstellung Nx DIP 1 DIP 2 Tab. 6 Überprüfen Sie ihre Berechnungen mit Hilfe des Spektrumanalysators! EL-V8 - 26 N PLL 3.3 3 MESSAUFGABEN Messaufgabe PFD mit CP Verschalten Sie das PFD / CP - Modul gemäß Abbildung 21! + 5 V 0 V + 15 V PFD / CP schwarz rot blau f Teiler,in I CP mA f ref,in Abb. 21: Messaufbau zur Charakterisierung des PFD Material: - 2 × 100 Ω Messkabel - Spannungsquelle 5V (rot) - diverse Kabel - PFD / CP - Platine - Multimeter - Spannungsquelle 15V (blau) Zur Bestimmung des Verstärkungsfaktors KP F D wird der Ausgangsstrom der Ladungspumpe ICP benötigt. Messen Sie dazu den Ladestrom ICP,up und den Entladestrom ICP,down . Gehen Sie dabei wie folgt vor: Kontaktieren Sie den Eingang fref,in mit 5 V, um ICP,up zu bestimmen und den Eingang fT eiler,in für ICP,down . ICP,up [mA] ICP,down [mA] 1. Bestimmen Sie den mittleren Strom der Ladungspumpe ICP . ICP = ICP,up +ICP,down 2 = _____________ 2. Bestimmen Sie den Verstärkungsfaktor KP F D . KP F D = ICP 2π = _____________ EL-V8 - 27 PLL 3.4 3 MESSAUFGABEN Messaufgabe Schleifenfilter Filter blau schwarz I CP Utune Abb. 22: Messaufbau zur Charakterisierung des Schleifenfilters Material: - Schleifenfilter - Platine Multimeter 1. Vervollständigen Sie Tabelle 7 mit den Werten der Randbedingungen zur Dimensionierung der PLL. fref KP F D KV CO ΦM ωD N Z(s): Tab. 7: Randbedingungen zur Dimensionierung der PLL EL-V8 - 28 ξref PLL 3 MESSAUFGABEN 2. Bestimmen Sie die Filterkoeffizienten für die Filterfunktion Z(s) bei den Durchtrittsfrequenzen fD mit Hilfe der folgenden Gleichungen: Berechnung von 1−sin φM cos φM τ1 = 1 ωD τ3 = 1 2πfref · Ergebnis q ξref · 10 10 − 1 ∗ ωM = p (τ1 + τ3 )2 + cos2 φM · (τ1 τ3 ) − sin φM · (τ1 + τ3 ) 1 · cos φM ·[(τ1 +τ3 )2 +τ1 τ3 ] τ2 = C1 = 1 ∗ 2 ·(τ +τ ) ωM 1 3 2πKP F D KV CO N · τ1 τ2 · 1 ∗ 2 ωM · q ∗ τ )2 1+(ωM 2 ∗ τ )2 1+(ωM 1 · q 1 ∗ τ )2 1+(ωM 3 C2 = C1 · ( ττ21 − 1) R2 = τ2 C2 C3 = 1 C 10 1 R3 = τ3 C3 Tab. 8: Berechnung der Filterkoeffizienten 3. Übertragen Sie die Koeffizienten auf das Schleifenfilter. fD R2 R3 C1 C2 C3 1 kHz 10 kHz 100 kHz Tab. 9: Bauelementwerte für das Filter Hinweis: Bestimmen Sie R2 und R3 mit dem Multimeter und stellen Sie C1 , C2 und C3 mit den DIP - Schaltern ein. EL-V8 - 29 PLL 3.5 3 MESSAUFGABEN Messaufgabe PLL 0V 5V rot 15V schwarz blau PLL SA SG Abb. 23: Messaufbau zur Charakterisierung der PLL - VCO-Platine PFD/CP-Platine Spannungsquelle 5V (rot) Referenzquelle (Signalgenerator) 2 Multimeter diverse Kabel - Teiler-Platine Filter-Platine Spannungsquelle 15V (blau) Spektrumanalysator 50 Ohm Abschlusswiderstand Verschalten Sie die PLL komplett. Achten Sie auf die Farben der Versorgungsspannungsanschlüsse der einzelnen Platinen (rot = 5V, blau = 15V, schwarz = Masse). Kontrollieren Sie die Höhe der Versorgungsspannungen mit einem Multimeter. Schliessen Sie den nicht verwendeten Ausgang des VCOs mit dem 50-Ohm-Abschlusswiderstand ab. 1. Messen Sie die Bandbreite fD der PLL mit Hilfe des Spektrumanalysators! 2. Messen Sie die Leistungsdifferenz in dB zwischen Signal und Störer! EL-V8 - 30 PLL Literaturverzeichnis Literatur [1] M. Weber, „Untersuchung und Schaltungsentwurf einer Phasenregelschleife in Fractional-N-Architektur für FMCW-Radarsysteme bei 24 GHz in 120-nm-CMOSTechnologie“, Diplomarbeit, Ruhr-Universität Bochum [2] C. S. Vaucher, „Architectures for RF Frequency Synthesizers“, Kluwer Academic Publishers, 2002 [3] S. Mecking, „System-in-Package-Lösungen von Sendeempfängerschaltungen für drahtlose Netze im 5-GHz-Band: Entwurf und Charakterisierung“, Dissertation, RuhrUniversität Bochum, 2005 [4] B. Razavi, „Design of Analog CMOS Integrated Circuits“, Mc-Graw-Hill, 2001 [5] B. Razavi, „RF Microelectronics“, Prentice Hall PTR, 1998 [6] U. Langmann, „Integrierte Schaltungen für Mobilfunksysteme“, Vorlesung, Lehrstuhl für Integrierte Systeme, Ruhr-Universität Bochum, 2007 [7] M. Weber, „Programmierbare Frequenzteiler für Phasenregelschleifen in HochfrequenzMesssystemen: Untersuchung von Teilungskonzepten und Schaltungsentwurf“, Studienarbeit, Lehrstuhl für Integrierte Systeme, Ruhr-Universität Bochum [8] National Semiconductor, „An Analysis and Performance Evaluation of a Passive Filter Design Technique for Charge Pump PLL’s“, National Semiconductor, July 2001 [9] ON Semiconductor, „MC10E136, MC100E136, 5V ECL 6-Bit Universal Up/Down Counter“, Datenblatt, http://onsemi.com, November 2006 [10] I. N. Bronstein, „Taschenbuch der Mathematik“, S. 1093, Verlag Harri Deutsch, 5. Auflage, 2000 EL-V8 - 31