herunterladen

Werbung

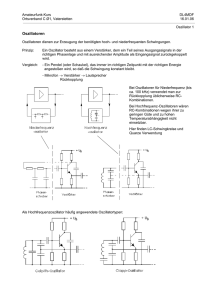

Phase Locked Loops - Grundlagen - cqDL Januar 2009 Phase Locked Loops finden sich in den verschiedensten Kommunikationsapplikationen. Sie werden eingesetzt in Modulatoren, Demodulatoren, Oszillatoren, Synthesizern, Taktsignalaufbereitungen usw.. Im Folgenden schauen wir uns die Wirkungsweise der einzelnen Elemente an und erarbeiten uns mit einigen Experimenten die Grundlagen der geschlossenen Phasenregelschleifen (engl. Phase Locked Loops). Hintergrund Die Phase Locked Loop (PLL) hat ihre Wurzeln in der Empfängertechnik. Sie wurde 1932 zur Erhöhung der Frequenzstabilität von Oszillatoren erfunden [2]. Die PLL wurde später in Fernsehempfängern zur Synchronisierung der horizontalen und vertikalen Ablenksignale mit dem empfangenen Videosignal eingesetzt. Mit der Verfügbarkeit von PLL-Schaltungen in ICs in den 60er Jahren des letzten Jahrhunderts verbreitete sich diese Technik sehr schnell. Beginnen wir mit dem Namen. „Phase“ oder auf Deutsch „Phase“ bezieht sich auf die Phasendifferenz eines externen Signals (Eingangssignal) und des Signals des internen Oszillators. „Locked“ oder „abgeschlossen“ bedeutet hier, daß die Phasendifferenz zwischen internem Oszillator und externem Signal konstant ist. Damit ist auch die Frequenz der beiden Signale identisch, denn andernfalls würde sich die Phasendifferenz ändern. „Loop“ oder „Schleife“ kommt von der Rückkopplungsschleife, die den internen Oszillator so steuert, daß dessen Frequenz fest mit der Frequenz des Eingangssignals gekoppelt ist. Die Rückkopplung ist der Schlüssel für die Funktion der PLL. Betrachten wir die Arbeitsweise eines Operationsverstärkers [3], [4]. Dabei wird das Differenzsignal zwischen invertierendem und nichtinvertierendem Eingang verstärkt und das Ausgangssignal so ausgebildet, daß es über die externe Beschaltung diese Eingangsdifferenz ausgleicht. Diese Art von Rückkopplung nutzt Spannung und Strom. Im Gegensatz dazu erfolgt dies mit Frequenz und Phase bei der PLL. Die Einzelteile der Schleife Eine PLL besteht aus drei Grundelementen (Bild 1) – einem Phasendetektor, dem Schleifenfilter und einem VCO (Voltage Controlled Oscillator = spannungsgesteuerter Oszillator). Bild 1 : Elemente einer PLL Der Phasendetektor arbeitet als Mischer und liefert am Ausgang u. a. die Summe und Differenz der beiden Frequenzen. Das Schleifenfilter extrahiert den Gleichspannungsanteil aus dem Mischerausgangssignal, daß dann das Steuersignal für den VCO bildet. Der Ausgang des Phasendetektors besteht aus einem Signal, daß die Differenz in Frequenz und Phase zwischen Eingangssignal und VCO-Ausgangssignal enthält (Punkt C in Bild 1). Das Schleifenfilter produziert daraus die Steuerspannung (Punkt D in Bild 1) für den VCO. Der VCO ändert somit seine Frequenz solange, bis seine Frequenz der Eingangsfrequenz gleicht. Ganz einfach, oder? Betrachten wir das alles nochmal in Ruhe. Ein VCO ist eine besondere Version eines Oszillators, bei dem die Frequenz mittels einer Steuerspannung geändert wird. Ohne diese Steuerspannung schwingt der Oszillator mit seiner Freilauffrequenz f0. Je nach Schaltungsauslegung erzeugt der VCO die Frequenz f0 bei einer Steuerspannung von 0V. Zur Frequenzänderung hin zu tieferen bzw.höheren Frequenzen ist dann ein bipolares Steuersignal von z.B. –Uctrl ... +Uctrl erforderlich. Unipolare VCOs wiederum kommen mit nur einer Betriebsspannung aus, dafür liegt f0 nur bei z.B. der halben Betriebsspannung an. Als nächstes mag es verwundern, warum ein Mischersymbol für den Phasendetektor im Bild 1 gezeichnet ist. Das ist deswegen so, weil der Phasendetektor genau das ist – eine Variante eines Mischers. In cqDL Juli 2008 D:\DL2MAJ\Eagle\projects\Funky\Fun_2009\Fun_0109\funky0109.doc DL2MAJ 17.11.2008 Seite - 1 - habe ich Gleichungen angegeben, die die Ausgangssignale beim Mischen an einer Diode beschreiben. Die Phaseninformationen wurden da vernachlässigt. Berücksichtigt man die Phase, so ergibt sich für die Differenz zweier Eingangsfrequenzen f1 und f2 ein Ausdruck mit cos(2π(f1-f2)*t + θ). Das θ repräsentiert die Differenz der Phasen der beiden Eingangsfrequenzen. Wenn nun beide Frequenzen gleich sind, bleibt auch die Differenz der beiden Phasen konstant. Von vorstehend genanntem Ausdruck verbleibt somit nur mehr der cos(θ). Der cos einer Konstanten ist eine Konstante. Hier in unserem Fall verbleibt eine Gleichspannung, da ja die von der Zeit t abhängigen Anteile sich gegenseitig ausgelöscht haben. Diese Gleichspannung eignet sich nun hervorragend zur Frequenzabstimmung unseres VCO. Die hohe Frequenz des Summensignals f1+f2 eignet sich nicht als VCO-Abstimmspannung und muß deswegen entfernt werden. Diese Aufgabe, alles zu entfernen bis auf die Differenzfrequenz und die Phaseninformation, übernimmt das Schleifenfilter, das als Tiefpaßfilter dimensioniert wird. Abhängig von der Art des Phasendetektors und der Signalform (Sinus, Rechteck, Puls) muß das Schleifenfilter noch zusätzlich kurze Stromimpulse in eine sich langsam ändernde Spannung überführen. Die Arbeitsweise der PLL Nach Anschalten der Betriebsspannung an die PLL ohne ein Eingangssignal, schwingt der VCO mit der Freilauffrequenz f0. Erreicht nun ein Eingangssignal den Phasendetektor, bildet dieser die entsprechenden Mischprodukte wie Summen- und Differenzfrequenz. Das Schleifenfilter entfernt die Summenanteile und erzeugt eine VCO-Abstimmspannung. Diese wiederum verändert die VCO-Ausgangsfrequenz. Wenn Eingangsfrequenz und VCO-Frequenz nicht gleich sind, so ergibt sich entweder eine höhere oder niedrigere Spannung am Ausgang, je nachdem welche Frequenz höher ist. Diese Änderung der Abstimmspannung veranlasst den VCO sehr schnell (bei modernen HF-Schaltungen innerhalb von wenigen Millisekunden) zu einer Frequenzänderung, die wiederum sehr schnell eine Verringerung der Differenz der Eingangsfrequenzen am Phasendetektor bewirkt. Dadurch reduziert sich auch das Ausgangssignal des Phasendetektors und folglich des Schleifenfilters. Die Frequenzänderungen des VCO werden immer kleiner, bis schließlich Eingangs- und VCO-Frequenz den gleichen Wert aufweisen – der Regelkreis ist geschlossen, die PLL ist eingerastet. Jeder weiteren Änderung des PLL-Eingangssignals oder der VCO-Frequenz folgt eine Änderung des Schleifenfilterausgangssignals, sodaß beide Frequenzen immer den gleichen Wert aufweisen. Dieser Vorgang von Abgleich und Halten nennt sich „Fangen“. Die minimale und maximale Eingangsfrequenz, bei denen das Schleifenfilterausgangssignal den internen VCO auf die Eingangsfrequenz ziehen kann, heißt Fangbereich (Bild 2). Bild 2 : Charakteristische Frequenzbereiche einer PLL Die oberhalb bzw. unterhalb der Freilauffrequenz f0 liegenden Fangbereichsgrenzen fuF und foF müssen nicht zwangsweise symmetrisch um die Freilauffrequenz f0 angeordnet sein. D:\DL2MAJ\Eagle\projects\Funky\Fun_2009\Fun_0109\funky0109.doc DL2MAJ 17.11.2008 Seite - 2 - Wenn das Steuersignal proportional zum Cosinus der Phasendifferenz ist, wird dieses zu Null, wenn die Phasendifferenz 90° beträgt (cos90° = 0). Bei Phasengleichheit ergibt sich das Maximum (cos0 = 1), bei entgegengesetzter Phasenlage das Minimum (cos180° = -1). Das definiert den Bereich, über den die PLL die Eingangs- und VCO-Frequenz zusammenhalten kann. Bewegt sich die Eingangsfrequenz immer weiter von der Freilauffrequenz f0 des VCO weg, hält der Regelkreis die VCO-Frequenz auf der Eingangsfrequenz fest. Die Phasendifferenz nähert sich dadurch aber immer mehr in Richtung 0° bzw. 180°, je nachdem in welche Richtung die Eingangsfrequenz wandert. Überschreitet die Phasendifferenz die Werte 0° bzw. 180°, so regelt das Steuersignal wieder in Richtung 90°. Allerdings bewegt sich die VCO-Frequenz damit weiter von der Eingangsfrequenz weg. Die Regelschleife ist nicht länger geschlossen und die Eingangsfrequenz und die VCOFrequenz weisen unterschiedliche Werte auf. Der Bereich zwischen Freilauffrequenz f0 des VCO und den Eingangsfrequenzen, bei denen die Regelschleife mit Phasendifferenzen zwischen 0 .. 180° geschlossen bleibt, nennt sich Haltebereich (engl. hold range). Die Haltebereichsfrequenzgrenzen foH oberhab der Freilauffrequenz muß nicht unbedingt gleich groß sein zur Haltebereichsfrequenzgrenze fuH unterhalb von f0. Aufbau einer PLL Dazu benutzen wir einen weit verbreiteten integrierten Schaltkreis, den LM565, der seit rund 40 Jahren verwendet wird. Das Datenblatt kann von der homepage des Herstellers National Semiconductor [5] unter cache.national.com/ds/LM/LM565.pdf heruntergeladen werden. Damit bauen wir die Schaltung nach Bild 3 auf. Bild 3 : Schaltung der PLL mit dem LM565 Am VCO-Ausgang schließen wir einen NF-Verstärker an, z.B. die Schaltung aus cqDL März 2008 [6] oder den Baustein AS208 des AATiS e.V. [7]. Die Stromversorgung erfolgt aus 2 Batterien zu je 9V, die wir in Serie schalten. Der Verbindungspunkt der beiden Batterien wird an GND angelötet, der freie Pluspol an +Ub, und der verbleibende Anschluß an –Ub. Bild 4 zeigt eine mögliche Aufbau- und Verdrahtungsvariante, in Bild 5 ist mein Musteraufbau zu sehen. D:\DL2MAJ\Eagle\projects\Funky\Fun_2009\Fun_0109\funky0109.doc DL2MAJ 17.11.2008 Seite - 3 - Bild 4 : Aufbau- und Verdrahtungsplan der PLL Bild 5 : Musteraufbau der PLL D:\DL2MAJ\Eagle\projects\Funky\Fun_2009\Fun_0109\funky0109.doc DL2MAJ 17.11.2008 Seite - 4 - Ohne Eingangssignal schwingt der VCO auf seiner Freilauffrequenz f0, die sich lt. Datenblatt [5] zu 1.2 f0 = --------------------- ≈ 1364Hz 4 * RT * CT Der angeschlossene NF-Verstärker verstärkt dieses Signal, der Lautsprecher setzt dieses in für uns hörbare Schallwellen um. Jetzt erweitern wir unseren Aufbau um einen variablen Oszillator, der das Eingangssignal für unsere Versuche bereitstellen soll. Dazu nutzen wir eine aus [8] modifizierte Schaltung (Bild 6). Bild 6 : Variabler RC-Generator Für den Aufbau folgen wir dem Vorschlag in Bild 7, Bild 8 zeigt den Musteraufbau. Bild 7 : Bestückungsplan für den variablen RC-Generator D:\DL2MAJ\Eagle\projects\Funky\Fun_2009\Fun_0109\funky0109.doc DL2MAJ 17.11.2008 Seite - 5 - Bild 8 : Musteraufbau des RC-Generators Zum Anschluß an unseren Testaufbau benötigen wir 4 Verbindungen – 3x Betriebsspannung (+Ub, GND, -Ub) und fout. Bild 9 visualisiert die Verdrahtung der einzelnen Baugruppen, Bild 10 die praktische Realisierung. Bild 9 : Verdrahtung des PLL-Versuchsaufbaus D:\DL2MAJ\Eagle\projects\Funky\Fun_2009\Fun_0109\funky0109.doc DL2MAJ 17.11.2008 Seite - 6 - Bild 10 : Foto des Experimentieraufbaus Die Betriebsspannungen wird mit den entsprechenden Leitungen der PLL verbunden, das Ausgangssignal fout muß an fin gelegt werden. Das Poti auf dem RC-Generator sollte in Mittelstellung stehen, wenn wir die Betriebsspannung einschalten. Wir hören, wenn alles richtig verdrahtet ist, einen Ton aus unserem Lautsprecher – wie vorher. Drehen wir jetzt am Poti, so ändert sich der Ton kontinuierlich – bis er plötzlich einen Sprung auf eine andere Frequenz macht. Weiterdrehen des Poti bewirkt nichts mehr. Wenn wir die Drehrichtung umkehren, erreichen wir wieder einen Punkt, wo ein erneuter Sprung in der Frequenz hörbar wird. Jetzt wechselt der Ton auch wieder mit dem Betätigen des Potis. Solange sich der Ton kontinuierlich damit ändert, befinden wir uns im Haltebereich der PLL. Nach dem Verlassen des Haltebereichs können wir durch Zurückdrehen des Potis wieder den Gleichlauf zwischen Potivariation und VCO-Frequenzänderung erreichen. Das geschieht mit dem Erreichen des Fangbereichs. Steht ein Oszilloskop oder ein Frequenzzähler zur Verfügung, so können die entsprechenden Frequenzen meßtechnisch bestimmt werden. Die Differenz der Frequenzen, bei dem wir die Kopplung Eingangssignal mit der VCO-Frequenz verlieren, ergibt den Haltebereich. Analog dazu liefert die Differenz der Frequenzen, bei denen der Gleichlauf wieder hergestellt wird, den Fangbereich. Verfügt das Oszilloskop über 2 Kanäle, so sehen wir die angesprochenen Frequenzen auch optisch. Mit Kanal 1 messen wir das Eingangssignal, die Triggerung erfolgt ebenso auf Kanal 1. Kanal 2 zeigt uns das VCO-Signal. Beide Signale stehen stabil auf dem Bildschirm, solange sich die Eingangsfrequenz im Haltebereich der PLL befindet. Außerhalb dieses Bereichs bekommen wir nur für das Eingangssignal im Kanal 1 ein stehendes Bild, die Anzeige im Kanal 2 läuft durch. Der Fangbereich unserer PLL wird vom Kondensator C4 zusammen mit einem im IC befindlichen Widerstand von 3.6kOhm festgelegt. Die Zeitkonstante dieser RCKombination errechnet sich zu t = R * C4 = 3.6kOhm * 10µF = 36ms Je größer die Zeitkonstante ist, desto länger dauert das Reagieren der PLL auf eine geänderte Eingangsfrequenz und desto kleiner ist der Haltebereich. Experimentiere mit anderen Kondensatorwerten bis herunter zu 1nF und beobachte wie sich die PLL verhält. Tabelle 11 listet meine Versuchsergebnisse auf. D:\DL2MAJ\Eagle\projects\Funky\Fun_2009\Fun_0109\funky0109.doc DL2MAJ 17.11.2008 Seite - 7 - Wert von C4 1.2nf 10nf 100nf 470nf 2µ2 10µ fuH [Hz] 605 610 655 630 634 ^636 fuF [Hz] 605 610 655 975 1117 1168 foH [Hz] 1825 1810 1780 1810 1790 1795 foF [Hz] 1825 1810 1780 1535 1390 1300 Freilauffrequenz f0 : 1282Hz Tabelle 11 : Charakteristische Frequenzen bei unterschiedlichen Zeitkonstanten Für Experimente rund um die PLL steht ein Materialsatz (Funky-PLL, ohne AS208) zur Verfügung, der bei Helmut Berka, DL2MAJ, Dornbuschweg 11, 86836 Obermeitingen ([email protected]) gegen Einsendung bzw. Überweisung von 10 Euro (Funky-PLL, ohne AS208, inkl. Versand) bzw. 20 Eur (Funky-PLL, inkl. AS208 und Versand) bezogen werden kann. Wer für seine Jugendarbeit auf die Versuche der Funky-Reihe zurückgreifen möchte, kann auch weiterhin entsprechendes Material (Funky-Bastlerbeutel, Funky- Signalgenerator, 2-TonSignalgenerator, Funky-Summierer, Funky-Doppelfilter) bei o.g. Bezugsquelle für jeweils 10 Euro pro Bauteilesatz (inkl. Versand) erhalten. Quellen : [1] QST September 2008 : Seite 71-72, H. Ward Silver, N0AX, Experiment #68 – Phase Locked Loops, the Basics [2] www.uoguelph.ca/~antoon/gadgets/pll/pll.html [3] cqDL November 2004 : Funky : Rund um den Operationsverstärker [4] cqDL Operationsverstärker <- ca. 1998 .. 2002 [5] Datenblatt von National Semiconductor, www.national.com [6] cqDL März 2008 : Funky : Summierer und NF-Verstärker [7] Praxisheft 18, Stereo-NF-Amp AS208 [8] cqDL Januar 2005 : Funky : Rund um den Oszillator D:\DL2MAJ\Eagle\projects\Funky\Fun_2009\Fun_0109\funky0109.doc DL2MAJ 17.11.2008 Seite - 8 -