Übungsblatt 6 mit Musterlösung

Werbung

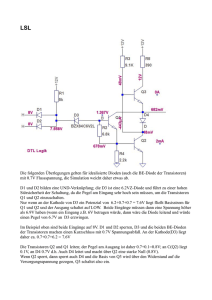

Musterlösung Übungsblatt 1 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 6 I Prof. Baitinger / Lammert Besprechung: 29.01.2001 S R Aufgabe 1 MOS-Widerstände U=10V C Abb_Dummy: 1.0 UC a) Zeichnen Sie einen Querschnitt durch einen MOS-Widerstand. Ein MOS-Widerstand entsteht aus einem MOS-Transistor dadurch, daß man Drain- und Gateanschluß miteinander verbindet. Abbildung: 1-1 Schaltung mit MOS-Widerstand A SiO2 Der MOS-Widerstand sperrt, wenn die Spannung über ihm unter die Schwellspannung abfällt. Das heißt I wird gleich 0, der Kondensator C kann somit nicht weiter aufgeladen werden und UC erreicht seinen Endwert UCend = 9V. Damit gilt: U = U th + U Cend => U th = U – U Cend = 1V B Al n+ n+ d) Wie groß ist der Strom I in dem Moment, in dem UC = 5V gemessen wird ? p- Aus der Bauweise eines MOS-Widerstandes (Gate- und Drain-Anschluß eines MOS-Transistors werden miteinander verbunden) kann man schließen, daß in diesem Fall gelten muß: Abbildung: 1-0 MOS-Widerstand U DS = U GS Wegen U DS = U GS > U GS – U th befindet sich der zur Herstellung dieses Widerstandes verwendete Transistor im gesättigten Bereich. Somit gilt: b) Nennen Sie zwei Nachteile von MOS-Widerständen. β β 2 2 I D = --- ⋅ ( U GS – U th ) = --- ⋅ ( U DS – U th ) 2 2 - spannungsabhängiger Widerstandswert - Offsetspannung c) Gegeben sei die Anordnung nach Abb. 1-1, wobei R ein MOS-Widerstand sei. Kurz nach Schließen des Schalters S mißt man den Strom I0 = 4.5 mA. Nach einiger Zeit stabilisiert sich die Spannung UC auf einen Wert von 9V. Berechnen Sie die Schwellspannung Uth des MOS-Widerstandes. Seite 1 von 11 wobei β die normierte Steilheit des zugundeliegenden MOS-Transistors ist (s. Vorlesung). Insgesamt ergibt sich also für unsere Schaltung die Beziehung: β 2 I D = --- ⋅ ( U – U C – U th ) 2 Seite 2 von 11 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 Kurz nach dem Schließen des Schalters S ist U C = 0V und daraus folgt β 2 I D = --- ⋅ ( U – U th ) = I 0 2 DCTL- NAND U+ RC I0 β --- = ------------------------2 2 ( U – U th ) y Für U C = 5V ergibt sich somit der gesuchte (Sättigungs-)Strom I = I D zu: A 2 ( U – U C – U th ) β 2 I = --- ⋅ ( U – U C – U th ) = I 0 ⋅ ---------------------------------------2 2 ( U – U th ) B Uy bzw. C 2 16 ( 10V – 5V – 1V ) I = 4, 5mA ⋅ --------------------------------------------- = 4, 5 ⋅ ------ mA = 0, 89mA 2 81 ( 10V – 1V ) Abbildung: 2-1 NAND-Gatter in DCTL-Technik Aufgabe 2 d) Wie groß ist die Ausgangsspannung Uy bei diesem NAND-Glied, wenn alle Eingänge auf dem logischen Wert 1 liegen? Dabei soll angenommen werden, dass bei einem gesättigten Transistor die Collector-Emitter-Spannung USat=0,2V beträgt. DCTL-Technik Abb_Dummy: 2.0 a) Was bedeutet die Abkürzung DCTL? DCTL=direct coupled transistor logic=direkt gekoppelte Transistorlogik b) Aus welchen Bauelementen ist eine Schaltung in DCTL-Technik aufgebaut? In diesem Fall sättigen alle drei Transitoren, wobei sich die Sättigungsspannungen an den Ausgängen der Transitoren wegen der Reihenschaltung addieren, d. h. Uy=3USat=0,6V. Es werden ausschließlich Transistoren und Widerstände verwendet. c) Zeichnen Sie ein NAND-Glied in DCTL-Technik mit drei Eingängen A, B und C sowie einem Ausgang y. Die Reihenschaltung der Transistoren ergibt eine UND-Verknüpfung, wobei die Logikfunktion durch die Schaltung noch negiert wird. Dadurch erhält man ein NAND-Gatter. e) Welches Problem ergibt sich bei der Reihenschaltung von Transistoren in der DCTL-Technik? Wenn alle Transistoren leiten und damit sättigen, sollte die Ausgangsspannung eigentlich 0V sein. Dadurch dass die Sättigungsspannungen der Transistoren immer etwas größer als 0V sind, ergibt sich beim Gatter eine Ausgangsspannung, die so groß sein kann, dass ein nachfolgendes Logikgatter dies als logische 1 auffasst. f) Erstellen Sie ein DCTL-Logikgatter, das die logische Funktion z = ( A + B ) ⋅ C realisiert. Dabei sollen nur drei Transistoren verwendet werden. Seite 3 von 11 Seite 4 von 11 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 Die ODER-Verknüpfung A+B wird durch eine Parallelschaltung der Transistoren realisiert, während die UND-Verknüpfung eine Reihenschaltung erfordert. Die Logikfunktion wird durch die DCTL-Schaltung insgesamt noch negiert, wodurch sich die gesuchte Logikschaltung nach Abb. 2-2 ergibt. DCTL- Gatter c) Welche Vorteile hat die TTL-Technik gegenüber der DTL-Technik? Bei der TTL-Technik ergibt sich eine Platzeinsparung gegenüber der DTL-Technik und die Schaltzeiten werden verkürzt. Der Multi-Emitter-Transistor sorgt auch noch für eine Stromverstärkung. d) Zeichnen Sie je ein NAND-Glied in DTL- und TTL-Technik mit drei Eingängen A, B und C. U+ DTL- NAND RC U+ RC z R1 C ABC A A R2 B B C Abbildung 3-1: NAND-Gatter in DTL-Technik Abbildung: 2-2 DCTL-Gatter Aufgabe 3 TTL- NAND DTL- und TTL-Technik U+ a) Erklären Sie die Begriffe DTL- und TTL-Technik. R1 RC DTL=Dioden-Transisitor-Logik, ABC TTL=Transitor-Transitor-Logik b) Beschreiben Sie in Stichworten die technologischen und schaltungstechnischen Merkmale beider Logikfamilien. Erklären Sie dabei, wie die TTL-Technik aus der DTL-Technik hervorgeht. In der DTL-Technik übernehmen die Dioden zusammen mit einem Widerstand die logische Verknüpfung, während der Transistor für die Spannungsverstärkung und die Negation verantwortlich ist. Dadurch, daß der Transistor nur als Verstärker auftritt, kann bei einer logischen „0“ am Ausgang höchstens ca. 0,2V anliegen. A B C Abbildung 3-2: NAND-Gatter in TTL-Technik Bei der TTL-Technik werden die Dioden der DTL-Schaltkreise durch einen Transistor mit mehreren Emitter-Eingängen (= Multi-Emitter-Transistor) ersetzt. Ansonsten hat ein TTL-Gatter den gleichen Aufbau wie ein entsprechendes DTL-Gatter. Seite 5 von 11 Seite 6 von 11 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 e) Eine Schaltung mit der logischen Funktion y=A xor B soll in TTL-Technik realisiert werden. Überlegen Sie sich dazu zunächst eine geeignete Darstellung dieses logischen Ausdrucks, so dass eine Realisierung in TTL-Technik möglich wird. Zeichnen Sie dann die dazugehörige TTL-Schaltung unter der Voraussetzung, dass alle Eingangsvariablen auch negiert zur Verfügung stehen. Aufgabe 4 ECL-Technik In Abbildung 4-1 ist der Grundschaltkreis der ECL-Technik mit drei Eingängen A, B und C sowie den Ausgängen y1 und y2 gegeben. U+ Der logische Ausdruck muss in eine NAND-Darstellung umgeformt werden: A xor B= ( A ∧ B ) ∨ ( A ∧ B ) = ( A ∧ B ) ∧ ( A ∧ B ) =(A nand B) nand (A nand B). Damit ergibt sich die Schaltung nach Abb. 3-3. RC2 RC1 Ty1 B A Ty2 U1 C y2 U+ R1 TA TB TR TC RC Uref U2 RE R1 A B Ry1 Uy1 Uy2 Ry2 RC y R1 y1 = Abbildung 4-1: Grundschaltkreis der ECL-Technik a) Was bedeutet die Abkürzung ECL und welcher andere Begriff ist dafür auch noch gebräuchlich? RC ECL=emitter coupled logic=Emittergekoppelte Logik. Es wird auch der Begriff CML (=current mode logic) verwendet. b) Warum hat eine ECL-Schaltung kürzere Schaltzeiten im Vergleich zu den anderen bipolaren Transistorschaltungen? A B Die ECL-Technik arbeitet im Unterschied zu den anderen Transistorschaltungen nicht mit gesättigten Transistoren, wodurch Abschaltverzögerungen vermieden werden. Abbildung 3-3: Logikschaltung in TTL-Technik c) Welche beiden logischen Funktionen liefert der Grundschaltkreis der ECLTechnik an den Ausgängen y1 und y2? Am Ausgang y1 wird eine NOR-Verknüpfung geliefert, während der Ausgang y2 eine ODER-Verknüpfung liefert. d) In welchen Spannungbereich muss eine Eingangsspannung Ue liegen, die den logischen Eingangswert 0 für das ECL-Gatter darstellt? Welcher Bereich gilt für den logischen Wert 1? Für eine logische 0 muss Ue<Uref sein, für eine logische 1 muss Ue>Uref gelten. Seite 7 von 11 Seite 8 von 11 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 e) Erklären Sie die Funktionsweise des Grundschaltkreises, wenn die Eingangsbelegung von ABC=000 auf ABC=001 wechselt. Bei der Eingangsbelegung ABC=000 sperren die Transistoren TA, TB und TC, da ihre Eingangsspannungen kleiner als Uref sind, während der Transistor TR leitet. Steigt nun die Eingangsspannung von TC auf einen Wert, der größer als die Referenzspannung Uref ist,so steigt dessen Basis-Emitter-Spannung an und er beginnt zu leiten. Dadurch wird das Potential am Emitterwiderstand RE größer, wodurch die Basis-Emitter-Spannung von TR sinkt und dieser zu sperren beginnt. hochohmig ausgelegt werden und F2 und F3 niederohmig. Für die geometrischen Abmessungen ergeben sich folgende Beziehungen: • F1 lang und schmal • F2 und F3 kurz und breit. Dies sind Einschränkungen, die der Packungsdichte auf einem Silizium-Chip entgegenwirken. Außerdem wird der Kondensator Ca über unterschiedlich hohe Widerstände der Transistoren auf- bzw. entladen, was die Geschwindigkeit einschränkt. NMOS-NAND U+ f) Wofür sind die Transistoren Ty1 und Ty2 notwendig? Die beiden Transistoren sind für die Pegelanpassung der Ausgangsspannungen notwendig. Wenn z. B. die Ausgänge y1=0 und y2=1 sind, so gilt zwar für die Spannungen U1 und U2, dass U1<U2 ist, jedoch sind beide Spannungen größer als Uref. Dadurch können nachfolgende Gatter nicht mit diesen Ausgangsspannungen angesteuert werden (vgl. Teilaufgabe d)). Durch die Transistoren Ty1 und Ty2 werden die Spannungen U1 und U2 so erniedrigt, dass Uy1<Uref wird und Uy2>Uref bleibt. Aufgabe 5 F1 AB A F2 Ca B F3 Logikschaltungen Abb_Dummy: 3.0 Eigenschaften der verschiedenen Logikfamilien. Abbildung 5-1: a) Erklären Sie folgenden Begriffe: • NMOS • CMOS b) Beschreiben Sie in Stichworten die technologischen und schaltungstechnischen Merkmale der Logikfamilien. c) Skizzieren Sie je eine NAND-Schaltung in NMOS und CMOS. NMOS (N-Kanal-MOS) NMOS Schaltungen werden aus N-Kanal-FETs aufgebaut. Da bei diesen Transistoren kein Dauerstrom in das Gate fließt, benötigen sie eine kleinere Ansteuerleistung als bipolar-Transistoren (der FET-Transistor wird durch das elektrische Feld gesteuert). Die Kapazität Ca stellt den MOS-Kondensator der nachfolgenden Logikschaltung dar, der auf- bzw. entladen werden muß. Wenn also die Transistoren F2 und/oder F3 sperren, lädt sich der Kondensator Ca über den Transistor F1 auf. Dadurch erhält man am Ausgang eine „1“. Wenn die Transistoren F2 und F3 leiten, entlädt sich der Kondensator Ca auf die durch den Spannungsteiler F1 und F2-F3 festgelegte Spannung. F1 muß deshalb Seite 9 von 11 CMOS [complementary MOS]: Hier werden sowohl NMOS als auch PMOS Transistoren verwendet. Das gestaltet die Herstellung schwieriger, behebt allerdings viele Nachteile eines reinen NMOS oder PMOS Aufbaus. Die NMOS und PMOS Transistoren werden niederohmig ausgelegt, was zu extrem kurzen Schaltzeiten führt, da sich der Kondensator Ca mit einem höheren Strom auf- und entladen kann. Auch können die Transistoren dadurch kleiner bemessen werden, was den Platzverbrauch durch das doppelte Vorhandensein aller Bauelemente kompensiert. Die Lade- und Entladezeiten des Kondensators Ca sind identisch. Durch den dualen Aufbau aus NMOS und PMOS Schaltungen leitet immer nur eine Baugruppe, was die Gleichstromverlustleistung niedrig hält. Seite 10 von 11 Elektrotechnische Grundlagen, WS 00/01 U+ CMOS-NAND A AB Ca B Abbildung 5-2: d) Warum nimmt die Verlustleistung von CMOS-Schaltungen mit der Schaltfrequenz zu? Wenn die Frequenz zunimmt, müssen die MOS-Kondensatoren öfters auf- bzw. entladen werden. Das erfordert mehr Leistung. Aufgabe 6 Vergleich Logikfamilien Wie unterscheiden sich die in den vorherigen Aufgaben erwähnten Logikfamilien hinsichtlich ihrer Schaltzeiten und den Verlustleistungen? Schaltzeiten: NMOS < CMOS < ECL < TTL < DTL < DCTL Verlustleitung: CMOS < NMOS < ECL < TTL < DTL < DCTL Seite 11 von 11