UniversitätÈOsnabrück Vorlesung Elektronik Dr. W. Bodenberger

Werbung

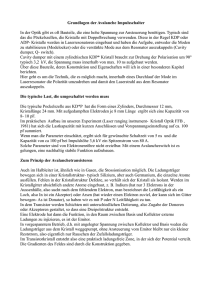

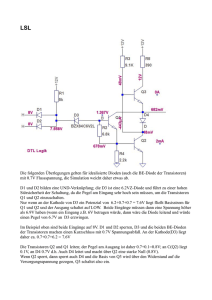

Universität Osnabrück Vorlesung Elektronik Dr. W. Bodenberger Aufbau von Planartransistoren Abbildungen aus dem Siemens Fachbuch Electronic Semiconductor Components 1 Universität Osnabrück Die einzelnen Produktionsschritte Vorlesung Elektronik Dr. W. Bodenberger 2 Universität Osnabrück Vorlesung Elektronik Dr. W. Bodenberger 1 AUfbau von Leistungstransistoren 1) Epitaxial Leistungstransistoren Für Leistungstransistoren ist der Herstellungsprozeß für Planartransistoren nicht geeignet. Der Planarprozeß ist nur für dünne Basiszonen zu gebrauchen. Bei Leistungstransistoren benötigt man hohe Basisströme, deshalb eignen sich nur Epitaxie-, Einfach- und DreifachDiffusions Herstellungsprozesse, um dicke, homogene Basisschichten zu erhalten. In der nebenstehenden Abbildung ist das Schichtabbild eines Leistungstransistors mit Epitaxie-Basis-Schicht dargestellt. Ausgangsmaterial ist hochdotiertes n-Silizium. Auf diese Schicht läßt man eine p-Silzium epitaktisch aufwachsen. In die aufgewachsene p-Schicht läßt man Phosphor in einzelnen miteinander verbundenen Inseln eindiffundieren, dies sind die Emitterzonen dea Transistors. Die Basis liegt ringförmig um die Emitterzonen. Mit diesem Verfahren lassen sich Transistoren mit ca. 100 Watt Verlustleistung und Kollektorströmen von 15 Ampere herstellen. Die obere Grenzfrequenz dieser Leistungstransistoren liegt bei 5 MHz. Einfach-diffundierte Leistungstransistoren Ausgangsmaterial ist ein p-dotierter Si Wafer, der von beiden Seiten in einem einzigen Diffusionsschritt n-dotiert wird. Die eine Seite der diffundierten Schicht wird nicht strukturiert und bildet die Kollektorzone. Die obere Seite des Wafers wird fingerartig strukturiert und bildet die Emitterzonen mit dazwischen liegenden Basiszonen des ursprünglichen p-Siliziums. Man erhält damit Transistoren mit hoher Verlustleistung bis ca. 150 Watt. Nachteilig wirkt sich auf Grund des Herstellungsverfahrens die geringe obere Grenzfrequenz von nur 1 MHz aus. Mit diesem Verfahren lassen sich nur npn-Transistoren herstellen. Universität Osnabrück Vorlesung Elektronik Dr. W. Bodenberger 2 Dreifach-diffundierte Leistungstransistoren Für noch größere Verlustleistung muß der Herstellungsprozeß noch weiter verbessert werden. Ausgangsmaterial ist diesmal schwach dotiertes n-Silizium. In einem ersten Diffusionsprozeß erzeugt man mit Phosphor Eindiffusion eine stark dotierte n-Siliziumschicht. Eine zweite Diffusion von Bor, die sich über den ganzen Wafer erstreckt, erzeugt die Basisschicht. Die dritte Diffusion von Phosphor erzeugt die n-Emitter-Bereiche des Transistors. Dreifach diffundierte Transistoren haben im Vergleich zu Epitaxial- und Einfach-Diffundierten Transistoren eine schwach dotierte Kollektorzone, in die sich bei angelegten hohen äußeren Spannungen die Verarmungszone ausbreitet. Die Verlustleistung beträgt ungefähr 200 Watt. Die Spannungsfestigkeit dieser Transistortypen beträgt mehrere Kilovolt. Die Schaltzeiten der Transistoren sind sehr kurz. Der Feldeffekt - Transistor (FET) Der Feldeffekttransistor ist im Gegensatz zum Bipolartransistor ein unipolarer Transistor. Bei einem Unipolar-Transistor sind die Ladungsträger entweder Elektronen oder Löcher, die den Strom durch das Bauelement transportieren. Das bedeutet, daß es nur reine n-Typ und nur reine p-Typ Feldeffekttransistoren gibt. Der Flächentransistor hat einen prinzipiellen Nachteil, er läßt sich nicht wie z.B. eine Elektronenröhre leistungslos steuern. Seine Steuerelektrode, in Emitterschaltung z.B. die Basis, verlangt von der Signalquelle einen endlichen Steuerstrom, da die Basis-Emitter-Diode im aktiven Bereich in Durchlaßrichtung betrieben werden muß. Feldeffekt-Transistoren besitzen diesen Nachteil nicht, ihr Steuerleistungsbedarf ist ähnlich gering wie der von Elektronenröhren. Die Wirkungsweise eines FET beruht darauf, daß man die Leitfähigkeit eines Halbleitermaterials verändern kann, indem man durch elektrische Felder die Konzentration der frei beweglichen Ladungstrager im Material variiert. Je nachdem, welches spezielle Verfahren man zur Steuerung der Ladungsträger-Konzentration anwendet, unterscheidet man verschiedene Typen von FET-Transistoren. Eine Übersicht über die gebräuchlichsten Varianten mit ihren Schaltsymbolen gibt die nachfolgende Abbildung. Schaltsymbole für Junction FET und MOS FET (Metal Oxyd Semiconductor FET) Transistoren P-Kanal A) n-Kanal B) p-Kanal c) n-Kanal D) p-Kanal E) n-Kanal F) A) bis D) Selbstleitende Feldeffekt-Transistoren E) bis F) Klassifizierung: Selbstsperrende Feldeffekt-Transistoren A) und B) Sperrschicht Feldeffekt-Transistoren (Junction FETs) C) bis F) MOS FETs Im Schaltsymbol wird die Durchlaßrichtung des PN-Überganges zwischen Substrat (Grundmaterial) und Source durch einen Pfeil dargestellt. Insgesamt gibt es noch zwei weitere Gruppen von Feldeffekttransistoren, das sind unter anderem Junction Fets und MOSFET Feldeffekttransistoren. Zu Erklärung der Funktionsweise des Junction Fets (Sperrschicht Fets) ist der Schichtaufbau eines Fets in der folgenden Abbildung dargestellt. Der Junction Fieldeffect Transistor (JFET) beteht aus einem n- oder p-dotierten Silizium Block, in dem seitlich zwei p- oder n-Inseln eindiffundiert sind, je nach dem, ob es sich bei dem Grundmaterial um noder p-dotiertes Silizium handelt. Legt man an beiden Enden des p- oder nGrundmaterials eine Spannung an, so fließt gleichgültig wie die Polarität der angelegten Spannung auch sein mag ein Strom vom Pluspol zum Minuspol der Spannungsquelle. Bei n-dotierten Material fließt der Strom von der Sourceelektrode zur Drainelektrode. Durch die beiden seitlichen Steuerelektroden läßt sich der Strom durch den Feldeffekttransistor steuern. Legt man eine negative Spannung an das Gate an, so breitet sich die Verarmungszone in den Kanal zwischen Source und Drain aus. Der Stromfluß von der Source zum Drain wird durch die Ausbreitung der Verarmungszone sehr viel kleiner. Durch die Verengung des Kanals wird der Strom von der Source zur Drain stark verkleinert, bis es bei hohen negativen Spannungen an der Gateelektrode zur Abschnürung des gesamten Stromes durch den Transistor kommt. Junction FETs werden als Verstärker für Analogsignale bei hohen Frequenzen benutzt. In der untenstehenden Abbildung ist das Ausgangskennlinienfeld und die Eingangangskennlinie eines Junction FETs dargestellt. Der MOS-Transistor Eine Steuerspannung beeinflußt die Leitfähigkeit einer dünnen Oberflächenschicht eines HalbleiterKristalles. Die Steuerelektrode ist bei allen Metalloxydfeldeffekttransistoren vom Kristall durch eine isolierende Metalloxydschicht vom Halbleiterkristall getrennt. MOS-Transistoren eignen sich wegen ihres einfachen und kostengünstigen Herstellungsprozesses besonders zur Herstellung großflächiger Integrierter Schaltungen. Als Beispiel für die Funktionsweise eines MOS-Transistors soll im folgenden ein p-Kanal MosTransistor vom Anreicherungstyp (enhancement type) betrachtet werden. Ohne Spannung an der Steuerelektrode (Gate-electrode) fließt kein Strom durch den Transistor, da beide Pn-Übergänge den Stromfluß verhindern, sie sind in Sperrichtung gepolt. Legt man an die Steuerelektrode eine negative Spannung an, so werden die unter der Gate-elektrode im n-Silizium befindlichen Elektronen von dem herrschenden elektrisch Feld in den Kristall zurück getrieben. Die Löcher aus Source und Drain werden dagegen unter die Gate-elektrode gezogen. Unterhalb der Steuerelektrode entsteht ein p-leitfähiger Kanal, das hat zur Folge, daß ein Strom von der Source-elektrode zur Drain fließen kann. Je größer die Steuerspannung an der Gate-elektrode wird, desto größer wird auch der Drainstrom IDS durch den Transistor. Von der Art der Leitfähigeit der Source-Drain-Strecke unterscheidet man zwei Arten von MOSTransistoren. Anreicherungs MOS-FET (enhancement transistor). Ohne Gatespannung sperrt die Source-DrainStrecke, es fließt kein Strom von der Source zur Drain, die Strecke ist nichtleitend. Besonders p-Typ MOSFETs sind vom Anreicherungstyp. Die zweite Art von MOSFETs, klassifiziert nach der Leitfähigkeit des Kanals, sind Verarmungs MOSFET-Typen (Depletion MOS-transistors). Ohne Gate-Spannung ist die Source-Drain-Strecke permanent leitfähig. Erst durch Anlegung einer Gate-Spannung läßt sich der Kanal zwisch Source und Drain sperren. Für alle Arten von Feldeffekttransistoren gilt gemeinsam, daß bei einem Strom durch den SourceDrain-Kanal der Transsitor in beiden Richtungen leitet. DIe Kennlinien der verschieden Feldeffekt-Transistoren unterscheiden sich nur wenig voneinander. MNOS-Technologie Mit dieser Technologie lassen sich sog. EEROMS realisieren. Bei diesen EROMS (Electrically re-programmable Read only Memories) wird die Gate-elektrode, die sehr dünn ist, mit einer Schicht Silizium Nitrid beschichtet. Die Programmierung geschieht durch Speicherung von Ladungen an der Zwischenschicht Nitrid - Gate Oxyd mittels eines Spannungspulses im gerade ausgewählten Transistor. Die Ladungen sind nichtflüchtig und bewirken, daß durch die gespeicherten Ladungen der Transistor durchgeschaltet wird, er bleibt dauernd leitfähig. Mit einem Entladepuls entgegengesetzter Polarität können die Ladungen wieder zum abfließen gebracht werden. Die Speicherstelle wird damit mit einer entgegengesetzten Polarität versehen. Der Transistor wird gesperrt. Ein Auslesen der gespeicherten Information hat keine Auswirkungen auf die Ladungen, sie bleiben dauerhaft erhalten. Erst durch Umprogrammieren, kann die Ladung wieder zum Abfließen gebracht werden. Eine Zusammenstellung der wichtigsten Prozesse zur Herstellung von MOS-Schaltungen ist in den folgenden Abbildungen zu sehen. P-Mos Device mit Aluminium Gate einfachster MOS Prozeß geringste Produktionskosten.Enhancement Typ. P-MOS mit Silizium Gate und mit damit verbundenen Kondensator. Anwendung: Speicher Ics. N-MOS mit Silizium Gate, höchste Verarbeitungsgeschwindigkeit. Sehr hohe Verarbeitungsgeschwindigkeit.Anwendung: Memory Ics, Mikroprozessoren. Sehr schwieriger Herstellungsprozeß. N-MOS mit Aluminium Gate, niedrige Schaltzeiten, niedrige Versorgungsspannung (5Volt).Kritischer Herstellungsprozeß.Anwendungen: Speicher Ics, Mikroprozessoren. P-MOS Integrierte Schaltungen mit Verarmungs- und Anreicherungs-Transistoren Um noch bessere elektrische Eigenschaften der Transistoren zu erreichen muß man weitere Prozeßschritte bei der Herstellung einfügen. Besonders wichtig ist die Verringerung der threshold Spannung bei MOS ICs. Dazu dienen die in den folgenden Bildern dargestellten Schritte bei der Herstellung der Speicher ICs, Mikroprozessoren und Standard Logik-Schaltungen. Mittels Ionenimplantation werden Bor Ionen auf den nach dem Standard Herstellungsverfahren hergestellten Chip geschossen. Die Bor Ionen durchdringen die Oxydschicht nur im Gate-Gebiet der Transistoren und erhöhen die Leitfähigkeit des Kanals vorm Sperren des Transistors.(Injektion von Löchern im Gatebereich). Im zweiten Schritt werden durch die Ionen Implantation ein Teil der Transistoren zu Verarmungstransistoren umgewandelt. Nur die nicht mit Photolack bedeckten Gatebereiche werden durch den Ionenbeschuß von Enhancement Typ zu Depletion Typ Transistoren umgewandelt. Vorteile:Kleinere Verustleistung des Chips als bei normalen Standard P-MOS Ics. Begründung warum? Anwendung:Mikroprozessoren ,Memories und Kundenspezifische ICs.l CMOS Technologie CMOS Schaltungen bestehen jeweils aus zwei komplementären Transistor Typen. Es ind jeweils ein n-Kanal und ein p-Kanal Transistor in Serie geschaltet. Dies sind zwei selbsleitende Transistoren. Zuerst werden die p-leitenden Bereiche in ein n-leitendes Grundsubstrat eindiffundiert. In einem zweiten Diffusionsprozeß werden die n- Bereiche für den n-Kanal Transistor in der p-Röhre eindiffundiert. Da bei zwei in Serie geschalteten komplementären Transistoren jeweils einer der beiden Transistoren gesperrt ist kann kein Strom von der Spannungsversorgung zum Substrat fließen. Die statische Verlustleistung von CMOS Schaltkreisen ist deshalb extrem gering, außerdem sind die Gatterschaltzeiten sehr klein. Nachteile: Komplizierte Herstellung und nur wenige Transistoren lassen sich auf einem Chip anordnen. Flächenbedarf ist 50% größer als bei p-MOS Schaltungen. Charge Coupled Devices CCD-Chips CCD-Chips sind ähnlich aufgebaut wie MOS-Chips. Sie unterscheiden sich jedoch wesentlich von MOS Schaltungen durch ihre Betriebsart. In CCD Chips werden elektrische Ladungen schrittweise von einem Element des Schaltkreises zum nächsten Element transportiert, wie in einem Schieberegister. Datensignale am Eingangstransistor werden in elektrische Ladungen umgewandelt und schrittweise wie in einer Eimerkette weiter transportiert.