5. Digitalschaltungen

Werbung

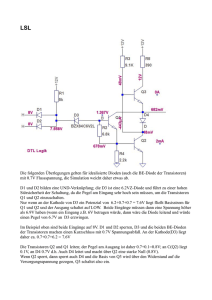

105 106 Def.: Digitalsignale sind zeit- und wertdiskret. 5. Digitalschaltungen 5.1 Grundbegriffe: Diese Definition geht von einem synchronen System aus, d.h. einem System, in dem Zustandsänderungen in festen, von einer zentralen Zeitbasis (Takt) bestimmten Zeitintervallen stattfinden. Ist dies nicht der Fall, liegt ein .asynchrones. System vor, in dem Zustandsänderungen zeitkontinuierlich erfolgen. Der .Wert. eines Signals hängt davon ab, wie Information übertragen wird. Wir beschäftigen uns mit Systemen, in denen Signale durch eine Spannungs- oder Stromamplitude übertragen werden. Die Amplitude gibt dann den Wert an. Sie ist der z.B. AD-Umsetzer, Switched-Capacitor-Logik Analogsignal .Informationsparameter. Neben der Amplitude gibt es andere Informationsparameter, z.B. - die .Frequenz einer Schwingung. (Modem) - die .Form eines Impulses. diskrete Werte Signal in asynchroner Digitaltechnik Digitalsignal (synchrone Digitaltechnik) In digitalen Schaltungen wird Information meist über .zweiwertige. („binäre“) Digitalsignale übertragen und zwar mit der .Spannungsamplitude. als Parameter. Die vier Hauptgruppen von Signalen 107 Der gesamte Amplitudenbereich wird dann unterteilt: U 108 Def.Gatter: Elementare Schaltung, die über .Digitalsignale. mit der Umgebung kommuniziert. ....H...... - Pegel Das Gatter implementiert eine ..Funktion der Schaltalgebra., UH UH ! UL z.B. .NAND, AND, OR, XOR. bzw. eine Speicher- UL funktion, z.B. ein Flip-Flop. ....L...... - Pegel Weitere Größen werden am Beispiel eingeführt. U t UH : Signal hat “H“ - Pegel (“H“) U d UL : Signal hat “L“ - Pegel ( “L“) UH ! U ! UL : Signal hat undefinierten Pegel UB = 5V Der Wechsel zwischen Pegeln wird auch als .Schalten. bezeichnet. Als Schnittstelle zur Schaltalgebra (Implementierung einer boolschen Logik) weisen wir den Pegeln logische Werte zu: U logischer Wert H L 0 1 RC = 5kȍ Strombegrenzung RB = 9kȍ Ue Ua RL = 5kȍ positive Logik Inverterschaltung Schaltbild undef. H L 0 Die angegebene Schaltung liefert zu einem definierten H- oder L- Pegel negative Logik 1 am Eingang den jeweils anderen am Ausgang. Der logische Wert wird also invertiert, die Schaltung ist ein .Inverter. undef. Der schraffierte Bereich ist .für Umschaltvorgänge. Der Ausgang des Inverters werde, z.B. durch nachfolgende Schaltungen, zwischen H- und L- Pegel reserviert. mit einer ohmschen Last von RL = 5kȍ belegt. Dämpfung gewünscht 109 Sperrbereich 110 Dynamische Kerngrößen: Analogtechnik: Angabe des dyn. Verhaltens durch Bode- Diagramm/ Ortskurve Steigung = -1 Digitaltechnik: Angabe durch Verzögerungszeiten aktiver Bereich 1,7V Verstärkung erwünscht 1,2V Sättigung Dämpfung gewünscht Übertragungskennlinie des Inverters mit Last RL = 5kȍ Wir definieren: das Gatter G2 weist für Ue d UL A und Ue t UH einen definierten Ausgangspegel auf. Rechteckverhalten des Inverters Definition der Gatterlaufzeit Störsicherheit: tS: Speicherzeit (storage time) (Signalverzögerungszeit) Zur Bestimmung der Störsicherheit bestimmen wir die Störspannung, die bei der Signalübertragung auftreten darf, ohne daß der Signalpegel verfälscht wird. tA: Anstiegszeit (rise time) tpd: propagation delay time tV: Verzögerungszeit (delay time) tF: Fallzeit (fall time) ..Störung............... tpdH: Verzögerung für Übergang L -> H tpdL: Verzögerung für Übergang Ue1 G1 G2 Ua1 Ue2 Ua2 H -> L Durch Einführen der Verzögerungszeiten erreicht man die Vereinfachung des Entwurfs und der Abschätzung des dynamischen Verhaltens einer Gatter 1 Schaltung. Gatter 2 111 112 5.2. Komplementäre MOSFET (CMOS- ) Logik CMOS-Schaltungen werden aus selbstsperrenden p-Kanal und n-Kanal MOSFETs aufgebaut. 1,7V US 1,2V p-Kanal-Typ S G Bestimmung des Störabstandes Das Gatter G1 hat die gleiche Übertragungskennlinie wie G2. T2 D IG ID Ia Am Eingang von G2 muß für definierten Ausgangspegel gelten: D UH d Ue2 oder UL t Ue2 Wir tragen UH und UL als Grenzwerte der Ausgangsspannung Ua1 von G1 ein, für die im störungsfreien Zustand geraden noch ein definierter Pegel am Ausgang von G2 anliegt. Ue G Ua S T1 n-Kanal-Typ Def: Störabstand: Inverter in CMOS-Technik SL = ............................................ bei Ue1 = UB (d.h. H-Pegel am Eingang) SH = ............................................ bei Ue1 = 0V (d.h. L-Pegel am Eingang) Sehr einfacher Aufbau bestehend aus nur 2 Transistoren ohne passive Der Störabstand ist ein Maß für die Störsicherheit eines digitalen Elemente Systems. mit sehr geringem Platzbedarf zu integrieren. Im Beispiel: Ua (Ue = 0V) = 2,5V In statischem Zustand gilt: Ua (Ue = 5V ) = 0,25V SL = .1,2V - 0,25V = 0,95V. SH = . 2,5V - 1,7V = 0,8V. ............................................... 113 114 Steigung -1 S Steigung -1 S Übertragungskennlinie des CMOS-Gatters Für zunehmende Eingangsspannung Ue werden folgende Betriebszustände durchlaufen. 0 bis b Stromaufnahme des CMOS-Gatters für Ia = 0 : .T1 sperrt, T2 leitet im Triodenbereich. b bis c : .T1 leitet im Sättigungsbereich, T2 im Triodenbereich. c bis d : .T1 im Sättigungsbereich, T2 im Sättigungsbereich. c bis e : .T1 im Triodenbereich, T2 im Sättigungsbereich. e bis f : .T1 im Triodenbereich, T2 ist gesperrt. 115 Störabstand: SL = 1,7V 116 5.3.2. Statische CMOS - Schaltungstechnik SH = 2,5V Implementierung von Logikfunktionen UB sehr großer Störabstand gute Störsicherheit Anmerkung: Übertragungskennlinie ist nicht symmetrisch S S G G trotz gleichem W/L, da für Elektronenbeweglichkeit µn und P1 Löcherbeweglichkeit µp gilt : µn ~3 · µp D P2 l/l/S Parallelschaltung l/S/S D Aus den Kennlinien: A a) Für Ue < | Utn | und Ue > US - | Utp | : D L/H/H Es fließt kein Strom solange Ia = 0. (nach Aufladung von C sperrt N_2) S/l/l E2 Ue2 Ua im statischen Zustand Ia | 0, da im statischen Zustand für alle N2 G C ist eine parasitäre Kapazität S ausgeschlossenen Gatter gilt: IG | 0 im .statischen Zustand. nimmt eine CMOS-Schaltung einen .verschwindend gering. Strom auf Verlustleistung Substrat des nKanalstransistor s immer auf niedrigstem Potential C D L/L/H E1 Ue1 G & S/l/S N1 S (In realen Schaltungen PV | pW ... nW / Gatter) Reihenschaltung Schaltbild NAND NAND - Gatter b) Während des Umschaltvorgangs: - Beide Transistoren sind .gleichzeitig leitend, wodurch .Querströme. entstehen. - Die parasitären Eingangskapazitäten der nachfolgenden Gatter müssen umgeladen werden, auch dies erzeugt Ströme. a + b Die Verlustleistung einer CMOS-Schaltung ist .proportional. .zur Frequenz. der Schaltvorgänge. E1 E2 N1 N2 P1 P2 S S l l S L L L H S l l H L l S S l H H l S S l l: leitend s: sperrend positive Logik: NAND-Funktion negative Logik: NOR-Funktion A Allgemeines Funktionsprinzip eines statischen CMOS - Gatters UB 117 118 Beispiel: A = E1 E2 NOR Parallelschaltung ... fn = .................... = ..................................................................... E1 fp = E1 E2 p-Block Reihenschaltung = .................................................................... UB ... E2 p-Kanal Transistor Substrat immer auf höchstem Potential P1 A E1 En ... Reihenschaltung p-Block n-Block P2 E2 Prinzip der statischen CMOS - Logik A 1) Zu jedem Zustand ist entweder n- oder der p-Block gesperrt 2) Es besteht immer eine leitende Verbindung von A zu einem festen Potential (0 oder UB) N1 n-Block Parallelschaltung N2 Inverter Konstruktionsregel: t1 Die zu realisierende Funktion sei "ODER" A = f (E1, ..., En) Schaltbild NOR NOR - Gatter Funktion des n-Blocks Komplexe Funktion: Z = A B C (D E) fn = ................................................. fn = ......................................... Funktion des p-Blocks (p-Transistoren invertiert gestreut) Reihe Parallel fp = ................................................. Reihe Dabei: UND ! .Reihen. schaltung ODER ! .Parallel. schaltung Parallel 119 fp = A B C (D E) = .................................................................. = = ........................ .......................... 120 Es können nur Funktionen mit Negation erstellt werden Beispiel: C = A B = ................................................ = ............................. Reihe Parallel NOR Parallel Inverter Reihe UB UB E P1 E1 C D A UB P2 E2 UB UB P3 A B N1 N2 Z C A B Abschätzung des dynamischen Verhaltens: D Komplexes Gatter UB E 1) Reihenschaltung von m leitenden Transistoren: leitet schlechter als Wc Verhalten wie Transistor mit Einzeltransistor Lc 2) Parallelschaltung von m leitenden Transistoren: Wc W m leitet besser als Verhalten wie Transistor mit Einzeltransistor Lc L N3 121 122 Einige spezielle Funktionen. • Tri - State Im Gegensatz zu einer normalen Leitung können an einem .mehrere Ausgänge. angeschlossen werden, von denen sich aber nur je einer nicht im Z-Zustand befinden darf. UB L/H Busse sind sehr kostengünstige und leicht erweiterbare Verbindungsfunktionen. l/s Inverter Precharge A E Busse können auch mit einer .Precharge-Logik. realisiert werden. Dabei wird die .Kapazität C. der Leitungen und der angeschlossenen Empfänger genutzt. EN H/L H/L l/s E En 1 A PrechargeTakt EN E A H L H H L C E2 l/l/S Z: ."hochohmiger" Zustand X L/H/H ... X: “Don‘t care“ (0 oder 1) L Busleitung H/H/L E1 n-Block H s/l Takt Z l/s Benötigt für Busse: L X En L X En 1 Z Takt und Precharge- Takt werden .abwechselnd betrieben. H H Z (s. Kapitel Flip - Flops). Der Precharge - Takt lädt den Bus auf H - Pegel 1 auf, während das Taktsignal für eine .bedingte Entladung. En L sorgt, falls eine der E - Leitungen auf H - Pegel liegt. 1 Das Bussignal ist damit nur phasenweise gültig. Bus - Einsatz im Speicher - Einsatz für "getaktete" Logik Es darf maximal ein Ausgang aktiv sein, d.h. 123 124 Transmission Gate Schaltfunktion mit 2 Transistoren: Precharge Takt s/l G S Bus Ue D UB S Ust Ue (W/L = 1) D T2 G Ust L/H H/L T1 Ua Ue Ua (W/L = 1) 0V Ust Schaltsymbole physikalischer Aufbau Transmission Gate a) Ust = UB| (Ust = H) Ue = 0 V Ua Ia s/l bedingte Entladung .. T Ue = 5V (H-Regel) Stromfluß durch das Transmission Gate für Ue = 0 und Ue = UB T1 : Trägt Hauptstromfluß für ..................................................... T2 : Liefert größten Betrag für ..................................................... c) Ust = 0 (Ust = L) : .Transmission Gate sperrt. 125 126 Einsatz des Transmission Gates : 6. Übertragung digitaler Signale auf Leitungen - Vereinfachung logischer Funktionen Bisher haben wir nur Netzwerke mit .konzentrierten. Bauelementen betrachtet. Dies ist nur zulässig, wenn die Effekte der Leitungen, die die UB H/L Bauelemente verbinden entweder .vernachlässigbarsind. oder .. T A durch Ersatzschaltbilder mit .konzentrierten Bauelem entm odelliert. .w erden. können. Im folgenden werden wir uns mit Leitungseffekten beschäftigen. Die .. B T Betrachtung wird auf .verlustarm e Leitungen. beschränkt. H/L L/H S 6.1 Impulsausbreitung auf Leitungen Multiplexer Als Modell nehmen wir zunächst vereinfachend eine Leitung mit einem - Dynamische Logik: Ausnutzen der parasitären Gatekapazität zur Sender und einem Empfänger und homogener physikalischer Speicherung elektrischer Ladung und damit von Information. Charakteristik . -hom ogene Leitung. UB Ust H/L H/L .. Ue T Leitung Ua Sender Empfänger Dynamisches Gate 127 128 In Technische Informatik I: Kurze Wiederholung aus Technischer Informatik I: Lösung für .einzelne,sinusförm ige W elle. Zur Betrachtung der Leitungseigenschaften zerlegen wir die Leitung Mit Vereinfachung ................................. und ............................... in .infinitesim alkleine. Stücke der Länge dx mit (verlustfreie Leitung) gilt dann: folgendem Ersatzschaltbild: I L' Wellenwiderstand: įI I dx įx R' U G' C' U įU dx įx („characteristic impedance“) Ausbreitungsgeschwindigkeit: ..................................................... Charakteristik der verlustfreien Leitung Bei der verlustfreien Leitung sind Wellenwiderstand und Ausbreitungsgeschwindigkeit .frequenzunabhängig. Der Wellenwiderstand ist .reellw ertig. dx Impulse können in .Fourierreihen. zerlegt werden. wobei L' : Induktivitätsbelag ª H º «¬ m »¼ C' : Kapazitätsbelag ª F º «¬ m »¼ G' : Leitwertsbelag ª S º «¬ m ¼» R' : Widerstandsbelag ª: º «¬ m »¼ Man kann .einen Im puls. also als eine .Ü berlagerung von. .W ellen. verschiedener Frequenzen betrachten. Auf einer verlustfreien Leitung breiten sich alle diese sinusförmigen Wellen mit gleicher Geschwindigkeit v aus und sind dem gleichen Wellenwiderstand unterworfen. Daher: damit gilt: Spannungsabfall über R' und L' : įU įx Strom durch G' und C' : įI įx R' I L' G' U C' įU įt įI įt Auf einer verlustfreien Leitung werden Impulsformen (1) (2) …unverzerrt.übertragen. Auf einer realen Leitung ist dies nicht der Fall; Amplitude und Phasengang sind frequenzabhängig. Leitungen, wie sie üblicherweise in Rechenanlagen verwendet werden, Dies ist ein allgemeiner Ansatz für Wellenausbreitungen aller Art in der Physik. können jedoch .näherungsw eise alsverlustfrei. betrachtet werden. 129 130 Anmerkung: Die Laufzeit einer Impulsflanke vom Anfang einer Leitung der Länge l bis zu ihrem Ende wird als .Leitungslaufzeit. bezeichnet. Die Fourierzerlegung gilt nur für periodische Signale. Wir können aber jede Impulsplanke als Ausschnitt eines periodischen Signals mit so In üblichen Aufbautechniken gilt eine Ausbreitungsgeschwindigkeit von ...................................................... großer Periode betrachten, dass weitere Zustandsänderungen nicht mehr in den Betrachtungszeitraum fallen. Wie sinusförmige Signale werden auch Impulse an nicht Veranschaulicht : angepassten Leitungsenden reflektiert. U 6.2 Reflexion und Brechung von Impulsen Impuls Aus Technische Informatik I wissen wir, dass eine sinusförmige Welle an .nichtangepassten Enden. einer Leitung .reflektiert. wird. t Dies können wir wieder auf Impulse übertragen (Fourierzerlegung) Zur Untersuchung von Reflexionen betrachten wir jede Impulsflanke 8 getrennt. t t 8 0 Getrennte Betrachtung der Flanken eines Impulses 131 Impulsübertragung und Einschwingvorgang 132 Innenwiederstand des Empfängers Innenwiderstand des Senders Zi Ih Ir }U }U rücklaufende Flanke hinlaufende h Flanke l (Länge der Leitung: l) U0 Ie U0 Ua Z0,T Ue Ze x 0 Leitungsanfang .Leitung m itW ellenw iderstand. .Sender. . und LeitungslaufzeitT. .Em pfänger. Ersatzschaltbild für Impulsausbreitung Eine Impulsflanke der Spannung U0 am Senderausgang ergibt einen Spannungssprung der Größe Uh am Ausgang der Leitung: Uh = U0 · ................... (Spannungsteiler) Nach der Laufzeit T wird die Welle am Leitungsende reflektiert, und zwar mit der Amplitude Ur (siehe TI I). Z Z e 0 Ur (T) = Uh (0) · Z Z e 0 Reflexionsfaktor r und Leitungsende Prinzip der Überlagerung von hin- und rücklaufender Impulsflanke bei Impulsreflexion Erreicht die rücklaufende Impulsflanke den Leitungsanfang, wird sie .erneutreflektiert: U h (2T) U r (T) Zi Z0 Zi Z0 Man unterscheidet: ra: Reflexionsfaktor am Leitungsanfang re: Reflexionsfaktor am Leitungsende Die Spannung U auf der Leitung ergibt sich aus der .Sum m e. aller hin- und rücklaufenden Wellen. Lineares System Überlagerung ergibt sich aus .Sum m e allerEinzelw ellen. (homogene Leitung). Ir = .......... r Insbesondere: U e (T) U h (0) U r (T) 133 Z0 U0 Zi Z 0 U h (0) 134 Ue(T) = Uh (0) + Ur(T) = Leitung mit Anpassung Zur Vereinfachung nehmen wir zunächst an: Zi = Z0, d.h. ra = 0, also keine Reflexion am Leitungsanfang (angepasster Leitungsanfang). die Leitung befindet sich nach t = .2T. im .eingeschw ungenem . .Zustand. Nachdem die rücklaufende Welle den angepassten Anfang der Leitung erreicht hat, ergibt sich auf der ganzen Leitung die Spannung 0V. Der spannungsteilende Effekt des Wellenwiderstandes, der zu U0 führte, ist also, wie im Fall 1, verschwunden. Uh 2 ......... Beispiele re = .1. 8 Allgemein gilt: der Effekt der Leitung ..verschw indetim . Ze 1) offenes Ende : Ur = ... .eingeschw ungenen Zustand, denn im Ir = ... Leitungsmodell hatten wir R' = 0 und G' o f angenommen. Die Welle wird .m itgleicherA m plitude. reflektiert. U e (T) U h (0) U r (T) ................................................. Wenn die rücklaufende Welle den Eingang erreicht hat, gilt ebenfalls: U h (0) U r (T) U a (T) 2) Kurzschluß am Ende re = .-1. U0 Ze = 0: Ur = ... Ir = ... Die Welle wird mit negativer Amplitude gleichen Betrags reflektiert Uh U0 2 0 U 0 2 }U }U h r hinlaufende Flanke rücklaufende Flanke 1 135 x Allgemeiner Fall Zi # Z0 136 Impulsfahrplan: Beispiel Der Ausgang eines Gatters mit Zi = 150 ȍ sei über eine homogene Leitung mit Z0 = 100 ȍ, T = 1 ns mit dem Eingang eines anderen Gatters mit Ze = 300 ȍ verbunden. 0,02V Das Gatter schalte in t = 0 von U0(0) = 0V auf U0(0+) = 5 V. G1 G2 Z0 = 100 ȍ , T = 1 ns =0,1V+0,02V= 0,12V 0,1V =0,2V+0,1V=0,3V 0,2V Zi = 150 ȍ U0=5V Ua Z0 = 100 ȍ, T = 1 ns Ze = 300 ȍ =1V+0,2V=1,2V 2V*0,5 = 1V Ue 2V =2V+1V=3V Ersatzschaltbild der Leitung Reflexionsfaktoren: Im Beispiel: Gatterausgang G1: U a (0) ra = …………………………………………… Eingang des folgenden Gatters G2: U e (T) …3V ……………………………………………… U a (2T) U a (0) U r (T) U h (2T) U a (0) ǻU a 2T .......... ...... U e (3T) U e (T) U h (2T) U r (3T) 3,3V U e (T) ǻU e (3T) .......... ..... Die hin- und herlaufende Wellenfront kann mit einem U a (4T) U a (2T) ǻU a (4T) .Im pulsdiagram m veranschaulicht werden. usw. re = …………………………………………… Die rücklaufende Welle wird am Gatterausgang von G1 .erneutreflektiert. U0 Z0 Z 0 Zi .................................................... 3,32V 3V .......... .......... .......... .......... ....... 137 Graphisch 138 Allgemein: U a (0) U a (0) re U a (0)r e ra U a (2nT) ...... U a (0)re n ra n 1 U a (0)re n ra n n U a (0) U a (0) ¦ (rae v ra v1 re v ra v ) v 1 n U a (0)(1 (1 ra ) ¦ re v ra v 1 ) Spannung am treibenden Gatter (abgelesen aus Impulsfahrplan) v 1 Spannung am empfangenen Gatter (abgelesen aus Impulsfahrplan) Ue ((2n 1)T) Ua (0) Ua (0)re . . . Ua (0)re n ra n Ua (0)re n1ra n n U a (0)(1 re ) ¦ re v ra v v 0 Anmerkung: Es wurden nur konstante ohmsche Abschlußwiderstände betrachtet. In der Realität oft: - .nichtlineare Abschlußwiderstände: Beispiel Transistor Eingangskennlinie - .Energiespeicher. (Kapazitäten, Induktivitäten): Beispiel FET Lösung: graphisch (Bergeron - Verfahren) oder Rechnersimulation. 140 139 Brechung Weitere Beispiele: Beispiel aus der Praxis: Verzweigte Leitungen auf Platinen: Koaxialkabelverbindung zwischen Platinen .Stoßstelle. Z0 Z0 Z0 S1 S2 Z0 Z0 .Stoßstelle. Z0 An den Stoßstellen tritt Reflexion .und Brechnung. auf: S3 Stoßstelle U U h + Ur Parallelschaltung von 2 Wellenwiderständen Z0: S1 0 Z2 Z1 x Amplitude der gebrochenen Welle = Spannung an der Stoßstelle Ug = Uh + Ur = ...................................... d.h. Ug = Z0/2 Z0 gebrochene Welle ST rST Z0 Z0 2 3 Z0 2 1 3 b Z0 3 Z0 2 2 3 Stoßstellen ebenso durch - Durchkontaktierung auf Platinen (==> Streifenleitung) b: Brechnungsfaktor Amplitude der gebrochenen Welle - Änderung des Wellenwiderstandes durch benachbarte Signalleitungen (nicht diese VL). S2, S3 141 6.3 Störungen 142 Gegenmaßnahmen: Klassifikation: - Stützkondensatoren zwischen den Versorgungsleitungen - interne Störungen: .Gegenseitige Beeinflussung. von Schaltvorgängen - Auslegung der Versorgungsleitungen (sternförmig geführte - externe Störungen: Störungen auf dem Versorgungsnetz, Masseverbindungen,getrennte Masseleitung für Störer), durch Elektromotoren, statische Aufladung. Versorgungsebenen bei Mehrlagentechnik. - symmetrische Signalübertragung: Im folgenden werden wieder konzentrierte Bauelemente angenommen + VCC + VCC Störungseffekte (grob): + _ & - galvanische Kopplung LVDS: SCSI, Serial ATA, PCI-Express - kapazitive und induktive Kopplung Hier wird die Gleichtaktunterdrückung eines Differenzverstärkers gebraucht Galvanische Kopplung: Kapazitive und induktive Kopplung: VCC G1 G2 USp Ua ˜ Ue R L G3 ZK i iS Masse US G3 sei ein Gatter, das mit hohen Strömen iS schaltet (Beispiel: Abhängig vom geometrischen Aufbau eines Systems werden Signale über Mikroprozessor, Bustreiber). Über die Induktivität L und den ohmschen elektrische und und magnetische Felder durch Schaltvorgänge auf Widerstand R der Masseleitung wird eine Störspannung US in die benachbarten Leitungen (oder externe Störfelder) beeinflußt. Übertragung G1 o G2 eingekoppelt. 143 Beispiele: 144 - Verschlagen von Leitungen Beispiel: Störungen kompensieren sich induktive und kapazitive Kopplung kapazitive Kopplung Gegenmaßnahmen: - geeignete Leitungsführung - starke kapazitive Kopplung mit Masseleitung, Einfügen von Masseebenen o Änderung des Feldlinienverlaufs und Verringerung des Wellenwiderstands: ZK kapazitive Kopplung mit Nachbarleitung kapazitive Kopplung mit „Masse“ Spannungsteiler Z0 ZK Spannungsteiler Störunterdrückung durch kapazitive Kopplung mit „Masse“ Problem: geringerer Wellenwiderstand Z 0 erfordert höhere Treiberleistung 145 7. Speicherfunktionen: Flip-Flops und ihr Einsatz 146 Das D-Latch .speichert. die Daten solange der Takteingang auf L-Pegel In digitalen Schaltwerken werden Funktionen zur Speicherung von liegt. Liegt der Takteingang auf H-Pegel, folgt der Q-Ausgang dem Zuständen benötigt (vgl. Variablen). Zu ihrer Steuerung werden Eingang, das Latch ist .transparent. .Taktsignale. verwendet. Die elementaren Speichergatter werden als .Flip-Flops. bezeichnet. Ebenso gibt es negativ taktpegelgesteuerte D-Latches. Schaltbild: Man unterscheidet: 1D Q C1 QN - .taktpegelgesteuerte. Flip-Flops - .taktflankengesteuerte. Flip-Flops 7.1 D - Latch: .Taktpegelgesteuertes Flip-Flop. G3 G1 L/H (H / L) / H / L & H/L/H R C & QN Takt dynamisches Verhalten des D-Latches als .Zeitdiagramm. dargestellt: Abhängigkeit positive Logik 1D D Q H L H/L S & D & C1 QN Q taktpegelgesteuert H/H/L Daten Takt (L / H) / L / H /L/H G2 G4 b) Schaltsymbol a) Schaltplan C D L X Q-1 QN-1 Q QN H L L H H H H L X: Don't care: L oder H c) Funktionstabelle t Langsame Schaltung (max. 3 Gatterlaufzeiten für Signalwechsel). Alternativ eingesetzt wird in der Regel das .Earle - Latch : Takt H/L & l: leitend s: sperrend L H L/H & L/H H/L & L/H Takt 148 Realisierung von D-Latches mit Transmission Gates Realisierung in .statischer. CMOS - Technik H/L/H D L/H/ 147 Q D H/L l/s TG L & H/L L/H H/L Q s/l H L/H TG H/ o erfordert komplementäres Taktsignal Wenn Taktsignale und Daten (D) nahezu gleichzeitig eintreffen, kann Kosten: 2x2 Tr = 4 Tr TG 2x2 Tr = 4 Tr Inv. -----8 Tr L/L/H Takt Takt H/H/L es Konstellationen geben, in denen das Flip-Flop im Kippvorgang unterbrochen wird. Dabei kann es in die Nähe des .metastabilen. Realisierung in .dynamischer. CMOS - Technik .Zustands. kommen (siehe VL Digitale Schaltungen) und für einen Invertierendes D-Latch: UB undefinierten Zeitraum undefinierte Ausgangspegel erzeugen. Wir definieren daher für D-Latch: ......Setup-Zeit..................: Spätester Zeitpunkt für Änderungen von D L/H L/H vor H o L-Übergang des Takts. D TG ......Hold-Zeit...................: Mindestzeit nach H o L-Übergang des Takts, in dem sich D nicht ändern darf. Takt Takt L/L/H H/H/L o nur 4 Transistoren ! verboten H/L Q 149 Einsatz des D-Latches:.Einphasige Taktung. Zusammenfassung von Flip-Flop zu Registern: Q1 150 Def.: Schaltnetz und Schaltwerk • .Schaltnetz: Schaltung zur Implementierung einer boolschen Funktion .ohne Zustandsspeicher. • .Schaltwerk: Schaltnetz .mit zusätzlichem Zustandsspeicher. (Flip-Flops) D2 Def.: Entscheidungs- und Übergangsintervall: Übergang gesperrt -> transparent Übergang transparent -> gesperrt Schaltnetz D2 D1 Register E Zyklisch, periodisch Wir definieren: Ü • tpdDmin d tpdDi d tpdDmax: Grenzen für Laufzeit aller D-Latches (DFF) späteste Änderung des Eingangs Um die Funktionsfähigkeiten sicherzustellen, muß gelten: 1) ij: • tpdSmin d tpdSi d t pdSmax: Grenzen für Laufzeit aller Signalwege durch das Schaltnetz S. ......... t - tsi + tpdDmax + tpdSimax + tsj - tskewij (2) für tsi = tsj ij: .Taktverschiebung (Skew). durch Laufzeiten im Taktnetz. • tskewmin d tskewijmin d tskewij d tskewijmax d tskewmax tskewij: Taktverschiebung zwischen Register i und j tskewmin,max: min bzw. max. Taktverschiebung im Schaltwerk transitiv: tskewij = tskewik + tskewkj tcyc t.................................................................................................................................. Mit dieser Bedingung wird sichergestellt, dass alle Signale rechtzeitig das Register erreichen, ohne ts zu verletzen (Berührung „rechtsseitig“) • Taktzykluszeit: tcyc = tCH + tCL: (3) (2) 151 2) ij: tpdDmax d tCH d tpdDmin + tpdSimin - th - tskewijmax 152 Rechts- und linksseitige Berührung im Zeitdiagramm. Die Bedingung stellt sich sicher, dass • das Latch ausreichend lang geöffnet ist, damit das D-Signal korrekt an den Ausgang Q übernommen wird. (3) • es ausreichend kurz geöffnet ist damit eine Signaländerung nicht in einem Takt schon das.nachfolgende Register beeinflussen kann. .................................. (Berührung „linksseitig“). Umformen: ij: 0 d tCH - tpdDmax d tpdSimin - th - tskewijmax + tpdDmin - tpdDmax d0 d ................................................................................................................ ü Da häufig tpdSimin sehr klein ist, ist diese Bedingung oft nicht zu erfüllen. Skew Lösungsansätze: • .künstliche Zeitglieder. zur Erhöhung von tpdSimin • .negative Holdzeiten..................................... z.B. Leitungsmeander nicht im 7.3 Einsatz des D-Latches : .M ehrphasige Taktung. • Taktung .entgegen der Datenflussrichtung, sofern es eine bevorzugte Richtung gibt o t skewijmax 0 D1 D Q S D2 D Q C Ɏ1 Ɏ2 tskew12 Taktgenerator D-Latch 2 D-Latch 1 D Q C C , aber im S1 D Q C D-Latch 3 S2 D Q C 153 154 7.4 Taktflankengesteuerte Flip-Flops Verbleibendes Problem: zwei Taktsignale mit u. U. unterschiedlichen Leitungslaufzeiten .Verdrahtungskosten, Entwurfsrisiko. Beim taktflankengesteuertem Flip-Flop werde Master- und Slave - Takt aus .einem Taktsignal abgeleitet, und zwar so, dass • kein transparenter Zustand auftritt • das Eingangssignal mit der steigenden oder fallenden Taktflanke an den Ausgang übernommen wird. Bei zweiphasiger Taktung kann durch die Wahl von Ɏ1 und Ɏ2 stets sichergestellt werden, dass die Schaltung funktionsfähig ist. Aber: die Schaltung muss so aufgebaut werden, dass stets ein Ɏ1 - D Q D D Q D Q Q getaktetes auf ein Ɏ2 - getaktetes Register folgt, ohne dass die Schaltung dabei ineffizient (Kosten, Geschwindigkeit) wird. C C C Vereinfachung mit .Master-Slave-Flip-Flop. Master - Slave - Flip - Flop für zweiphasige Taktung Master-Slave-Flip-Flop D D Q D Q C Entscheidungs- und Übergangsintervall: Q C MasterTakt SlaveTakt 155 156 Während 1) immer erfüllbar ist, kann bei großen Taktnetzen 2) nicht 7.5 Einsatz taktflankengesteuerter Flip-Flops erreichbar sein. Lösungsansatz: • Taktung auf unterschiedlichen Flanken. Effekt wie bei taktgesteuerten FFs mit 2 Taktsignalen. tCH D Q Um die Funktionsfähigkeiten der Taktung sicherzustellen, muss gelten: 1) Der Taktzyklus muss ausreichend groß sein, damit die Ausgangssignale tCL D Q S1 D Q C C C CLK S2 der Schaltnetzes korrekt in das folgende Flip-Flop übernommen werden, ohne ts zu verletzen (vgl. taktpegelgesteuertes FF) ij: tcyc t .................................................................................................................... tskew 2) Die Taktverschiebung muss ausreichend klein sein, damit ein Signal nicht während einer Taktperiode zwei aufeinanderfolgende Flip-Flops • Master - Slave - Anordnung mit 2 Taktflanken. beeinflussen kann. ij: tskewijmax d .................................................................. J J K K Takt Q D Q Q 157 158 • minimale .Zykluszeit: .K ürzestes zulässiges Zeitintervallzwischen aufeinanderfolgenden Schreib- oder Lesezyklen 8. Zusammengesetzte und reguläre Schaltungsstrukturen 8.1. Übersicht Neben Gattern und Flip-Flops werden regelm äßig aufgebaute,. kom plexe Schaltungsstrukturen. verwendet, mit denen umfangreichere Funktionen realisiert werden können. Bestandteile eines Speichers: Dazu gehören Speicher, PLAs und FPGAs. Vorteile: • .V erringerung derA nzahlICs. bei Logikentwurf • oftmals .bessereFlächeneffizienz. bei Integration bestimmter Funktionen • Vereinfachung des Entwurfs und kürzere Entwicklungszeit Probleme: • .Zeitverhalten, • Flächeneffizienz bei großen Schaltwerken 8.2. .Speicher. Wichtigste Gruppe der regulären Schaltungsstrukturen. Hauptkomponenten: • .Speicherm atrix m itSpeicherzellen. • .Zeilen-und Spaltendekoder. • .W ortpufferm itEin-und A usgabe. • .Schreib-und Lesesteuerung. • .Speicherm atrix. Die .Speicherm atrix. besteht aus einem 2-dimensionalen Feld von 2m Zeilen und 2n Spalten. Die Zeilen entsprechen .Speicherw orten. und die Spalten den .Bitpositionen eines Speicherw ortes. . Ein Speicher kann somit insgesamt 2m x 2n bit speichern. Wichtigste Kenndaten: • maximale .Zugriffszeit: maximale Verzögerungszeit vom Anlegen einer .A dresse. bis zur Gültigkeit der ausgelesenen .D aten . Jeder Spalte ist eine .Bitleitung. zugeordnet. Jeder Zeile ist eine .W ortleitung. zugeordnet. Jedem Kreuzungspunkt ist eine 1bit .Speicherzelle. zugeordnet. Die Speicherzelle hat einen Tri-State-Ausgang und jede Bitleitung bildet einen Bus. • .D ecoder. Der Dekoder wird mit einem Adresswort der Länge .m +n-ld x . bit angesteuert. Dabei ist ld x die Breite des Ein- /Ausgabeworts des Speichers. Davon adressieren m Bit die Zeile (das Wort o Wortadresse) und n-ld x Bit wählen einen Teil der Spalten aus (Spaltenadresse). Entsprechend zerfällt der Dekoder in einen .Zeilen-. und einen .Spaltendekoder. Der .Zeilendekoderadressiert. für jede Belegung des Adressworts (d.h. jede Adresse) immer genau eine W ortleitung. Je nach Auslegung entspricht eine Aktivierung dem Anlegen eines H- bzw. eines L-Pegels, während der jeweils andere dann der Deaktivierung entspricht. Beispiel für Zeilendekoder: m = 2 a1 a0 a1 a0 a1a0 a1 a0 a1a0 a1 a0 Wort11 159 160 a1 a0 Wort00 Wort01 Wort10 Wort11 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 1 1 0 0 0 1 Wenn eine Wortleitung aktiviert ist, verlassen alle angeschlossenen Speicherzellen den hochohmigen Zustand. Alle anderen Speicherzellen bleiben im hochohmigen Zustand. .Bitleitungen. tragen den .Inhaltdes. .Speicherw orts, das deraktivierten Speicherzeile. .entspricht. Funktion des Speichers: a) .W ortauslesen: 1) Die Signale auf den Bitleitungen werden in ein Register aus Flip-Flops (durch Taktung) übernommen. Dieses Register ist der .W ortpuffer. 2) Aus dem Wortpuffer wird mit den verbleibenden n - ld x bit des Adressworts ein .Teilw ort. der Länge .X selektiert. und ausgegeben. x Wort10 Wort01 Wort00 Wortpuffer x x3 S x2 x1 Multiplexer x Spaltendekoder A x0 161 .M ultiplexer: Gibt ein Eingangswort an den Ausgang weiter, abhängig von einem Steuerwort. 162 8.2.2 Statische Schreib- /Lesespeicher Ein Speicher wird als .statisch. bezeichnet, wenn die einzelnen Speicherzellen in .statischerSchaltungs-. .technik. realisiert w erden. Im Beispiel: G A .......................................................... Ein .Schreib-/Lesespeicher. ist ein Speicher, bei dem während des Betriebs Speicherworte gelesen und geschrieben werden können (siehe 8.2.1). “ o “ Vektor binärer Variablen b) .W ortschreiben: 1) .W ortleitung aktivieren: Wie lesen 2) .Ü berschreiben des von der Spaltenadresse adressierten Teilworts durch das zu schreibende Wort der Länge x. Dazu sind Treiber an den Bitleitungen notwendig, die einen .niedrigeren A usgangsw iderstand. .aufw eisen alsdieSpeicherzellen. Wortleitung Speicherzelle Bitleitungstreiber En Bitleitungstreiber Inverter Inverter Flip-Flop Statische CMOS-Speicherzelle Leseverstärker Funktion: .T1,T2,T3. und .T4. bilden ein .Flip-Flop. aus .gegengekoppelten Invertern, die ihren einmal eingenommenen Zustand stabil halten. Wortpuffer 3) Einschreiben der Werte auf den Bitleitungen in die aktivierten Speicherzellen Die Aktivierung erfolgt durch H-Pegel auf der Wortleitung xi, der die Transistoren T5 und T6 in den leitenden Zustand versetzt (vereinfachte Transmission-Gates), sonst sperren die Transistoren. 163 Bei leitenden Transistoren T5 und T6 werden die komplementären Pegel des Flip-Flops auf die Bitleitungen yj und y j übertragen. Die Bitleitungen sind hier doppelt ausgelegt und ihre .Spannungs-. .differenz. wird in einem Differenzverstärker (.Lese-. .verstärker) ausgewertet. Diese differentielle Signalübertragung verringert den Einfluss von Störungen (Kap. 6) und erlaubtkürzereZugriffszeiten. Bei Einsatz von Precharge mit ........................... erlaubt sie zudem eine .schnelleA usw ertung. des Flip-Flop-Zustands, denn die Bitleitungen haben eine große kapazitive Last durch die .................. .parasitären D rain-G ate-K apazitäten C G D . der angeschlossenen Transistoren T5 und T6 der nicht aktivierten anderen Speicherzellen (s. unten). 164 Am statischen RAM sind bereits die typischen Probleme der Speicherelemente erkennbar: • Um eine hohe Flächeneffizienz zu erzielen, müssen die .Speicher-. .m atrizen m öglichstgroß und dieSpeicher-. .zellen m öglichstklein sein. • Neuere Speicher bestehen aus mehr als 512 Zeilen und Spalten. Beim Auslesen werden die Speicherzellen daher mit .großen parasitären. .K apaiztäten belastet, bestehend aus .den parasitären C G D 's. und .Sperrschichtkapazität. bzw. .Leitungskapazität. aller angeschlossenen Transistoren (T5, T6). Da die Speicherzellen möglichst klein dimensioniert sind, weisen Ihre Transistoren einen .hohen A usgangsw iderstand. auf .hohe Zugriffszeiten. T5 CGD Beim .Lesen. bleiben die .Treiber. an den Bitleitungen im .hochohm igen Zustand . Beim .Schreiben. werden die .Bitleitungstreiberaktiviert. (H- oder L-Pegel). Da sie einen .niedrigeren A usgangsw iderstand. als die Speicherzelle besitzen, bestimmen sie den Pegel auf den Bitleitungen. Über .T5 und T6. werden damit die Pegel an den Invertern T1 - T2 und T3 - T4 so verändert, daß .derFlip-Flop um schaltet, falls die Pegel auf den Bitleitungen invers zu den Flip-Flop-Pegeln sind. 165 166 Der Aufbau ist symmetrisch. Wir können in erster Näherung beide Bitleitungen getrennt betrachten. t Einsatz von .Precharge Vor Auslesen der Leitungen wird mit dem Treiber der Bitleitungen .............................................................. erzeugt. Aufgrund des kleinen Innenwiderstands geschieht dies sehr schnell. U yj ( t ) (U H U yj (0))(1 e Allgemein: Ra C L ) U yj (0) Ladekurve des RC-Elements Wortleitung bei Annahme, dass Uyj auf UH wechselt (Wechsel auf UL analog, da Aufbau symmetrisch) UXi t= Umformen: UB UYj Es sei Uyjs die Spannung, bei der der Leseverstärker schaltet, dann UB/2 t sei dann t_read UB UYj tread = UB/2 Symmetrie, daher: Uyjs = ........................................................ wo Ud Differenzspannung, ab der der Leseverstärker schaltet. UB UBit j Zahlenbeispiel: UB/2 Ausgangsverstärker UB = UH = 3V Signaldifferenz Mit Precharge: Ud = 50mV Ohne Precharge: treado = erkannt Rechenbeispiel: UB = UH = 3V UL = 0V treadp = Durch den Einsatz von Precharge ist die Lesezeit auf UL = 0V 1/43 Ud = 50 mV Differenzspannung, ab der der Leseverstärker schaltet. verkürzt worden! Ra: Ausgangswiderstand der Speicherzelle Beispieldaten realer statischer Speicher: CL: Lastkapazität an der Bitleitung Kapazität: .16 M b................. Zugriffszeit: ta = .0,2 ...20ns. tcyc = .0,2 ...20ns. x = .1 ...32................. 167 8.2.3 Dynamische Schreib- / Lesespeicher ............... 168 Um ein möglichst großes Lesesignal zu erreichen, wird mit großem Aufwand eine möglichst ......................................................................... erzeugt. Eine Standardtechnik ist das Ätzen einer tief in das Substrat reichenden ............................................................ Dynamische CMOS-Speicherzelle Im ................................................... liegt die Wortleitung auf ..................., so daß der Transistor .................................. und die ................................... ............................................ wird. Beim ........................ wird die Bitleitung, wie beim statischen Speicher, vom Treiber auf den zu schreibenden Wert gebracht und bei aktivierter Wortleitung (H-Pegel) die .................................................... ............................................................... . Beim ....................... befindet sich der Treiber im ...................................... ........................... und T leitet. Die .............................................................. ................................................................................... . Also: Uyj(t) = .......................................................................... Da ................... , verändert sich Uyj(t) nur geringfügig. Der ...................................... muß daher eine............................................... ........................................ besitzen. Weil zudem kein Differenzsignal zur Verfügung steht, ist die Schaltung störanfälliger. Eine .............................. .............................. , die parallel zur Bitleitung geführt wird, soll die Störeinflüsse dämpfen (siehe Kap. 6). Dynamische Zelle mit Trench-Kapazität Der Lesevorgang ist ........................................., d.h. der Wert muß nach dem Auslesen wieder in die Speicherzelle .............................................. werden. Aufgrund von ...................................... entlädt sich die Kapazität C und muß in regelmäßigen Abständen durch einen Lese- /Schreibzugriff (.............................) wieder ...................................... werden. Während des Refresh kann kein anderer Zugriff erfolgen. Insgesamt erfordert ein dynamischer Speicher eine viel komplexere Ablaufsteuerung als ein statischer. 169 Beispiel: 170 8.2.4. ........................................................ Im Normalbetrieb kann der Inhalt dieser Speicher nur gelesen werden. Man unterscheidet: • ............................................................................ Der Speicherinhalt wird bereits bei der Fertigung festgelegt und ist daher nicht änderbar. Vergleich von SRAM und DRAM • .......................................................................: Der Speicherinhalt kann ................................... vom Anwender – der dynamische Speicher erreicht eine .................................................... .............................................. (ca. 4x) als der statische. programmiert werden. Heute: .......................... • ......................................................................: – der dynamische Speicher ist ................................................................... und aufwendiger zu steuern. Der Speicherinhalt kann vom Anwender programmiert und durch .................................................... wieder gelöscht werden. Dieser Unterschied bildet die Basis einer Speicherhierarchie. • .....................................................................: DRAM: ....................................................................................... Der PROM-Speicher wird auf elektrischem Weg wertweise überschrieben. SRAM: ....................................................................................... • ...................................................: Daneben gibt es seit neuerem Speicher, die beide Typen auf einem Chip integrieren. Wie EEPROM, mit dem Unterschied, daß das Löschen blockweise geschieht. 171 172 EPROM ROM: Ein EPROM ist grundsätzlich wie ein ROM aufgebaut, aber mit einem .......................... statt einem MOS-Transistor. FAMOS-Transistor (Floating Gate Avalanche MOS) Funktion: Ein ............................................ wird .......................................................... ROM in MOS-Technik in SiO2 unter dem Gate eingebettet (Floating Gate). Wird eine aus- Im Beispiel des MOS-ROMs bildet jede Bitleitung eine ........................... reichend hohe Spannung UDS (z.B. UDS = 17 V) angelegt, entsteht eine ....................... Sobald ein Transistor leitet, liegt am Bit j ein L-Pegel an, hohe Feldstärke nahe dem Drainbereich (abgeschnürter Kanal), die zur sonst ein H-Pegel. Es kann nur der Transistor leiten, dessen Wortleitung Generierung ................................................................................................ aktiv ist (H-Pegel), alle anderen sperren. führt, die bei gleichzeitig hoher Spannung UGS teilweise .......................... Auf diese Weise wird ein Wort ausgelesen. ............................................................................ werden und dort zu einer Der Inhalt wird durch das Uth des Transistors bestimmt: negativen Ladung führen, die nach Abschaltung erhalten bleibt und zu U th !U H o......................................................................... einem .......................................................................................... führt. Die ..................................... erfolgt durch ............................................., U th U H o......................................................................... Die Thresholdspannung Uth wird durch ....................................................... ..................................................................................................................... .................................................................... die wieder zu beschleunigten Elektronen führt. 173 174 EEPROM, Flash EPROM Programmierbare Logikfunktionen Speicherzelle ähnlich wie FAMOS, aber mit einem sehr kleinen Abstand ................. zwischen Floating Gate und Kanal oder Drain, der ein ............................. Ein ........... (Programmable Logic Array) ist ähnlich einem Festwertspeicher ................................................................ (Welleneigenschaft) ermöglicht. aufgebaut, weist jedoch eine ............................................................................ Durch ................................................................... kann das Floating Gate anstelle des Adreßdekoders auf. wieder entladen werden. Dabei kann Uth aber auch negativ werden, so Ein PLA implementiert eine ........................................................................... daß ein ................................................................................ erforderlich ................................................................................................. (UND-ODER- wird, der die Zelle größer macht. Beim Flash-Speicher sind beide Verknüpfung). Transistoren in einer komplexen 3D-Struktur integriert. Beispiel einer EEPROM-Speicherzelle PLA mit NOR-Implementierung Zwei-Transistor-Zelle für EEPROM 175 Nach der DeMorgan´schen Regel läßt sich eine UND-ODERVerknüpfung durch eine NOR-NOR-Implementierung ersetzen, wenn man negative Logik verwendet. ............................................................................... Jeder .............................. des OR-Felds entspricht einer ............................ ........................................ Jeder Ausgang des AND-Felds entspricht einer UND-Verknüpfung. Die Ausgangsleitung, die gleichzeitig Eingänge des ODER-Felds sind, werden als .......................................................... bezeichnet. Durch gleiche UND-Verknüpfungen (konjunktive Terme) in verschiedenen Funktionen läßt sich ihre Zahl und damit der Aufwand 176 ......................................... Bei größeren Funktionen werden PLAs oft ............................................... ......................................., da eine zweistufige (UND-ODER)-Implementierung dann zu umfangreich ist. Moderne Bauteile integrieren daher .............................................. oder andere programmierbare reguläre Basisstrukturen (CLBs) auf einer integrierten Schaltung zusammen mit Flip-Flops und Speichern und verknüpfen diese mit .................................. .......................................................... Diese integrierten Schaltungen werden .................... (Logic Cell Arrays) oder ..................... (Field Programmable Gate Arrays) genannt. verringern. Da die DNF nicht eindeutig ist, ist dies ein Optimierungsproblem (TI III). Schaltmatrix eines FPGA Die Schaltmatrizen bestehen aus matrixförmigen Feldern von .................. ..................................................., in der Regel aus nur je einem Transistor (.............................................................................). 177 Beispiel für CLB (XILINX) Die CLBs wie auch die Schalter können mit normalen MOS-Transistoren oder mit einer der Festwertspeicher-Technologien (PROM, EPROM, EEPROM) realisiert sein. Bei Verwendung normaler Transistoren wird die Programmierung in ........................................................... gespeichert. Es ergibt sich damit die Möglichkeit, die Funktion .................................... ..............................................