Prüfungsklausur Rechnertechnologie / Techn. Informatik 2 / Techn

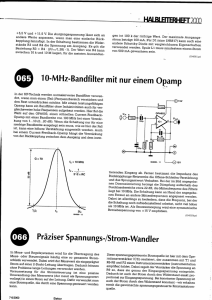

Werbung

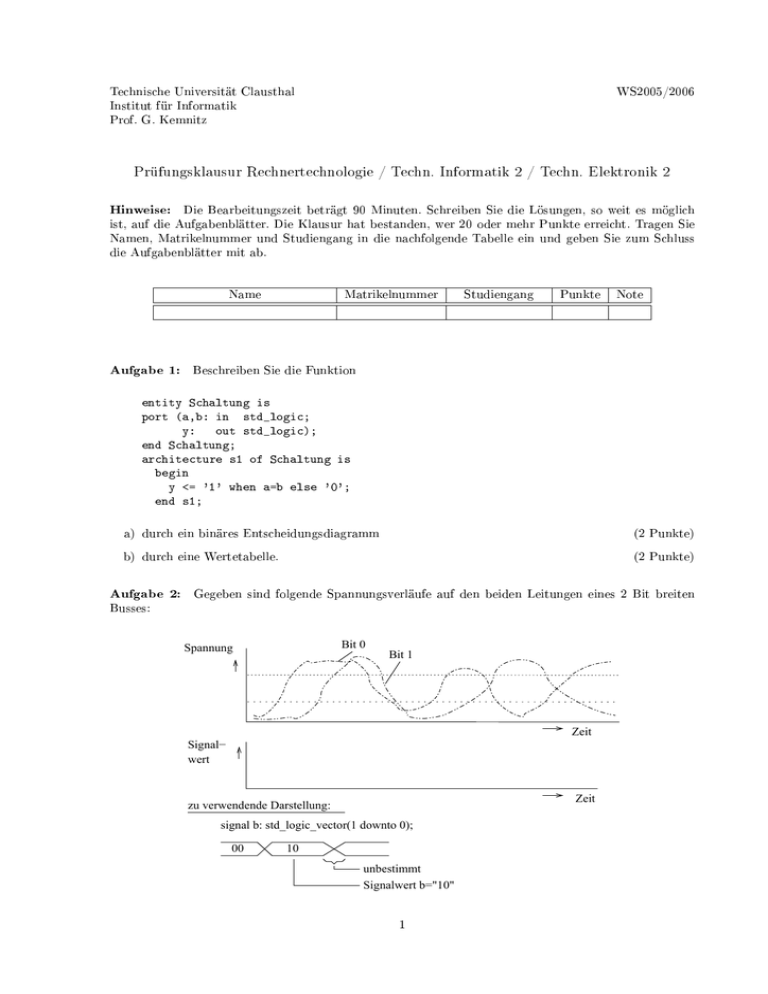

Technische Universität Clausthal

Institut für Informatik

Prof. G. Kemnitz

WS2005/2006

Prüfungsklausur Rechnertechnologie / Techn. Informatik 2 / Techn. Elektronik 2

Hinweise: Die Bearbeitungszeit beträgt 90 Minuten. Schreiben Sie die Lösungen, so weit es möglich

ist, auf die Aufgabenblätter. Die Klausur hat bestanden, wer 20 oder mehr Punkte erreicht. Tragen Sie

Namen, Matrikelnummer und Studiengang in die nachfolgende Tabelle ein und geben Sie zum Schluss

die Aufgabenblätter mit ab.

Name

Matrikelnummer

Studiengang

Punkte

Note

Aufgabe 1: Beschreiben Sie die Funktion

entity Schaltung is

port (a,b: in std_logic;

y: out std_logic);

end Schaltung;

architecture s1 of Schaltung is

begin

y <= '1' when a=b else '0';

end s1;

a) durch ein binäres Entscheidungsdiagramm

(2 Punkte)

b) durch eine Wertetabelle.

(2 Punkte)

Aufgabe 2: Gegeben sind folgende Spannungsverläufe auf den beiden Leitungen eines 2 Bit breiten

Busses:

Bit 0

Spannung

Bit 1

Zeit

Signal−

wert

Zeit

zu verwendende Darstellung:

signal b: std_logic_vector(1 downto 0);

00

10

unbestimmt

Signalwert b="10"

1

a) Kennzeichnen Sie in der Grak darunter die zeitlichen Bereiche, in denen der Signalwert auf dem

Bus unbestimmt ist.

(3 Punkte)

b) Tragen Sie für alle Bereiche, in denen der Signalwert deniert ist, den Signalwert ein (positive

Logik).

(3 Punkte)

Aufgabe 3: Für die nachfolgende Schaltung

X1

X

X

X2

2.1

X 3.1

X

X

3

Z1

=1

=1

Z

1.2

X

3.2

X 2.2

1.1

Z 1.1

&

1.2

&

Z3

X

y1

Z2

Z

3.1

1

y2

Z3.2

&

2.3

y3

sind für die verwendeten Gattertypen die minimalen Haltezeiten th und die maximalen Verzögerungszeiten

td gegeben:

Gattertyp

EXOR

UND

ODER

NAND

th

2 ns

1 ns

1,5 ns

1 ns

td

6 ns

4 ns

5 ns

3 ns

a) Bestimmen Sie die minimale Haltezeit und die maximale Verzögerungszeit der Gesamtschaltung.

(3 Punkte)

b) Erweiteren Sie die Schaltung (auf dem Aufgabenblatt) zu einer laufzeittoleranten Schaltung und

bestimmen Sie die maximale Taktfrequenz (Setup-Zeit der Register: ts = 1ns; Verzögerungszeit der

Register: tdr = 1ns).

(2 Punkte)

Aufgabe 4: Bestimmen Sie für das nachfolgend dargestellte rückgekoppelte Schieberegister den zeitlichen

Verlauf des Ausgabesignals Q (Datenübernahme in die Speicherzellen bei steigender Taktanke).(4 Punkte)

D

D

Q(0)

Q(1)

Q(2)

D

x

Datenübernahme bei

steigender Taktflanke

Takt

Takt

x

Q(2 downto 0)

111

1

2

3

4

2

5

6

7

8

Aufgabe 5: Die Funktion eines Automaten ist durch folgenden Graphen und die Zusatzbedingung:

"Zustandswechsel bei steigender Taktanke" gegeben:

x=’0’

Z2

x=’0’

Z1

y<=’0’

y<=’0’

x=’1’

x=’1’

Z3

x=’1’

y<=’1’

x=’0’

symbolische Zustandsbezeichnung

Zustandsvektor

Z1

00

Z2

01

Z3

"1X"

a) Füllen Sie die nachfolgende Übergangstabelle für den Automaten aus:

Eingabe

Zustand

Folgezustand

Ausgabe

0

00

1

00

0

01

1

01

0

1X

(2 Punkte)

1

1X

b) Beschreiben Sie die Funktion des Automaten in VHDL (Entity- und Architecture-Teil).(4 Punkte)

c) Stellen Sie für alle Registereingangssignale und alle Ausgangssignale je ein KV-Diagramm auf und

lesen Sie aus den KV-Diagrammen minimierte logische Gleichungen ab.

(4 Punkte)

d) Zeichnen Sie die Gesamtschaltung.

(2 Punkte)

Aufgabe 6: Eine digitale Schaltung soll folgende Berechnungen durchführen:

...

use IEEE.STD_LOGIC_UNSIGNED.ALL

...

signal a, b: std_logic_vector(2 downto 0);

...

c <= a * (('0' & a(2) & "00") + (b & "111"));

a) Berechnen Sie für folgende Eingaben den Wert von c:

a

b

c

"010"

"001"

"000"

"000"

(4 Punkte)

"111"

"111"

"011"

"101"

b) Bestimmen Sie den maximalen Wert von c. Wie groÿ muss der Bitvektor für c gewählt werden?

(1 Punkt)

3

Aufgabe 7: Entwickeln Sie eine komplette VHDL-Beschreibung für eine Schaltung, die zyklisch folgendes

Ausgabesignal y erzeugt:

(6 Punkte)

y

’1’

’0’

Zeit

10 µs

10 µs

10 µs

10 µs

10 µs

10 µs

10 µs

Zyklus

Zur Bewertung:

Aufgabe

max. Punktezahl

erzielte Punktezahl

1

4

2

6

3

5

4

4

5

12

4

6

5

7

6

Summe

40 + 2 Zusatzpunkte