Technische Informatik I

Werbung

Technische Informatik I

Prof. Dr. M. Radetzki

Universität Stuttgart

Vorlesung im Sommersemester 2009

Folienmaterial mit freundlicher Genehmigung von

Dr. D. Stoffel, TU Kaiserslautern

Folie 1-1

Einführung

Vorlesungstermine

Termine:

• montags,

• dienstags,

11.30 – 13.00 Uhr, V38.01

11.30 – 13.00 Uhr, V38.01

Achtung!

Nicht an jedem Termin findet eine Vorlesung statt!

Die jeweils nächsten Termine werden in der Vorlesung

bekanntgegeben.

Terminvorschau außerdem auf der Vorlesungs-Webseite:

http://www.iti.uni-stuttgart.de

→ Kurse

→ Sommersemester 2009

→ Vorlesung Technische Informatik I

Folie 1-2

Einführung

Übungen - Ablauf

•

•

•

•

Gruppenübungen (Tutorien)

5 Übungsgruppen

Insgesamt 5 Übungstermine pro Gruppe

Übungsblätter können von der Übungswebseite

heruntergeladen werden

• Übungen werden von der Abteilung Parallele Systeme (Prof.

Simon) durchgeführt

http://www.ipvs.uni-stuttgart.de

→ Abteilungen: Parallele Systeme

→ Lehre: Lehrveranstaltungen

→ Technische Informatik 1 Übung

→ Materialien

Folie 1-3

Einführung

Online-Anmeldung zu den Übungen

Zu den Übungen ist eine Online-Anmeldung erforderlich. Die

Anmeldungs-Webseite ist über die Übungs-Webseite erreichbar:

http://uebungsgruppen.informatik.uni-stuttgart.de

→Technische Informatik

→ Übungen zu Technische Informatik I

Dienstags,

15:45-17:15 Uhr in 0.363, 14-tägig

Dienstags,

17:30-19:00 Uhr in 0.108, 14-tägig

Donnerstags, 14:00-15:30 Uhr in 0.463, 14-tägig

Die Online-Anmeldung wird ab

Dienstag, 21.04.2009, 14:00 Uhr

freigeschaltet.

Anmeldung möglich bis Freitag, 24.04.2009, 18:00 Uhr!

Folie 1-4

Einführung

Sonstiges

Kriterien für Erwerb des Übungsscheins:

• Anwesenheitspflicht und aktive Mitarbeit in der Übung als

Voraussetzung für die Zulassung zur Scheinklausur

• Scheinklausur in der letzten Vorlesungswoche

(lernen Sie vorlesungsbegleitend!)

• Auch wenn Sie den Schein nicht brauchen: die Inhalte dieser

Vorlesung machen 50% der Prüfungsklausur aus!

Skript/Folien:

• Tafelanschrieb mitschreiben!

• Buch „Technische Informatik 1“ in der Inf.-Bibliothek.

• Folien stehen über die Vorlesungs-Webseite zur Verfügung.

• Benutzername und Passwort am Ende dieser Vorlesung.

Folie 1-5

Technische Informatik I

Technische Informatik I

Prof. Dr. Martin Radetzki

Universität Stuttgart

Kapitel 1

Einführung

Folie 1-1

Einführung

Informationstechnik – Technische Informatik

Informationstechnische Systeme

halten Einzug in viele Bereiche

des täglichen Lebens:

PC, Handy, Multimedia,

Automobil etc.

Überall im Alltag stoßen wir auf technische Systeme, die Information speichern,

übertragen und verarbeiten.

Folie 1-2

Einführung

Technische Informatik

Die Technische Informatik ist ein wichtiges Grundgebiet der

Informatik.

Ihr Gegenstand sind die Techniken, die die

Speicherung,

Übertragung und

Verarbeitung

von Information ermöglichen.

Was ist Information ? „etwas Wissbares“ (S. Wendt)

Was ist „wissbar“ ? …

(unsere intuitive Vorstellung soll uns genügen)

Information wird in physikalisch realisierbaren Mustern symbolisiert: „Daten“

(In der Informatik betrachten wir meistens nur die Daten, nicht die symbolisierte

Information.)

Folie 1-3

Einführung

Speicherung

von Information (oder „Daten“) in technischen Systemen

Speichermedien sind beispielsweise:

Hauptspeicher eines Computers (RAM), Festplatte eines Computers, FlashSpeicher, CDs, DVDs, Plastikkarte mit Magnetstreifen, Leitz-Ordner

Wie realisiere ich elektronische Speichermedien physikalisch?

Mit dieser Frage beschäftigen sich beispielsweise Mikroelektronik oder

Halbleiterphysik.

Folie 1-4

Einführung

Speicherung

von Information (oder „Daten“) durch technische Systeme

Es kommen wichtige Fragen hinzu:

Wie strukturiert, wie repräsentiert man die Information, so dass man:

• sie möglichst einfach (und schnell) abspeichern kann?

• sie möglichst einfach (und schnell) wieder abrufen kann?

• möglichst wenig Ressourcen benötigt?

Solche Fragen werden z.B. in der Datenbanktechnik behandelt, wo es darum geht,

große Mengen von Daten zu verwalten,

oder z.B. in der Rechnerarchitektur, wo man sich Speicherhierarchien

(Register→Cache→Hauptspeicher→Festplatte →Magnetband) überlegt, um eine

möglichst schnelle und dennoch kostengünstige Informationsverarbeitung zu

gewährleisten.

Folie 1-5

Einführung

Übertragung

von Information (oder „Daten“) durch technische Systeme

Information (Daten) wird heute in Kommunikationsnetzwerken übertragen, in

denen unterschiedliche Übertragungsstrecken zusammengeschaltet sind. Damit

beschäftigt sich die Kommunikationstechnik.

Beispiele für Übertragungsstecken:

Richtfunk, Kupferkabel, Glasfaserkabel,

per Satellit etc.

Wie realisiert man Kommunikationsnetzwerke mit guten physikalischen

Übertragungseigenschaften?

Aber auch:

Wie repräsentiert („kodiert“) man Information, so dass man in möglichst kurzer

Zeit unter Aufwendung möglichst geringer Ressourcen möglichst viel

Information übertragen und möglichst einfach weiterverarbeiten kann?

Folie 1-6

Einführung

Verarbeitung

von Information (oder „Daten“) durch technische Systeme

Information (Daten) wird in technischen Systemen unterschiedlicher Art

verarbeitet.

Der Informationsverarbeitung in technischen Systemen liegt stets ein formales

Verfahren zugrunde, also eine Abfolge von vorher festgelegten elementaren

Verfahrensschritten.

Im Unterschied dazu verarbeitet der Mensch Information häufig ohne ein (ihm

bewusstes) formales Verfahren.

Folie 1-7

Einführung

Beispiele

informationsverarbeitender Systeme

Der Getränkeautomat

Eingabe von Daten in Form von

unterschiedlichen Münzen und mit einer

Tastatur zur Auswahl einer Getränkesorte

Ausgabe einer Getränkedose und von

Wechselgeld entsprechend der eingeworfenen

Geldsumme

Der Getränkeautomat muss ein einfaches formales Verfahren besitzen, mit

dem er für jede Eingabe entscheidet, ob eine Getränkedose bestimmten Typs

ausgegeben wird und wieviel Wechselgeld zurückgegeben wird.

Folie 1-8

Einführung

Beispiele

informationsverarbeitender Systeme

Das Überdruckventil eines Schnellkochtopfs

Eingabe ist der Dampfdruck im Inneren des Topfes.

Ausgabe ist ein Pfeifgeräusch, das ertönt, wenn der Druck einen bestimmten

Schwellenwert übersteigt, sowie das Auslösen des Ventils, um den Dampf

entweichen zu lassen.

Das Überdruckventil kann z. B. durch eine einfaches mechanisches Verfahren

basierend auf einer Feder realisiert werden.

Folie 1-9

Einführung

Beispiele

informationsverarbeitender Systeme

Der Computer

Eingabe von Daten über Tastatur, Maus, Netzwerk und andere periphere Geräte

Ausgabe von Daten über Monitor, Lautsprecher, Netzwerk, Drucker und andere

periphere Geräte

Durch Programmierbarkeit können je nach Anwendung und Art der Ein-/Ausgabedaten unterschiedliche formale Verfahren zur Informationsverarbeitung

„implementiert“ werden:

z.B.

•

•

•

•

Verfahren zur Lösung mathematischer Probleme

Verfahren zur Steuerung von produktionstechnischen Anlagen

Verfahren zur Unterstützung verwaltungstechnischer und betrieblicher Abläufe

Verfahren zur Unterstützung von Entwurfsprozessen (CAD)

Folie 1-10

Einführung

Verarbeitung

von Information (oder „Daten“) durch technische Systeme

Wie realisiert man informationsverarbeitende Systeme?

Wie realisiert man die physikalischen Vorgänge, die informationsverarbeitenden

Prozessen zugrunde liegen?

Dies ist eine Fragestellung der Mikroelektronik, der Elektronik und der

Schaltungstechnik.

Wie strukturiert man die Information und ihre Verarbeitung?

Welche informationellen Strukturen und welche Formalismen legt man

informationsverarbeitenden Systeme zugrunde?

Dies ist eine Fragestellung der Informatik.

Folie 1-11

Einführung

Verarbeitung

von Information (oder „Daten“) durch technische Systeme

Beispiel: Formalismus zur Darstellung nichtnegativer ganzer Dezimalzahlen als

Dualzahl

Man gibt zur Identifikation einer Zahl jeweils diejenigen Zweierpotenzen an, deren

Summe die gemeinte Zahl ist. Zum Beispiel ist mit 11001 die Zahl fünfundzwanzig

gemeint, weil 1·24 + 1·23 + 0·22 + 0·21 + 1·20 = 16 + 8 + 1 = 25 ist.

Für ein physikalisches System zur Darstellung einer Dualzahl gibt es viele

Möglichkeiten, z.B. eine Folge von Speicherzellen (Bits) in einem Register, eine

Folge von Leuchtdioden, eine Lochkarte, etc.

Zum Verständnis der Funktion eines solchen Systems benötigt man beides:

•

Kenntnis der elektrotechnisch/physikalischen Realisierung,

•

Kenntnis des zugrundeliegenden Formalismus, mit dem eineInterpretation

verbunden ist. Diese muss man kennen, wenn man das System seinem Zweck

entsprechend einsetzen will.

Folie 1-12

Einführung

Die Trennung zwischen den informationellen Strukturen eines informationstechnischen Systems, die man mit bestimmten Formalismen beschreiben kann und

den Techniken zu ihrer physikalischen Realisierung ist unvermeidlich, wenn man

große, komplexe Systeme entwerfen will.

Beispiel: Computerprogramm

Ein Programm ist zunächst lediglich eine Beschreibung eines technischen Systems. Es

ist selbst nicht zu Wechselwirkungen mit seiner Umwelt fähig. Im Bereich software

engineering beschäftigt man sich mit den Strukturen eines Programms. Sie sind nicht

mit den Strukturen des durch das Programm beschriebenen Systems zu verwechseln.

Das beschriebene System wird realisiert, indem man das Programm in ein programmierbares System einbringt, so dass es sich gemäß dem Programm verhalten kann.

Während man das Programm entwirft, braucht man sich nicht mit den technischen

Realisierungen zu beschäftigen, für die es viele Möglichkeiten gibt. Während man die

technischen Realisierungen entwirft, braucht man sich nicht mit den Programmen

beschäftigen, die später darauf abgearbeitet werden sollen.

Nur durch diese Trennung ist es möglich, große Systeme zu entwerfen.

Folie 1-13

Einführung

Thema der Vorlesung "Technische Informatik I"

physikalische/elektrotechnische

Hilfsmittel,

einfache Bausteine zur Realisierung

informationstechnischer Systeme

mathematische Hilfsmittel

(Formalismen)

zur Beschreibung

informationstechnischer Systeme

Methodik für den Entwurf komplexer

informationstechnischer Systeme

In dieser Vorlesung betrachten wir die elektrotechnischen Grundlagen

der technischen Informatik und die Anwendung ihrer Formalismen auf

den Entwurf digitaler Schaltungen.

Folie 1-14

Einführung

Beispiel: Signale

Information kann in unterschiedlichen physikalischen Erscheinungsformen

übermittelt werden, z.B. mittels

Schallwellen, Spannungs- und Stromschwankungen in einem Leiter, elektromagnetischen Wellen.

Die Prozesse der räumlichen und zeitlichen Änderung dieser physikalischen

Größen beschreiben wir mathematisch durch Signale.

Auf Signale und ihre Klassifikation wird später noch genauer eingegangen.

Die meisten technischen Systeme zur Informationsverarbeitung verbinden

Information mit bestimmten Objekten, z.B. Münzen (Getränkeautomat) oder

binäre Zahlen (Computer). Kennzeichen dieser Objekte ist, dass sie voneinander

unterscheidbar (diskret) und somit abzählbar sind.

Folie 1-15

Einführung

Digital versus analog

Digitale und analoge Signale

+5

+5

1

0

1

V

V

Zeit

Zeit

–5

Digital:

es können nur diskrete Werte

angenommen werden (hier werden

sogar nur zwei Werte unterschieden,

es handelt sich deshalb um ein

binäres Signal)

–5

Analog:

Werte variieren kontinuierlich über

den gesamten Wertebereich

Folie 1-16

Einführung

Vorteile digitaler Systeme

Analoges System: kleine Schwankungen am Eingang können zu großen

Schwankungen am Ausgang führen

Digitales System: höhere Robustheit und Genauigkeit, kleine Signalschwankungen

werden „wegabstrahiert“

einzelne Systemkomponenten können leichter zusammengesetzt

werden

Computer benutzen intern digitale Schaltungen.

Die reale physikalische Welt ist analog. Interface-Schaltungen (z.B. Sensoren und

Aktuatoren) sind daher meist analog.

Folie 1-17

Einführung

Digitale Hardware

Binäre Systeme

• Zwei diskrete Werte:

on, 5 Volt, high, Strom fließt, magnetischer Nordpol, "1"

off, 0 Volt, low, kein Strom fließt, magnetischer Südpol, "0"

• Vorteile binärer Systeme:

sehr gut durch Gesetze der mathematischen Logik beschreibbar,

vor allem: technologisch leicht realisierbar

Beispiel:

WENN

WENNdie

dieAmpel

Ampelfür

fürdie

dieHauptstraße

Hauptstraßegrün

grünist

ist

UND

die

Ampel

für

die

einmündende

Straße

UND die Ampel für die einmündende Straßerot

rotist

ist

UND

UND45

45Sekunden

Sekundenseit

seitdem

demletzten

letztenWechsel

Wechselvergangen

vergangensind,

sind,

DANN

wird

die

Ampel

für

die

Hauptstraße

gelb

DANN wird die Ampel für die Hauptstraße gelb

Folie 1-18

Einführung

Beispiel einer Implementierung

Beispiel einer Implementierung eines informationstechnischen

Systems mit Hilfe eines Netzwerkes von Schaltern:

Jeder Schalter wird von einem Steuersignal bedient.

Man kann mit einem solchen Schalternetzwerk die Gültigkeit

logischer Aussagen bestimmen.

Hauptstraße

grün

True

einmündende

Straße rot

45 s seit

letztem Wechsel

Hauptstraße

wird gelb

WENN

WENNdie

dieAmpel

Ampelfür

fürdie

dieHauptstraße

Hauptstraßegrün

grünist

ist

UND

die

Ampel

für

die

einmündende

Straße

UND die Ampel für die einmündende Straßerot

rotist

ist

UND

UND45

45Sekunden

Sekundenseit

seitdem

demletzten

letztenWechsel

Wechselvergangen

vergangensind,

sind,

DANN

wird

die

Ampel

für

die

Hauptstraße

gelb

DANN wird die Ampel für die Hauptstraße gelb

Folie 1-19

Einführung

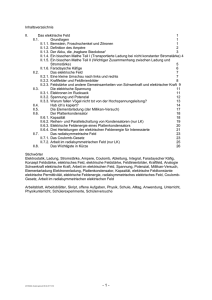

Gliederung

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

Einführung

Physikalische und mathematische Grundbegriffe

Das elektrostatische Feld

Elektrischer Strom und elektrische Netzwerke

Elektromagnetische Vorgänge

Halbleiterbauelemente

Digitale Grundschaltungen

Optimierung von Schaltnetzen

Bausteine digitaler Entwürfe

Automaten als Verhaltensmodelle sequenzieller Netzwerke

Schaltwerke

Funktionseinheiten sequenzieller Systeme

Aufbau eines Rechners

Entwurfsautomatisierung

Folie 1-20

Einführung

Literatur (1)

Manfred Albach:

Grundlagen der Elektrotechnik I

2004, Pearson Studium Verlag, ISBN 3-8273-7106-6, 292 S.

Wolfram Schiffmann, Robert Schmitz:

Technische Informatik 1

5. Aufl., 2004, Springer-Verlag, ISBN 3-540-40418-7, 337 S.

Bernd Becker, Rolf Drechsler, Paul Molitor:

Technische Informatik

Eine Einführung.

2005, Pearson Studium Verlag, ISBN 3-8273-7092-2, 390 S.

Randy Katz:

Contemporary Logic Design

1994, Benjamin/Cummings-Verlag, ISBN 0-8053-2703-7.

Folie 1-21

Einführung

Literatur (2)

U. Schöning:

Logik für Informatiker

1995, Spektrum Lehrbuch, Akademischer Verlag, ISBN 3-86025-684-X.

S. Wendt:

Nichtphysikalische Grundlagen der Informationstechnik

Interpretierte Formalismen

1991, Springer-Verlag, ISBN 3-540-54452-6, 487 S.

Folie 1-22

Technische Informatik I

Prof. Dr. Martin Radetzki

Universität Stuttgart

Kapitel 2

Physikalische und mathematische Grundbegriffe

Folie 2-1

Physikalische und mathematische Grundbegriffe

Physikalische Größen

Die Physik befasst sich mit messbaren Eigenschaften von Naturvorgängen

und den zwischen ihnen bestehenden gesetzmäßigen Beziehungen.

Eigenschaften werden durch den Begriff „Physikalische Größe“

bezeichnet.

Physikalische Größen sind beispielsweise:

•

•

•

•

•

Länge (gemessen in Meter,m)

Zeit (gemessen in Sekunde,s)

Kraft (gemessen in Newton,N)

elektrische Spannung (gemessen in Volt,V)

...

Physikalische Größen sind durch mathematische Gleichungen, so

genannte Größengleichungen, miteinander verknüpft. Diese Gleichungen

beschreiben physikalische Gesetzmäßigkeiten, beispielsweise:

Spannung = elektrischer Widerstand mal Stromstärke

U=R•I

(Ohm'sches Gesetz)

Folie 2-2

Physikalische und mathematische Grundbegriffe

Physikalische Größen

Der Wert einer physikalischen Größe ist das Produkt aus einem

Zahlenwert und einer Einheit:

Wert der Größe = Zahlenwert • Einheit

Bsp.: U = 5,2 V bedeutet:

gemessene Spannung U beträgt das 5,2fache eines Volt.

Zahlenwert = 5,2

Einheit = V

Zur besonderen Kennzeichnung der Einheit wird die eckige Klammer

verwendet.

Bsp.: [I] = A bedeutet:

die Einheit der elektrischen Stromstärke I ist Ampere.

Folie 2-3

Physikalische und mathematische Grundbegriffe

Basisgrößenarten

In der Physik werden 7 Basisgrößenarten verwendet. Sie sind voneinander

unabhängig. Von ihnen lassen sich alle anderen Größen ableiten. Die

Basiseinheiten sind im internationalen Système International d’Unités (SI)

festgelegt.

übliches

Formelzeichen

SI-Basiseinheit

Länge

l

das Meter (m)

Masse

m

das Kilogramm (kg)

Zeit

t

die Sekunde (s)

elektrische Stromstärke

I

das Ampere (A)

Temperatur

T, ϑ

das Kelvin (K)

Stoffmenge

n

das Mol (mol)

Lichtstärke

IV

die Candela (cd)

MKSA-System

Basisgrößenart

Für die Beschreibung mechanischer sowie elektromagnetischer Vorgänge

reichen die vier SI-Basisgrößen des MKSA-Systems (Meter, Kilogramm,

Sekunde, Ampere) aus.

Folie 2-4

Physikalische und mathematische Grundbegriffe

Abgeleitete Einheiten

Aus den Basiseinheiten lassen sich durch Multiplikation, Division und

Potenzierung abgeleitete Einheiten bilden, die ihrerseits einen eigenen

Namen bzw. ein eigenes Zeichen besitzen können.

Beispiele:

[Ladung] = Coulomb

[Q] = C

mit 1 C = 1 As

[Kraft] = Newton

[F] = N

mit 1 N = 1 kg m/s2

[Frequenz] = Hertz

[f] = Hz

mit 1 Hz = 1/s

Die Dimension dim x einer Größe x gibt den Zusammenhang

zwischen x und den Basisgrößen an. Sie wird als Produkt von

Potenzen der Basisgrößen-Formelzeichen angegeben.

Beispiel: Die Dimension der Geschwindigkeit v (= Weg/Zeit) lautet

dim v = l t–1

Folie 2-5

Physikalische und mathematische Grundbegriffe

Weitere Einheiten

Neben den SI-Einheiten existieren noch einige andere Einheiten für die

Anwendung in speziellen Gebieten. Ihr Zusammenhang mit den SIEinheiten wird experimentell ermittelt. Die für uns wichtigen Beispiele sind

das Elektronenvolt (eV) und die atomare Masseneinheit (u).

Ein Elektronenvolt (eV) entspricht der kinetischen Energie, die ein

Elektron beim Durchlaufen einer Potenzialdifferenz von 1 V im Vakuum

gewinnt.

1eV = 1,6021892 · 10–19 J

Die atomare Masseeinheit u wird angegeben in kg und entspricht 1/12 der

Masse eines Kohlenstoffisotops 12C.

1u = 1,66057 · 10–27 kg

Folie 2-6

Physikalische und mathematische Grundbegriffe

SI-Vorsätze

Ist der Zahlenwert einer physikalischen Größe unpraktisch groß

oder klein, so kann eine Zehnerpotenz der Einheit verwendet

werden.

Die Zehnerpotenz wird durch einen der folgenden Vorsätze

gekennzeichnet:

Potenz Name Zeichen

Potenz Name Zeichen

1015

Peta

P

10-3

Milli

m

1012

Tera

T

10-6

Mikro

µ

109

Giga

G

10-9

Nano

n

106

Mega

M

10-12

Piko

p

103

Kilo

k

10-15

Femto

f

Folie 2-7

Physikalische und mathematische Grundbegriffe

SI-Vorsätze

Der Vorsatz wird so gewählt, dass der Zahlenwert der Größe

zwischen 0,1 und 1000 liegt.

Bsp.: Ein Radiosender sendet auf einer Frequenz von 106 300 000 Hertz

106 300 000 Hz = 106 300 kHz = 106,3 MHz

Anmerkung:

Eine Besonderheit bildet die SI-Basiseinheit Kilogramm (kg). Die Vorsätze

werden nicht auf kg, sondern auf die Einheit Gramm (g) angewendet.

Beispielsweise werden 10-3 g als mg und nicht als µkg bezeichnet.

Folie 2-8

Physikalische und mathematische Grundbegriffe

Skalare und vektorielle Größen

Physikalische Größen sind entweder Skalare oder Vektoren.

Skalare Größen sind durch Zahlenwert und Einheit vollständig

charakterisiert.

Beispiele skalarer Größen:

Zeit t, Temperatur T, elektrische Ladung Q, Masse m, ...

Vektorielle Größen haben neben Zahlenwert und Einheit auch noch

eine Richtung.

Beispiele vektorieller Größen:

Geschwindigkeit v, Kraft F, elektrische Feldstärke E, ...

Benötigt man von einer vektoriellen Größe A nur Zahlenwert und

Einheit, also den Betrag des Vektors A, so schreibt man |A| oder nur

kurz A.

Folie 2-9

Physikalische und mathematische Grundbegriffe

Freie und gebundene Vektoren

In der Physik unterscheidet man zwischen freien Vektoren und

gebundenen Vektoren.

Bei freien Vektoren spielt die Position ihres Anfangspunktes keine

Rolle, d.h. sie können frei im Raum verschoben werden.

Gebundene Vektoren sind an ihren Anfangspunkt gebunden und

somit ortsabhängig.

Bsp.:

die Feldvektoren der elektrischen Feldstärke. Sie sind im

Allgemeinen von Ort zu Ort nach Betrag und Richtung verschieden.

Vektoren, die in einem festen Punkt (z.B. dem Koordinatenursprung)

beginnen, können überhaupt nicht verschoben werden und heißen

Ortsvektoren.

Axiale Vektoren tragen die Information eines Drehsinns. Ihre

Richtung verläuft parallel (oder antiparallel) zur Drehachse. Das

Vorzeichen kennzeichnet den Drehsinn.

Folie 2-10

Physikalische und mathematische Grundbegriffe

Negativer Vektor, Einheitsvektor, Nullvektor

Unter einem Vektor -a versteht

man einen Vektor mit dem

gleichen Betrag wie +a, aber

mit entgegengesetzter Richtung.

Ein Vektor vom Betrag 1 wird

Einheitsvektor genannt. Jeder

Vektor kann aus einem Betrag

(seiner Länge) und einem in

Richtung des Vektors

zeigenden Einheitsvektor

dargestellt werden.

Der Nullvektor 0 ist ein Vektor mit Betrag 0. Er hat keine Richtung.

Für den Nullvektor ist auch die Schreibweise 0 (ohne Vektorpfeil)

gebräuchlich.

Folie 2-11

Physikalische und mathematische Grundbegriffe

Addition und Subtraktion von Vektoren

Vektoraddition a+b:

Parallelverschiebung und

"Aneinanderhängen".

Die Vektoraddition ist

kommutativ:

Vektorsubtraktion –b:

Bildung von –b, danach

Vektoraddition:

r

r r r

a − b = a + ( −b )

r r r r

a+b =b +a

Folie 2-12

Physikalische und mathematische Grundbegriffe

Multiplikation von Vektor und Skalar

Die Multiplikation eines Vektors mit einem Skalar ergibt wieder

einen Vektor gleicher (oder entgegegengesetzter) Richtung.

a

b = ·a ,

b = ·a ,

>0

<0

Folie 2-13

Physikalische und mathematische Grundbegriffe

Skalarprodukt ("inneres Produkt")

Das Skalarprodukt a·b zweier Vektoren a und b ist ein Skalar und

ist definiert als:

a·b = |a|·ea · |b|·eb = a·b·cos

Folie 2-14

Physikalische und mathematische Grundbegriffe

(Skalarprodukt)

Das Skalarprodukt ist kommutativ:

a·b = b·a

Das Skalarprodukt ist distributiv bezüglich der

Vektoraddition und Vektorsubtraktion:

a·(b + c) = a·b + a·c

Für parallele bzw. senkrecht aufeinander stehende Vektoren a und b

gelten folgende Spezialfälle:

a·b = ab

wenn a und b parallel sind

a·b = 0

wenn a und b senkrecht zueinander sind

a·b = –ab

wenn a und b antiparallel sind

Folie 2-15

Physikalische und mathematische Grundbegriffe

Vektorprodukt ("Kreuzprodukt", "äußeres Produkt")

Das Vektorprodukt a×b zweier Vektoren a und b ist ein Vektor c

definiert durch:

Betrag:

|c| = |a|·|b|·sin

= ab sin

Richtung: c steht senkrecht auf der von a und b

aufgespannten Ebene und zwar so, dass

a, b und c ein Rechtssystem bilden.

Folie 2-16

Physikalische und mathematische Grundbegriffe

(Vektorprodukt)

Das Vektorprodukt ist nicht kommutativ:

a×b = – b×a

Das Vektorprodukt ist distributiv bezüglich der

Vektoraddition und Vektorsubtraktion:

a×(b + c) = a×b + a×c

Für parallele bzw. senkrecht aufeinander stehende Vektoren a und b

gelten folgende Spezialfälle:

a×b = 0

wenn a und b parallel sind

a×b = ab ec

wenn a und b senkrecht zueinander stehen

a×b = 0

wenn a und b antiparallel sind

Folie 2-17

Physikalische und mathematische Grundbegriffe

Kartesisches Koordinatensystem

Die Koordinatenachsen sind

zueinander orthogonal.

Die Einheitsvektoren ex, ey und ez

verlaufen parallel zu den Koordinatenachsen und bilden ein Rechtssystem.

Ein Raumpunkt P wird bezogen auf

den Koordinatenursprung 0 durch einen

Ortsvektor r der Länge r = | r |

beschrieben.

r = x ex + y ey + z ez

r

r = r = x2 + y2 + z2

Folie 2-18

Physikalische und mathematische Grundbegriffe

Vektoroperationen im kartesischen Koordinatensystem

Mit a = ax ex + ay ey + az ez und b = bx ex + by ey + bz ez lassen sich die

Vektoroperationen in kartesischen Koordinaten wie folgt berechnen:

Vektoraddition: a + b = (ax + bx) ex + (ay + by) ey + (az + bz) ez

Vektorsubtraktion: a – b = (ax – bx) ex + (ay – by) ey + (az – bz) ez

Multiplikation mit Skalar:

Skalarprodukt:

a =

a x ex + a y ey + a z ez

a · b = axbx + ayby + azbz

Vektorprodukt: a × b = (aybz – azby) ex + (azbx – axbz) ey + (axby – aybx) ez

Folie 2-19

Physikalische und mathematische Grundbegriffe

Beispiele krummliniger Koordinatensysteme

Zylinderkoordinaten

Ein Raumpunkt P wird durch die Koordinaten , und z beschrieben.

Die (ortsabhängigen) Einheitsvektoren e , e und ez bilden in jedem

Raumpunkt ein orthogonales Rechtssystem.

Folie 2-20

Physikalische und mathematische Grundbegriffe

Beispiele krummliniger Koordinatensysteme

Kugelkoordinaten

Ein Raumpunkt P wird durch die Koordinaten r, ϑ und beschrieben.

Die (ortsabhängigen) Einheitsvektoren er, eϑ und e bilden in jedem

Raumpunkt ein orthogonales Rechtssystem.

Folie 2-21

Technische Informatik I

Prof. Dr. Martin Radetzki

Universität Stuttgart

Kapitel 3

Das elektrostatische Feld

Folie 3-1

Elektrostatisches Feld

Bohr'sches Atommodell

Niels Bohr (1885-1962)

–

–

0 + 0 Atomkern, ∅ ~ 10-14 m

+0+

0+

–

+

Proton

–

Elektron

0

Neutron

Elektronenhülle, ∅ ~ 10-10 m (!)

–

Folie 3-2

Elektrostatisches Feld

Elektrische Ladung

Die kleinste (nicht weiter teilbare) Ladungsmenge heißt

Elementarladung e = 1.6021892·10-19 As

Protonen tragen die Ladung +e.

Elektronen tragen die Ladung –e.

Da die Anzahl der Protonen und Elektronen in den Atomen gleich groß ist,

verhalten sich Atome nach außen elektrisch neutral.

Ladungen sind stets ein Vielfaches der Elementarladung.

In einem abgeschlossenen System ist die Summe der Ladungen stets

konstant.

Ladungen gleichen Vorzeichens stoßen sich gegenseitig ab.

Ladungen unterschiedlichen Vorzeichens ziehen sich gegenseitig an.

Folie 3-3

Elektrostatisches Feld

Coulomb'sches Gesetz

Durch Messung hat Charles Augustin de

Coulomb (1736-1806) für die Kraft F zwischen

zwei Punktladungen Q1 und Q2 festgestellt:

Q1Q2

F~ 2

r

Die Proportionalitätskonstante ist 1/4 0. Der Faktor 0 heißt

elektrische Feldkonstante und beträgt 0 = 8,854·10-12 As/Vm.

Mit der Festlegung eines

Einheitsvektors er in Richtung

von Q1 nach Q2 ergibt sich der

Kraftvektor nach Betrag und

Richtung zu:

r

F=

1 Q1Q2 r

er

2

4πε 0 r

Folie 3-4

Elektrostatisches Feld

Elektrisches Feld

Die Ladung Q2 erfährt durch das Vorhandensein der Ladung Q1 eine

Kraftwirkung. Die Kraftwirkung ist direkt proportional zu Q2 und abhängig

vom Ort der Ladung Q2.

Man sagt, die ruhende Ladung Q1 ruft ein elektrisches Feld hervor, das sich

durch Kraftwirkung auf Probeladungen Q2 bemerkbar macht.

r

F=

r

1 Q1 r

e ⋅ Q2 = E ⋅ Q2

2 r

4πε 0 r

r

E=

1 Q1 r

e

2 r

4πε 0 r

Die Größe E wird elektrische Feldstärke genannt und hat die Einheit V/m.

Der Zusammenhang zwischen der Kraft F auf eine Ladung Q in einem

elektrischen Feld und der elektrischen Feldstärke E lautet

r r

F = E ⋅Q

Folie 3-5

Elektrostatisches Feld

(Elektrisches Feld)

Der Begriff elektrische Feldstärke bezeichnet einen Vektor in einem speziellen

Raumpunkt. Die Gesamtheit der Feldvektoren im Raum wird als elektrisches

Feld bezeichnet.

Eine positive Punktladung ruft eine radial nach außen gerichtete elektrische

Feldstärke hervor. Bei einer negativen Punktladung zeigt der Feldstärkevektor

zur Punktladung hin.

Die Kraft auf eine positive Punktladung hat die gleiche Richtung wie die

elektrische Feldstärke an der Stelle der Punktladung. Bei einer negativen

Punktladung zeigen Feldstärke und Kraft in entgegengesetzte Richtungen.

Auf die Ladung Q2 wirkt eine Kraft infolge des durch Q1 hervorgerufenen

elektrischen Feldes. Q2 erzeugt aber ihrerseits ein elektrisches Feld, das eine

gleich große, entgegengesetzt gerichtete Kraft F1 = E2Q1 = –F2 auf die

Punktladung Q1 ausübt.

Folie 3-6

Elektrostatisches Feld

Überlagerung von Feldern

Die Gesamtfeldstärke einer aus mehreren Ladungen bestehenden Anordnung

ergibt sich durch lineare Überlagerung der Beiträge der Einzelladungen:

r

r r

1

ri

E ( rP ) =

Qi 3

∑

4πε 0 i =1, 2,... ri

mit

r r r

ri = rP − rQi

und

r

ri = ri

Bsp.: Das Feld dreier

Punktladungen Q1, Q2 und

Q3 in einem Raumpunkt P:

Folie 3-7

Elektrostatisches Feld

Darstellung von Feldern

Als Feldlinien bezeichnet man

Raumkurven, bei denen die Tangente

in jedem Punkt in Richtung der

elektrischen Feldstärke zeigt.

Die Dichte der in einem Feldlinienbild eingezeichneten Feldlinien

kann in vielen Fällen so gewählt werden, dass sie ein Maß für den

Betrag der Feldstärke darstellt.

Die Feldlinien beginnen immer bei positiven Ladungen und enden auf

negativen Ladungen.

Folie 3-8

Elektrostatisches Feld

Beispiele von Feldlinienbildern

Feldlinienbilder zweier Punktladungen

Folie 3-9

Elektrostatisches Feld

(Beispiele für Feldlinienbilder)

Feldlinienbild einer einzelnen positiven Punktladung.

Zur Vereinfachung nimmt man an, dass sich die zugehörigen negativen

Ladungen auf einer unendlich fernen Hülle befinden.

Folie 3-10

Elektrostatisches Feld

(Beispiele für Feldlinienbilder)

Elektrisches Feld zwischen zwei mit den Ladungen +Q und –Q

geladenen Platten.

Folie 3-11

Elektrostatisches Feld

Arbeit

Wenn eine Kraft einen Körper auf einem bestimmten Weg verschiebt,

so verrichtet sie am Körper Arbeit.

Unter der physikalischen Größe der Arbeit W versteht man das

Produkt aus Kraft F und Weg s.

Die verrichtete Arbeit W vergrößert die Energie des Körpers um W.

SI-Einheit der Arbeit bzw. der Energie:

[W] = [F]·[s] = N·m = Joule (J) = W·s = kg·m2/s2

Wenn W die verrichtete Arbeit, F die konstante Kraft, die in

Wegrichtung wirkt und s der vom Körper zurückgelegte Weg ist,

dann gilt W = F · s.

Bilden Kraft- und Wegrichtung einen Winkel , dann darf nur die

Kraftkomponente in Wegrichtung mit dem Weg multipliziert werden:

W = F · s · cos , oder, in vektorieller Schreibweise: W = F · s.

Folie 3-12

Elektrostatisches Feld

(Arbeit)

Im allgemeinen Falle, wenn die Kraft nicht konstant, sondern nach

Betrag und Richtung ortsabhängig ist, dann ist die Arbeit das

Wegintegral der Kraft:

r r

W = ∫ F ds

P2

P1

Merke:

• Die Arbeit ist eine skalare Größe!

• Das Integral zählt die durch die Kraft verrichtete Arbeit.

• Bewegt man den Körper gegen die Kraft, so wird die aufzuwendende

Arbeit aufgrund der Eigenschaften des Skalarprodukts negativ.

Folie 3-13

Elektrostatisches Feld

Arbeit im elektrischen Feld

Auf eine Punktladung Q wirkt in einem

äußeren, durch andere Ladungen

hervorgerufenen elektrischen Feld eine

(ortsabhängige) Kraft. Verschiebt man

P

die Punktladung gegen die Feldkraft von 1

einem Punkt P1 zu einem Punkt P2, so

beträgt die aufzuwendende Arbeit:

P2

P2

r r

r r

= ∫ F ⋅ ds = Q ∫ E ⋅ ds

P2

WP1 → P2

P1

P1

Verschiebt man die Punktladung auf einem anderen Weg von P2 wieder

zurück nach P1, so ist die aufzuwendende Arbeit

P1

r r

r r

= ∫ F ⋅ ds = Q ∫ E ⋅ ds

P1

WP2 → P1

P2

P2

Folie 3-14

Elektrostatisches Feld

Konservatives Feld (Energieerhaltung)

Im elektrischen Feld wechselt das Vorzeichen der Arbeit bei Umkehrung des

Weges (Vertauschung von Start- und Endpunkt), deshalb gilt:

WP1 → P2 → P1

⎛ P2 r r ⎞ ⎛ P1 r r ⎞

⎛ P2 r r P2 r r ⎞

= ⎜ Q ∫ E ⋅ ds ⎟ + ⎜ Q ∫ E ⋅ ds ⎟ = Q ⎜ ∫ E ⋅ ds − ∫ E ⋅ ds ⎟ = 0

⎜ P

⎟ ⎜ P

⎟

⎜P

⎟

P

1

⎝ 1

⎠ ⎝ 2

⎠

⎝ 1

⎠

Darüber hinaus ist die genaue Wahl des Weges für die Arbeit unerheblich, es

kommt lediglich auf den Start- und Endpunkt an. Deshalb gilt für jeden

beliebigen geschlossenen Weg von einem beliebigen Startpunkt zu sich selbst:

r r

∫ E ⋅ ds = 0

(Ein geschlossener Integrationsweg wird durch einen

Ring im Integralzeichen gekennzeichnet.)

Diese Eigenschaft bezeichnet man als Konservativität: auf einem „Rundweg“

wird weder Energie gewonnen noch verloren; vgl. Radfahren: die beim

Bergauffahren investierte Energie wird bei der Abfahrt wieder gewonnen,

wenn man von Reibungsverlusten absieht.

Folie 3-15

Elektrostatisches Feld

Elektrostatisches Potential

Jeder Punkt des Raumes in einem

(elektrostatischen) konservativen

Feld kann durch eine skalare

Größe charakterisiert werden,

die (elektrostatisches) Potential

genannt wird, so dass gilt:

P0

ϕ2

P2

ϕ1

P1

W12 = Q ⋅ (ϕ1 − ϕ 2 )

Das Potential ist auf einen Punkt P0 bezogen (Bezugspunkt). Der Bezugspunkt

und sein Potentialwert können frei gewählt werden, da sich nur durch Addition

eines konstanten Werts auf ϕ1 und ϕ2 auswirken und so wie oben auch im

Folgenden stets nur Potentialdifferenzen verwendet werden.

Übliche Vereinbarungen für den Bezugspunkte mit (P0)= 0:

• Erdoberfläche (Äquipotentialfläche, siehe Folie 3-18)

• "Masse" in Schaltungen, z.B. Minuspol der Batterie oder Gehäuse

• eine gedachte unendliche ferne Hülle

Folie 3-16

Elektrostatisches Feld

Berechnung des elektrostatischen Potentials

P0

W12 = W10 + W02

P1

P2

ϕ1

r r

r r

= Q ∫ E ⋅ ds + Q ∫ E ⋅ ds

P0

ϕ2

P2

P1

P0

⎛ P0 r r P0 r r ⎞

= Q⎜ ∫ E ⋅ ds − ∫ E ⋅ ds ⎟ ≡ Q ⋅ (ϕ1 − ϕ 2 )

⎜P

⎟

P2

⎝ 1

⎠

Es folgt: Das elektrostatische Potential (P) an einem Punkt P ist der Quotient

aus der Arbeit, die nötig ist, um eine Ladung Q von einem Punkt P0 mit dem

Bezugspotential (P0)=0 zum Punkt P zu bringen, und der Ladung Q:

Pi

r r

r r

W0i

ϕ i = ϕ ( Pi ) = ∫ E ⋅ ds = − ∫ E ⋅ ds = −

Q

Pi

P0

P0

Folie 3-17

Elektrostatisches Feld

Äquipotentialflächen

Auf Äquipotentialflächen ist

das Potential konstant. Bewegt

man Ladungen entlang dieser

Flächen, so ändert sich ihre

potentielle Energie nicht.

Die elektrischen Feldlinien

stehen senkrecht auf den

Äquipotentialflächen.

Äquipotentiallinien sind die

Schnittlinien der Äquipotentialflächen mit der Zeichenebene.

Zeichenkonvention:

Der Abstand zwischen jeweils

benachbarten Linien entspricht

einer festen Potentialdifferenz.

(Potential einer Punktladung Q:)

Q

1

⋅

ϕ (r) =

4πε 0 r

Folie 3-18

Elektrostatisches Feld

Elektrische Spannung

Die Potentialdifferenz zwischen zwei beliebigen Punkten P1 und P2 in einem

elektrischen Feld E wird als elektrische Spannung U bezeichnet.

r r

U12 = ϕ ( P1 ) − ϕ ( P2 ) = ∫ E ⋅ ds

P2

P1

Die Einheit der elektrischen Spannung ist das Volt: 1 V = 1 J/As = 1 kg m2/As3

(nach Alessandro Giuseppe Antonio Anastasio Graf von Volta, 1745–1827).

Die potentielle Energie, die eine Ladung Q im Punkt P1 gegenüber dem Punkt

P2 besitzt, ist gegeben durch das Produkt aus der Spannung zwischen P1 und

P2 und der Ladung Q:

W12 = Q ⋅ U12

Folie 3-19

Elektrostatisches Feld

Elektrisches Feld geladener Platten

Wenn der Abstand der

Platten klein ist im Vergleich

zu den Abmessungen der

Platten, ist das elektrische

Feld, wie in b) skizziert,

nahezu homogen, d.h. die

elektrische Feldstärke ist in

Betrag und Richtung überall

gleich. Außerdem ist das

Streufeld am Rande der Platten und im Außenraum vernachlässigbar klein.

gegeben:

A = Innenfläche einer Platte

Q = Ladung auf einer Platte

gesucht:

E = Feldstärke (Betrag des

homogenen elektrischen Feldes)

Folie 3-20

Elektrostatisches Feld

Elektrisches Feld geladener Platten

+

+ + + +

...

Die elektrische Feldstärke kann berechnet werden,

indem die Fläche der ebenen Platte als kleiner

Ausschnitt der Oberfläche einer sehr großen Kugel

(Radius r

∞) aufgefasst wird.

+

+

+

+

+

+

+

Plattenfläche A

+

Das Feld außerhalb einer Kugel mit gleichmäßig

auf A: Ladung Q

+

über die Oberfläche verteilter Ladung ist das

+

gleiche, als wäre die gesamte Ladung im

+

Mittelpunkt der Kugel konzentriert (Punktladung!).

+

Die äquivalente Mittelpunktladung ist:

+

+

2

...

Kugeloberfläche

4π r

QKugel = Q ⋅

es folgt:

A

= Q⋅

A

1 QKugel

1 Q ⋅ 4π r 2 1 Q

E=

=

=

2

2

4πε 0 r

4πε 0 A ⋅ r

ε0 A

Folie 3-21

Elektrostatisches Feld

Spannung zwischen geladenen Platten

Da das Feld homogen ist, berechnet sich die Spannung zu:

r r d

∫ E ⋅ ds = ∫ Edx = Ed

rechte Platte

U=

linke Platte

Mit

1 Q

E=

ε0 A

0

ergibt sich

1 d

U=

Q

ε0 A

Die Spannung U ist also nur von den geometrischen Abmessungen (Fläche A

und Plattenabstand d) sowie der Ladung Q abhängig.

Folie 3-22

Elektrostatisches Feld

Influenz

In das homogene Feld zwischen den beiden

Platten bringen wir einen aus zwei dünnen

leitenden Scheiben bestehenden ungeladenen

Körper.

Auf die Ladungsträger in den Scheiben werden

infolge des elektrischen Feldes Kräfte ausgeübt.

Die freien Elektronen werden zur positiven

Platte hin angezogen, auf der gegenüberliegenden Seite entsteht ein entsprechender

Elektronenmangel. Man spricht von

influenzierten Ladungen.

(Nachweisbar durch getrenntes Herausnehmen

der Scheiben und Messung der Ladungen).

Das elektrische Feld der influenzierten Ladungen kompensiert das äußere

Feld im Innern des Leiters. Der Leiter ist im Innern feldfrei.

Folie 3-23

Elektrostatisches Feld

Nichtleitende Materie im elektrischen Feld

Bringt man ein nichtleitendes homogenes Material (ein Dielektrikum) in ein

elektrisches Feld ein, so wird die elektrische Feldstärke geschwächt.

Im Versuch mit den geladenen Platten sinkt bei gleichbleibender Ladung die

Spannung zwischen den Platten ab.

Vakuum

Nichtleiter

Leiter

Folie 3-24

Elektrostatisches Feld

Dielektrische Polarisation

Die Ursache für dieses Verhalten liegt im inneren Aufbau des isolierenden

Materials. Im Gegensatz zu einem Leiter sind die Elektronen zwar nicht frei

beweglich, dennoch tritt eine Ladungsverschiebung innerhalb der atomaren

Strukturen auf. Infolge des von außen angelegten elektrischen Feldes wirken

Kräfte auf die Ladungsträger, die dazu führen, dass Atome bzw. Moleküle in

der einen Richtung negativ und in der entgegengesetzten Richtung positiv

polarisiert werden.

Die Ursachen für die Polarisation sind vielfältig.

Ein Beispiel: Verschiebungspolarisation, Elektronenpolarisation

Folie 3-25

Elektrostatisches Feld

Nichtleitende Materie im elektrischen Feld

1 Q

E=

ε0 A

im Vakuum

1 Q

E=

,εr > 1

ε 0ε r A

im Dielektrikum

E=0

im Leiter

Folie 3-26

Elektrostatisches Feld

Dielektrizitätszahl

Stoff

r

für verschiedene Materialien

r

Stoff

r

Trockene Luft

1,000594

Polyäthylen

2,3

Bariumtitanat

1000 ... 4000

Polystyrol

2,3 ... 2,7

Bernstein

2,8

Porzellan

6,0 ... 8,0

Gummi

2,6

Quarz

3,5 ... 4,5

Hartpapier

5,0 ... 6,0

Quarzglas

4

Papier

1,2 ... 3,0

Destilliertes Wasser

81

Folie 3-27

Elektrostatisches Feld

Kapazität

Wir haben bereits beim Plattenkondensator gesehen, dass die elektrische

Spannung U zwischen den Platten der gespeicherten Ladung ±Q

proportional ist. Diese Proportionalität gilt unabhängig von der Geometrie

der Anordnung.

Q~U

Q = CU

Unter der Kapazität C versteht man das Verhältnis aus der aufgenommenen

Ladung Q zu der angelegten Spannung U. Sie ist ein Maß für die Fähigkeit

eines Körpers, Ladungen zu speichern.

Die Einheit der Kapazität ist das Farad: 1 F = 1 As/V = 1 C/V.

(Nach Michael Faraday, 1791-1867).

Kondensatoren sind Bauelemente zur Ladungsspeicherung mit definierter

Kapazität C.

Schaltsymbol des Kondensators:

Folie 3-28

Elektrostatisches Feld

Kapazität des Plattenkondensators

U=

1 d

Q

ε 0ε r A

A⎞

⎛

Q = ⎜ ε 0ε r ⎟U

d⎠

⎝

Die Kapazität des Plattenkondensators berechnet

sich zu

A

A

C = ε 0ε r = ε

d

d

Die Kapazität des (idealen) Plattenkondensators hängt also nur von der

Fläche der Platten, dem Abstand der Platten und von den Materialeigenschaften ab, nicht aber von der auf den Platten befindlichen

Ladung.

Folie 3-29

Elektrostatisches Feld

Parallelschaltung von Kondensatoren

Alle oberen und alle unteren Kondensatorplatten liegen jeweils auf gleichem

Potential, d.h., die Spannung U ist für alle Kondensatoren gleich. Für den

Gesamtkondensator (Ersatzschaltbild) muss Qges = CgesU gelten.

n

n

n

k =1

k =1

k =1

Qges = ∑ Qk = ∑ CkU = U ∑ Ck = U Cges

n

Cges = ∑ Ck

k =1

Folie 3-30

Elektrostatisches Feld

Reihenschaltung von Kondensatoren

Die gesamte an den Eingangsanschlüssen vorhandene Spannung

(Potentialdifferenz) Uges setzt sich als Summe der Teilspannungen über den

einzelnen Kondensatoren zusammen. Bringt man auf die beiden äußeren, mit

den Anschlussklemmen verbundenen, Platten eine Ladung ±Q, dann werden

auf allen inneren Kondensatoren ebenfalls Ladungen ±Q influenziert.

n

Q

1

1

= ∑U k = ∑

= Q∑

=Q

Cges

k =1 Ck

k =1 Ck

k =1

n

U ges

n

n

1

1

=∑

Cges k =1 Ck

Folie 3-31

Elektrostatisches Feld

Praktische Ausführungsformen von Kondensatoren

Vielschichtkondensator

Die Schichten wirken wie eine Parallelschaltung von Kondensatoren.

Besteht jeder Kondensatoranschluss aus n Platten, dann sind 2n-1

Kondensatoren parallel geschaltet.

Folie 3-32

Elektrostatisches Feld

(Praktische Ausführungsformen von Kondensatoren)

Drehkondensator

In Abhängigkeit von der

Rotorposition ändert sich

die überdeckte Fläche und

damit auch die Kapazität.

Wickelkondensator

Zwei Metallfolien,

dazwischen zwei Kunststofffolien. Durch das Aufwickeln

tragen beide Seiten der

Metallfolie zur Kapazität bei.

Folie 3-33

Elektrostatisches Feld

Im Kondensator gespeicherte Energie

Die in einem Kondensator gespeicherte elektrische Energie ist proportional

zum Produkt aus der Kapazität C und dem Quadrat der angelegten

Spannung U.

1

1

2

We = CU = QU

2

2

Diese Beziehung ist unabhängig von der speziellen Geometrie des

Kondensators. (Alle geometrischen Einflüsse sind in der Kapazität C

berücksichtigt).

Bemerkung: W = Q ·U gilt nur, wenn die Spannung konstant ist. Wird

elektrische Arbeit verrichtet, sinkt die Spannung durch Entladung

(dies wird im folgenden Abschnitt behandelt).

Folie 3-34

Technische Informatik I

Prof. Dr. Martin Radetzki

Universität Stuttgart

Kapitel 4

Elektrischer Strom

und elektrische Netzwerke

Folie 4-1

Elektrischer Strom und elektrische Netzwerke

Elektrischer Strom

Elektrode 1

+Q

1

r

E

Elektrode 2

-Q

2<

1

Zwischen zwei Elektroden mit den Ladungen +Q und –Q besteht ein

elektrisches Feld. Die Elektrode 1 liegt auf dem Potential 1, die Elektrode 2

liegt auf dem Potential 2. Zwischen den Elektroden besteht demnach die

Spannung U12 = 1– 2.

Folie 4-2

Elektrischer Strom und elektrische Netzwerke

(Elektrischer Strom)

Elektrode 1

I

+Q

Verbindet man die Elektroden durch eine

leitende Verbindung, in der sich die

Elektronen frei bewegen können, so findet

ein Ladungsausgleich statt, und zwar

solange, bis zwischen den Elektroden keine

Spannung mehr vorhanden ist.

Elektrode 2

-Q

Die Bewegung der Ladungsträger bezeichnet man als elektrischen Strom.

Definition der Stromrichtung:

Ein positiver Strom fließt von der Elektrode höheren Potentials zur Elektrode

niedrigeren Potentials (technische Stromrichtung).

Die Elektronen bewegen sich entgegengesetzt zur technischen Stromrichtung!

Folie 4-3

Elektrischer Strom und elektrische Netzwerke

Elektrische Stromstärke

Die elektrische Stromstärke ist die Ladungsmenge Q, die in einer Zeitspanne

t durch die leitende Verbindung von der Elektrode 1 zur Elektrode 2 fließt.

ΔQ

I=

Δt

Die elektrische Stromstärke ist eine SI-Basiseinheit. Ihre Einheit ist das

Ampere (nach André Marie Ampère, 1775 – 1836).

SI-Basiseinheit der Stromstärke: [I] = A = Ampere

Wenn die Stromstärke zeitlich nicht konstant ist, dann gibt obige Beziehung

lediglich die mittlere Stromstärke während des Zeitabschnittes t an. Die

momentane Stromstärke zu einem Zeitpunkt t erhält man als

Δ Q dQ

=

I (t ) = lim

Δt →0 Δt

dt

Folie 4-4

Elektrischer Strom und elektrische Netzwerke

Ladungsträgerbewegung im Leiter

Bei Metallen sind die Elektronen auf der äußersten Schale nur sehr schwach

gebunden. Sie können sich quasi frei innerhalb des Atomverbandes bewegen.

Ohne äußere Einflüsse bewegen sich die Atome ungeordnet mit gleicher

Wahrscheinlichkeit in alle Richtungen. Der Mittelwert über alle Bewegungen

ist Null, das heißt, ein elektrischer Strom ist nicht feststellbar.

Folie 4-5

Elektrischer Strom und elektrische Netzwerke

(Ladungsträgerbewegung im Leiter)

In einem elektrischen Feld

erfahren die Elektronen

eine Kraft und damit eine

permanente Beschleunigung entgegengesetzt zum

Feldstärkevektor. Ihre

Bewegung wird immer

wieder durch Stöße mit den

ortsfesten Atomen und an

den Unregelmäßigkeiten im

Gitteraufbau unterbrochen.

An den Stoßstellen werden die Elektronen gestreut, d.h., sie werden

abgebremst und ändern ihre Richtung, wobei sie kinetische Energie verlieren.

Im Mittel erlangen sie aber durch das elektrische Feld eine mittlere

r

Driftgeschwindigkeit:

r

v e = − μe E µe: Beweglichkeit der Elektronen

Folie 4-6

Elektrischer Strom und elektrische Netzwerke

Stromdichte

Wir betrachten einen Ausschnitt

aus einem stromführenden Leiter.

Der Leiterquerschnitt habe die

Fläche A. Im Leiter befinden

sich positive Ladungsträger mit

einer Driftgeschwindigkeit vx in xRichtung.

Die Stromdichte J gibt den Strom bezogen auf die

durchströmte Fläche an. Sie hat die Einheit A/m2:

Die Raumladungsdichte gibt die pro Volumenelement zum Ladungstransport zur Verfügung stehende

Ladung an. Sie hat die Einheit As/m3.

J=

ΔQ

ΔI

ΔQ Δx

=

=

⋅

= ρ v , vektoriell:

ΔA ΔAΔt ΔAΔx Δt

ΔI

J=

ΔA

ΔQ

ρ=

ΔV

r

r

J = ρv

Folie 4-7

Elektrischer Strom und elektrische Netzwerke

Ohm'sches Gesetz in differentieller Form

Bezeichnen wir mit n die Anzahl der freien Ladungsträger pro Volumen

(Ladungsträgerkonzentration), dann lässt sich die zum Ladungstransport

zur Verfügung stehende Raumladungsdichte ausdrücken als

ρ = − en

r

r

r

r

Mit v e = − μe E und J = ρ v ergibt sich für die Stromdichte:

r

r

r

J = neμe E = κ E

Die Größe heißt

spezifische Leitfähigkeit

und hat die Einheit

[

J ] A/m

[κ ] = =

[E ] V/m

1

=

m

ACHTUNG:

und

2

ρR =

R

1

κ

Ohm'sches Gesetz in

differentieller Form

Der Kehrwert von heißt

spezifischer Widerstand

und hat die Einheit

[ρ ] = [E ] = V/m2

[J ] A/m

= m

sind grundverschiedene Größen!

Folie 4-8

R

Elektrischer Strom und elektrische Netzwerke

Temperaturabhängigkeit des spezifischen Widerstands

Der spezifische Widerstand ist im Allgemeinen temperaturabhängig. Für die

meisten technischen Anwendungen kann man die Temperaturabhängigkeit

durch eine lineare Näherung hinreichend genau beschreiben.

ρ R (T ) = ρ R (20°C) ⋅ [1 + α (T − 20°C)]

kurz:

ρ R (T ) = ρ R (20°C) ⋅ [1 + α ΔT ]

Ursache für die Temperaturabhängigkeit:

Bei höherer Temperatur schwingen die Atome im Gitter stärker; die Wahrscheinlichkeit, dass Elektronen mit Atomen zusammenstoßen, steigt. Daher ist

bei allen reinen Metallen der Temperaturkoeffizient positiv und liegt in etwa

derselben Größenordnung. Bei Legierungen dominiert der Effekt, dass Elektronen am unregelmäßigen Gitteraufbau gestreut werden. Der spezifische Widerstand von Legierungen ist daher grundsätzlich größer. Die Bewegungen der

Gitteratome spielen bei Legierungen für die Streuung der Elektronen kaum eine

Rolle, so dass der Temperaturkoeffizient deutlich geringer ist.

Folie 4-9

Elektrischer Strom und elektrische Netzwerke

Leitfähigkeit, Widerstand und Temperaturkoeffizient

verschiedener Materialien bei 20°C

Leiter

Aluminium

Chromnickel

· m-1 mm2

35

0,91

R

·m

-1mm-2

· 103 K

0,0287

3,8

1,1

0,2

Eisen

10

0,10

6,1

Gold

44

0,022

3,9

Graphit

0,125

8

-0,2

Konstantan*)

2

0,5

0,0035

Manganin*)

2,3

0,43

0,02

Kupfer

56

0,0178

3,9

Messing

12,5

0,08

1,5

Silber

62,5

0,016

3,8

Wolfram

18

0,055

4,1

*) Konstantan:

Manganin:

Legierung aus 54% Cu, 45%Ni, 1% Mn

Legierung aus 84% Cu, 4% Ni, 12% Mn

Folie 4-10

Elektrischer Strom und elektrische Netzwerke

Strom und Spannung an einem stromdurchflossenen Leiter

r r

E, J

Für die Spannung gilt:

r r

U = ϕ 1 − ϕ 2 = ∫ E ds = E ⋅ l

U

Mit

I

E = J = ρR J = ρR

κ

A

1

l

U = ρR I

A

ergibt sich

Ohm'sches Gesetz in

integraler Form!

l

R = ρR

A

Folie 4-11

Elektrischer Strom und elektrische Netzwerke

Ohm'sches Gesetz in integraler Form

Das Ohm'sche Gesetz (nach Georg Simon Ohm, 1789 – 1854) beschreibt eine

empirische Erfahrung:

Die an einem Leiter anliegende Spannung ist der durch den Leiter fließenden

Stromstärke proportional.

U

U = R⋅I

R

I

(Schaltsymbol eines el. Widerstandes)

Der Proportionalitätsfaktor R heißt elektrischer Widerstand.

Er hat die Einheit [R] = V/A = = Ohm.

In vielen Fällen bietet es sich an, dass man nicht den

Widerstand, sondern seinen Kehrwert G = 1/R verwendet.

G heißt elektrischer Leitwert und besitzt die Einheit 1/

= A/V.

1

G=

R

Folie 4-12

Elektrischer Strom und elektrische Netzwerke

(Ohm'sches Gesetz in integraler Form)

Temperaturabhängigkeit des elektrischen Widerstands:

R(T ) = ρ R ( 20°C) ⋅

l

⋅ [1 + α (T − 20°C)]

A

R(T ) = R( 20°C) ⋅ [1 + α (T − 20°C)]

Bsp.:

Ein Kupferdraht habe bei 20°C

einen Widerstand von 1 . Wie

groß ist sein Widerstand bei

100°C?

1

⎡

⎤

R(100°C) = R( 20°C) ⋅ ⎢1 + 3,9 3 ⋅ 80K ⎥ ≈ 1,31Ω

10 K

⎣

⎦

Folie 4-13

Elektrischer Strom und elektrische Netzwerke

Leistung des elektrischen Stroms

Beim Transport von Ladung durch einen Leiter infolge eines elektrischen

Feldes wird an den Ladungsträgern Arbeit verrichtet. Diese Energie wird dem

Energieinhalt des elektrischen Feldes entnommen und im Leiter als

Wärmeenergie umgesetzt.

Die Leistung gibt die verrichtete Arbeit pro

Zeiteinheit an.

Sie hat die Einheit [P] = VA = Watt (W)

(nach James Watt, 1736 – 1819).

ΔW dW

=

P(t ) = lim

Δt →0 Δt

dt

Für einen elektrischen Widerstand R gilt:

U

1

R

I

2<

1

2

U

P = UI = I 2 R =

R

Folie 4-14

Elektrischer Strom und elektrische Netzwerke

Festwiderstände - Bauformen

Folie 4-15

Elektrischer Strom und elektrische Netzwerke

Weitere Widerstandsformen

Einstellbare Widerstände (Potentiometer):

Ein Schleifkontakt wird über das nicht isolierte Widerstandsmaterial

bewegt, und damit ein bestimmter Bruchteil des insgesamt möglichen

Widerstands abgegriffen.

Bauformen:

• Schiebewiderstand (linear angeordneter Widerstandskörper)

• Drehwiderstand (ringförmig angeordneter Widerstandskörper)

Temperaturabhängige Widerstände

• NTC (negative temperature coefficient), oder Heißleiter: er hat bei

Raumtemperatur einen hohen Widerstand, im Betrieb erhitzt er sich und

hat einen niedrigen Widerstand. (Verwendung beispielsweise zur

Begrenzung von Einschaltströmen).

• PTC (positive temperature coefficient), oder Kaltleiter:

Temperaturverhalten genau umgekehrt wie beim NTC.

Folie 4-16

Elektrischer Strom und elektrische Netzwerke

Elektrische Netzwerke

Zur Beschreibung elektronischer Schaltungen verwendet man elektrische

Netzwerke. Man verwendet für die elektronischen Bauelemente einfache

Modelle (Ersatzschaltbilder), in denen das Verhalten der realen Bauelemente

durch integrale Größen wie z. B. Widerstand R und Kapazität C modelliert

werden.

Ein zentraler Begriff bei der Behandlung von Netzwerken ist der des

Zweipols. Unter einem Zweipol versteht man ein Bauelement mit zwei

Anschlussklemmen. Aus Sicht des Netzwerkes spielt nur noch das

Klemmenverhalten (d. h. der Zusammenhang zwischen Strom und

Spannung) am betreffenden Bauelement eine Rolle.

Zur vollständigen Beschreibung eines elektrischen Netzwerkes (Schaltkreis)

kommt zum Klemmenverhalten der einzelnen Bauelemente auch ihre

Verknüpfung hinzu (Schaltungstopologie).

Folie 4-17

Elektrischer Strom und elektrische Netzwerke

Schaltbilder

Die grafische Darstellung von Netzwerken bezeichnet man als Schaltbilder.

Zur Darstellung der Bauelemente werden Schaltsymbole verwendet. Die

leitenden Verbindungen zwischen den Bauelementen werden als ideale, d.h.

widerstandslose, Leiter angesehen und spielen bei der Rechnung keine Rolle.

Kreuzen sich Verbindungslinien, so

gelten sie nur als verbunden, wenn dies

durch einen Punkt ("Lötpunkt")

markiert ist. Diese Verbindungspunkte

heißen Knoten des Netzwerkes. Die

Bauelemente zwischen den Knoten

stellen zusammen mit ihren leitenden

Verbindungen Zweige des Netzwerks

dar.

Folie 4-18

Elektrischer Strom und elektrische Netzwerke

Zählpfeile

Strom und Spannung sind skalare Größen. Dennoch werden ihnen in

Schaltungen Pfeile zugeordnet. Diese Pfeile dienen der Zählweise und dürfen

nicht mit Vektoren verwechselt werden.

Ein Spannungspfeil in Richtung der elektrischen Feldstärke zeigt positive

Spannungen an. Er zeigt von einem Punkt höheren Potentials zu einem Punkt

niedrigeren Potentials.

Ein Strompfeil in Bewegungsrichtung der positiven Ladungsträger zeigt

positive Ströme an. Er wird in die Verbindungslinie eingezeichnet, die den

Strom führt.

U

1

R

I

2

<

1

für U > 0

Folie 4-19

Elektrischer Strom und elektrische Netzwerke

Spannungs- und Stromquellen

Ein Kondensator produziert nur solange einen Strom, bis seine gesamte

Ladung abgeflossen ist. Als Gleichstromquelle ist er nicht geeignet.

Eine Gleichstromquelle muss die von den Platten abfließenden Ladungen

immer wieder nachliefern.

Folie 4-20

Elektrischer Strom und elektrische Netzwerke

Ideale Spannungs- und Stromquellen

I

U

Gleichspannung

i(t)

u(t)

Gleichstrom

zeitlich veränderliche Spannung

zeitlich veränderlicher Strom

Bei einer idealen Spannungsquelle hängt die Ausgangsspannung nicht vom

angeschlossenen Netzwerk ab, (sondern nur der gelieferte Strom).

Bei einer idealen Stromquelle hängt der Ausgangsstrom nicht vom

angeschlossenen Netzwerk ab, (sondern nur die gelieferte Spannung).

Folie 4-21

Elektrischer Strom und elektrische Netzwerke

Zählpfeilsysteme

An Verbrauchern werden Strom und Spannung in der gleichen Richtung

gezählt (Verbraucherzählpfeilsystem).

An Spannungs- und Stromquellen sind Spannung und Strom entgegengesetzt

gerichtet (Generatorzählpfeilsystem).

Hintergrund: Quellen liefern Energie, Verbraucher nehmen sie auf.

Folie 4-22

Elektrischer Strom und elektrische Netzwerke

Netzwerkanalyse

Ziel der Netzwerkanalyse ist die Berechnung aller Ströme und Spannungen

an den einzelnen Bauelementen.

Bsp.: Wie groß sind die Spannungen an den Widerständen R1 bis R5 und wie

groß sind die Ströme durch die Widerstände? Wie groß ist der Strom, den die

Gleichspannungsquelle liefert?

Das Ohm'sche Gesetz alleine reicht für die Beantwortung dieser Fragen nicht

aus.

Folie 4-23

Elektrischer Strom und elektrische Netzwerke

Kirchhoff'sche Gleichungen

Maschenregel

r r

∫ E ⋅ ds = 0

⇒ U R1 + U R 3 − U R 4 = 0

∑U = 0

Masche

Die Summe aller Spannungen beim Umlauf in einer

geschlossenen Masche ist Null.

Spannungen, deren Zählpfeil dabei entgegen der

Umlaufrichtung verläuft, werden negativ gezählt.

Folie 4-24

Elektrischer Strom und elektrische Netzwerke

Kirchhoff'sche Gleichungen: Knotenregel

Knotenregel

Ein Schaltungsknoten

hat keine Kapazität.

Alle Ladung, die in ihn

hineinfließt, muss auch

wieder aus ihm

herausfließen.

⇒

I R1 − I R 3 − I R 5 = 0

∑I = 0

Knoten

Die Summe aller in einen Knoten hineinfließenden

Ströme ist Null.

Ströme, deren Zählrichtung vom Knoten wegzeigt,

werden dabei negativ gezählt.

Folie 4-25

Elektrischer Strom und elektrische Netzwerke

Reihenschaltung von Widerständen

Alle Widerstände werden vom selben Strom

durchflossen. Anwendung der Maschenregel

liefert:

n

n

U ges = ∑U k =∑ Rk I = Rges I

k =1

k =1

n

Rges = ∑ Rk

k =1

n

1

1

=∑

Gges k =1 Gk

Folie 4-26

Elektrischer Strom und elektrische Netzwerke

Parallelschaltung von Widerständen

An allen Widerständen liegt dieselbe Spannung.

Anwendung der Knotenregel liefert:

n

I ges

n

U

U

= ∑ I k =∑

=

Rges

k =1

k =1 Rk

n

1

1

=∑

Rges k =1 Rk

n

Gges = ∑ Gk

k =1

Folie 4-27

Elektrischer Strom und elektrische Netzwerke

Spannungsteiler

Mit einer Reihenschaltung

von Widerständen kann man

eine gegebene Spannung U

mit hoher Genauigkeit in

kleinere Teilspannungen

aufteilen.

Es gilt:

U1 R1

=

U 2 R2

und

U2

R2

=

U

R1 + R2

Folie 4-28

Elektrischer Strom und elektrische Netzwerke

Spannungsabfall am Widerstand

Die an einem Widerstand entstehende Teilspannung wird als Spannungsabfall

bezeichnet.

Bsp.: Potentialverlauf an einer Reihenschaltung. Definiert man das

Bezugspotential = 0 für die rechte Klemme (Minuspol der Spannungsquelle),

dann besitzt die linke Klemme das Potential = U. Innerhalb der Widerstände

nimmt das Potential linear ab.

Folie 4-29

Elektrischer Strom und elektrische Netzwerke

Belasteter Spannungsteiler

Schließt man an den

Spannungsteiler einen

Verbraucher an, zum

Beispiel ein Spannungsmessgerät (Voltmeter), so

entspricht der gemessene

Wert nicht mehr dem oben

berechneten, d.h.

U2

R2

≠

U

R1 + R2

In die Berechnung muss noch der Widerstand des Verbrauchers (hier

der Innenwiderstand des Messgerätes) berücksichtigt werden.

Im Beispiel:

U2

R2 ⋅ RM

=

U

R1 (R2 + RM ) + R2 ⋅ RM

Folie 4-30

Elektrischer Strom und elektrische Netzwerke

(Belasteter Spannungsteiler)

U2

R2 ⋅ RM

=

U

R1 (R2 + RM ) + R2 ⋅ RM

Auswertung des Beispiels

für (R1+R2) = 10 k ,

0 ≤ R2 ≤ 10 k

und

verschiedene Werte von RM.

Man sieht: mit kleinerem Innenwiderstand RM geht die Linearität

zwischen der Potentiometerstellung und der Ausgangsspannung verloren.

Folie 4-31

Elektrischer Strom und elektrische Netzwerke

Stromteiler

Mit einer Parallelschaltung von

Widerständen kann ein

Gesamtstrom I in mehrere

Teilströme aufgeteilt werden.

Es gilt:

I1 R2 G1

=

=

I 2 R1 G2

und

I2

R1

G2

=

=

I

R1 + R2 G1 + G2

Folie 4-32

Elektrischer Strom und elektrische Netzwerke

Reale Spannungsquelle - Ersatzschaltbild

Wird eine reale Spannungsquelle durch

einen Verbraucher belastet, dann ruft

der Strom einen Spannungsabfall und

damit interne Verluste hervor. Man

modelliert dies durch einen mit der

Quellenspannung U0 in Reihe

liegenden Innenwiderstand Ri.

Man kann die Quelle vollständig

charakterisieren durch ihre Leerlaufspannung und ihren Kurzschlussstrom:

Leerlaufspannung:

U = UL = U0

Kurzschlussstrom:

IK = U0 / Ri

Im Kurzschlussbetrieb werden beide Klemmen leitend verbunden. Die

gesamte Leistung wird dann am Innenwiderstand umgesetzt!

Folie 4-33

Elektrischer Strom und elektrische Netzwerke

Reale Stromquelle - Ersatzschaltbild

Wird eine reale Stromquelle durch

einen Verbraucher belastet, dann ruft

die Spannung über dem Verbraucher

eine Reduzierung des Stroms und

damit interne Verluste hervor. Man

modelliert dies durch einen parallel

zum Quellenstrom I0 liegenden

Innenwiderstand Ri.

Man kann die Quelle vollständig

charakterisieren durch ihre Leerlaufspannung und ihren Kurzschlussstrom:

Leerlaufspannung:

UL = I0 Ri

Kurzschlussstrom:

I = IK = I0

Im Leerlaufbetrieb ist kein Verbraucher angeschlossen. Die gesamte

Leistung wird dann am Innenwiderstand umgesetzt!

Folie 4-34

Elektrischer Strom und elektrische Netzwerke

Äquivalente Quellen

Spannungs- und Stromquelle können ineinander umgerechnet werden. Dazu

muss sichergestellt werden, dass beide Quellen die gleiche Leerlaufspannung

und den gleichen Kurzschlussstrom aufweisen. Beide Forderungen sind

erfüllt, wenn für Quellenspannung und Quellenstrom gilt:

U0 = I0 Ri

Folie 4-35

Elektrischer Strom und elektrische Netzwerke

Überlagerungsprinzip

Enthält eine Schaltung mehrere Quellen, dann können die Ströme und

Spannungen in den einzelnen Zweigen durch Überlagerung von

Teillösungen berechnet werden. Voraussetzung: lineare Beziehungen

zwischen Strom und Spannung an den Netzwerkelementen.

Berechnung von Teillösungen:

• nur eine einzige Quelle wird betrachtet

• alle anderen Stromquellen werden durch Leerlauf ersetzt (I = 0)

• alle anderen Spannungsquellen werden durch Kurzschluss ersetzt (U = 0)

Berechnung der Gesamtlösung aus den Teillösungen:

• alle Teilströme eines Zweiges werden addiert

• alle Teilspannungen eines Zweiges werden addiert

Folie 4-36

Elektrischer Strom und elektrische Netzwerke

(Überlagerungsprinzip) Beispiel

Bsp.:

Wie groß ist der Strom I2 durch R2?

Folie 4-37

Elektrischer Strom und elektrische Netzwerke

(Überlagerungsprinzip Beispiel)

Teillösung a)

Setze I0 = 0,

d.h., ersetze die Stromquelle

durch Leerlauf.

U0

I 2a =

R1 + R2

Teillösung b)

Setze U0 = 0,

d.h., ersetze die Spannungsquelle

durch Kurzschluss.

R1 I 0

I 2b =

R1 + R2

Folie 4-38

Elektrischer Strom und elektrische Netzwerke

(Überlagerungsprinzip Beispiel)

Zusammengesetzte Gesamtlösung:

U 0 + R1 I 0

I 2 = I 2a + I 2b =

R1 + R2

Folie 4-39

Elektrischer Strom und elektrische Netzwerke

Aufladung eines Kondensators

R

t=0

i(t)

U0

u(t)

Für die Ladung q(t) am Kondensator gilt:

Mit

i (t ) =

Der Kondensator sei

zunächst ungeladen. Zum

Zeitpunkt t=0 werde der

Schalter geschlossen.

dq

dt

folgt daraus:

Anwendung der Maschenregel:

und damit die Differentialgleichung:

C

Gesucht:

Das zeitliche Verhalten der

Spannung u(t) und des

Stromes i(t) in der

gezeigten Schaltung.

q(t ) = Cu(t )

du

dt

Ri (t ) + u(t ) = U 0

i (t ) = C

du

RC

+ u(t ) = U 0

dt

Folie 4-40

Elektrischer Strom und elektrische Netzwerke

(Aufladung eines Kondensators)

du

+ u(t ) = U 0

dt

Lineare inhomogene Differentialgleichung:

RC

Zugehörige homogene Differentialgleichung:

du

RC

+ u (t ) = 0

dt

Lösungsansatz (z.B. durch Separation der Variablen):

u(t ) = K ⋅ e

−

t

RC

Dabei ist K eine aus den Randbedingungen

noch zu bestimmende Konstante.

Eine offensichtliche spezielle Lösung der inhomogenen

Differentialgleichung ist:

u(t ) = U 0

Damit ergeben sich alle Lösungen zu

u(t ) = K ⋅ e

−

t

RC

+ U0

Folie 4-41

Elektrischer Strom und elektrische Netzwerke

(Aufladung eines Kondensators)

Bestimmung der Konstanten K aus den Randbedingungen:

Zum Zeitpunkt t=0 wird der Schalter geschlossen. Der Kondensator soll zu

diesem Zeitpunkt noch ungeladen sein, d.h. u(0) = 0.

Einsetzen in u(t ) = K ⋅ e

−

t

RC

+ U0

ergibt K = – U0

Damit ergibt sich für die Spannung am Kondensator:

t

−

⎛

⎞

RC ⎟

⎜

u (t ) = U 0 ⎜1 − e ⎟

⎝

⎠

du

Für den Strom i(t) erhält man aus i (t ) = C

dt

t

U 0 − RC

U0

e

i (t ) =

Anfangsstrom: i (0) =

R

R

Folie 4-42

Elektrischer Strom und elektrische Netzwerke

(Aufladung eines Kondensators)

u(t)

U0

t

−

⎛

⎞

RC

u(t ) = U 0 ⎜⎜1 − e ⎟⎟

⎝

⎠

63% ·U0

U0

t

t

du U 0 − RC

=

e

dt RC

=RC

i(t)

U0

R

t

Die Zeitkonstante = RC ist ein Maß dafür, wie schnell die Kondensatorspannung ihren Endwert erreicht. Nach t = 1 erreicht sie ca. 63% ihres

Endwertes; nach t = 3 sind es bereits ca. 95%.

Folie 4-43

Technische Informatik I

Prof. Dr. Martin Radetzki

Universität Stuttgart

Kapitel 6

Halbleiterbauelemente

Folie 7-1

Halbleiterbauelemente

Mikroelektronik – 1970 bis heute

Keine andere Technologie macht eine so rasante Entwicklung durch wie die

Mikroelektronik – und das seit vielen Jahrzehnten!

Intel 1101 256-bit SRAM

Intel 4004 4-bit-Mikroprozessor

(1971, ca. 2500 Transistoren, ca.

100kHz, 30mm2, 4 Designer)

Folie 6-2

Halbleiterbauelemente

Prozessortechnologie 2007: Beispiel

2006: AMD Athlon-64-FX, ca. 3 000 000 kHz Taktfrequenz,

ca. 227 400 000 Transistoren, ca. 230 mm² Chipfläche.

Folie 6-3

Halbleiterbauelemente

Batch production

Auf einer Silizium-Scheibe (engl. wafer) kann eine Vielzahl von

Kopien einer Schaltung gleichzeitig hergestellt werden.

Folie 6-4

Halbleiterbauelemente

In 2003 überstieg die Zahl der jährlich produzierten Transistoren weltweit die

Marke von einer Trillion (1018) Transistoren. Damit werden im Schnitt für

jeden Menschen auf der Erde jährlich 100 Millionen Transistoren produziert.

Umsätze in der Mikroelektronik - global

(Milliarden US$)

200

150

100

50

0

1982

1984

1986

1988

1990

1992

1994

1996

1998

2000

2002

Jahr

Folie 6-5

Halbleiterbauelemente

Moore's Gesetz - Transistorzahlen

Die Anzahl der Transistoren pro CPU-Typ verdoppelt sich etwa alle 26 Monate.

Quelle: http://www.intel.com/technology/mooreslaw/

Folie 6-6

Halbleiterbauelemente

Moore's Gesetz - Taktfrequenzen

CPU-Taktfrequenzen verdoppeln sich ca. alle 34 Monate.

10,000

4004

1,000

8008

Taktfrequenz (MHz)

8080

8086

100

80286

Intel386

Intel486

10

Pentium

Pentium Pro/II/III

Pentium 4

1

1970

1975

1980

1985

1990

1995

2000

2005

Jahr

Die Transistoren werden kleiner; dadurch werden sie auch schneller,

verbrauchen weniger Energie und kosten weniger pro Stück.

Folie 6-7

Halbleiterbauelemente

Grade der Integration

Man klassifiziert integrierte Schaltungen nach dem Grad ihrer Integration,

d.h. nach der Größenordnung, in der sich die Anzahl ihrer Gatter bewegen.

Small Scale Integration

SSI

~ 10 Gatter

z.B. 7404 InverterBaustein

Medium Scale Integration

MSI

~ 1000 Gatter

z.B. 74161 ZählerBaustein

Large Scale Integration

LSI

~10.000 Gatter

z.B. einfacher 8-bitMikroprozessor

Very Large Scale

Integration

VLSI > 10.000 Gatter z.B. heutige

Prozessoren,

Systems-on-Chip

Folie 6-8

Halbleiterbauelemente

Leiter – Halbleiter - Nichtleiter

Leiter

Halbleiter

Nichtleiter (Isolatoren)

Wir betrachten im weiteren Verlauf das Element Silizium. Es ist

wirtschaftlich das bedeutendste Halbleitermaterial. Die physikalischen

Zusammenhänge sind mit nur geringen Modifikationen auf andere

Halbleitermaterialien übertragbar.

Folie 6-9

Halbleiterbauelemente

Modell des Siliziumatoms

Die erste Schale hat 2 Elektronen, die zweite 8 und die dritte ("Valenzschale")

hat 4 Elektronen (Valenzelektronen). Sie ist nicht vollständig aufgefüllt, da sie

bis zu 8 Elektronen aufnehmen kann.

Folie 6-10

Halbleiterbauelemente

Kovalente Bindung im Siliziumkristall

Jedes Siliziumatom teilt sich mit seinen vier Nachbarn je ein Elektron.

Folie 6-11

Halbleiterbauelemente

Diamantgitter

Die Struktur des Siliziumkristalls ist dieselbe wie beim Diamant (Kristall des

Kohlenstoffs). Größe der Einheitszelle (Seitenlänge): 5,43·10−10 m.

Anzahl der Atome pro Einheitszelle: 8.

Folie 6-12

Halbleiterbauelemente

Herstellung von Silizium-Wafern

Das Ausgangsmaterial für die IC-Prozesstechnologie ist monokristallines Silizium in

hoher Reinheit. Es wird mit der sogenannten

Czochralski-Methode hergestellt. Dazu wird

ein Impfkristall (engl. seed crystal) in geschmolzenes Silizium abgesenkt. Beim Herausziehen aus der Schmelze lagern sich Siliziumatome an. Es wächst ein Kristall, dessen

Gitterstruktur durch die des Impfkristalls vorgegeben ist.

Das Ziehen des Kristalls geschieht unter

Rotation. Dadurch entstehen zylinderförmige

Kristalle, die in Scheiben, sogenannte Wafer,

gesägt werden.

Folie 6-13

Halbleiterbauelemente

Energieniveaus am Beispiel des Wasserstoffatoms

n=3

–1,51eV

EH / eV

0 eV

n=∞

n=3

n=2

n=1

–13,6eV

–5 eV

n=2

–3,4eV

–10 eV