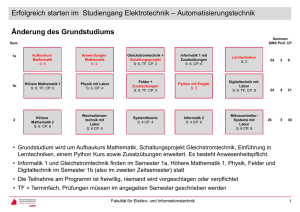

Digitaltechnik II SS 2007

Werbung

Digitaltechnik II SS 2007 7. Vorlesung Klaus Kasper Inhalt • Register • Halbleiterspeicher – Random Access Memory (RAM) – SRAM – DRAM – ROM – Programmierbare ROM • Realisierung digitaler Systeme Digitaltechnik 2 2 Hinweis! A B C AJ AK BJ BK CJ CK 0 0 0 1 = 1 = 1 = 1 1 1 - 0 = 1 - 0 1 0 1 - 0 1 = = 1 1 1 0 = 1 = 1 1 = 0 0 1 0 - 1 = = 1 0 1 0 0 - = 1 0 - 0 0 0 AJ C 1 0 − B 0 * * − = A Digitaltechnik 2 3 Register • Parallele Anordnung von Flip-Flops mit gemeinsamen Takt. • Auffang- oder Buffer-Register zur Zwischenspeicherung von Bitfolgen. • Schiebe- oder Shift-Register zur Parallel-Seriell-Umwandlung oder für binäre Multiplizierer / Dividierer Digitaltechnik 2 4 Digitaltechnik 2 5 Schieberegister Für X=1 werden die Daten parallel eingelesen und seriell ausgelesen (PISO). Für X=0 wird ein SISO realisiert. Digitaltechnik 2 6 Halbleiterspeicher Halbleiterspeicher Festwertspeicher (Nur-Lese-Speicher) Flüchtige Speicher (Lese-Schreib-Speicher) Einmal beschreibbar Mehrfach beschreibbar Dynamisch Statisch ROM EPROM erasable DRAM SRAM PROM programmable EEPROM electrical SDRAM Synchronous Flash ROM DDR-RAM Double Data Rate RDRAM Rambus Digitaltechnik 2 7 Random Access Memory (RAM) • Speicher mit wahlfreiem Zugriff. • Zeitaufwand für Lese- und Schreibvorgang ist in etwa gleich groß. • Speicherzelle wird mit Hilfe einer Adresse gewählt und Information eingeschrieben. • Zum Auslesen wird die Speicherzelle ebenfalls über eine Adresse ausgewählt und die Information gelesen. • Hierbei wird die Information nicht gelöscht. Digitaltechnik 2 8 Statische RAM (SRAM) • Für statische RAM werden die Speicherzellen mit Flip-Flops realisiert. • Solange die Versorgungsspannung anliegt, bleibt die Information im SRAM erhalten. • Sehr kurze Schreib- und Lesezeiten. • Relativ große Fläche zur Realisierung einer Speicherzelle. • Es werden 6 Transistoren für die Realisierung eines Flip-Flop benötigt. • SRAM werden häufig für die Realisierung von Cache eingesetzt. Digitaltechnik 2 9 Auffangregister (PIPO) 4 bit werden parallel gespeichert und können parallel gelesen werden Mit dem Reset Eingang (R) können alle Ausgänge auf 0 gesetzt werden Digitaltechnik 2 10 Dynamische RAM (DRAM) • Elementares Speicherelement ist eine Kapazität. Prinzip wurde 1966 von IBM entwickelt. Erstes Produkt 1970 von Intel (1 kbit). • Sehr hohe Speicherdichte (ca.10-fach im Vergleich zu SRAM). • Beim Schreiben wird ein adäquater Spannungspegel an der Kapazität realisiert (1 entspricht einer geladenen und 0 einer entladenen Kapazität). Digitaltechnik 2 11 • Beim Lesen wird der Pegel abgefragt. DRAM (Forts.) • Beim Lesen einer Zelle wird die gespeicherte Information zerstört, muss also anschließend wieder eingeschrieben werden. • In den Schaltungen existieren ständig Leckströme. • Auch sehr kleine Leckströme führen zu einem Verlust der Information, da die Kapazitäten sehr klein sind (0.1 … 1pF). • Zur Erhaltung der Information muss diese in regelmäßigen Abständen (ca. 2–16ms) Zeilenweise ausgelesen und direkt wieder geschrieben werden (Refresh). • Während des Refresh kann auf den Inhalt des DRAM nicht zugegriffen werden. Digitaltechnik 2 12 Prinzip einer DRAM Speicherzelle Digitaltechnik 2 13 Beispiel: Refresh DRAM • • • • 1 M bit DRAM, 512 Zeilen 512 Refresh-Zyklen alle 8 ms Zykluszeit für den Refresh: 0.2 µs Zeitbedarf Refresh: 512*0.2 µs = 0,1024 ms ca. 1.3% der Betriebszeit für Refresh Digitaltechnik 2 14 Prinzip SRAM Digitaltechnik 2 15 Tri-State-Gatter Tri-State- Gatter können neben den beiden logischen Ausgangspegeln Low und High einen dritten hochohmigen Zustand annehmen. Digitaltechnik 2 16 Architektur SRAM Digitaltechnik 2 17 Speichermatrix Digitaltechnik 2 18 Aufbau eines RAM A: Adresseingänge, CS: Chip Select, WE: Write Enable Dout: Datenausgang, Din: Dateneingang Digitaltechnik 2 19 Symbolische Darstellung eines RAM Digitaltechnik 2 20 DRAM Typen • SDRAM (Synchronous Dynamic RAM) wird mit einem Taktgeber synchronisiert, der vom CPU-Takt abgeleitet ist. Alle Schreib- und Lesevorgänge werden von der steigenden Flanke dieses Taktes ausgelöst. • DDR-SDRAM (Double Data Rate) ist eine Variante des SDRAM mit doppelter Datenübertragungsrate. Die Daten werden mit der steigenden und der fallenden Taktflanke gelesen oder geschrieben. Die angeforderten oder zu speichernden Daten müssen immer mindestens der doppelten Busbreite entsprechen (2-fach Prefetch). • RDRAM ist eine spezielle Entwicklung der Firma Rambus. Daten werden aus vielen Bänken parallel gelesen und dann über einen Multiplexer auf den Datenausgang schaltet. Z.B. können aus 8 Bänken gleichzeitig 8 Byte gelesen werden. Das entspricht dann der 8-fachen internen Lesegeschwindigkeit. Digitaltechnik 2 21 Aktuelle Entwicklung Digitaltechnik 2 22 DDR2-RAM • • • • Double Data Rate Verfahren wird weiter genutzt verringerte Betriebsspannung: 1,8 V (2,5V) nicht Pin-kompatibel: 240 (184) Pins intern wird mit verringerter Taktfrequenz gearbeitet (prefetch 4-fach, bzw. 8-fach bei DDR3) • interne Datenbreite wurde erweitert • 2007: DDR3 (GDDR3 schon verfügbar) höhere Datentübertragungsraten günstigere Produktion Digitaltechnik 2 23 DDR vs. DDR2 Speichertyp Speichertakt Bezeichnung Bandbreite SDRAM 133 MHz PC133 1,1 GB/s DDR266 133 MHz PC2100 2,1 GB/s DDR400 200 MHz PC3200 3,2 GB/s DDR2-400 100 MHz PC2-3200 3,2 GB/s DDR2-533 133 MHz PC2-4300 4,3 GB/s DDR2-1066 266 MHz PC2-8500 8,5 GB/s DDR3-1066 133 MHz PC3-8500 8,5 GB/s DDR3-1600 200 MHz PC3-12800 12,8 GB/s PC3200: 200 MHz ∗ 8 Byte ∗ 2 Zugriffe/Takt = 3200 MByte/s Digitaltechnik 2 24 RAM Kenngrößen • Speicherkapazität: Anzahl der speicherbaren Bit. • Zugriffszeit: Zeit zwischen Adressierung eines Speicherelementes bis zur Verfügbarkeit am Ausgang. • Zykluszeit: kürzeste Zeit zwischen zwei Schreib-Lese-Vorgängen. • Leistungsbedarf: Gesamtleistungsbedarf der integrierten Schaltung. Digitaltechnik 2 25 Neue nichtflüchtige Speicher • MRAM (Magnetoresestive RAM): Speicherung erfolgt über zwei Magnetplättchen, aktuell aussichtsreichster Kandidat für die Nachfolge DRAMs • F(e)RAM (Ferro Electric): ferroelektrisches Prinzip, Information wird mit Kondensatoren gespeichert Digitaltechnik 2 26 Festwertspeicher (ROM) • Auf einen typischen ROM wird während des Betriebs ausschließlich lesend zugegriffen. • Die Programmierung (Schreiben) eines ROM ist deutlich aufwändiger als der Lesezugriff. • Der Aufbau eines ROM entspricht hinsichtlich der Matrixanordnung der Speicherzellen und der Adressverwaltung dem Aufbau eines RAM. Digitaltechnik 2 27 Maskenprogrammierte ROM • Für große Stückzahlen werden bei der Herstellung der Speicher die Information fest eingegeben. • Die zu speichernde Information wird mittels einer Metallisierungsmaske eingebracht. • Beispiel: Haushaltsgeräte Digitaltechnik 2 28 Programmierbare ROM (PROM) • Mit speziellen Programmiergeräten können PROM vom Anwender programmiert werden. • Die Programmierung erfolgt durch die Herstellung von Verbindungen (AntiFuse) oder durch die Trennung von Verbindungen (Fuse). • Die Programmierung ist irreversibel. Digitaltechnik 2 29 UV-löschbares PROM (EPROM) • EPROMS können mit speziellen Geräten programmiert und gelöscht werden. • Für die Programmierung wird eine Spannung von ca. 20 Volt benötigt. • Bei der Programmierung werden mit Hilfe des Avalanche-Effektes (Lawineneffektes) elektrische Ladungen injiziert. • Für die Löschung wird entsprechend energiereiches Licht benötigt. • Die Löschung dauert einige Minuten. • Der Baustein muss i.a. zur Löschung aus der Schaltung entfernt werden. Digitaltechnik 2 30 Elektrisch lösch- und programmierbare ROM (EEPROM) • Der Baustein kann für den Löschvorgang in der Schaltung verbleiben. • Für den Löschvorgang wird eine Spannung von ca. 20 Volt benötigt. • Für Programmierung und Löschung wird der Tunneleffekt ausgenutzt. • Jedem Schreibvorgang wird ein Löschvorgang vorgeschaltet. • Der Schreibvorgang für ein Byte benötigt ca. 10 ms. • Anzahl von Lösch-/Schreibzyklen: ca. 10000 • Speicherdauer: mindestens 10 Jahre Digitaltechnik 2 31 Floating-Gate-Technologie für EEPROM-Speichertransistor Digitaltechnik 2 32 Flash-Speicher • Weiterentwicklung der EEPROMs. • Im Fall des Flash-Speichers wir im Unterschied zu EEPROMS der Speicher blockweise (!) gelöscht. • In ersten Realisierungen wurde der Speicher mit einem Flash (Blitz) vollständig gelöscht. • Ein Block umfasst ca. 0,5 KB – 128 KB. • Der direkte Zugriff auf einzelne Bytes ist prinzipiell nicht möglich. Dies entspricht dem Prinzip von Massenspeichern, die eine typische Blockgröße von 512 Byte haben. • Moderne Typen kommen mit 5 Volt als Programmier- und Löschspannung aus. Digitaltechnik 2 33