Dokument_1. - MOnAMi

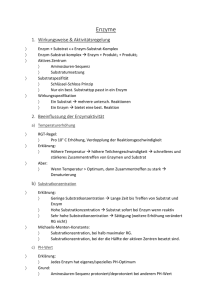

Werbung