Feldeffekt-Transistoren

Werbung

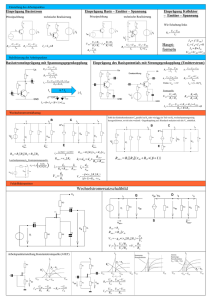

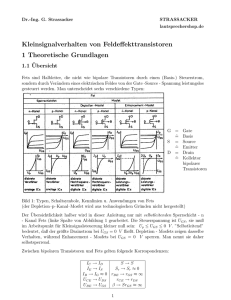

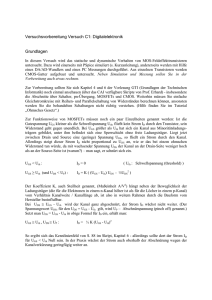

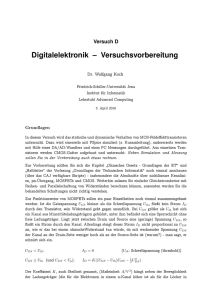

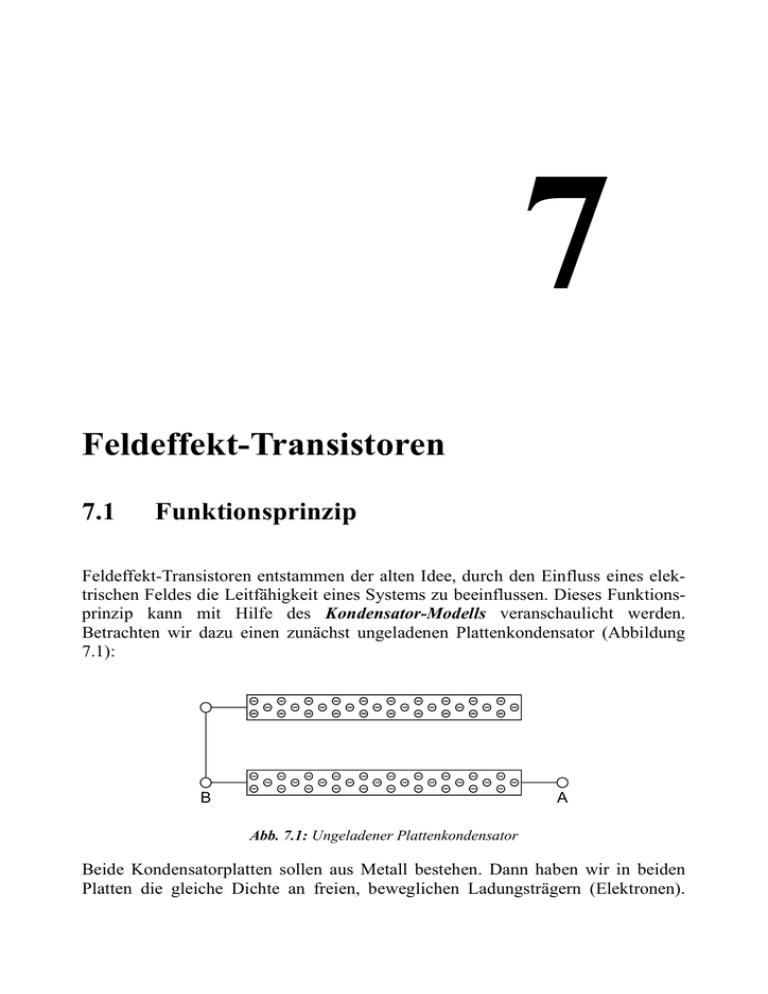

7 Feldeffekt-Transistoren 7.1 Funktionsprinzip Feldeffekt-Transistoren entstammen der alten Idee, durch den Einfluss eines elektrischen Feldes die Leitfähigkeit eines Systems zu beeinflussen. Dieses Funktionsprinzip kann mit Hilfe des Kondensator-Modells veranschaulicht werden. Betrachten wir dazu einen zunächst ungeladenen Plattenkondensator (Abbildung 7.1): B A Abb. 7.1: Ungeladener Plattenkondensator Beide Kondensatorplatten sollen aus Metall bestehen. Dann haben wir in beiden Platten die gleiche Dichte an freien, beweglichen Ladungsträgern (Elektronen). 2 Feldeffekt-Transistoren Wenn nun an die Platten eine Spannung US angelegt wird, so verändern sich die Ladungen und damit auch die Dichten der freien Ladungsträger in beiden Platten. Man erhält also etwa das Bild von Abbildung 7.2: US B A Abb. 7.2: Geladener Plattenkondensator Die Dichte der freien Ladungsträger ist auf der unteren Platte wesentlich kleiner als im Falle des ungeladenen Kondensators. Da die Leitfähigkeit eines Materials proportional zur Dichte der beweglichen Ladungsträger ist, wäre zu erwarten, dass der Widerstand zwischen den Klemmen A und B der unteren Platte grösser ist als bei ungeladenem Kondensator. Man kann also offenbar den Widerstand zwischen den Klemmen A und B durch Anlegen einer Steuerspannung US beeinflussen. Je grösser diese Steuerspannung wird, desto mehr freie Elektronen werden von der unteren auf die obere Platte verschoben und desto grösser wird auch der resultierende Widerstand. Eine kurze Abschätzung zeigt, weshalb dieser Effekt in dieser Form technisch nicht ausgenützt werden kann. Wenn wir Glimmer als Dielektrikum verwenden, so lauten die relevanten Materialdaten: relative Dielektrizitätskonstante gr = 7 und maximal zulässige Feldstärke (Durchschlagfeldstärke) Emax = 100 MV/m. Für die auf einer Platte influenzierte Flächenladungsdichte F erhalten wir: As As σ = ε 0 ⋅ ε r ⋅ E max = 8.85 ⋅ 10 – 12 ⋅ 7 ⋅ 10 8 ------- ≈ 6.2 ⋅ 10 – 3 ------2 m m2 Zum Vergleich untersuchen wir die gesamte bewegliche Ladung in einer Elektrode. In Metallen haben wir eine Ladungsträgerdichte von etwa 5@1028 m-3. Unter der Annahme einer Elektrodendicke von 1 µm erhalten wir für die gesamte freie Ladung pro Flächeneinheit: Q As As ---- = n ⋅ d ⋅ e = 5 ⋅ 10 28 ⋅ 10 – 6 ⋅ 1.6 ⋅ 10 –19 ------- = 8 ⋅ 10 3 ------2 A m m2 7.2 Sperrschicht-Feldeffekt-Transistoren 3 Für das Verhältnis von maximaler influenzierter Ladung zu vorhandener freier Ladung erhalten wir also einen Wert von etwa 0.775@10-6, also etwa 0.775 ppm (ppm = parts per million). Die durch das elektrische Feld verursachte Änderung der Ladungsträgerdichte und damit der Leitfähigkeit ist also praktisch unmessbar klein und kann technisch nicht ausgenützt werden. Der Hauptgrund für dieses Verhalten liegt in der ausserordentlich hohen Dichte der freien Ladungsträger in Leiterwerkstoffen. Man muss also Materialien suchen, die gegenüber den Leitern eine wesentlich geringere Dichte der freien Ladungsträger aufweisen. Halbleiter wie Silizium, Germanium oder Gallium-Arsenid erfüllen diese Bedingungen. Die Mbau ajoritätsträgerdichten betragen bei dotiertem Silizium etwa 1020 ... 1022 m-3, also einige Zehnerpotenzen weniger als bei metallischen Leitern. Da die influenzierte Ladung nicht vom Elektrodenmaterial abhängig ist, wird das Verhältnis von influenzierter Ladung zu gesamter freier Ladung Qi/Q entsprechend grösser. Die technische Umsetzung dieses Konzeptes erfolgt auf zwei verschiedene Arten, nämlich in Form der Sperrschicht-Feldeffekt-Transistoren und in Form der MOS-Feldeffekt-Transistoren. 7.2 Sperrschicht-Feldeffekt-Transistoren 7.2.1 Aufbau und Wirkungsweise Der grundsätzliche Aufbau eines Sperrschicht-FET (junction FET, JFET) ist in Abbildung 7.3 gezeigt. Ein relativ schwach dotiertes n-Gebiet ist sandwichartig von stark p-dotiertem Material umgeben. Zwischen p- und n-Gebiet bildet sich eine Sperrschicht aus. G p+ UGS = 0 n S D p+ Abb. 7.3: Sperrschicht-FET in spannungslosem Zustand Wird dieser pn-Übergang durch Anlegen einer Spannung UGS < 0 in Sperrrichtung vorgespannt, so beginnt die Dicke der Sperrschicht zuzunehmen. Wegen der unterschiedlichen Dotierung wächst die Sperrschicht vorwiegend in die schwach dotierte n-Zone hinein. Diese n-leitende Zone wird auch als Kanal bezeichnet, seine Anschlüsse heissen Drain (D) bzw. Source (S). Durch Veränderung der Spannung UGS (das p-Gebiet wird als Gate G bezeichnet) kann also die Dicke des Kanals und 4 Feldeffekt-Transistoren damit der Widerstand zwischen Drain und Source beeinflusst werden. Wenn die angelegte Spannung UGS gross genug ist, berühren sich die beiden Sperrschichten (Abbildung 7.4) und mangels Ladungsträgern kann zwischen D und S kein Strom mehr fliessen. Man sagt dann auch, der Kanal sei abgeschnürt (pinched off). Die dazu notwendige Spannung UGS = UP heisst deshalb auch Abschnürspannung bzw. pinch off Spannung. G p+ UGS = UP n S D p+ Abb. 7.4: Abgeschnürter FET Wenn nun ein Drainstrom ID fliesst, so verursacht dieser Strom einen Spannungsabfall längs des Kanals. Damit nimmt die Spannung in Richtung auf das drainseitige Ende des Kanals zu, was zu einer entsprechenden Verbreiterung der Sperrschicht führt (Abbildung 7.5). G p+ UGS = 0 ID n S D p+ Abb. 7.5: Stromführender FET Bei einer weiteren Steigerung des Drainstromes auf den Wert ID = IDSS erreicht schliesslich die Spannung am drainseitigen Ende des Kanals den Wert UP , was bedeutet, dass sich die Sperrschichten berühren und der Kanal abgeschnürt wird (Abbildung 7.6). G p+ UGS = 0 ID = IDSS n S D p+ Abb. 7.6: Durch Drainstrom abgeschnürter FET 7.2 Sperrschicht-Feldeffekt-Transistoren 5 Der Strom ID kann nicht mehr weiter gesteigert werden, sondern bleibt praktisch konstant. Die Spannung UDS ist an der Abschnürgrenze gerade gleich UP . Eine Zunahme von ID mit wachsender Spannung UDS würde eine weitere Verengung des Kanals bewirken, also eine Vergrösserung des Kanalwiderstandes. Dies wiederum müsste eine Abnahme des Drainstromes ID bewirken. Umgekehrt würde eine Abnahme von ID eine Kanalerweiterung, also eine Senkung des Kanalwiderstandes und damit auch wieder eine Zunahme von ID bewirken. Oberhalb der Spannung UDS = UP bleibt also der Drainstrom konstant auf dem Wert ID = IDSS; dieser Strom wird auch Drain-Source-Kurzschlussstrom genannt. Der über die pinch off Spannung UP hinausgehende Anteil der Drain-Source-Spannung UDS wird wird im wesentlichen vom drainseitigen, nahezu abgeschnürten Kanalende aufgenommen. Bei den bisherigen Überlegungen haben wir UGS = 0 angenommen. Wenn nun bei einer Gate-Source-Spannung UGS < 0 ein Drainstrom ID fliesst, so addiert sich der Spannungsabfall längs des Kanals zu UGS und wir erhalten eine Sperrschicht, wie sie in Abbildung 7.7 dargestellt wird. G p+ UGS < 0 ID n S D p+ Abb. 7.7: Leitender FET mit Vorspannung In diesem Fall ist der Kanal von Anfang an etwas schmaler, der Kanalwiderstand also grösser. Wenn nun der Strom ID weiter gesteigert wird, so kommt es am drainseitigen Ende des Kanals wieder zu einer Abschnürung, wie das in Abbildung 7.8 gezeigt wird. G p+ UGS < 0 ID n S D p+ Abb. 7.8: Abgeschnürter FET mit Vorspannung Dieser Abschnürpunkt wird bereits bei einem wesentlich kleineren Drainstrom erreicht, wie im Falle ohne Vorspannung. Einerseits ist der Kanalwiderstand - wie oben erläutert - grösser, anderseits muss die zusätzliche Spannung UDS, die benötigt 6 Feldeffekt-Transistoren wird, um am drainseitigen Kanalende den Wert UP zu erreichen, um den Betrag der Vorspannung UGS kleiner sein. Eine weitere Steigerung des Stromes ist auch hier nicht mehr möglich; oberhalb der Abschnürgrenze bleibt der Drainstrom ID praktisch unabhängig von der Drain-Source-Spannung UDS. Für praktische Anwendungen ist man daran interessiert, dass der Kanalwiderstand möglichst klein wird und damit der maximale Drainstrom IDSS möglichst gross wird. Das kann erreicht werden, wenn der Kanal sehr kurz und dafür breit gemacht wird. Um Platz zu sparen, werden deshalb häufig mehrere Kanäle parallel geschaltet, wie das aus Abbildung 7.9 hervorgeht, die eine Aufsicht auf den FET BFW10 zeigt. Abb. 7.9: BFW10 Im Bild sind deutlich die acht parallel geschalteten Kanäle zu erkennen. Links unten ist der Source-Anschluss, rechts oben der Drain-Anschluss sichtbar; die GateKontaktierung erfolgt an der Kristall-Unterseite. Aus der vorangegangenen Analyse geht hervor, dass der Sperrschicht-FET nur dann vernünftig betrieben werden kann, wenn die pn-Übergänge zwischen Gate und Kanal mit Sicherheit sperren. Unter dieser Voraussetzung erfolgt die Steuerung des Bauelementes praktisch leistungslos, da im Gate-Anschluss höchstens der Sperrstrom einer Diode fliesst. Aus diesem Grund ist natürlich nach dem Knotensatz der Source-Strom exakt gleich dem Drain-Strom. Ähnlich wie bei den bipolaren Transistoren (FET werden auch als unipolare Transistoren bezeichnet, da an der Stromleitung nur eine Ladungsträgersorte beteiligt ist) können auch bei den Sperrschicht-FET die Schichtfolgen vertauscht werden; man unterscheidet dann zwischen n- und p-Kanal FET. 7.2 Sperrschicht-Feldeffekt-Transistoren D 7 D ID ID UDS G UDS G UGS UGS S S n-Kanal p-Kanal Abb. 7.10: JFET-Symbole und Bezugsrichtungen Beim n-Kanal-JFET (die Abkürzung JFET steht für junction FET, also einen Sperrschicht-FET) sind die Grössen UDS und ID normalerweise positiv, UGS hingegen ist negativ. Beim p-Kanal-JFET sind die Polaritäten gerade umgekehrt. Es werden in der Praxis vorzugsweise n-Kanal-JFET verwendet, da sie bei gleicher Geometrie einen etwa dreimal kleineren Kanalwiderstand aufweisen. Das ist eine Folge der wesentlich grösseren Beweglichkeit der Elektronen gegenüber derjenigen von Löchern. Der Aufbau eines JFET ist im Prinzip symmetrisch, das heisst, die Anschlüsse Drain und Source könnten eigentlich vertauscht werden. Aus den Überlegungen über die grundsätzliche Funktionsweise folgt aber leicht, dass immer die negativere (bei einem n-Kanal-JFET) der beiden Kanal-Elektroden die Rolle der Source-Elektrode übernimmt. Bei einer Vorzeichenänderung der Spannung UDS würde damit auch der Bezugspunkt für die Steuerspannung UGS ändern. 7.2.2 Kennlinie und Gleichungen Die Tatsache, dass bei einem JFET eigentlich nur ein Strom, nämlich der Drainstrom ID und nur zwei Spannungen, nämlich UDS und UGS vorkommen, hat zur Folge, dass das Kennlinienfeld wesentlich einfacher wird, als beim bipolaren Transistor. Wir können uns zunächst auf das sogenannte Ausgangskennlinienfeld beschränken, das den Drainstrom ID der Drain-Source-Spannung UDS gegenüberstellt, wobei die Steuerspannung UGS als Parameter dient. In Abbildung 7.11 ist das Ausgangskennlinienfeld eines typischen n-Kanal-JFET dargestellt. 8 Feldeffekt-Transistoren ID IDSS 10mA UGS = 0V ohmscher Bereich 9 pinch off Bereich (Abschnürbereich) 8 7 UGS = -1V 6 5 UGS = -2V 4 3 2 UGS = -3V 1 UGS = -4V 5 10 15V UDS |UP| Abb. 7.11: Ausgangskennlinienfeld eines n-Kanal-JFET Man unterscheidet im Ausgangskennlinienfeld zwei Gebiete, nämlich den ohmschen Bereich und den Abschnürbereich. Im ohmschen Bereich wird der JFET als steuerbarer Widerstand verwendet, entsprechend sind auch die Anwendungen. Im Abschnürbereich (oder pinch off Bereich) ist der Drainstrom nahezu unabhängig von der Drain-Source-Spannung; die meisten Verstärkeranwendungen arbeiten in diesem Bereich. Die Ausgangskennlinien können in recht guter Näherung durch die folgenden, der Literatur1 entnommenen Gleichungen beschrieben werden. Im ohmschen Gebiet (UDS # UGS - UP) gilt: 2 2 ⋅ I DSS ⎛ U GS⎞ U DS ⎞ ⎛ ID ( U GS , U DS ) ≈ ------------------- ⎜ U DS ⎜ 1 – -----------⎟ – ---------------------⎟ – UP ⎝ U P ⎠ 2 ( – U P )⎠ ⎝ 1. Hanspeter von Ow: Der Feldeffekttransistor als steuerbarer Widerstand und seine Anwendung in regelbaren Verstärkern und Dämpfungsgliedern. Zürich 1970 (Dissertation ETH Nr. 4513) 7.2 Sperrschicht-Feldeffekt-Transistoren 9 Für das pinch off Gebiet (UDS $ UGS - UP) gilt dann die einfache Beziehung, die auch etwa als FET-Gleichung bezeichnet wird: U GS⎞ 2 ⎛ I D ( U GS ) ≈ I DSS ⎜ 1 – -----------⎟ UP ⎠ ⎝ Aus diesen Beziehungen folgt, dass die FET-Kennlinien durch die beiden Transistor-Parameter UP und IDSS beschrieben werden. Da im pinch off Bereich der Drainstrom praktisch nicht von der Spannung UDS abhängig ist, kann der FET auch durch eine einzige Kennlinie, die sogenannte Transfer-Kennlinie beschrieben werden. Diese Kennlinie (Abbildung 7.12) folgt der FET-Gleichung. ID IDSS UGS UP Abb. 7.12: Transfer-Kennlinie ID (UGS )(pinch-off-Bereich) Da die zwei Parameter IDSS und UP das Verhalten eines JFET offenbar massgeblich bestimmen, stellt sich die Frage, wie diese Parameter gemessen werden können. Die Messung von IDSS bereitet keine grossen Schwierigkeiten, IDSS ist ja der maximale Strom, der bei UGS = 0 fliesst. Als Messschaltung kommt die Schaltung von Abbildung 7.13 in Frage. IDSS U0 > UP A Abb. 7.13: Messung von IDSS 10 Feldeffekt-Transistoren Schwieriger wird die Bestimmung von UP . Wenn wir gemäss Abbildung 7.14 die Transfer-Kennlinie ausmessen und auftragen, so haben wir das Problem, den Scheitelwert der Parabel zu bestimmen; es tritt hier ein schleifender Schnitt auf. +15 V A ID V UGS -15 V Abb. 7.14: Messung der Transfer-Kennlinie Wenn wir die FET-Gleichung aber etwas umformen, so erhalten wir eine lineare Form, die dann auch einen eindeutigen Schnittpunkt liefert: U GS ID ---------- = 1 – ----------UP I DSS Die so ausgewerteten Messwerte eines konkreten FET (2N5458) sind in Abbildung 7.15 dargestellt: 1/2 (ID/IDSS) Messwerte 1 Regressionsgerade UGS UP Abb. 7.15: Bestimmung von UP 7.2 Sperrschicht-Feldeffekt-Transistoren 11 Da es sich bei der FET-Gleichung um eine Näherung handelt, liegen die tatsächlich gemessenen Werte nicht genau auf einer Geraden, wie man das erwarten würde. Mit Hilfe der Regressionsrechnung kann nun eine Gerade durch die Messwerte gelegt werden. Diese Regressionsgerade schneidet die Spannungsachse bei der Spannung UP. Auf diese Weise lässt sich also auch die pinch off Spannung UP mit hinreichender Genauigkeit bestimmen. Wenn wir mit den so gefundenen Werten von IDSS und UP die Transferkennlinie berechnen und mit den Messwerten vergleichen, so erhalten wir das folgende Bild (Abbildung 7.16): ID UGS Abb. 7.16: Vergleich der gerechneten und der gemessenen Transferkennlinie Die Übereinstimmung der Kennlinien ist hinreichend gut, so dass wir ohne Skrupel mit den Näherungsgleichungen für den JFET arbeiten können. Die beiden Parameter UP und IDSS unterliegen übrigens einer ziemlich starken Exemplarstreuung; beim erwähnten Typ 2N5458 lauten die entsprechenden Angaben auf dem Datenblatt: -1 V $ UP $ -7 V 2 mA # IDSS # 9 mA Dieser grosse Streubereich ist typisch für die üblicherweise verwendeten JFET (mindestens für die low cost JFET). Wir haben also ähnlich wie bei den bipolaren Transistoren die Aufgabe, Schaltungen zu entwickeln, deren Eigenschaften möglichst wenig von diesen stark streuenden Parametern abhängig sind. 12 Feldeffekt-Transistoren 7.2.3 Thermisches Verhalten von JFET Zwei Effekte sind für das thermische Verhalten von JFET verantwortlich. Der erste Effekt ist die temperaturbedingte Abnahme der Trägerbeweglichkeit bei zunehmender Temperatur. Dies führt zu einer Vergrösserung des Kanalwiderstandes mit wachsender Temperatur und damit zu einer Abnahme des Drainstromes ID. Der zweite Effekt ist die Abnahme der Sperrschichtdicke mit wachsender Temperatur, was zu einer Vergrösserung des Kanalquerschnittes und damit zu einer Zunahme des Drainstromes führt. Die beiden Temperatureinflüsse sind also gegenläufig. Eine genauere Analyse zeigt, dass bei höheren Drainströmen der Einfluss der Trägerbeweglichkeit dominiert und damit eine Erhöhung der Temperatur netto zu einer Abnahme des Drainstromes führt. Bei kleinen Drainströmen dominiert in der Regel der Einfluss der Sperrschichtdicke, was zu einer Zunahme des Drainstromes führt. Daraus folgt, dass es einen Punkt geben muss, in dem sich die beiden gegenläufigen Temperatureinflüsse exakt kompensieren. Nun ist dieser Punkt von eher akademischem Interesse, da sich die üblicherweise verwendeten Arbeitspunkte im Bereich des Einflusses der Trägerbeweglichkeit befinden, wo also der Drainstrom mit wachsender Temperatur abnimmt. 7.2.4 Die Kleinsignal-Ersatzschaltung Der JFET im Verstärkerbetrieb arbeitet eigentlich immer im linearen Teil des Ausgangskennlinienfeldes, also im pinch off Bereich. Aus dem Verlauf der Ausgangskennlinien kann man schliessen, dass der JFET in diesem Bereich wie eine spannungsgesteuerte Stromquelle wirkt; die in der Praxis beobachtbare geringe Zunahme des Drainstromes mit der Spannung UDS kann durch einen differentiellen Widerstand rDS erfasst werden. Der Eingangsstrom (Gatestrom) eines JFET ist vernachlässigbar klein (Sperrstrom einer Diode) und wird in der Ersatzschaltung nicht berücksichtigt. G Kleinsignal-Ersatzschaltung iD D S•uGS uGS uGS rDS uDS S Abb. 7.17: Kleinsignal-Ersatzschaltung des JFET 7.2 Sperrschicht-Feldeffekt-Transistoren 13 Der Faktor S wird Steilheit genannt. Mathematisch gesehen entspricht S der Steigung der Transferkennlinie im Arbeitspunkt. Daraus kann nun mit Hilfe der FETGleichung die Steilheit bestimmt werden: – 2 ⋅ IDSS ⎛ – 2 ⋅ IDSS dI D U GS⎞ S = -------------- = ---------------------- ⋅ ⎜ 1 – -----------⎟ = -------------------------- ⋅ UP UP dU GS UP ⎠ ⎝ U GS⎞ ⎛ I DSS ⋅ ⎜ 1 – -----------⎟ UP ⎠ ⎝ Der Ausdruck in eckigen Klammern entspricht genau der Wurzel aus ID, was durch Vergleich mit der FET-Gleichung leicht verifiziert werden kann. Wir erhalten demnach für die Steilheit schliesslich den folgenden Ausdruck: 2 ⋅ ID ⋅ I DSS – 2 ⋅ I D ⋅ I DSS S = ------------------------------------- = --------------------------------UP UP Die Steilheit ist arbeitspunktabhängig und hat ihren Maximalwert bei ID = IDSS und beträgt dann Smax = -2IDSS/UP. In der Literatur werden für die Steilheit, die übrigens üblicherweise in mA/V ausgedrückt wird, auch etwa die Bezeichnungen gFS oder yFS verwendet (es handelt sich schliesslich bei der Steilheit formal um einen Leitwert). Der differentielle Drain-Source-Widerstand rDS ist relativ gross und nimmt mit steigendem Drainstrom etwas ab (rDS ist ungefähr umgekehrt proportional zur Wurzel aus ID). Wegen seiner Grösse, die wir in einem späteren Kapitel noch messtechnisch ermitteln werden, kann rDS in vielen Fällen auch vernachlässigt werden. 14 Feldeffekt-Transistoren 7.3 Verstärker-Grundschaltungen 7.3.1 Arbeitspunkt-Einstellung Das Gate-Potential muss beim n-Kanal-JFET negativer sein als das Source-Potential. Das kann man entweder durch eine separate negative Betriebsspannung erreichen, was allerdings eine relativ teure Lösung ist, oder durch eine Schaltung wie sie in Abbildung 7.18 gezeigt wird. UDD ID UGS RG RS Abb. 7.18: Arbeitspunkt-Einstellung beim JFET Da kein Gatestrom fliesst (gesperrter pn-Übergang), liegt das Gate auf MassePotential. Der Widerstand RG hat nur die Aufgabe, das Gate auf diesem Potential zu halten; da er von keinem Strom durchflossen wird, kann er nahezu beliebig gross gewählt werden. Der Drainstrom ID verursacht am Widerstand RS einen Spannungsabfall und erzeugt so die gewünschte negative Spannung UGS. Für die sich einstellenden Arbeitspunktgrössen IDA und UGSA erhalten wir zwei Gleichungen. Die eine ist die FET-Gleichung, die andere das ohmsche Gesetz für RS. U GSA⎞ 2 ⎛ I DA = I DSS ⋅ ⎜ 1 – --------------⎟ UP ⎠ ⎝ U GSA = – IDA ⋅ Rs Dieses Gleichungssystem kann nun algebraisch aufgelöst werden. Es interessieren uns eigentlich nur zwei Werte, nämlich der Wert von RS für einen geforderten Drainstrom IDA und der Wert von IDA für einen gegebenen Widerstand RS. Die erste Aufgabe ist sehr einfach lösbar, für den geforderten Wert von RS erhalten wir: –U P ⎛ I DA ⎞ -⎟ RS = ---------- ⋅ ⎜ 1 – ---------I DA ⎝ I DSS⎠ 7.3 Verstärker-Grundschaltungen 15 Das negative Vorzeichen braucht uns nicht weiter zu irritieren, denn die pinch off Spannung UP ist ja selbst auch negativ; RS wird also schon positiv. Die Lösung der zweiten Aufgabe sei dem Leser als Übungsaufgabe überlassen (Hinweis: Bei einer quadratischen Gleichung sind nicht immer beide Lösungen sinnvoll). Man kann sich aber rasch einen Überblick verschaffen, wenn man die beiden Gleichungen grafisch darstellt (Abbildung 7.19). Der Schnittpunkt der Graphen der beiden Gleichungen ergibt dann den Arbeitspunkt. ID RS IDSS IDA UP UGSA UGS Abb. 7.19: Arbeitspunkt beim JFET (grafische Darstellung) Die gestrichelte Kurve gehört zum zweiten Ast der Parabel, die ja die Transferkennlinie bildet. Die zweite Lösung der angesprochenen quadratischen Gleichung liefert den Schnittpunkt der Widerstandsgeraden mit diesem Ast. Nun liegen die Verhältnisse leider nicht ganz so einfach; die enormen Streuungen der FET-Parameter wurden bereits einmal angesprochen. In Abbildung 7.20 sind die möglichen Transferkennlinien des FET 2N5458 massstäblich eingetragen; sie bilden in ihrer Gesamtheit die schraffierte Fläche. Man erkennt nun, dass die Schnittpunkte der Widerstandsgeraden RS mit den Transferkennlinien, also die Arbeitspunkte, in weiten Grenzen streuen können. Der Maximalwert des Ruhestromes ist um ein Mehrfaches grösser als der Minimalwert. Es ist also offenbar sehr schwierig, bei Feldeffekt-Transistoren stabile Arbeitspunkte einzustellen (stabil hier nicht unbedingt im Sinne von Temperaturstabilität, sondern eng toleriert, damit eine Serienproduktion ohne Abgleichprozesse möglich wird). 16 Feldeffekt-Transistoren ID IDSSmax RS IDAmax IDSSmin Bereich der möglichen Ruhströme IDAmin UPmin UPmax UGS Abb. 7.20: Einfluss der Exemplarstreuung auf den Arbeitspunkt Damit wir eine kleinere Streuung bei den Ruheströmen erhalten, müsste die Widerstandsgerade wesentlich flacher verlaufen, der Widerstand RS also viel grösser gewählt werden. Das hat aber den Nachteil, dass der Ruhestrom nahezu beliebig klein wird und damit die Schaltung nur noch bedingt brauchbar ist. Einen Ausweg aus diesem Dilemma zeigt die Abbildung 7.21, wo der Schnittpunkt der Widerstandsgeraden nicht mehr im Ursprung liegt, sondern um den Wert UG in Richtung auf positive Spannungen verschoben wird. Dies führt zu einer wesentlich geringeren Streuung des Ruhestromes IDA bei noch vernünftigen Werten des Drainstromes. ID IDSSmax IDSSmin RS UPmin IDAmax IDAmin UPmax UG Abb. 7.21: Arbeitspunktstreuung mit Vorspannung UGS 7.3 Verstärker-Grundschaltungen 17 Aus der Abbildung 7.22 können wir die folgende Gleichung für die Widerstandsgerade entnehmen: U GS = U G – I D ⋅ R S Nach einer kleinen Umstellung (Auflösen nach UG) erhalten wir die folgende Form der Geradengleichung: U G = U GS + I D ⋅ R S Daraus erhalten wir leicht die zugehörige Schaltung, wie sie in Abbildung 7.22 dargestellt ist: UDD R1 UG UGS R2 ID RS Abb. 7.22: Verbesserte Schaltung zur Arbeitspunkteinstellung Die gewünschte Vorspannung kann einfach durch einen Spannungsteiler realisiert werden, der das Gate-Potential auf den Wert UG anhebt. Diese Schaltung erlaubt wesentlich enger tolerierte Arbeitspunkte, benötigt aber auch eine nicht unbeträchtlich höhere Betriebsspannung. Der Spannungsteiler darf auch hier wieder fast beliebig hochohmig gewählt werden, da er unbelastet ist; der Sperrstrom des pn-Überganges zwischen Gate und Kanal muss dabei allerdings beachtet werden. Angaben dazu und besonders zur Temperaturabhängigkeit des Gatestromes findet man in den entsprechenden Datenblättern. Bei der Dimensionierung ist darauf zu achten, dass die Schaltungen möglichst ohne Abgleichprozesse auch in grossen Stückzahlen herstellbar sein müssen. Man muss daher den Ruhestrom IDA so wählen, dass er sicher kleiner ist, als der minimale Wert von IDSS des betreffenden Transistortyps. Empfehlenswert im Sinne einer garantierten Aussteuerbarkeit ist ein Wert von IDA . IDSSmin / 2. 18 Feldeffekt-Transistoren 7.3.2 Die Source-Schaltung Die Source-Schaltung entspricht im Prinzip der Emitterschaltung bei den bipolaren Transistoren. Der Aufbau der Schaltung ist in Abbildung 7.23 gezeigt. Dabei wurde der Einfachheit halber die einfachste Form der Arbeitspunkteinstellung gewählt, da diese auf das Kleinsignalverhalten keinen Einfluss hat. UDD RD C1 u1 RG RS CS u2 Abb. 7.23: Schema der Source-Schaltung Bei der Arbeitspunkteinstellung der Source-Schaltung ist noch darauf zu achten, dass der momentane Betriebspunkt des JFET den Abschnürbereich nicht verlassen darf, andernfalls würden grosse Signalverzerrungen auftreten. Das bedeutet, dass die Ruhespannung UDSA grösser als |UP| gewählt werden muss. Bei der Wahl der Betriebsspannung bzw. bei der Wahl von RD ist darauf Rücksicht zu nehmen. In Analogie zu den Schaltungen mit bipolaren Transistoren können wir auch für diese Verstärkerstufe eine Kleinsignal-Ersatzschaltung zeichnen (Abbildung 7.24). S·uGS u1 RG uGS rDS RD u2 Abb. 7.24: KSE der Source-Schaltung Die Spannungsverstärkung dieser Schaltung kann man direkt aus der Kleinsignalersatzschaltung herauslesen: u2 v u = ----- = – S ⋅ ( R D || r DS ) ≈ – S ⋅ RD u1 7.3 Verstärker-Grundschaltungen 19 Ebenso leicht lassen sich Ein- und Ausgangswiderstand bestimmen: r ein = R G r aus = R D || r DS ≈ R D Zahlenbeispiel Der verwendete JFET des Typs 2N5458 habe eine Spannung UP = -3 V und einen Strom IDSS = 5 mA. Bei einem gewünschten Wert für IDA von 1 mA erhält man für den Widerstand RS einen Wert von 1.66 kS; gerundet auf den nächstliegenden Normwert der Reihe E12 ergibt sich RS = 1.5 kS. Der sich in diesem Fall einstellende Drainstrom beträgt IDA = 1.07 mA; es ist also nur eine relativ kleine Abweichung vom Sollwert zu verzeichnen. Für die Betriebsspannung UDD wählen wir 12 V, dann verbleiben bei einer Spannung UGSA = 1.6 V und einem Widerstand RD = 5.6 kS noch etwa 4.4 V > |UP| = 3 V als Spannung über dem FET. Der Widerstand RG wird zu 1 MS gewählt. Unter diesen Voraussetzungen erhält man für die Steilheit des JFET S = 1.54 mA/V. Für die Spannungsverstärkung resultiert damit: vu = -8.64. Diese Spannungsverstärkung liegt um Grössenordnungen unter den mit bipolaren Transistoren erreichbaren Werten. Im Vergleich zur Emitterschaltung fällt anderseits der sehr hohe (fast frei wählbare) Eingangswiderstand positiv auf. Klirrfaktor Die einzige Nichtlinearität der Source-Schaltung ist die Transferkennlinie, die in recht guter Näherung durch die FET-Gleichung beschrieben werden kann. U GS⎞ 2 ⎛ I D = I DSS ⋅ ⎜ 1 – -----------⎟ UP ⎠ ⎝ Für die Spannung UGS können wir vorderhand den folgenden Ansatz machen: U GS = U GSA + u GS Wir stellen also die Gate-Source-Spannung als Überlagerung von Arbeitspunktspannung UGSA und Signalspannung uGS dar. Damit können wir jetzt den resultierenden Drainstrom berechnen. 20 Feldeffekt-Transistoren U GSA + u GS⎞ 2 ⎛ ID = IDSS ⎜ 1 – ------------------------------⎟ UP ⎝ ⎠ 2 ⎛ 2 ( U GSA + u GS ) ( U GSA + u GS ) ⎞ = I DSS ⎜ 1 – --------------------------------------- + --------------------------------------⎟ ⎜ ⎟ 2 UP ( UP ) ⎝ ⎠ 2 2 ⎛ 2U GSA 2u GS ( U GSA ) 2U GSA u GS ( u GS ) ⎞ = IDSS ⎜ 1 – ----------------- – ------------- + ---------------------- + ---------------------------- + -----------------⎟ ⎜ 2 2 2⎟ UP UP ( UP ) ( UP ) ( UP ) ⎠ ⎝ Zur Berechnung des Klirrfaktor benötigen wir nur den zeitabhängigen Teil des Drainstromes; wir erhalten dafür: 2⎞ ⎛ – 2u 2U u u ( ) GS GSA GS GS i D = IDSS ⎜ ---------------- + ---------------------------- + -----------------⎟ ⎜ U 2 2⎟ P ( UP ) (UP) ⎠ ⎝ 2⎞ ⎛ U – U ( ) u ⎛ ⎞ –2 P GSA GS = I DSS ⎜ ------- ⋅ ⎜ ----------------------------⎟ ⋅ u GS + -----------------⎟ ⎜U ⎝ 2⎟ UP ⎠ (U ) ⎠ ⎝ P P 2⎞ ⎛ u ( ) U ⎛ ⎞ –2 GSA GS = IDSS ⎜ u GS ⋅ ------- ⋅ ⎜ 1 – --------------⎟ + -----------------⎟ ⎜ UP ⎝ UP ⎠ ( U )2 ⎟ ⎝ P ⎠ Für die Signalspannung uGS machen wir noch den folgenden Ansatz: ˆ ⋅ cos ( ωt ) u GS ( t ) = U ˆ2 2 U ( u GS ) ( t ) = ------- ( 1 + cos ( 2ωt ) ) 2 Daraus erhalten wir, wenn wir wiederum nur die zeitabhängigen Terme berücksichtigen und ausmultiplizieren, den folgenden Ausdruck für den Drainstrom iD(t): 7.3 Verstärker-Grundschaltungen 21 ˆ ˆ 2 U GSA⎞ ⎛ 2U 1⎛ U i D = ---------- ⋅ I DSS ⋅ ⎜ 1 – --------------⎟ ⋅ cos ( ωt ) + IDSS ⋅ --- -------⎞ ⋅ cos ( 2ωt ) UP ⎠ UP 2 ⎝ U P⎠ ⎝ = a 1 ⋅ cos ( ωt ) + a 2 ⋅ cos ( 2ωt ) Betrachten wir den Fourier-Koeffizienten a1 noch etwas genauer: ˆ I ⋅I ˆ ˆ 2U U GSA⎞ U GSA⎞ ⎛ ⎛ 2U 2U DA DSS ---------- ⋅ I DSS ⋅ ⎜ 1 – --------------⎟ = ---------- IDSS I DSS ⋅ ⎜ 1 – --------------⎟ = ------------------------------------UP UP UP ⎠ UP ⎠ UP ⎝ ⎝ Für den Klirrfaktor d erhalten wir schliesslich: ˆ a2 I DSS U d = ----- = -------------- ⋅ -----------a1 4 UP I DA Der Klirrfaktor scheint also auf den ersten Blick ziemlich stark von den FETParametern und vom Arbeitspunkt abhängig zu sein. Berechnen wir noch die für einen vorgegebenen Klirrfaktor zulässige Amplitude der Eingangsspannung: IDA Uˆe = 4 ⋅ U P ⋅ d ⋅ ---------I DSS Für die Werte aus dem vorherigen Beispiel erhalten wir für einen Klirrfaktor von 1% (d = 0.01) eine zulässige Amplitude der Eingangsspannung von Ûe = 54 mV. Bei der Emitterschaltung haben wir dafür nur einen Wert von 1 mV gefunden. Der JFET scheint hier einen grossen Vorteil gegenüber dem Bipolartransistor zu haben. Eine genauere Überlegung zeigt aber, dass man eigentlich die Klirrfaktoren bei gleicher Ausgangsamplitude vergleichen muss, denn das Ziel eines Verstärkers ist es ja in der Regel, eine kleine Eingangsspannung auf einen definierten Wert zu bringen. Es gilt: Uˆa = v u ⋅ Uˆe = S ⋅ RD ⋅ Uˆe 22 Feldeffekt-Transistoren Damit erhalten wir für die zulässige Amplitude der Ausgangsspannung den folgenden Ausdruck: IDA 2 IDA ⋅ IDSS Uˆa = 4 ⋅ U P ⋅ d ⋅ ---------- ⋅ --------------------------------- ⋅ R D = d ⋅ 8 ⋅ I DA ⋅ R D = d ⋅ 8 ⋅ U RDA UP IDSS Die für einen bestimmten Klirrfaktor zulässige Amplitude der Ausgangsspannung ist also proportional zur Ruhespannung URDA über dem Drainwiderstand und damit völlig unabhängig von den FET-Parametern und von der genauen Lage des Arbeitspunktes. In unserem Beispiel erhalten wir bei einem Ruhespannungsabfall über RD von 6 V eine zulässige Amplitude der Ausgangsspannung (für d = 0.01) von 480 mV. Bei einer Emitterschaltung würde die Spannungsverstärkung unter sonst gleichen Verhältnissen etwa URCA/UT = 230 betragen; entsprechend wäre dann zu maximal zulässige Ausgangsamplitude etwa 230 mV, also etwa die Hälfte des Wertes beim JFET. Verstärkerstufen mit JFET haben also einen etwas kleineren Klirrfaktor als mit bipolaren Transistoren aufgebaute Stufen. Anderseits ist die erreichbare Spannungsverstärkung wesentlich kleiner und die Probleme mit der Arbeitspunkteinstellung sind auch nicht zu vergessen. Ein weiterer Nachteil ist, dass JFET nur ziemlich kleine Ströme (im mA-Bereich) verarbeiten können. Die Hauptvorteile von JFETVerstärkern liegen in den sehr hohen erzielbaren Eingangswiderständen und im besseren Rauschverhalten bei hochohmigen Signalquellen. Aus diesen Gründen werden JFET in analogen Schaltungen eher selten und dann vorwiegend in Eingangsstufen verwendet, wo ihre Vorteile zum Tragen kommen. 7.3.3 Der Source-Folger Der Source-Folger oder Drain-Schaltung (Abbildung 7.25) entspricht dem Emitterfolger und hat auch ähnliche Eigenschaften. UDD C1 u1 R1 R2 RS u2 Abb. 7.25: Schema eines Source-Folgers 7.3 Verstärker-Grundschaltungen 23 Damit wir den Arbeitspunkt vernünftig wählen können (Source-Potential etwa die halbe Betriebsspannung), müssen wir die Arbeitspunkt-Einstellung mit Vorspannung wählen. Für die Kleinsignal-Ersatzschaltung erhalten wir auf gewohnte Weise: uGS u1 S·uGS Rp = R1||R2 rDS RS u2 Abb. 7.26: KSE des Source-Folgers Für die Spannungsverstärkung erhalten wir unter Vernachlässigung von rDS durch Berechnung der Spannungen u1 und u2 sofort: S ⋅ RS u2 v u = ----- = ----------------------1 + S ⋅ RS u1 Mit den Werten UDD = 12 V, UP = -3 V, IDSS = 5 mA, R1 = 1.5 MS, R2 = 1 MS und RS = 6.8 kS erhalten wir für den Ruhestrom IDA . 1 mA, für das Source-Potential etwa 6.3 V und für die Steilheit S in diesem Arbeitspunkt S . 1.5 mA/V. Damit resultiert für die Spannungsverstärkung vu = 0.91, also signifikant weniger als 1. Der Eingangswiderstand lässt sich sofort aus der Ersatzschaltung entnehmen; die Berechnung des Ausgangswiderstandes ist etwas schwieriger. Bei eingangsseitigem Leerlauf (oder Kurzschluss) ist uGS = -u2 und damit wird der eingeprägte Strom der Stromquelle i2' = -S@u2. Der Ausgangswiderstand ist die Parallelschaltung von RS, rDS und dem Widerstand u2/-i2' = 1/S. Damit erhalten wir, wenn wir wieder rDS vernachlässigen: r ein = R P = R 1 || R 2 1 raus ≈ R S || --S Mit den oben verwendeten Zahlwerten erhalten wir für den Eingangswiderstand rein = 600 kS und für den Ausgangswiderstand raus . 600 S. Das Verhalten des Source-Folgers gleicht demjenigen des Emitterfolgers, allerdings haben wir eine Spannungsverstärkung, die deutlich kleiner als 1 ist und auch der Ausgangswiderstand erreicht nicht die tiefen Werte wie der bipolare Emitterfolger. 24 Feldeffekt-Transistoren 7.4 MOS-Feldeffekt-Transistoren 7.4.1 Funktionsprinzip der MOS-FETs MOS-Feldeffekt-Transistoren entsprechen in ihrer Wirkungsweise eher dem zu Beginn dieses Kapitels verwendeten Kondensator-Modell als die Sperrschicht-FET. Die metallische Gate-Elektrode ist durch eine dünne Oxid-Schicht vom Halbleiterkristall getrennt. Gate-Elektrode und Halbleitermaterial bilden die beiden Elektroden des Kondensators, die Oxidschicht dient als Dielektrikum. Von diesem Schichtaufbau (Metal Oxide Semiconductor) hat dieser Transistortyp seinen Namen: MOS-FET; in der Literatur findet man noch andere Bezeichnungen wie: IGFET ( für Insulated Gate FET) oder MIS-FET (für Metal Insulation Semiconductor). Abbildung 7.27 zeigt den grundsätzlichen Aufbau eines n-Kanal MOS-Feldeffekt-Transistors. S G n+ D n+ p B Abb. 7.27: Aufbau eines MOS-Feldeffekt-Transistors Das Grundmaterial ist schwach p-leitend; Source und Drain bestehen aus stark ndotiertem Material. Zwischen Drain und Source kann in dieser Anordnung kein Strom fliessen, da immer einer der beiden pn-Übergänge in Sperrrichtung gepolt ist. Der hier neu auftretende Anschluss „B“ (engl. bulk: Substrat oder Grundmaterial) muss auf einem negativeren Potential liegen als die beiden Elektroden Source und Drain, da sonst die pn-Übergänge leitend werden und das Halbleiterelement nicht mehr steuerbar ist. Üblicherweise wird das Substrat mit der negativen Betriebsspannung verbunden. Wenn in dieser Anordnung eine positive Gate-Source-Spannung UGS angelegt wird, so bildet sich durch Influenz am oberen Rand der p-Zone eine dünne Schicht mit freien Elektronen, man spricht dabei auch von einer Inversionsschicht. Damit haben wir einen leitenden Kanal zwischen Source und Drain; sein Widerstand wird umso kleiner, je grösser die angelegte Spannung UGS ist, weil damit auch die influenzierte Ladung vergrössert wird. Diese Verhältnisse sind in Abbildung 7.28 dargestellt. Bei der Spannung UGS = 0 sperrt der FET; man nennt diesen Typ deshalb auch selbstsperrend (normally off, enhancement type, Anreicherungstyp). 7.4 MOS-Feldeffekt-Transistoren UGS 25 Inversionsschicht S G n+ D n+ p B Abb. 7.28: Selbstsperrender n-Kanal-MOS-FET Wenn es gelingt, dem Kondensator eine Vorspannung sozusagen einzubauen, so könnte man auch Transistoren realisieren, bei denen ein influenzierter Kanal bereits bei der angelegten Spannung UGS = 0 auftritt. Man kann diese Vorspannung realisieren, indem im Siliziumdioxid, also dem Dielektrikum, positive Ladungen „eingefroren“ werden. Man erhält dann einen selbstleitenden FET (normally on, depletion type, Verarmungstyp), wie er in Abbildung 7.29 gezeigt wird. S G D +++++++++++++ n+ n+ p B Abb. 7.29: Selbstleitender n-Kanal MOS-FET Beim selbstleitenden MOS-FET kann man durch eine negative Spannung UGS den Drainstrom verkleinern, durch eine positive Spannung kann der Strom vergrössert werden. Bis jetzt haben wir den MOS-FET immer im stromlosen Zustand betrachtet. Wenn wir nun einen Drainstrom ID fliessen lassen, so nimmt die Kondensatorspannung gegen das drainseitige Ende des Kanals als Folge des Spannungsabfalls immer mehr ab und der Kanal wird wie beim Sperrschicht-FET abgeschnürt, wie das in Abbildung 7.30 am Beispiel des selbstsperrenden n-Kanal-MOS-FETs skizziert wird. Es ist also zu erwarten, dass auch beim MOS-FET der Drainstrom ab einer gewissen Spannung UDS nicht mehr von dieser abhängig ist, dass also die 26 Feldeffekt-Transistoren Ausgangskennlinien im Abschnürbereich ebenfalls praktisch horizontal verlaufen und der Drainstrom in diesem Gebiet fast ausschliesslich von der Gate-SourceSpannung UGS abhängt. Selbstleitende FETs zeigen natürlich genau dasselbe Verhalten. UGS S G D ID n+ n+ p B Abb. 7.30: Selbstsperrender MOS-FET im Abschnürbereich Im Gegensatz zu den Sperrschicht-FETs kann aber der Drainstrom durch höhere Spannungen UGS fast beliebig gesteigert werden, da ja kein pn-Übergang leitend werden kann. Es existiert also auch kein Maximalstrom IDSS. Durch Umkehrung der Polaritäten kann man auch p-Kanal-MOS-Feldeffekt-Transistoren hergestellt werden. Allerdings haben p-Kanal-Transistoren auch hier den Nachteil, dass sie bei gleicher Geometrie einen wesentlich grösseren Kanalwiderstand aufweisen, da die Beweglichkeit der Löcher viel geringer ist als die Beweglichkeit der Elektronen. Aus technologischen Gründen findet man praktisch keine selbstleitenden p-Kanal-MOS-FETs. Die meisten MOS-Transistoren als diskrete Bauelemente sind selbstsperrende n-Kanal-Transistoren; in integrierten Schaltungen werden alle verfügbaren Typen verwendet. 7.4.2 Kennlinien und Gleichungen Die Ausgangskennlinien eines MOS-FETs (selbstsperrend oder selbstleitend) stimmen praktisch mit den Ausgangskennlinien von Sperrschicht-FET überein. Der grosse Unterschied besteht darin, dass die Spannung UGS praktisch keinen Einschränkungen unterliegt (im Rahmen der im Datenblatt spezifizierten Grenzwerte) und dass damit eben auch keine „oberste“ Kennlinie existiert. Es wird auch hier wieder zwischen dem ohmschen Bereich und dem Abschnürbereich unterschieden. Die für den Abschnürbereich (pinch off Bereich) gültige Transferkennlinie weist nun einen abweichenden Verlauf auf. Wir wollen das am Beispiel des meistverwendeten MOS-FETs, dem selbstsperrenden n-Kanal-Typ, etwas genauer untersuchen und die zugehörigen Gleichungen formulieren. 7.4 MOS-Feldeffekt-Transistoren 27 ID UGS Uth Abb. 7.31: Transferkennlinie eines n-Kanal MOS-Feldeffekttransistors Man erkennt, dass man eine minimale Spannung Uth, die sogenannte Schwellspannung (threshold voltage) anlegen muss, damit der MOS-FET überhaupt zu leiten beginnt. Diese Schwellspannung beträgt wenige Volt und spielt eine ähnliche Rolle wie die pinch off Spannung UP bei den JFET. Für den ohmschen Bereich (UGS $ Uth und UDS # UGS - Uth) gilt der folgende Zusammenhang: 2 ( U DS ) ⎞ ⎛ ID ( U GS , U DS ) = K ⋅ ⎜ ( U GS – U th ) ⋅ U DS – ------------------⎟ 2 ⎠ ⎝ Die hier auftretende FET-Konstante K hängt von den Eigenschaften des Halbleitermaterials und von der Geometrie ab; für ihre Einheit gilt: [K] = A / V2. K spielt bei den MOS-FETs die Rolle, die der Strom IDSS bei den JFET innehat. Für den Abschnürbereich (UDS $ UGS - Uth) findet man: 2 K ID ( U GS ) = ---- ⋅ ( U GS – U th ) 2 Die beiden Parameter Uth und K müssen nun noch messtechnisch bestimmt werden. Dazu kann man die für den pinch off Bereich gültige Beziehung verwenden und einige Wertepaare UGS, ID im Abschnürbereich messen. Wählen wir das Wertepaar UGS0 und ID0 als Referenzwert, so können wir das Verhältnis zweier Stromwerte bilden und erhalten mit der FET-Gleichung durch Ziehen der Quadratwurzel auf beiden Seiten der Gleichung: 28 Feldeffekt-Transistoren U GS – U th ID 1 -------= ---------------------------- = ( U GS – U th ) ⋅ ---------------------------- = α ⋅ ( U GS – U th ) U GS0 – U th U GS0 – U th I D0 Man erkennt, dass die Wurzel aus ID proportional zur Differenz UGS - Uth ist. Wenn wir alle Messwerte von ID auf den Referenzstrom 1 A beziehen und die Wurzel daraus über UGS auftragen, so schneidet die resultierende Gerade (die wegen der Messunsicherheit wieder durch eine lineare Regressionsrechnung gewonnen werden sollte) die Spannungsachse bei der Schwellspannung Uth. Dieser Schnittpunkt ist unabhängig vom Proportionalitätsfaktor ". 1/2 (ID/1A) Regressionsgerade Messwerte Uth UGS Abb. 7.32: Bestimmung der Schwellspannung Uth Die in Abbildung 7.32 eingezeichneten Messwerte stammen von einem IRF520, einem selbstsperrenden n-Kanal Leistungs-MOS-FET. Bei bekannter Schwellspannung Uth kann man nun aus jedem gemessenen Wertepaar die FET-Konstante K berechnen: 2 ⋅ ID K = --------------------------------2 ( U GS – U th ) Man sollte diese Rechnung wegen der Messunsicherheiten auch wieder für jedes gemessene Wertepaar durchführen und den Mittelwert als Resultat verwenden. Mit den so gewonnenen Werten für Uth und K kann die Transferkennlinie mit Hilfe der FET-Gleichung berechnet werden. Ein Vergleich der so gewonnenen Näherung mit den Messwerten zeigt, dass auch bei den MOS-FETs die Näherung hinreichend genau ist (Abbildung 7.33). 7.4 MOS-Feldeffekt-Transistoren 29 ID Näherung Messwerte UGS Uth Abb. 7.33: Vergleich von gemessener und gerechneter Transferkennlinie Die bisher angegebenen Zusammenhänge stimmen nur unter der Voraussetzung, dass die Spannung zwischen Substrat B und Source gleich Null ist. Diese Spannung UBS hat nämlich auch einen Einfluss auf den Drainstrom. Damit der pn-Übergang zwischen Substrat und Source (bzw. Drain) mit Sicherheit sperrt, muss UBS # 0 sein. Die Abhängigkeit des Drainstromes ID von UBS entspricht der Stromabhängigkeit beim JFET; je negativer UBS wird, desto kleiner wird der Drainstrom bei konstanter Spannung UGS (eine Sperrspannung zwischen Substrat und Kanal verengt diesen und bewirkt eine Abnahme des Stromes). Diese doppelte Steuerungsmöglichkeit wird bei gewissen Schaltungen (z.B. Modulatoren) technisch ausgenützt; in den meisten Fällen ist sie aber eher störend. Bei sehr vielen MOS-FETs ist deshalb die Substratelektrode intern direkt mit Source verbunden (UBS = 0) und gar nicht von aussen zugänglich. 7.4.3 Symbole und Bezugsrichtungen Die folgende Tabelle gibt eine Übersicht über die verschiedenen MOS-FET-Typen und die Häufigkeit , mit der sie praktisch angewendet werden. Typenübersicht selbstsperrend (enhancement type, normally off, Anreicherungstyp) selbstleitend (depletion type, normally on, Verarmungstyp) n-Kanal p-Kanal sehr häufig häufig seltener praktisch nie 30 Feldeffekt-Transistoren Abbildung 7.34 zeigt die Symbole, die Bezugsrichtungen mit den im Betrieb normalen Polaritäten der Spannungen und Ströme sowie die Transferkennlinien der Gruppe der selbstsperrenden MOS-FETs. D D ID > 0 ID < 0 UDS > 0 UDS < 0 G G UGS > 0 UGS < 0 S S n-Kanal p-Kanal ID ID UGS UGS Abb. 7.34: Symbole und Transferkennlinien der selbstsperrenden MOS-FETs Im Symbol wird durch den unterbrochen gezeichneten Kanal ausgedrückt, dass der FET bei UGS = 0 nicht leitet, was ja das Kennzeichen der selbstsperrenden MOSFETs ist. Dieser Sachverhalt wird auch in der englischen Bezeichnung „normally off“ dargestellt. Die Bezeichnungen „Anreicherungstyp“ oder „enhancement type“ sagen aus, dass der leitfähige Kanal erst durch Anlegen einer Steuerspannung durch Inversion entsteht, dass also erst die freien Ladungsträger angereichert werden müssen. Die Gate-Elektrode ist auch im Symbol isoliert vom Kanal, drückt also aus, dass kein Gatestrom fliessen kann. Bei den selbstleitenden MOS-FETs (Abbildung 7.35) ist dementsprechend der Kanal ausgezogen gezeichnet, weil der Kanal für UGS = 0 leitet (englisch „normally on“). Die Begriffe „Verarmungstyp“ bzw. „depletion type“ illustrieren, dass bei diesen FETs die Ladungsträgerdichte im Kanal durch eine negative Spannung UGS (beim n-Kanal-Typ) verkleinert werden kann, der Kanal eben an Ladungsträgern verarmt. Selbstverständlich kann durch eine Spannung UGS mit umgekehrter Polarität der Kanal auch angereichert werden, insofern ist also diese Bezeichnung etwas irreführend. Die hier primär verwendeten Begriffe „selbstleitend“ und „selbstsperrend“ sind vorzuziehen, da sie aussagekräftiger sind. 7.4 MOS-Feldeffekt-Transistoren D 31 D ID > 0 ID < 0 UDS > 0 UDS < 0 G G UGS UGS S S n-Kanal p-Kanal ID ID UGS UGS Abb. 7.35: Symbole und Transferkennlinien der selbstleitenden MOS-FETs 7.4.4 Bauformen und Empfindlichkeit MOS-Feldeffekt-Transistoren gibt es in den verschiedensten Bauformen, vom Kleinsignaltransistor bis zum Leistungsbauelement mit weit über 20 A Strom und Maximalwerten für die Drain-Source-Spannung von einigen 100 V. Die Gehäuseformen entsprechen denen, die wir bei den bipolaren Transistoren kennen gelernt haben. Bei den meisten diskret erhältlichen MOS-FETs handelt es sich um Leistungs-Transistoren. Kleinsignal-Transistoren sind eher selten. Das hängt mit der Empfindlichkeit der MOS-FETs auf statische Ladungen zusammen. Gate und Kanal bilden einen Kondensator mit einer dünnen Oxidschicht als Dielektrikum. Dieser Kondensator hat eine Kapazität, die bei Kleinsignaltypen im pF-Bereich liegt. Eine elektrostatische Ladung, wie wir sie immer tragen (z.B. Reibungselektrizität) lädt diesen Kondensator auf sehr hohe Spannung auf, die dann zum Durchbruch der Oxidschicht und damit zur Zerstörung des Transistors führen. Kleinsignal-MOSFETs sind deshalb ab Werk mit einem Kurzschlussring aus leitfähigem Gummi oder aus dünnem Draht versehen, der alle Elektroden gegeneinander kurzschliesst. Dieser Kurzschlussring darf erst entfernt werden, wenn der Halbleiter eingelötet ist und damit die Gefahr von extremen statischen Aufladungen weitgehend gebannt ist. Weitere notwendige Vorsichtsmassnahmen sind das Verwenden von leitfähigen 32 Feldeffekt-Transistoren Arbeitsflächen und damit verbundene Armbänder, die eine statische Aufladung verhindern. Leistungshalbleiter sind weniger empfindlich, weil einerseits hier die GateKapazität im nF-Bereich liegt und anderseits die Gate-Elektrode durch Dioden oder andere Elemente gegen Überspannungen geschützt werden kann. In der Leistungselektronik spielt es nicht mehr so eine grosse Rolle, wie hochohmig ein Bauelement angesteuert werden kann. 7.5 Anwendungen von MOS-FETs 7.5.1 Verstärkerschaltungen MOS-FETs werden eher in Ausnahmefällen in Verstärkerschaltungen eingesetzt, da sie ähnliche Eigenschaften haben wie die JFET. Wir haben die bereits bekannten Schwierigkeiten mit der Arbeitspunkt-Einstellung (Exemplarstreuung), die erreichbaren Verstärkungen sind ebenfalls bescheiden. Dazu kommen jetzt noch die vorher erwähnten Probleme mit statischen Aufladungen. Die Anwendungen beschränken sich deshalb auf Schaltungen, in denen der enorm hohe Eingangswiderstand wichtig ist. Die Kleinsignalersatzschaltung der MOS-FETs ist identisch mit derjenigen für JFETs; für die Steilheit erhalten wir hier: dID S = -------------- = K ⋅ ( U GSA – U th ) = dU GS 2 ⋅ K ⋅ I DA Etwas günstiger liegen die Verhältnisse bei integrierten Schaltungen. Hier kann man das Problem der statischen Aufladung besser in den Griff bekommen, damit fällt ein Nachteil weg. Da alle Transistoren im selben Prozess aus dem gleichen Stück Silizium hergestellt wurden, fallen die Streuungen der Parameter auch wesentlich kleiner aus, was die Arbeitspunkteinstellung erleichtert. MOS-Transistoren benötigen viel weniger Fläche als bipolare Transistoren, so dass integrierte MOS-Schaltungen platzsparender und damit auch billiger sind. 7.5.2 Leistungsanwendungen Gegenüber bipolaren Leistungstransistoren haben MOS-Leistungstransistoren einige Vorteile. Nebst der viel kleineren Ansteuerleistung fällt ins Gewicht, dass der Drainstrom bei zunehmender Temperatur abnimmt (jedenfalls bei hohen Strömen) und damit die Parallelschaltung von Leistungsbauteilen massiv erleichtert wird. Wir werden in späteren Kapiteln im Detail auf mögliche Anwendungen von MOS-Leistungstransistoren eingehen. 7.5 Anwendungen von MOS-FETs 7.5.3 33 CMOS-Schaltungen in der Digitaltechnik CMOS steht für Complementary MOS, also für komplementäre MOS-Transistoren (n-Kanal- und p-Kanal-Transistoren in derselben Schaltung). In dieser Technik sind sehr interessante Schaltungen möglich. Betrachten wir einmal einen CMOSInverter (Abbildung 7.36): UDD USS Abb. 7.36: CMOS-Inverter (Grundschaltung) Zunächst eine kurze Beschreibung der Funktionsweise: Für eine hinreichend kleine Eingangsspannung (. 0 V, also ein Low) sperrt der n-Kanal-FET mit Sicherheit (es handelt sich ja um selbstsperrende Typen). Falls die Betriebsspannung grösser ist als die Schwellspannung Uth, leitet der obere p-Kanal-FET. Es kann allerdings kein Strom fliessen, wenn der Ausgang nicht mit einem Widerstand belastet ist. Damit ist der Ausgang über den leitenden p-Kanal-FET mit der positiven Betriebsspannung UDD verbunden und damit im Zustand High. Für eine hohe Eingangsspannung (High) wird der p-Kanal-FET sperren und der n-Kanal-FET leiten und so den Ausgang mit USS verbinden, also ein Low liefern. Bemerkenswert an dieser Schaltung ist die Tatsache, dass sie ohne Widerstände auskommt und dass im statischen Fall kein Strom fliesst. Dank der Einfachheit der Schaltung (nur zwei MOS-Transistoren, die erst noch sehr wenig Chip-Fläche beanspruchen) sind solche CMOSSchaltungen sehr billig. Eben haben wir festgestellt, dass bei CMOS-Schaltungen statisch kein Strom fliesst. Falls wir aber einen Wechsel am Eingang haben, so muss der unvermeidliche Kondensator zwischen Gate und dem Kanal umgeladen werden. Es wird also bei jedem Umschaltvorgang die Ladung )Q = C UDD verschoben; kurzzeitig fliesst also ein Strom. Strom ist ja als verschobene Ladung pro Zeiteinheit definiert; damit ist es offensichtlich, dass der Stromverbrauch bei CMOS-Schaltungen proportional zur Schaltfrequenz zunimmt. Der Vorteil des geringen Stromverbrauchs kommt also vor allem bei quasi statischen Systemen (z.B. Speichererhaltung bei Systemen im stand by Modus) zum Tragen. Bei schnell getakteten Systemen ist Vorsicht geboten; oberhalb von etwa 34 Feldeffekt-Transistoren 5 MHz Taktfrequenz sind beispielsweise LS-TTL-Schaltkreise genügsamer. CMOS-Schaltungen sind aber auch etwas langsamer als die bipolaren Technologien, ihre typische Verzögerungszeit liegt bei der Reihe 74HCxx bei 10 ns, also etwa gleich schnell wie Standard-TTL. In der gleichen Technik können auch NOR-Gatter realisiert werden, wie Abbildung 7.37 zeigt: UDD USS Abb. 7.37: NOR-Gatter in CMOS-Technik Fast symmetrisch zum NOR-Gatter ist das NAND-Gatter realisiert (Abbildung 7.38): UDD USS Abb. 7.38: NAND-Gatter in CMOS-Technik Auch diese Schaltungen bestehen ausschliesslich aus MOS-Transistoren. Da ja alle logischen Funktionen unter ausschliesslicher Verwendung von NAND- bzw. NORGattern realisiert werden können, würden diese Grundschaltungen ausreichen, um eine ganze Logik-Familie zu realisieren. Eine Ausnahme müssen wir noch erwähnen, nämlich Gatter mit Tristate-Ausgängen. Wie Abbildung 7.39 zeigt, sind auch solche Ausgänge sehr einfach realisierbar. 7.5 Anwendungen von MOS-FETs 35 UDD EN USS Abb. 7.39: CMOS-Inverter mit Tristate-Ausgang Falls der Enable-Eingang auf Low ist, sind der unterste n-Kanal-FET und der oberste p-Kanal-FET in der Ausgangsstufe beide gesperrt, der Ausgang ist also im hochohmigen Z-Zustand. Für EN = High leiten die beiden erwähnten Transistoren und der Inverter funktioniert normal. In der CMOS-Technik ist noch eine weitere Grundschaltung üblich, das sogenannte Transmission-Gate (Abbildung 7.40): UDD IN S OUT USS Abb. 7.40: Grundschaltung des Transmission-Gates In dieser Schaltung fallen zunächst die beiden mittleren MOS-FETs auf, denn die Anschlüsse Source und Drain sind nicht eindeutig identifizierbar. In dieser Schaltung wird die Symmetrie der FET ausgenützt (Drain und Source vertauschen ihre Rolle je nach Vorzeichen der Drain-Source-Spannung). Falls der Eingang S mit UDD verbunden ist, wird gleichzeitig der Inverterausgang auf USS gehen und damit sind die beiden mittleren MOS-Transistoren mit Sicherheit gesperrt; IN und OUT sind also getrennt. Ist S mit USS verbunden, so bewirkt das, dass je nach Vorzeichen 36 Feldeffekt-Transistoren der Eingangsspannung mindestens einer der beiden mittleren Transistoren leitet und somit IN und OUT miteinander verbunden sind. Solche Transmission-Gates werden in der CMOS-Technik häufig verwendet, da sie in vielen Fällen einfachere Realisierungen komplexer Logikfunktionen erlauben (z.B. bei Multiplexern). Bei bescheideneren Ansprüchen kann ein Transmission-Gate auch zum Schalten eines analogen Signals verwendet werden. Die erste Familie von CMOS-Schaltungen war die Reihe CD4000. Diese Logik konnte mit Betriebsspannungen bis 15 V betrieben werden und umfasste ein recht grosses Spektrum an lieferbaren Logikfunktionen. Allerdings war die Reihe von den Verzögerungszeiten her nicht vergleichbar mit den damals üblichen TTL-Schaltungen. Zudem haben die Hersteller für die gleichen Logikfunktionen wie die TTLLogik andere Pin-Belegungen gewählt, so dass es mit sehr viel Arbeit verbunden war, eine bestehende TTL-Schaltung auf CMOS-Technik umzubauen. Deshalb hat diese Reihe nie die grosse Bedeutung erlangt wie die TTL-Technik. Später wurde das mit der Schaffung der Reihe 74Cxx korrigiert; diese Reihe war von der logischen Funktion, von der Betriebsspannung und von der Pin-Belegung her identisch mit den TTL-Reihen. Das Handicap war immer noch die deutlich tiefere Geschwindigkeit. Die Reihe 74HCxx (H steht für High Speed) hat in dieser Richtung grosse Fortschritte gebracht; die Verzögerungszeiten der HC-Reihe entsprechen denen der Reihe 74xx bzw. 74LSxx (tpd . 10 ns). Gegenüber den älteren CMOS-Reihen konnten die Ausgänge auch etwas grössere Ströme liefern bzw. aufnehmen. Es blieb nur noch ein Unterschied, nämlich die H- und L-Pegel. Die folgende Tabelle zeigt die wichtigsten Werte der Reihe 74HCxx und den TTLReihen. Parameter 74HCxx 74xx 74LSxx 74ASxx 74ALSxx UIHmin 3.5V 2V 2V 2V 2V UILmax 1V 0.8V 0.8V 0.8V 0.8V UOHmin 4.9V 2.4V 2.7V 2.7V 2.7V UOLmax 0.1V 0.4V 0.4V 0.4V 0.4V IIHmin 1µA 40µA 20µA 200µA 20µA IILmax -1µA -1.6mA -400µA -2mA -100µA IOHmin -4mA -400µA -400µA -2mA -400µA IOLmax 4mA 16mA 8mA 20mA 4mA Bei diesen elektrischen Kennwerten fällt auf, dass die Ausgangsspannungen der CMOS-Schaltungen praktisch nicht von den Betriebsspannungen abweichen. Im 7.5 Anwendungen von MOS-FETs 37 Gegensatz zu den mit bipolaren Transistoren arbeitenden TTL-Schaltungen treten hier weder pn-Übergänge noch Sättigungsspannungen auf. Die Ausgangstransistoren der CMOS-Schaltungen arbeiten ja eigentlich im ohmschen Gebiet des Kennlinienfeldes und so ist der Ausgang über den relativ kleinen Kanalwiderstand des leitenden MOS-Transistors mit der jeweiligen Betriebsspannung verbunden. Im Falle einer sehr hochohmigen Belastung ist die Ausgangsspannung gleich der Betriebsspannung. Wenn CMOS-Bausteine mit TTL-Bausteinen gemischt werden sollen, muss man vor allem die unterschiedlichen Spannungspegel beachten. Beim Übergang von HC auf TTL gibt es keine Probleme, da die Ausgangspegel des CMOS-Gatters mit Sicherheit unter bzw. über den Schwellwerten der TTL-Eingänge liegen. Der Übergang von TTL- auf HC-Gatter ist hingegen problematisch. Im Zustand Low ergeben sich keine Schwierigkeiten, da die maximale Ausgangsspannung der TTL-Schaltung mit 0.4 V unter dem für CMOS zugelassenen Maximalwert von 1 V liegt. Im Zustand High liefert die TTL-Schaltung mit Sicherheit noch 2.4 ... 2.7 V, also weniger als die minimal geforderten Eingangsspannung von 3.5 V bei der CMOS-Schaltung. Man kann durch Zuschalten eines pull up Widerstandes an den TTL-Ausgang die Ausgangsspannung im Zustand H anheben, so dass auch diese Kopplung einwandfrei funktioniert (Abbildung 7.41). 5V Rp TTL CMOS Abb. 7.41: Übergang von TTL auf CMOS Der Widerstand Rp darf gross werden, da er praktisch nur durch den sehr kleinen Eingangsstrom der CMOS-Schaltung belastet wird. Damit aber die Geschwindigkeit der Schaltung nicht leidet, sollte man den Widerstand eher klein wählen, damit die Eingangskapazität der CMOS-Schaltung rasch aufgeladen wird. Die Schaffung der Reihe 74HCTxx (das T steht für TTL-Kompatibilität) hat auch noch dieses letzte Problem aus der Welt geschafft; diese Reihe ist vollständig kompatibel zu den TTL-Reihen und arbeitet mit denselben Pegeln. Der Aufbau von gemischten Schaltungen ist problemlos und erfordert keine pull up Widerstände mehr. Die Reihen 74HCxx und 74HCTxx sind heute erste Wahl, wenn es nicht auf besonders hohe Geschwindigkeit ankommt. 38 Feldeffekt-Transistoren 7.6 Übungsaufgaben und Kontrollfragen 7.6.1 Übungsaufgaben 28. Daten des JFET: UP = -2 ... -6 V, IDSS = 3 .. 9 mA +12 V IDA 1 MΩ 1 kΩ Abb. 7.42: Schaltung zu Aufgabe 28 In welchen Grenzen kann der Ruhestrom IDA schwanken? 29. Daten des JFET: UP = -3 ... -6 V, IDSS = 4 ... 8 mA +24 V R1 R2 IDA RS Abb. 7.43: Schaltung zu Aufgabe 29 Gesucht sind der Sourcewiderstand RS und das Verhältnis R1/R2 für einen Ruhestrom IDA = 2 mA ± 10%. 30. UDD RD C1 u1 RG RS CS Abb. 7.44: Schaltung zu Aufgabe 30 u2 7.6 Übungsaufgaben und Kontrollfragen 39 Gesucht ist die untere Grenzfrequenz fg dieser Verstärkerstufe. Der Kondensator C1 soll bei der Rechnung vernachlässigt werden, also für alle Frequenzen als Kurzschluss betrachtet werden. 31. UDD RD C u1 RG RS u2 Abb. 7.45: Schaltung zu Aufgabe 31 Berechne die Spannungsverstärkung dieser Schaltung (Hinweis: Man versuche, die „ideale“ Verstärkung -RD/RS auszuklammern) und vergleiche das Resultat mit dem der entsprechenden Schaltung mit bipolaren Transistoren (Emitterschaltung mit Gegenkopplung). 32. UCC R1 C u1 R2 RC u2 Abb. 7.46: Schaltung zu Aufgabe 32 Berechne mit Hilfe der Kleinsignalersatzschaltung die Spannungsverstärkung dieser Verstärkerstufe. 33. An einem n-Kanal-MOS-FET wurden die folgenden Wertepaare für ID und UGS gemessen (im Abschnürbereich): UGS /V 3.3 3.39 3.51 3.59 3.7 3.95 ID /mA 25 50 100 150 250 500 Bestimme daraus die Schwellspannung Uth und die FET-Konstante K. 40 Feldeffekt-Transistoren 7.6.2 Fragen zur Lernkontrolle Es wird erwartet, dass die folgenden Fragen ohne im Buch nachzuschlagen beantwortet werden können. 1 Weshalb haben p-Kanal-FET bei gleicher Geometrie schlechtere Eigenschaften als n-Kanal-Transistoren und welches sind diese Eigenschaften? 2 Weshalb darf bei einem n-Kanal-JFET die Spannung UGS nicht positiv werden? Was geschieht, wenn diese Bedingung verletzt wird? 3 Unter welchen Bedingungen ist die Transferkennlinie verwendbar? 4 Wie lautet die FET-Gleichung für einen JFET im Abschnürbereich? 5 In welcher Grössenordnung liegen die möglichen Werte für IDSS bei JFET? 6 Nenne Synonyme (andere Bezeichnungen) für selbstleitende bzw. selbstsperrende FETs. 7 Welches ist das Hauptanwendungsgebiet für MOS-FETs? 8 Sind JFET empfindlich auf statische Aufladung? 9 Wie verhält sich der Stromverbrauch von CMOS-Schaltungen in Abhängigkeit von der Taktfrequenz? 10 Welche CMOS-Familie ist vollständig kompatibel zu den TTL-Familien?