ADAM Research Berechnungen und Dienstleistungen

Werbung

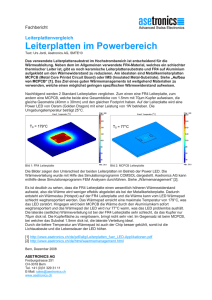

ADAM Research Berechnungen und Dienstleistungen II. Mindeststrombelastbarkeit von Leiterbahnen Kritik an der klassischen IPC-2221 und der neuen IPC-2152 Die Design-Richtlinie IPC-2221 (=MIL-STD-275) (Bild 1) ist die klassische Datenquelle für die GleichstromTemperaturbelastbarkeit von Leiterbahnen: welcher Strom führt zu welcher Temperatur? Die Messungen dazu stammen vom National Bureau of Standards aus den späten 1950er Jahren. Bild 1: Die alte IPC 2221 (Kurven und blaue Punkte zu 20 K) und neue IPC-2152 (gelbe Punkte zu 20 K) führen meistens zu Überdimensionierung von Leiterbahnen. Vorsicht: der dort angegebene Temperatur-Strom-Zusammenhang gilt nur unter folgenden Bedingungen: • Es gibt nur eine geradlinige strombelastete Leiterbahn auf der Leiterplatte • Die Leiterbahndicke ist 35 µm • Sie befindet sich auf einer 2-lagigen 1.6 mm dicken FR4 Leiterplatte in natürlicher Konvektion und freier Abstrahlung • Die Leiterplatte hat eine 35 µm Kupferlage auf der Rückseite Ein wesentliches, zweites Manko der Original IPC-2221 Charts (Raubkopie bei: (http://www.ultracad.com/ipcchart.htm) ist die x-Achse des Diagramms. Diese ist der Leiterquerschnitt = Breite mal Dicke, was bedeutet, dass Leiter mit dem gleichen Querschnitt (egal, ob breit und dünn oder hoch und dick) die gleiche Temperatur bei gleichem Strom haben müßten. Da aber der Wärmeeintrag in die Leiterplatte und damit die darauffolgende Kühlung durch Spreizung und Wärmeabgabe von der Grundfläche abhängt, ist bei gleichem Strom eine breite Leiterbahn immer kühler als eine schmale, auch wenn sie den gleichen Querschnitt haben. Also muß man für Leiterbahnen, deren Dicke anders ist als 35 µm, richtigerweise den in den IPC Charts abgelesenen Strom erst mit Hilfe des Jouleschen Gesetzes umrechnen. Die richtige Umrechnungsformel lautet Id = d (in µm) ∗ I IPC − Chart . 35µm Ein kleines Beispiel: verglichen mit einer 35 µm dicken Leiterbahn kann eine 70 µm dicke Leiterbahn bei gleicher Temperatur und gleicher Leiterbreite den 1.4-fachen Strom tragen. Noch einen, allerdings gewaltigen Irrtum enthält die IPC-2221 beim Teildiagramm für sog. Internal Conductors. Demnach soll eine Leiterbahn auf einer Innenlage ein de-rating des Stromwerts um (exakt) 50% haben - das ist schlichtweg falsch. Tatsächlich könnten Innenlagen sogar besser gekühlt werden, sollten sich massive Lagen in nächster Nachbarschaft darüber oder darunter befinden. Die neue IPC-2152 ist noch konservativer als die IPC-2221 (gelbe Punkte in Bild 2). Wenn man sich daran hält, wird man die Leiterbahn überdimensionieren. Es sieht so aus, als wäre die benutzte Leiterplatte einlagig. Folgende Zitate (in deutscher Übersetzung beim Shop in www.fed.de erhältlich) daraus sollen den Blick auf die eingeschränkte Benutzbarkeit der IPC-2152 lenken: S. 18: „.. Bei einer derart großen Vielfalt von an Leiterplattenkonstruktionen, Materalien L Umgebungsbedingungen L kann nicht erwartet werden, dass ein einziges Diagramm die Temperaturerhöhung als Funktion des Stroms beschreibt“ S. 20:„Für die Leiterplattentemperatur müssen die Verlustleistung der Bauteile, der Leiter, der Steckverbinder L berücksichtigt werden L“ S. 22: „Falls eine Leiterplatte Kupferlagen aufweist, wird die Temperaturerhöhung niedriger ausfallen. Es wird empfohlen, Kupferlagen für Temperaturreserven des Designs zu nutzen und nicht bei der Dimensionierung der Leiter zu berücksichtigen.“ S. 32:„Kupferlagen, die verschiedene Stellen der Leiterplatte mit Spannung versorgen, müssen häufig hohe Ströme tragen. Diese Kupferlagen weisen nicht selten unregelmäßige Formen auf. Die einfachen Diagramme zur Dimensionierung der Leiter sind hier nur begrenzt anwendbar.“ Fazit: Fragen nach allgemeingültigen Designregeln zur Stromtragfähigkeit können einfach nicht beantwortet werden. Wir führen dafür Detailuntersuchungen am konkreten Leiterbild in seiner geometrischen Umgebung durch. Bild 2: x-Achse= Leiterbahnbreite (mm) , y-Achse=Stromstärke (A) zu 20 K des Leiters über Umgebung. Rote Kurve: reine FR4 Leiterplatte (einlagig), Grüne Kurve: zweilagig nach IPC-2221 mit 35 µm Cu Außenlage auf der Rückseite, hellBlaue Kurve: 4-lagige Leiterplatte mit VDD und GND Cu-Innenlagen zu je 35 µm. Mit numerischen Berechnungsmethoden (Softwareprojekt TRM=Thermal Risk Management), die die Wärmeabgabe durch Strahlung und Konvektion berücksichtigen, kann man diese Messungen sehr gut reproduzieren und auf andere Leiterplattenaufbauten anwenden. Bild 2 zeigt den Zusammenhang zwischen Stromstärke und Temperatur (bei 20 °C Umgebungstemperatur) für eine Leiterbahnbreite von 6 mm und 35 mu Dicke. Je höher der Kupferinhalt in der Leiterplatte ist, d.h. je besser die Wärmespreizung ist, desto mehr Strom kann über die Leiterbahn (bei gleichem Temperaturniveau) transportiert werden. Die Kurven aus der IPC-2221 stellen aus heutiger technologischer Sicht einen Minimalstrom dar, der zu einer sehr konservativen Auslegung von (zu breiten) Leiter- bahnen führt. Als Ergebnis unserer berechneten Parameterstudien scheint die Temperaturerhöhung einer Leiterbahn auf organisch basierten Leiterplatten einem Gesetz der Art b ∆T ≈ B LP ∗ mm −1.45 −1 d ∗ I 2 ∗ 35 µ m zu gehorchen. In dieser Formel ist b die Breite der Leiterbahn in mm und d deren Dicke in µm. Der Koeffizient BLP ist vom Lagenaufbau der LP abhängig und gleich 3.6 für eine ein-lagige LP, 1.7 für die zweilagige IPC-Leiterplatte und kleiner als 1.5 für Multilayer. Je kleiner der B-Wert ist, desto höher ist die Strombelastbarkeit. Die obige Formel gilt auch für FlexLPs, jedoch für Keramiksubstrate (DCB) ist der Exponent von b etwa -1.1. [Auszug aus einem Artikel f. die ElektronikPraxis Heft 2 Jan 2010] Welcher Strom welche Temperatur auf dem konkreten Layout und Boardaufbau verursacht, kann man nur mit detailgetreuer Simulation berechnen, z.B. mit unserem Projekt „TRM“.