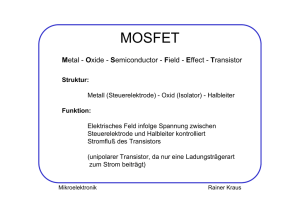

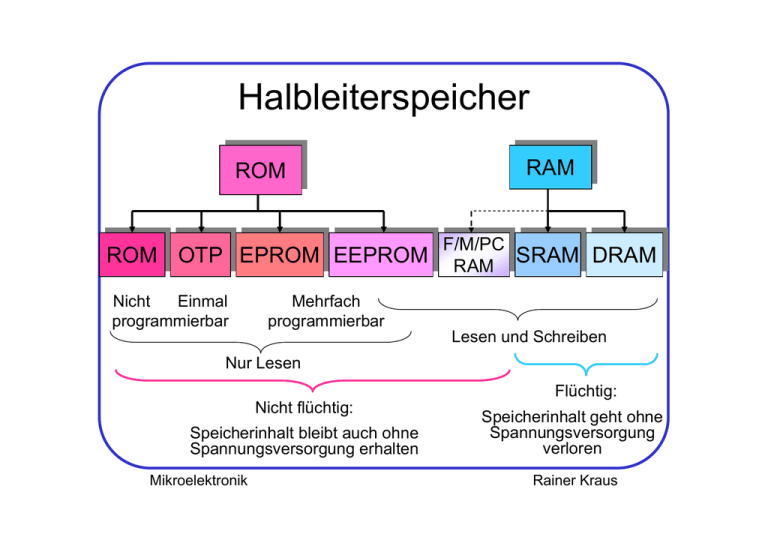

Halbleiterspeicher

Werbung

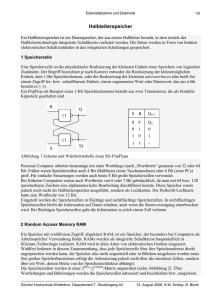

Halbleiterspeicher RAM RAM ROM ROM F/M/PC F/M/PC SRAM DRAM ROM OTP EPROM EEPROM ROM OTP EPROM EEPROM RAM RAM SRAM DRAM Nicht Einmal programmierbar Mehrfach programmierbar Lesen und Schreiben Nur Lesen Flüchtig: Nicht flüchtig: Speicherinhalt bleibt auch ohne Spannungsversorgung erhalten Mikroelektronik Speicherinhalt geht ohne Spannungsversorgung verloren Rainer Kraus ROM / RAM ROM (Read Only Memory) : nur Lesen von Daten beliebiger Speicherzellen ist uneingeschränkt möglich in Zellen von EEPROMs (Electrically Erasable and Programmable ROM) können zwar Daten geschrieben und mehrfach geändert werden, Anzahl der Schreibvorgänge ist jedoch begrenzt (bis zu 106 mal), und Schreiben erfordert mehr Zeit als Lesen, wird daher eher Programmieren als Schreiben genannt RAM (Random Access Memory) : beliebiger Zugriff auf jede Speicherzelle, Lesen und Schreiben von Daten uneingeschränkt möglich Mikroelektronik Rainer Kraus ROM - Speicherzelle ROM - Zelle für „0“ ROM - Zelle für „1“ BL BL WL WL Kontakt BL : Bitleitung WL : Wortleitung Herstellungsprozeß bis zur Kontaktierung für alle ROMs gemeinsam individuelle Programmierung durch selektive Kontaktierung der Zellen (Speicherung der Daten) Mikroelektronik Rainer Kraus Speichermatrix eines ROMs BL2 BL1 0 1 ≈ WL2 ≈ 1 ≈ ≈ 0 1 ≈ WLn 1 Mikroelektronik 0 1 BL--Dekoder Dekoder (Spalten) (Spalten) BL WL WL--Dekoder Dekoder (Zeilen) (Zeilen) ≈ WL1 BL Adressen WL - Adressen BLn 0 Daten Rainer Kraus Lesen Lesen einer „0“ Lesen einer „1“ BL BL WL WL U U WL BL BL WL t Vorladen der BL Mikroelektronik Lesen der Speicherzelle t Vorladen der BL Lesen der Speicherzelle Rainer Kraus DRAM - Speicherzelle DRAM : Dynamic Random Access Memory BL WL Gespeicherte Information: Ladung QS = CS US US CS Speicherkapazität Schreiben : Spannung der Wortleitung UWL > UDD + UT (UT : Einsatzspannung des Auswahltransistors) Spannung der Bitleitung UBL = 0 oder UBL = UDD UWL = 0 : Information gespeichert, 0: US = 0, 1: US = UDD Mikroelektronik Rainer Kraus Speicherzelle Mikroelektronik Rainer Kraus Lesen BL BL Ladungsausgleich zwischen CS und CBL WL WL US CBL CS CBL 3 2 UBL 1 0 1n Lesen einer „1“ 2n 3n Zeit [s] Mikroelektronik 4n 5n Spannung [V] US 4 0 CS 5 5 Spannung [V] US 4 3 UBL 2 1 0 0 US 1n Lesen einer „0“ 2n 3n Zeit [s] 4n 5n Rainer Kraus BL Lesesignal WL US CBL CS Verhältnis CS zu CBL : 1:7 bis 1:15 Beim Lesen verteilt sich Ladung QS auf Kapazität der Bitleitung CBL und Speicherkapazität CS → Signal auf Bitleitung (Lesesignal) : für Vorladespannung UBL = ½ UDD : Mikroelektronik ΔU BL CS (U BL − U S ) = C S + C BL ΔU BL CS U DD ≈± CS + CBL 2 Rainer Kraus Leseverstärker φP Spannungsdifferenz zwischen Bitleitung und Referenzbitleitung wird verstärkt WL1 5 BL ≈ ≈ Vorladen der BL WLn Spannung [V] BL 4 Mikroelektronik BL φN BL 3 2 1 0 φN φP 0 2n 4n 6n 8n Zeit [s] Rainer Kraus 10n Refresh Wegen Leckströmen bleibt Speicherladung nicht beliebig lange erhalten In bestimmten Zeitintervallen (Millisekunden) muß deshalb Speicherinhalt erneuert werden: Auslesen der Zelle Verstärken des Signals auf vollen Pegel Zurückschreiben Daher Bezeichnung dynamischer Speicher (DRAM) Mikroelektronik Rainer Kraus Speicher - Aufbau A0 . . An Din DatenDatenpuffer puffer Mikroelektronik Vorladeschaltung Vorladeschaltung ... Adresspuffer Adresspuffer DRAMDRAMSteuerung Steuerung WL WL--Dekoder Dekoder (Zeilen) (Zeilen) RAS CAS WE ... Speicherzellenfeld Speicherzellenfeld ... Leseverstärker Leseverstärker ... I/O I/O BL--Dekoder Dekoder (Spalten) (Spalten) BL DatenDatenpuffer puffer Rainer Kraus Dout 16 MBit DRAM Mikroelektronik Rainer Kraus SRAM Static Random Access Memory Statischer Speicher : gespeicherter Spannungspegel wird aktiv mit Schaltung festgehalten Datenbit und dessen Inverses werden gespeichert Schreiben und Lesen über Bitleitung und inverser Bitleitung Mikroelektronik BL BL Speicherzelle : Flipflop WL 1 1 Rainer Kraus SRAM - Zellen NMOS - Flipflop mit Lastwiderständen (4 - Transistor - Zelle) CMOS - Flipflop (6 -Transistor - Zelle) BL BL BL BL UDD WL UDD WL WL WL 4 - Transistor - Zelle benötigt weniger Platz, hat aber Querstrom und ist empfindlicher gegenüber Störungen Mikroelektronik Rainer Kraus Nichtflüchtige Speicherzellen EPROM - und EEPROM - Zellen: MOSFET mit 2 Gates Ladungsspeicherung auf „Floating Gate“, welches durch umhüllende Oxidschicht von Umgebung völlig elektrisch isoliert ist (Ladungen können länger als 10 Jahre gespeichert bleiben) BL WL Floating Gate Source Steuergate Oxid (Isolator) n n Drain p - Substrat (Bulk) Mikroelektronik Rainer Kraus Gespeicherte Information Floating Gate elektrisch neutral: Floating Gate Steuergate +++++ Source Floating Gate negativ geladen: Oxid Floating (Isolator) Gate Drain IDS Source Steuergate +++++ Oxid (Isolator) Drain IDS UGS Einsatzspannung klein Strom beim Lesen groß Mikroelektronik UGS Einsatzspannung groß Strom beim Lesen klein Rainer Kraus Programmieren Elektronen müssen über isolierende Oxidschicht gebracht werden Isolator: große Energielücke zwischen Leitungs- und Valenzband, Isolator zwischen zwei leitenden Materialien stellt Energiebarriere für Elektronen dar W Überwinden der Energiebarriere: X X Zufuhr ausreichender Energie Y Tunneln durch die Barriere Y WC (Tunnelwahrscheinlichkeit wächst mit Abnahme der Barrierenbreite) x Mikroelektronik Rainer Kraus EPROM X Zufuhr ausreichender Energie: Floating Gate Electrically Programmable ROM Steuergate +++++++ Oxid (Isolator) Drain Source E Hohe Drain-Source-Spannung → hohes elektrisches Feld am Kanalende Elektronen mit sehr hoher Energie („heiße Elektronen“) : Stoßionisation (Generation von Elektron-Loch-Paaren) Ablenkung in Richtung Floating Gate und Überwinden der Barriere Mikroelektronik Rainer Kraus Löschen Entfernen der Elektronen vom Floating Gate: Bestrahlen mit UV - Licht: optische Anregung (Zufuhr der zum Überwinden der Barriere erforderlichen Energie) Inhalte aller Zellen werden gemeinsam gelöscht, danach ist neues Programmieren möglich (einige hundert mal) EPROMs besitzen transparentes Fenster im Gehäuse Speicher ohne dieses Fenster (kostengünstiger) nennt man OTPs (One Time Programmable) Mikroelektronik Rainer Kraus EEPROM Y Tunneln durch die Barriere: Floating Gate Source Electrically Erasable and Programmable ROM Steuergate Oxid (Isolator) Drain Tunnelfenster Tunnelfenster: n p sehr dünne Oxidschicht (wenige Nanometer) bei Anlegen von Spannung tunneln Elektronen zwischen Draingebiet und Floating Gate (in beiden Richtungen möglich) Mikroelektronik Rainer Kraus Tunneln Anlegen hoher Spannung verkürzt Breite der isolierenden Energiebarriere so weit, daß Elektronen hindurchtunneln W WC FG HL WV Floating Gate Oxid x n - HL U FG HL x UFG - HL ≈ 0 : Barriere zu breit für Tunneln, Elektronen auf Floating Gate gespeichert Mikroelektronik UFG - HL >> 0 : UFG - HL << 0 : Barriere schmal für Elektronen im HL Barriere schmal für Elektronen auf Floating Gate Rainer Kraus Floating-Gate-Spannung Änderung der Floating-Gate-Spannung durch kapazitive Kopplung: Steuergate (SG) C1 USG-HL Floating Gate (FG) C2 UFG-HL Halbleiter (HL) ΔU FG−HL C1 = ΔU SG−HL C1 + C 2 Hohe Programmierspannungen (10 - 12 V) können intern auf Speicherchip erzeugt werden, da Tunnelströme sehr gering Mikroelektronik Rainer Kraus Störungen von Nachbarzellen ausgewählte Zelle BLi 10 V WLi BLi+1 5V 10 V Programmieren möglich offen WLi+1 Spannungen beim Programmieren -5V 0V 0V Löschen möglich 0V Mikroelektronik 5V entsprechende Probleme beim Löschen Rainer Kraus EEPROM / Flash-EPROM Flash-EPROM - Zelle EEPROM - Zelle BL BL SL WL WL Zusätzlicher Auswahltransistor Kein Auswahltransistor jede Zelle kann individuell zum Programmieren und Löschen angesteuert werden Programmieren der Zellen individuell aber Löschen gemeinsam Mikroelektronik Rainer Kraus EEPROM / Flash-EPROM Viele Variationen für Programmieren und Löschen: z.B. Tunneln zwischen Floating Gate und Substrat Programmieren mit „heißen“ Elektronen / Löschen durch Tunneln Verschiedene Speicherfeldstrukturen (Flash): Speicherzellen parallel (NOR) Speicherzellen seriell (NAND) Mikroelektronik Rainer Kraus Zeiten Ströme pro Bit Zeit pro Bit Programmieren mit „heißen“ Elektronen Igate ≈ 1 ... 5 nA 1 ... 10 µs Programmieren / Löschen durch Tunneln Igate ≈ 10 pA ≈ 1 ms IDS ≈ 5 ... 50 µA < 100 ns Lesen Mikroelektronik IDS ≈ 100 ... 500 µA Rainer Kraus Umprogrammieren Umprogrammieren: Löschen, (Neu-) Programmieren Verschieben der Einsatzspannung (bei gleichen Spannungspegeln, gleicher Dauer der Programmier- oder Löschpulse) - nicht identisch für alle Zellen (Gefahr des Überlöschens (over erase) einiger Zellen) - abhängig von bereits erfolgter Anzahl der Umprogrammierungen Î Programmier- / Löschalgorithmen - mehrere (variable) Programmier-/Löschimpulse - Kontrollieren des Speicherzellenstroms nach jedem Impuls Flash-EPROM: alle Zellen müssen zuerst in programmierten Zustand gebracht werden Mikroelektronik Rainer Kraus Datenhaltung 10 Jahre Datenhaltung gefordert Leckströme reduzieren gespeicherte Ladung Hohe Anzahl von Umprogrammierungen erhöht Leckströme (Degradation, z.B. Schädigung des Oxids) Anzahl möglicher Umprogrammierungen begrenzt: 105 - 106 Mikroelektronik Rainer Kraus Halbleiter - Speicherzellen Flüchtig: BL Nicht - Flüchtig: BL DRAM WL ROM WL BL BL SRAM WL 1 Fest verdrahtet (programmiert) nur Lesen EPROM (Flash-EPROM) BL WL EEPROM BL SL WL 1 Lesen und Schreiben Mikroelektronik Lesen und elektrisch Programmieren Rainer Kraus Neue Zellen (Speicher) Eigenschaften: sowohl nicht flüchtig als auch beliebiges Schreiben und Lesen mit hoher Geschwindigkeit (RAM) FRAM: ferroelektrisch, Isolatormaterial mit zwei stabilen Polarisationszuständen, variable Kapazität MRAM: magnetoresistive, sehr dünner Isolator zwischen zwei magnetischen Schichten, Tunneln (Widerstand) abhängig von Magnetisierungsrichtung PCRAM: phase change, Wechsel zwischen amorphem und polykristallinem Zustand, Änderung des Widerstandes Mikroelektronik Rainer Kraus Transistor als Verstärker UDD (5V) Übertragungsfunktion: R UA D UE G UA [V] 5 4 3 2 1 S 0 0 1 0 U E (t ) = U E ,DC + u E (t ) 3 4 UE [V] U A (t ) = U A,DC + u A (t ) u A (t ) ≈ Au E (t ) Mikroelektronik 2 A: Verstärkung Rainer Kraus 5 Kleinsignal - Parameter I DS (t ) = I DS ,DC + ids (t ) ∂I DS ∂I DS ∂I DS ids (t ) ≈ u gs (t ) + u ds (t ) + u sb (t ) U GS U DS U SB = g mg u gs (t ) + g 0 u ds (t ) + g mb u sb (t ) 4.0 10 Gatesteilheit gmg 6 4 2 0 1 2 3 UGS [V] Mikroelektronik 3.0 Arbeitspunkt 4 5 IDS [mA] IDS [mA] 8 0 Arbeitspunkt Ausgangsleitwert g0 2.0 1.0 0.0 0 1 2 U DS 3 [V] 4 5 Rainer Kraus Kleinsignal - Ersatzschaltung ids = g mg u gs + g 0 u ds + g mb u sb Drain Gate gmgugs g0 gmbusb Bulk Source Mikroelektronik Rainer Kraus Verstärkung Verstärkung bei kleinen Frequenzen : (Kapazitäten vernachlässigbar) UDD (5V) u A = − R ids R uA uE 0 Mikroelektronik i ds = g mg u E + g 0 u A R g mg uA A= =− uE 1+ R g0 Rainer Kraus Transistor und Stromquelle Verstärkung bei kleinen Frequenzen : (Kapazitäten vernachlässigbar) UDD I DS = I 0 = const → I0 uA =0 uE 0 Mikroelektronik ids = g mg u E + g 0 u A g mg uA A= =− uE g0 Rainer Kraus Frequenzverhalten u (t ) = u 0 exp( jωt ) UDD ω = 2πf I0 C uE ids ids = g mg u E + g 0 u A = − iC Mikroelektronik uA iC du = jω u 0 exp( jωt ) dt = jω u du A iC = C = Cjω u A dt g mg uA A= =− uE g 0 + jω C Rainer Kraus Stromspiegel UDD Tp2 Transistor Tp1 in Sättigung ! UDD S Ip2 G Tp1 D S Ip1 G D I0 0 I0 : UA D UE G Tn Referenzstrom W p1 Lp1 I p1 = I p2 Wp 2 Lp 2 IDSn S 0 Mikroelektronik Rainer Kraus Differenzverstärker UDD UA I0 UE1 UE2 I0 0 Mikroelektronik 0 Rainer Kraus Verstärkung Verstärkung A in Abhängigkeit der Frequenz 5 3000 4 2500 Verstärkung UA [V] Übertragungsfunktion (UE1 = 2V) 3 2 1 2000 1500 1000 500 0 1.90 1.95 2.00 UE2 [V] 2.05 2.10 0 1k 10k 100k 1M 10M 100M Frequenz [Hz] uA Amplitude (U A ) A= = u E Amplitude (U E1 − U E 2 ) Mikroelektronik Rainer Kraus 1G Operationsverstärker UDD UDD UE2 U´A UA UE1 UGS UE2 UE1 UA I0 0 Differenzverstärker Mikroelektronik x·I0 0 Source-Folger Rainer Kraus Verstärkung Verstärkung A in Abhängigkeit der Frequenz 5 3000 4 2500 Verstärkung U´A / UA [V] Übertragungsfunktion (UE1 = 2V) 3 2 1 2000 1500 ohne mit SourceFolger 1000 500 0 1.90 1.95 2.00 UE2 [V] Source-Folger: Mikroelektronik 2.05 2.10 0 1k 10k 100k 1M 10M 100M Frequenz [Hz] keine Spannungsverstärkung sondern Pegelverschiebung und höherer Strom (schnelleres Umladen von Lastkapazitäten) Rainer Kraus 1G DB / Phase 20 log (|A|) [dB] 80 60 40 20 0 Phase (UA,UE2) [Grad] -20 1k 10k 100k 1M 10M 100M 1G Frequenz [Hz] 180 150 uA 120 90 60 uE2 30 0 1k 10k 100k 1M 10M 100M 1G Phase Frequenz [Hz] Mikroelektronik Rainer Kraus Rückgekoppelter Verstärker R2 R1 Stabilitätsbedingung für Rückkopplung des Ausgangs auf Eingang: Verstärkung ≤1 (≤0 dB) wenn Phase = 0 - U2 UE2 U1 UA + UE1 U E 2 = U E1 für A→∞ U A − U 1 = R2 I U 1 − U 2 = R1 I Mikroelektronik R2 (U 1 − U 2 ) U A = U1 + R1 Rainer Kraus Halbleitertechnologie Schichtherstellung und Strukturierung Schichten: Halbleiter: Substrat, Epitaxie Isolatoren Metalle, Polysilizium Verfahren: Abscheiden aus der Gasphase (CVD) Aufdampfen, Sputtern Schicht wird auf Oberfläche aufgebracht Oxidation Schicht wächst in Tiefe Diffusion, Implantation Mikroelektronik Rainer Kraus Herstellung der Siliziumscheiben Sand (SiO2) reines polykristallines Silizium aus Siliziumschmelze wird monokristalliner Stab gezogen Monokristalliner Siliziumstab wird in Scheiben (Wafer) zersägt Mikroelektronik Rainer Kraus Epitaxie Wachstum einer Siliziumschicht auf monokristallinem Substrat mit Hilfe der Gasphasenabscheidung (CVD, chemical vapour deposition) Epitaxiereaktoren SiCl2 H2 HCl Si - Epitaxieschicht Silizium - Substrat Mikroelektronik Temperatur 1000°C - 1200°C Dotierstoffe für Epitaxieschicht sind Gas zugefügt Rainer Kraus Thermische Oxidation O2 SiO2 Si - Epitaxieschicht Silizium - Substrat Temperatur 900°C - 1200°C Reaktionskammer (Oxidationsofen) Mikroelektronik Rainer Kraus Abscheiden aus Gasphase CVD: chemical vapor deposition Isolatoren: Oxide, Nitrid (Si3N4) Halbleiter auf Halbleiterkristall: Epitaxieschicht auf Isolator: Polysilizium (polykristallines Si) Metall: Wolfram (Füllen von Kontaktlöchern) Metall 2 W Oxid Metall 1 Mikroelektronik Rainer Kraus Abscheiden von Metall Aluminium, Kupfer, Silizide (Metall-Silizium-Verbindungen) Aufdampfen: Metall wird in Vakuum verdampft Sputtern: hohes elektr. Feld ionisiert Argon, beschleunigt + Ionen auf Target Target (Metall) Metallatom Ar+ Si-Scheibe Pumpe Argon Mikroelektronik Rainer Kraus Strukturierung Schaltungsdesign Geometriedaten für verschiedene Prozessschritte Maskenlayout und -herstellung Lithographie Struktur der Masken wird auf Silizium-Scheiben übertragen Ätzen lokales Dotieren lokale Oxidation Mikroelektronik Rainer Kraus Lithographie Standard bisher optische Belichtungsmethoden Aufbringen von Photolack Belichten Maske Photolack SiO2 Silizium Mikroelektronik Rainer Kraus Ätzen Entwickeln des Photolacks (belichtete Gebiete werden abgelöst) Photolack SiO2 Silizium Ätzmittel (z.B. Säure) Photolack SiO2 Wegätzen der Schicht, die nicht vom Photolack geschützt wird Mikroelektronik Silizium Rainer Kraus Diffusion / Implantation Dotierung einzelner Halbleitergebiete erfolgt durch Diffusion oder Ionenimplantation Diffusion Implantation Ionen Dotiergas Photolack SiO2 Silizium Silizium erhöhte Temperatur nötig 900°C - 1200°C bessere Regelbarkeit der Dotierung Mikroelektronik Rainer Kraus Ionen - Implantation Anlage für die Ionenimplantation Mikroelektronik Rainer Kraus Gehäuse / Bonden Bonddrähte: Verbindungen zwischen Chip und Gehäuseanschlüssen Mikroelektronik Rainer Kraus CMOS - Prozeß (die wesentlichen Schritte von einigen hundert erforderlichen) Maske n - Wanne p - Epitaxie p+ - Substrat Dotierung der n-Wanne durch Ionen-Implantation und anschließender Diffusion Maske SiO2 p n Aufwachsen von Dickoxid (lokale Oxidation) p+ Mikroelektronik Rainer Kraus CMOS - Prozeß Poly-Si SiO2 p n Oxidation zur Erzeugung des Gateoxids, Abscheiden von Poly-Si p+ Maske Photolack p n Wegätzen von Poly-Si mit Photolack-Maske p+ Mikroelektronik Rainer Kraus CMOS - Prozeß Arsen n +Dotierung p n Implantation von Donatoren (Arsen) für Source/Drain der NMOS-Transistoren und den n-WannenKontakt p+ als Maske wirken Photolack, Poly-Si und Dickoxid Bor p+Dotierung p n p+ Mikroelektronik Implantation von Akzeptoren (Bor) für Source/Drain der PMOS-Transistoren Rainer Kraus CMOS - Prozeß SiO2 Abscheiden von SiO2 p n p+ Ätzen der Kontaktlöcher Aluminium Abscheiden von Metall (Al) p n p+ Mikroelektronik Metallätzung zur Erzeugung der verbindenden Leiterbahnen Rainer Kraus Masken - Layout Masse CMOS - Inverter VDD n-Wanne Eingang n+ n+ p+ Ausgang Mikroelektronik Rainer Kraus Schaltungsentwurf System technologieunabhängig Logik Bauelemente Technologie Schaltung Redesign Layout Extraktion parasitärer Kapazitäten und Widerstände Herstellung Test Mikroelektronik Fehlerdiagnose Parameterextraktion Rainer Kraus CAD Rechnereinsatz bei der Schaltungs- und Bauelemente-Entwicklung auf verschiedenen Entwurfs- und Realisierungsebenen: System Spezifikation (Anforderungen, Struktur, Verhalten) Mikroelektronik Logik Logiksimulation, Optimierung Schaltungen Schaltungssimulation, Layout, Test Bauelemente Prozeßsimulation, Baulementesimulation, Messung Rainer Kraus Logik- / Schaltungs-Simulation Logiksimulation: Schaltungssimulation: Logische Funktionen: Zustände 0 und 1 (Bool´sche Algebra), hochohmig, undefiniert Analysen: DC, AC, Transient, Noise (Rauschen), Monte Carlo (Statistik infolge Parameterstreuungen) Timing: Verzögerungen Nichtlineare Modelle der Bauelemente Spannung [V] Logischer Zustand 5 0 5n Mikroelektronik 10n 15n Zeit [s] 4 3 2 1 0 0 5n 10n 15n Zeit [s] Rainer Kraus Prozeß- / Device-Simulation Numerische Lösung der Prozeß- und Halbleitergleichungen Prozeß- (Technologie-) Simulation: Diskretisierungsgitter Analyse der erforderlichen Schritte und optimalen Parameter für den Herstellungsprozeß Dotierung Device(Bauelemente-) Simulation: Potentiallinien Mikroelektronik Analyse der elektrischen Eigenschaften von Halbleiterbauelementen Rainer Kraus Layout Design der Masken für Herstellungsprozeß Überprüfen der elektrischen Regeln (Verbindungen) Überprüfen der Entwurfsregeln Schaltungsextraktion mit parasitären Widerständen und Kapazitäten Entwurfsregeln: minimale Breite minimaler Abstand minimale Kanallänge, -weite minimale Kontaktlochgröße Mikroelektronik Rainer Kraus Programmierbare Logik FPGA Field Programmable Gate Array für geringe Stückzahlen, Prototypen etc. Integrierte Schaltung mit logischen Zellen, Matrix von Verbindungsleitungen und programmierbaren Schaltern, Auswahl von Zellen und deren Verbindungen ermöglicht Realisierung gewünschter Schaltung Programme (Verilog, VHDL) zur Umsetzung (Entwurf nur auf System- und Logikebene) Vorteil: schneller Entwurf, flexibel, kostengünstig Nachteil: große Fläche, geringe Geschwindigkeit Mikroelektronik Rainer Kraus 16 G 4G Integration Transistoren pro Chip Speicher (DRAM) 10 9 Prozessor 1G 256 M 10 6 Pentium 1M 10 6 i486 UltraSpark 1000 Pentium 1K i486 1 1970 1980 1990 2000 2010 Rechenleistung MIPS (Million Instructions per Second) Trends der Integration Jahr Mikroelektronik Rainer Kraus Strukturverkleinerung Zunahme von Integrationsdichte und Rechenleistung (Geschwindigkeit) ist in erster Linie durch Strukturverkleinerung möglich 10 μm 1M Strukturgröße 1 μm DRAM 256 M 1G 0,1 μm Wellenlänge des Elektrons 10 nm 1 nm Wellenlänge von UV-Licht Moleküle Quantenbereich NanoElektronik Atome 1970 1980 1990 2000 2010 Jahr Mikroelektronik Rainer Kraus Probleme und Grenzen Verkleinerung der Transistorstrukturen: Dicke des Gateoxids: Tunnelstrom, wenn dox < 3 nm, bis dox = 1,5 nm aber noch tolerierbar Gate Source Drain Substrat Widerstände von Source und Drain: Verkleinerung der Transistorlänge nicht mehr sinnvoll, wenn Widerstände Strom begrenzen Kurzkanaleffekte: Abnahme der Einsatzspannung, minimale Einsatzspannung UT ≈ 0,3 V (bereits erreicht), Leckströme zu groß, wenn UT kleiner Streuungen der Einsatzspannung Lmin ≈ 25 nm : TBit - DRAM möglich (1012 Bit) ! Mikroelektronik Rainer Kraus Neue Transistorstrukturen Fin-FET Isolator mit großer Dielektrizitätskonstante Drain Gate SiO2 Source Tripel- (Doppel-) Gate SoI: Silicon on Insulator Mikroelektronik Rainer Kraus Leistungsverbrauch Pdyn = f C U 2 DD C = 0,1 fF/Transistor 109 Transistoren/cm2 UDD = 1V 106 Transistoren/cm2 Leistung [W/cm2] 100 Max. Wärmeabfuhr bei Flüssigkeitskühlung 10 Max. Wärmeabfuhr bei Luftkühlung 1 0.1 106 109 Frequenz [Hz] Mikroelektronik 1012 25 nm MOSFET: Verzögerung eines Gatters: einige ps (mehrere 100 GHz) Rainer Kraus Herstellung Lithographie: Belichtung mit Röntgen- und Elektronenstrahlen Problem bei Strukturierung durch Ätzen: hohe Defektdichte - geringe Ausbeute (wenig fehlerfreie Chips pro Si-Scheibe) Evtl. Alternative: geordnetes Wachsen von Strukturen Si Poly-Si Nitrid SiO2 Silizium Mikroelektronik Rainer Kraus Quanteneffekte Strukturen < Wellenlänge der Elektronen (20 nm): (Quantenfläche, Quantendraht, Quantenpunkt) Elektronen verlieren Teilchencharakter und verhalten sich wie Wellen Effekte: Tunneln, Interferenz, diskrete Energiezustände z.B. Transistorstrom nur bei bestimmten Spannungspegeln Quantenbauelemente: Ein-Elektron-Transistor Drainstrom Gate Source Drain Isolator Gatespannung Mikroelektronik Ein-Elektron-Speicherzelle Rainer Kraus Auswirkungen ? Mikroelektronik verändert unsere Welt Mikroelektronik Rainer Kraus