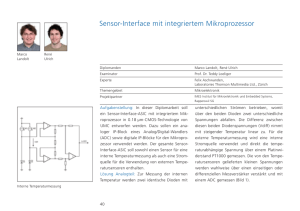

Geschichte des Transistors

Werbung

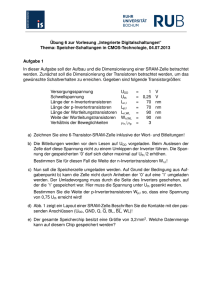

MOSFET Metal - Oxide - Semiconductor - Field - Effect - Transistor Struktur: Metall (Steuerelektrode) - Oxid (Isolator) - Halbleiter Funktion: Elektrisches Feld infolge Spannung zwischen Steuerelektrode und Halbleiter kontrolliert Stromfluß des Transistors (unipolarer Transistor, da nur eine Ladungsträgerart zum Strom beiträgt) Mikroelektronik Rainer Kraus MOS - Transistor (Material der Steuerelektrode ist meist nicht Metall sondern hochdotiertes polykristallines Silizium) Gate Drain Source n n Struktur: p - Substrat (Bulk) G Symbol: S D NMOSTransistor B Mikroelektronik Rainer Kraus Transistorkanal Inversionsschicht von Elektronen: leitender Kanal zwischen Source und Drain (N-Kanal-Transistor, NMOS) Gate Source n Drain n Raumladungszone des pn-Übergangs Verarmungszone der MOS-Struktur p - Substrat (Bulk) Mikroelektronik Rainer Kraus Inversionsladung Gate Source n 0 Udep USB p - Substrat (Bulk) x Udep polt pn-Übergang an Halbleiteroberfläche in Durchlassrichtung Elektronen werden von der Source ins Substratgebiet unterm Gate injiziert ⎛ qU pn ( x = 0) ⎞ ni2 ⎛ q(U dep − U SB ) ⎞ ⎟⎟ = ⎟⎟ n p ( x = 0) = n po exp⎜⎜ exp⎜⎜ kT kT ⎝ ⎠ NA ⎝ ⎠ n p ( x = 0) = N A Mikroelektronik U dep = 2 kT N A ln + U SB = 2φF + U SB q ni Rainer Kraus Transistor - Einsatzspannung Gate Source n Uox Udep USB U dep ≈ 2φF + U SB Qdep ≈ − A 2ε oε Si qN A (2φF + U SB ) p - Substrat (Bulk) Qn = QHL − Qdep Inversion: QHL = −CoxU ox ( U ox = U GB − U FB − U dep Qn = −Cox (U GB − U FB − (2φF + U SB ) ) − − A 2ε oε Si qN A (2φF + U SB ) ⎛ ⎛ A = −Cox ⎜⎜ U GS − ⎜ U FB + 2φF + Cox ⎝ ⎝ ⎞⎞ 2ε oε Si qN A (2φF + U SB ) ⎟ ⎟⎟ ⎠⎠ UT Mikroelektronik ) Einsatzspannung Rainer Kraus Transistorstrom Gate Source Drain n n E p - Substrat (Bulk) UGS > UT : Injektion von Elektronen aus Source in Kanal UDS > 0 : Drift der Elektronen im Kanal infolge Potentialdifferenz, Strom zwischen Drain und Source Gate-Source-Spannung bestimmt Menge der Elektronen für Stromfluß, Drain-Source-Spannung bestimmt deren Geschwindigkeit Mikroelektronik Rainer Kraus Bänderdiagramm Source n UGS = 0 Energiebarriere ΔW zwischen Source und Substrat (Diffusionsspannung des pn-Übergangs) p-Substrat unterm Gate WC WV Diff UGS > UT WC Energiebarriere reduziert durch Udep WV Mikroelektronik Drain n ΔW Drift ΔW Rainer Kraus Kanalladungsdichte Gate W ⋅L = A L W Drain Source n n z y p x Elektronenladung pro Fläche im Kanal für UGS > UT und UDS = 0: Qn C ox (U GS − U T ) = −cox (U GS − U T ) σn = =− A A Mikroelektronik Rainer Kraus Potentialverlauf im Kanalgebiet Gate Source Drain n n φ Für UDS > 0 Ladungsdichten längs des Kanals nicht konstant, da Potential sich ändert UGB - UFB Udep(y) Uox(y) UK(y) y 0 Mikroelektronik L UK(y) : Spannung zwischen Kanalanfang (y = 0) und Ort y im Kanal Rainer Kraus Potential und Ladungsdichten φ UGB - UFB Udep(y) Uox(y) UK(y) y 0 L σ HL ( y ) = −coxU ox ( y ) = −cox (U ox (0) − U K ( y ) ) σ n ( y ) = σ HL ( y ) − σ dep ( y ) ≈ σ HL ( y ) − σ dep (0) = −cox (U GS − U T − U K ( y ) ) Mikroelektronik Rainer Kraus Driftstrom I n = qAnμ n E ∂U K = −Wσ n ( y ) μ n E ( y ) = Wσ n ( y ) μ n ∂y ∂U K = −Wμ n cox (U GS − U T − U K ( y ) ) ∂y Integration von y = 0 bis y = L : 1 2 ⎛ ⎞ I n L = −Wμ n cox ⎜ (U GS − U T )U K ( L) − U K ( L) ⎟ 2 ⎝ ⎠ Mikroelektronik Rainer Kraus Integrationsgrenzen UK(y) UGS - UT = UDSsat UDS y L´ L 0 Integration der Stromgleichung für UDS ≤ UDSsat : bis L und UK(L)= UDS σn(y) für UDS > UDSsat : y 0 bis L´ und UK(L´)= UDSsat L´ L 0 σ n ( y) = −cox (U GS − UT − U K ( y)) gilt nur für UK < UGS - UT für UDS > UDSsat = UGS - UT ist Halbleiterladung im Bereich y > L´ nicht mehr vom Gate gesteuert Mikroelektronik Rainer Kraus Drain - Source - Strom UGS ≥ UT : UDS < UDSsat = UGS - UT : I DS Widerstandsbereich W 1 2 ⎞ ⎛ = μ n cox ⎜ (U GS − U T )U DS − U DS ⎟ L 2 ⎝ ⎠ UDS ≥ UDSsat = UGS - UT : Sättigungsbereich I DS 1W 2 = μ n cox (U GS − U T ) 2 L´ (Langkanaltransistor: L´ ≈ L) Mikroelektronik Rainer Kraus Ausgangs - Kennlinien UDS = UGS - UT Widerstandsbereich 6 UGS= 4V IDS [mA] 5 Sättigungsbereich 4 UGS= 3V 3 2 UGS= 2V 1 0 1V 0 Mikroelektronik 1 2 3 UDS [V] 4 5 Rainer Kraus Übertragungs - Kennlinie 10 UDS = 5V IDS [mA] 8 6 4 UT 2 0 0 1 2 3 4 5 UGS [V] Mikroelektronik Rainer Kraus IDS [mA] Temperaturabhängigkeit 6 5 4 3 2 1 0 T T 0 1 2 3 4 5 UDS [V] Beweglichkeit und Einsatzspannung nehmen mit steigender Temperatur ab: ⎛T μ n (T ) = μ n (To )⎜⎜ ⎝ To Mikroelektronik ⎞ ⎟ ⎟ ⎠ −a U T (T ) = U T (To ) − b(T − To ) Rainer Kraus Unterschwellstrom -3 10 UT -6 IDS [A] 10 Bestimmen (Messen) von UT: I DS W L -9 10 = 10 − 7 A -12 10 0.0 Mikroelektronik 0.5 1.0 UGS [V] 1.5 2.0 Rainer Kraus Kurzkanal - Transistor Kurzkanaleffekte: Kanallängenmodulation, Abhängigkeit der Einsatzspannung von Kanallänge und Drain-Source-Spannung, Abnahme der Beweglichkeit durch hohes E-Feld 4.0m VGS = (0.4, 1.0, 1.5, 2.0)V L=0.25μm Kanallängenmodulation: IDS [A] 3.0m 2.0m 1.0m 0.5m 0.0 0.0 L = 1 + λ (U DS − U DSsat ) L´ 0.5 Mikroelektronik 1.0 1.5 UDS [V] 2.0 2.5 Rainer Kraus Variation der Einsatzspannung 0.6 nMOSFET UT [V] 0.5 0.4 0.3 0.0 Mikroelektronik l = 0.25µm l = 0.21µm l = 0.18µm 0.5 1.0 UDS [V] 1.5 2.0 Rainer Kraus Variation der Einsatzspannung Source n p-Substrat unterm Gate Drain n ΔW WC UDS = 0 WV ΔW Kurzer Transistor WC WV UDS > 0 DIBL Drain Induced Barrier Lowering Absenken der Energiebarriere, Abnahme der Einsatzspannung Mikroelektronik Rainer Kraus PMOS - Transistor Gate Source - - - - - - - - p Drain p E n - Substrat (Bulk) UGS > UFB : Akkumulation von Elektronen UGS < UFB : Verarmungsschicht positiver Donatorionen UGS < UT : (UT < 0) Löcherschicht in Kanal (P-Kanal-Transistor) UDS < 0 : Löcherstrom zwischen Drain und Source, IDS < 0 Mikroelektronik Rainer Kraus PMOS - Kennlinien UDS [V] -4 -1V -3 -2 -1 0 0 UGS= -2V -0.5 UGS= -3V -1 IDS [mA] -5 -1.5 UGS= -4V Mikroelektronik Rainer Kraus Logik - Schaltungen Zustände 0 und 1 entsprechen bestimmten Spannungspegeln, z.B.: 0 = 0V 1 = 5V spannungsgesteuerte Schalter Beispiel UND: A B 5V C + 0 0 1 1 0 1 0 1 0 0 0 1 Mikroelektronik UA (C): S1 (A) 0V, wenn ein oder beide Schalter offen S2 (B) R 0V UA 5V, wenn beide Schalter geschlossen Rainer Kraus MOSFET als Schalter UE = 0 : MOSFET sperrt D UDD (z.B. 5V) UE = UDD : MOSFET leitet, ist in Sättigung, da UDS = UGS G I DS = S = UE UA R 0 UA = 0 V 1W 2 μ n cox (U GS − U T ) 2 L´ β 2 (U G − U A − U T ) UA R U G − U A > UT 2 I DS = I R = damit I DS > 0 UA < UG - UT = UDD - UT Mikroelektronik Rainer Kraus Schaltungen in Serie UDD (z.B. 5V) UE UA1 0 UA2 UA3 Serienschaltung nicht möglich Mikroelektronik ! Rainer Kraus Inverter UDD (z.B. 5V) UE = 0 : MOSFET sperrt (UGS = 0) UA = UDD R UE = UDD : MOSFET leitet UA D UE UA = UDD - RIDS G S Inverter (Negation, NOT - Gatter) E A 0 1 1 0 Mikroelektronik E 1 A 0 0 : Lowpegel (L) 1 : Highpegel (H) Rainer Kraus Dimensionierung UDD R UE UA U A,low 1 ≤ UT 2 R R bestimmt maximalen Strom (→ Schaltgeschwindigkeit) W 1 ⎛ ⎞ μn cox ⎜ (U E ,high − U T )U A,low − U A2 ,low ⎟ L 2 ⎝ ⎠ U A,low U DD − U A,low ≈ = RTransistor R I DS = damit angesteuerter Transistor sicher sperrt → erforderliches W/L für Transistor (L meist Minimalwert der jeweiligen Technologie) Mikroelektronik Rainer Kraus Logik-Gatter NMOS – Transistoren in Serie UDD A B C 0 0 1 1 1 1 1 0 R C B 0 1 0 1 A A NAND – Gatter (NICHT – UND) Mikroelektronik B & C Rainer Kraus Logik-Gatter NMOS – Transistoren parallel UDD A B C 0 0 1 1 1 0 0 0 R C A B A NOR – Gatter (NICHT – ODER) B Mikroelektronik 0 1 0 1 ≥1 C Rainer Kraus Dimensionierung der Transistoren 2 Transistoren in Serie UDD UE1 und UE2 high: R U DS 1 ≈ U DS 2 ≈ UDS1 UE1 UA UE2 UDS2 1 U A ,low 2 → W/L der Transistoren doppelt so groß wie bei einem Transistor (Inverter) n Transistoren in Serie: n-faches W/L Mikroelektronik Rainer Kraus Dimensionierung der Transistoren Transistoren parallel UDD R UE1 UE2 UA W/L wie bei einzelnem Transistor, damit UA,low auch ausreichend niedrig ist, wenn nur ein Transistor leitet Mikroelektronik Rainer Kraus NMOS - Inverter Integrierte Schaltungen: Transistoren leichter realisierbar als Widerstände Nachteil des NMOS-Inverters (oder entsprechend gebauter Logik-Gatter): UE = 0 : UDD (z.B. 5V) D T1 sperrt und T2 sperrt bei UA = UDD - UT2 S da dann UGS, 2 = UT2 → reduzierter Pegel für UA,high Abhilfe: Gatespannung von T2 > UDD oder: Einsatzspannung UT2 < 0 Mikroelektronik T2 G UA D UE G T1 S 0 Rainer Kraus CMOS - Inverter Kombination von NMOS- und PMOS-Transistoren: CMOS-Schaltungen (complementary MOS) UDD (z.B. 5V) Komplementärinverter: S UE = 0 : NMOS-FET sperrt PMOS PMOS-FET leitet G UA = UDD UE UE = UDD : PMOS-FET sperrt NMOS-FET leitet UA = 0 Strom fließt nur beim Umschalten Mikroelektronik D UA D G NMOS S 0 Rainer Kraus Transistor - Symbole NMOS PMOS D S B G G B 0 S UDD D Substratanschlüsse: (Regelfall, Ausnahmen möglich) NMOS an Masse (niedrigste Spannung der Schaltung) PMOS an UDD (höchste Spannung der Schaltung) im Folgenden werden meist Symbole ohne Substratanschlüsse verwendet Mikroelektronik Rainer Kraus CMOS - Inverter NMOS-FET: PMOS-FET: UGSn = UE -UGSp = UDD - UE UDSn = UA -UDSp = UDD - UA USBn = 0 USBp = 0 im statischen Fall: IDSn = - IDSp UDD (z.B. 5V) PMOS G UE S - IDSp D UA D G NMOS IDSn S 0 Mikroelektronik Rainer Kraus Übertragungsfunktion Abhängigkeit der Ausgangspannung UA von der Eingangsspannung UE UE = UGSn UDD - UE = -UGSp 5 IDSn [mA] z.B.: IDSn = - IDSp UE = 3V UDSn = UA 5 UDD = 5V 4 4 UGSn = 3V 3 2 UA 2 UGSp = -2V 1 0 3 -IDSp [mA] 1 0 0 1 U DSn [V] Mikroelektronik 2 3 4 5 -U DSp [V] Rainer Kraus Übertragungsfunktion, Strom 5 1 4 3 3 2 4 1 3 0 0 1.5 2 1 2 3 UA [V] Mikroelektronik 4 5 I [mA] 6 5 4 3 2 4 1 5 0 0 1 UA [V] I [mA] 2 5 1 2 3 4 5 1 2 3 UE [V] 4 5 1.0 0.5 0.0 0 Rainer Kraus Störsicherheit U A [V] 5 4 Störung “0“ 3 Störung “1“ 2 1 0 0 1 2 3 4 5 U E [V] Inverter am unempfindlichsten gegen Störungen des Eingangssignals UE , wenn Umkippen der Ausgangsspannung UA von 1 auf 0 bei UE = ½ UDD erfolgt Mikroelektronik Rainer Kraus Dimensionierung I DSn I DSn 1 Wn 2 = μ n cox (U GSn − U Tn ) 2 Ln 1 Wp 2 I DSp = − μ p cox (U GSp − U Tp ) 2 Lp U DD = − I DSp für U GSn = −U GSp = und U Tn ≈ −U Tp : 2 Wp Wn μn = μp Ln Lp Mikroelektronik μ n Wn = L p μ p Ln Wp μn ≈3 μp Rainer Kraus Schaltverhalten Spannung [V] 5 UE 4 3 UA td2 td1 2 Zeitverzögerung zwischen Eingangsund Ausgangssignal: td1 und td2 1 0 0 10m 5n 10n 15n Zeit [s] Strom [A] 8m 6m -IDSp IDSn 4m 2m 0 0 5n Mikroelektronik 10n 15n Zeit [s] Rainer Kraus Kapazitive Last CL Ausgang einer MOSFET-Schaltung steuert Eingänge anderer MOSFETSchaltungen an Umladen von Kapazitäten: Kapazitive Last Mikroelektronik Rainer Kraus Ladeströme UDD UDD 1 1 - IDSp 0 - IDSp 0 1 UE UA CL UE UA 0 IDSn CL IDSn 0 0 Entladen der Lastkapazität Mikroelektronik Aufladen der Lastkapazität Rainer Kraus 1 MOSFET - Kapazitäten Verbindungsleitungen (Aluminium) n n p Mikroelektronik Rainer Kraus Schaltverhalten NMOS UDD Spannung [V] 5 UE 4 UDD UGS (T2) 3 IDS2 UA 2 UGS 1 0 0 10n 20n 30n Zeit [s] Strom [A] UE UA IDS1 IDS1 6m 4m 2m 0 IDS2 0 10n Mikroelektronik 20n 30n Zeit [s] Rainer Kraus CL Schaltverhalten CMOS Spannung [V] 5 UE 4 3 UA td2 td1 2 1 0 0 10m 5n 10n 15n Zeit [s] -IDSp UA Strom [A] 8m 6m UE -IDSp IDSn 4m IDSn 2m 0 0 5n Mikroelektronik 10n 15n Zeit [s] Rainer Kraus CL Schaltzeiten UA 4 tf 3 8m Strom [A] Spannung [V] 5 tr 2 0 tf 5n ∫I DSn 10n 15n dt ≈ QCL = CLU DD 4m QCL tf ≈ (U DD − UTn ) CL 2 C L ~ WLcox β = Mikroelektronik 0 0 5n 10n 15n ≈ I max t f = β n (U DD − U Tn ) t f 0 4 U DD -IDSp IDSn 2m 1 0 6m βn W μ cox L 1 1 2 4 tr ≈ 2 4 U DD CL 2 U U − ( DD Tp ) β p → Schaltzeiten proportional L2 Rainer Kraus Leistungsverbrauch UDD (z.B. 5V) PMOS G UE In Transistoren wird Leistung verbraucht: S D UA D G NMOS P = I DSU DS - IDSp IDSn Energie ∫ W = Pdt wird in Wärme umgesetzt S 0 Komponenten des Leistungsverbrauchs: Mikroelektronik P = Pstat + Pquer + Pdyn Rainer Kraus Leistungsverbrauch 10m Strom [A] 8m 6m UA IL -IDSp IDSn CL 4m 2m 0 0 5n 10n 15n Zeit [s] I L = − I DSp − I DSn I L = − I DSp − I DSn I quer = − I DSp I quer = I DSn I stat ≈ 0 dU A I L = CL dt (PMOS-FET sperrt oder NMOS-FET sperrt) In CMOS-Schaltung dominiert dynamischer Leistungsverbrauch, da Strom IL überwiegt Mikroelektronik Rainer Kraus Dynamischer Leistungsverbrauch UE UA Frequenz: f = t1 0 Pdyn = − I LU A tP Pdyn = I L (U DD − U A ) 1 tP dU A I L = CL dt Mittlerer dynamischer Leistungsverbrauch in Periode tP : Pdyn tp t1 ⎞ 1⎛ = ⎜⎜ ∫ (− I L )U A dt + ∫ I L (U DD − U A )dt ⎟⎟ tp ⎝ 0 t1 ⎠ U DD 0 ⎞ CL 2 CL ⎛ 2 U DD = f CLU DD = ⎜ ∫ (−U A )dU A + ∫ (U DD − U A )dU A ⎟ = ⎟ tp t p ⎜⎝ U DD 0 ⎠ Mikroelektronik Rainer Kraus Frequenz und Leistung fmax : maximal mögliche Schaltfrequenz 9 fmax [Hz] 10 f max = 6 10 l = 0.25µm l = 0.18µm 0.5 1.0 1.5 2.0 UDD [V] U CC P [W] -9 10 l = 0.25µm l = 0.18µm 0.0 0.5 1.0 1.5 UDD [V] U CC Mikroelektronik 2.0 P/fmax [Ws] -6 10 t P min 15f 10 -12 1 = td1 + td 2 P/fmax : Power-Delay-Product Energie pro Schaltvorgang 3 100.0 1 10f 5f 0 0.0 0.5 1.0 1.5 2.0 UUCC [V] DD Rainer Kraus CMOS NAND / NOR UDD UDD A A B C B B C A B C 0 0 1 1 1 1 1 0 0 1 0 1 A Mikroelektronik A B Komplementärgatter volle Pegel für UA kein statischer Querstrom A B C 0 0 1 1 1 0 0 0 0 1 0 1 Rainer Kraus CMOS AND / OR A B OR (ODER) C B A A B C AND (UND) Mikroelektronik A B Rainer Kraus Alternative für AND / OR A & B A C ≥1 B OR AND C = A⋅ B = A + B A B 1 1 NOT Mikroelektronik C ≥1 NOR C = A + B = A⋅ B A C B 1 1 NOT & C NAND Rainer Kraus EXKLUSIV - ODER (XOR) A B C 0 0 1 1 0 1 1 0 0 1 0 1 A A B B C C = A⊕ B A A A B B B =1 C XOR : Mikroelektronik Summenbildung in Addierern Rainer Kraus CMOS - Logikgatter C B Q = (A • B + C • D) • E + B • C C D A B E Q A C B B D C E Mikroelektronik Q = ((A • B + C • D) • E) • (B • C) = ((A • B + C • D) + E) • (B + C) = ((A • B) • (C • D) + E) • (B + C) = ((A + B) • (C + D) + E) • (B + C) Rainer Kraus Schaltzeiten A , (B) A B C A B Spannung [V] 5 4 C1 3 2 1 0 C2 0 5n Mikroelektronik 15n Zeit [s] Transistoren parallel: Schaltzeit abhängig von Anzahl der leitenden Transistoren 10n C1 : A: 0→1, B=0 C2 : A: 0→1, B:0→1 Rainer Kraus Schaltzeiten B C A D T1 A B C T2 Spannung [V] 5 A oder B und C 4 3 D2 2 D1 1 0 0 D3 5n T3 10n 15n Zeit [s] D1 : A : 0 → 1 , B = 0, C = 0 D2 , D3 : A = 0 , B und C : 0 → 1 D2 : W/L aller NMOS-Transistoren gleich D3 : W/L von T2 und T3 doppelt so groß wie W/L von T1 Mikroelektronik Rainer Kraus Problem bei Signalwechsel A A B CL Spannung [V] B B A 5 4 3 C 2 1 0 0 5n 10n 15n 20n Zeit [s] Temporär falsches Ergebnis für C durch flache Anstiegsflanke von Eingangssignal B Mikroelektronik Rainer Kraus 25n Getaktete Schaltungen UDD φ (Takt) φ=0: Ausgang C wird auf UDD vorgeladen C φ=1: A B Ergebnis der logischen Funktion für C ( C = A·B ) (Entladen der Kapazität auf 0 V oder Highpegel bleibt gespeichert) Eingangssignale dürfen sich nur während φ = 0 ändern ! Mikroelektronik Rainer Kraus Getaktete Gatter in Serie UDD φ (Takt) φ (Takt) A = 1, B = 1, D = 1 φ E B C D Spannung [V] A 5 4 E 3 2 C 1 0 0 2n 4n 6n 8n 10n Zeit [s] Problem: Reduzierter High-Pegel für E möglich, da verzögertes Low-Signal C teilweises Entladen des Ausgangs verursacht Mikroelektronik Rainer Kraus Dominoschaltung UDD A φ φ UDD C C E D E E = C·D = C + D Inverter zwischen getakteten Gattern Spannung [V] B 5 4 C E 2 1 0 Mikroelektronik φ 3 0 2n 4n 6n Zeit [s] 8n 10n Rainer Kraus Dominoschaltung 2 UDD A UDD φ C D φ NMOS- und PMOSLogikgatter wechseln 2 Takte: φ und φ E C Spannung [V] 5 B 3 2 E φ 1 0 Mikroelektronik φ 4 0 2n 4n 6n Zeit [s] 8n Rainer Kraus 10n Zwischenspeicher UDD φ UDD C A φ B φ=0: φ=1: φ vorladen speichern logische Operation Mikroelektronik φ φ C E D φ logische Operation vorladen speichern Rainer Kraus E Dekoder A0 A0 A1 A1 φ Y0 A0 A1 : Adressbits A0 A1 Y0 Y1 Y2 Y3 Y1 0 0 1 1 1 0 0 0 Y2 0 1 0 1 0 1 0 0 0 0 1 0 0 0 0 1 Y3 Mikroelektronik Rainer Kraus PLA Programmierbare Logikanordnung (Programmable Logik Array) : Realisierung beliebiger logischer Funktionen von mehreren Eingangsund Ausgangsvariablen mit 2 Transistormatrizen A A B C D 0 0 1 1 0 1 1 1 0 1 0 1 A B B 1 0 0 1 C Mikroelektronik Rainer Kraus D Programmierung des PLA´s Programmierung: nur die für logische Funktion erforderlichen Transistoren werden kontaktiert A A B C D 0 0 1 1 0 1 1 1 0 1 0 1 A B B 1 0 0 1 C Mikroelektronik Rainer Kraus D Transfergatter - Schaltungen S1 S1 S2 Beispiel : Multiplexer S2 E1 E2 A E3 S1 S2 A 0 0 1 1 E1 E2 E3 E4 0 1 0 1 NMOSTransfertransistoren: kein voller Highpegel am Ausgang E4 Transfertransistoren Mikroelektronik PMOS? Rainer Kraus Pegelherstellung S1 S1 S2 S2 E1 UDD E2 A E3 A E4 Mikroelektronik Rainer Kraus Flip - Flop UDD φ A φ Ai Ai A 2 Inverter deren Ein- und Ausgänge über Kreuz gekoppelt sind φ=0: φ=1: 2 stabile Zustände, Ai = 0, Ai = 1 oder Ai = 1, Ai = 0 d.h. Information ist gespeichert über Transfertransistoren wird neue Information übertragen (Ai = A, Ai = A) Mikroelektronik Rainer Kraus D - Flipflop φ Q D φ=0: Information Q gespeichert φ=1: Q=D φ Mikroelektronik Rainer Kraus Master – Slave - Flipflop D(t) Master φ1 φ2 φ1 φ2 Mikroelektronik φ1 Q = D(ti) Slave φ2 φ1 = 1, φ2 = 0 : Master übernimmt D, Slave speichert φ1 = 0, φ2 = 1 : Master speichert, Slave übernimmt Rainer Kraus Dynamisches MS - Flipflop φ2 φ1 Q = D(ti) D(t) Master φ1 φ2 Slave φ1 = 1, φ2 = 0 : Master übernimmt D, Slave speichert φ1 = 0, φ2 = 1 : Master speichert, Slave übernimmt Informationsspeicherung auf Transistorkapazitäten (dynamisch) Mikroelektronik Rainer Kraus Register φ2 φ1 D(t) MS FF φ1 φ2 MS FF MS FF Q0 Q1 ==D(t D(t43251)) ==D(t D(t3421)) t1 t2 t3 MS FF Q2 ==D(t D(t321)) t4 MS FF Q3 Q4 = D(t21) = D(t1) t5 D(t) Mikroelektronik Rainer Kraus