Referat zu den Themen Mainboard und Prozessor - WinFuture

Werbung

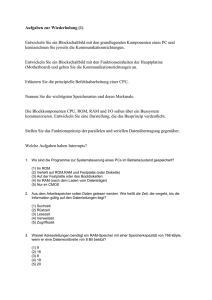

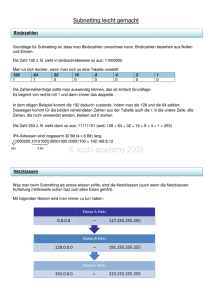

Referat zu den Themen Mainboard und Prozessor Mainboard Alle wichtigen Elemente (Ventilator, Stromversorgung, Grafikkarte, RAM- Sockel, Lautsprecher , CPU , Laufwerke) eines PCs sind auf dem Mainboard (auch: Motherboard, Hauptplatine) angebracht. Sie wird durch ein Gehäuse geschützt. Alle anderen Bauteile, also sogenannte Peripheriegeräte wie z.B. Diskettenlaufwerke, Festplatte, CD-Rom-Laufwerk und Zusatzkarten wie Modem oder Grafikkarte werden an die Hauptplatine angeschlossen und tauschen mit ihr Informationen aus. Die Hauptplatine wird daher als Mutter (mother), die Karten und Komponenten als ihre Kinder bezeichnet. Auf das Motherboard sind metallische Leiterbahnen aufgebracht, über die die Chips und die anderen Komponenten auf der Platine elektronische Impulse austauschen. Prozessor Der Zentralprozessor erfüllt mit seiner Control Unit (Leitwerk) die Aufgabe der Steuerung des Befehlsablaufs, der Entschlüsselung von Befehlen und der Weitergabe von diesen an Speicher oder Peripheriegeräte. Den zeitlichen Ablauf steuert ein Taktgeber (= Pulsgenerator zur Synchronisierung von Operationen). Das Rechenwerk (ALU = Arithmetic and Logic Unit) verknüpft Daten in Rechenvorgängen. Da sich CU und ALU i. d. R. auf einem Prozessorchip befinden, werden sie unter dem Begriff CPU (Central Processing Unit) oder Prozessor zusammengefasst. Die CPU interpretiert die Befehle, führt Programme aus und bringt den Rechner zum Laufen. Ein Eingabe/Ausgabeprozessor steuert „im Auftrag der CPU“ den Datenaustausch mit der Peripherie. Personalcomputer basieren auf einer Prozessorfamilie der Firma Intel, die ausgehend vom Typ 8088 über 8086, 80286, 80386, 80486 bis zur heutigen Pentium-Generation die Leistungsfähigkeit von Prozessoren stetig gesteigert hat. In einem Pentium-Prozessor stecken ca. 3 Millionen Transistoren. Auch verfügt der Pentium über ein eigenes RAM sowie ein Ein- und Ausgabesystem, so dass man von einem „kleinem Computer“ im Computer sprechen kann. 1. Grundsätzlicher Aufbau eines Motherboards Formfaktoren Unter einem Formfaktor versteht man einen Standard der die Größe des Boards sowie die Lage der Bauteile auf dem Motherboard bestimmt. Auch Bohrlöcher und Stromanschluss sind darin definiert. Vom vergleichsweise riesigen AT-Board (etwa 30 x 35 cm) ging die PC-Industrie spätestens beim 486er weitgehend auf Baby-AT (BAT) über (etwa 22 x 33 cm), jedoch wuchsen gleichzeitig CPU (und der Kühlturm auf der CPU), es wurden zunehmend Schnittstellen (Parallel, Seriell, Floppy, Festplatte, ...) auf dem Motherboard mit integriert, so das der Platz knapp wurde. Daher definierte Intel 1995 den neuen Formfaktor ATX, wichtigster Inhalt: Das Motherboard wird um 90° gedreht, die Steckplätze behalten aber ihre alte Lage. Auf diese Weise wird die CPU von den Steckplätzen wegbewegt und kann diese nicht mehr blockieren. Auch wird ein neuer Stecker für die Spannungsversorgung definiert, dieser ist im Gegensatz zum alten BAT-Stecker verpolungssicher. Des weiteren wird ein Bereich auf dem Board bestimmt, an dem sich die Anschlüsse für Tastatur, Parallele- und Serielle- Schnittstelle, usw. sammeln sollen. Erwähnenswert sind außerdem noch die LPX und NPX Formfaktoren, hierbei basiert LPX auf BAT, NPX aber auf ATX. Diese beiden definieren Motherboards die mittels Riser- Platine die Steckplätze um 90° kippen und so ein wesentlich flacheres Gehäuse ermöglichen. Busse, Sockel und Slots Die erste Riege der PC-Prozessoren (8086 und 8088) hatte noch Sockel wie übliche Microchips. Zu den Zeiten von 286, 386 und einigen 486ern waren dann auch viele fest aufgelötete CPU's anzutreffen, dann aber kamen die ZIF-Sockel (Zero Insertion Force, zu deutsch: Null-Kraft Sockel) auf. Diese erlauben das Einsetzen und Herausnehmen der CPU praktisch ohne Kraft und ermöglichen so ein problemloses Wechseln. Die ZIF-Sockel entwickelten sich bis zum Sockel-8 (PentiumPro), als Nachfolger definierte Intel dann den Slot1 für den Pentium-II. Und bald gab es auch einen Slot2 für die dritte Generation PentiumII (Xeon). Die Slots erinnern in ihrer Beschaffenheit übrigens an EISA Steckplätze (zwei Kontakt-Etagen), und aufgrund der Größe der von der Platine abstehenden Pentium-II CPU sind sie nur auf ATX Motherboards wirklich praktikabel. Auch bei den Bussystemen hat sich einiges getan. Bei den ersten PC war noch der ISA-Bus primäre Erweiterungsschnittstelle, er wurde später zwar noch von 8 auf 16 Bit Breite aufgebohrt, aber er blieb doch auf 8 MHz beschränkt. Mehrere Hersteller und HerstellerVereinigungen versuchten in der Folgezeit dann neue Bussysteme einzuführen, so u.a. EISA, Microchannel oder Vesa-Local Bus. Im Endeffekt aber dominiert heutzutage der erheblich offener gestaltete PCI-Bus. Die neueste Entwicklung nun ist der AGP-Bus, dieser bietet der Grafikkarte eine schnellere Anbindung an den Hauptspeicher. Mit der Zeit wurden auch ganz neue Erweiterungsbussysteme eingeführt, in erster Linie seien hier PS/2 Schnittstellen für Maus und Tastatur, IRDA zur drahtlosen Übertragung von Daten zwischen zwei PC's mittels Infrarot, der USB (Universal Serial Bus) als zukunftsweisende Anschlussmöglichkeit für Hardware mit kleinem bis mittlerem Datenaufkommen (Tastatur, Maus, Hand-Scanner, ...) sowie der in den neuesten Chipsätzen integrierte I²C-Bus (von Intel SMBus, System-Management-Bus, genannt) der Computerinterne Management-Hardware wie Temperaturfühler anbindet. 2. Prinzipieller Aufbau eines Motherboards Das Motherboard fungiert in einem Computer als Plattform, worauf alle wichtigsten Organe untergebracht sind. Neben dem Prozessor, dem Herzen des Rechners und dem Speicher, dem Gehirn, ergeben sich noch viele nötige Organe, um einen PC zum Laufen zu bringen. Daraus ergibt sich die Architektur, die man auf den Hauptplatinen wiederfinden kann. Eines der Merkmale, das PCs erfolgreich gemacht hat, sind die Bussysteme, die es ermöglichen, den Computer per Steckkarten flexibel aufzurüsten (vulgo slot). 2.1 Die 8 - Bit - Architektur des PC/XT. Diese Architektur ist maßgebend für alle nachfolgenden Systeme. Die alten Chips unterscheiden sich oftmals in ihren grundlegenden Funktionen nicht sehr von denen, die man heute z.B. in einem Pentium wiederfindet. So z.B. die DMA - Chips wie der 8237A oder der PIC 8259A. Komponenten und ihr Zusammenwirken. Der Zentrale Baustein ist der Prozessor. Den Systemtakt gibt ein Taktgenerator an (8284), der mit 14,318 MHz läuft und diesen durch drei teilt, so dass sich ein effektiver Systemtakt von 4,77 MHz ergibt. Der Prozessor ist über den Adreß -, Daten - und Steuerbus mit dem Hauptspeicher verbunden. Die CPU kann durch den Adressbus den Speicher adressieren (ansprechen) und die Datenübertragung über den Steuerbus steuern. Man unterscheidet vier verschiedene Adressbusse: 1. Lokaler Adressbus: Er beherrscht 20 Signale vom 8086/88. Es ist ein prozessornaher Bus, der sich zwischen den Externen Adresspuffer und den Adress - Latches befindet. Damit ist es ein Bus, der neben dem Systemadressbus arbeitet. 2. Systemadressbus: Das ist die gelatchte Version des lokalen Busses und ist einer der wichtigsten Busse im PC/XT System. Das Signal zur Verriegelung der Adresssignale auf dem lokalen Adressbus in den Latches ist ALE. Der Systembus geht bei den Busslots nach außen raus. 3. Speicheradressbus: Ist ein nur auf dem Motherboard vorhandener Bus, der eine gemultiplexte Version des Systemadressbusses darstellt. Über diesen Bus werden nacheinander die Zeilen - und Spaltenadressen an die DRAM - Chips übergeben. 4. X - Adressbus: Er ist über Puffer und Treiber vom Systembus abgetrennt und dient zur Adressierung der I/O - Einheiten und des ROM - BIOS auf dem Motherboard, wie z.B. der Register des Interrupt - Controllers, des Timers oder eines On - Board - Diskettencontrollers. I/O - Ports und Zusatz - BIOS auf Erweiterungskarten (SCSI Host Adapter) werden aber vom Systemadressbus angesprochen. Wir unterscheiden auch vier verschiedene Datenbusse: 1. Lokaler Datenbus: Er umfasst 16 bzw. 8 Datensignale vom 8086/88. Eine Buslogik regelt die Word - und Byte - Zugriffe. Externe Datenpuffer und Daten - Latches grenzen ihn vom übrigen Systemdatenbus ab. Im XT ist er 16 Bit breit. 2. Systemdatenbus: Das ist die gelatchte Version des lokalen Datenbusses, die nach außen auf die Busslots herausgeführt ist. (Beim XT 16 Bit breit). 3. Speicherdatenbus: Ist ein interner Motherboardbus, der die Verbindung zwischen dem Systemdatenbus und dem Hauptspeicher darstellt. 4. X - Datenbus: Dieser ist über Puffer und Treiber vom Systemdatenbus abgetrennt und steuert die I/O - Einheiten und das ROM an. I/O - Ports und Zusatz - BIOS werden wieder vom Systemdatenbus angesprochen. Die CPU kann über diesen Systembus auch externe Bauteile der Steckkarten im Rechner ansprechen (Slotkarten). Über den Systembus führen einige wichtige Signale auf die Slots, so dass Slotkarten angesprochen werden können. Wichtig ist, dass der PC mit 8 und der XT mit 16 Bit auf den Bussen arbeitet. Es ist jedoch so, dass der Datenbus beim XT trotzdem mit 8 Bit auf die Slots herausgeführt wird, was Probleme mit sich bringt. Wird ein Steckplatz mit 16 Bit angesprochen, so müssen zwei 8 Bit lange Daten einzeln entnommen und später wieder zusammengeführt werden. Das hat zufolge, dass beim gleichzeitigen Zugriff auf Steckkarten und den Systemhauptspeicher die Zugriffe auf die Karten viel langsamer sind, da sie jedes Mal die Umwandlung benötigen. Dabei erscheint noch das Problem, dass die Steckkarten selbst langsam sind, so dass sie mit den Systemtaktraten nicht mitkommen. Dieses hatte auch in späterer Zeit entscheidende Nachteile mit sich gebracht, weil sogar schnelle 50 MHz Rechner mit Busslottakten die mit maximal 8 MHz arbeiteten, auskommen mussten. Irgendwann wurde der Systembustakt für 8 - Bit - Steckplätze und somit den gesamten Systembus auf exakt 8,33 MHz festgesetzt Um die Adressen vom Prozessor bei einem Zugriff auf den Speicher zu dekodieren, weist der PC/XT einen Adressmultiplexer auf. Er steuert zusammen mit dem Speicherpuffer die Speicherchips auf dem Motherboard an. Die Logik zur Prüfung der Parität löst einen NMI aus, wenn die Daten beim Auslesen nicht mit dem zusätzlich gespeicherten Paritätsbit konform sind. Die Paritätsprüfung erfolgt byteweise, d.h. jedem für sich adressierbaren Byte wird ein Paritätsbit zugewiesen. (Für eine 16 - Bit - Organisation sind 18 Chips notwendig 16 Chips für die Daten und zwei Paritätsbits (je Byte einer)). Der PC/XT besitzt weiterhin ein ROM, in dem Code und Daten für den Boot - Vorgang und die BIOS - Routinen gespeichert sind. Der 8086/88 spricht das BIOS wie den Hauptspeicher an. Greift die CPU auf BIOS, Hauptspeicher oder den I/O - Adressbereich, so werden alle Wartezyklen von einer eigenen Logik gesteuert (Wait - State - Logik). Damit Peripheriegeräte unterstützt werden, befindet sich ein programmierbarer Interrupt Controller (PIC) 8259A auf dem Motherboard. Er verwaltet externe Hardware - Interrupts wie z.B. Festplattencontroller oder Timer - Chip. Der PIC hat 8 Eingangskanäle, die jeweils mit einer Leitung mit einem Baustein verbunden sind, der ein Interrupt auslösen kann. Sie werden mit IRQ 0 bis IRQ 7 durchnumeriert. Außer des PIC gibt es einen weiteren Support - Chip, der sich Timer - Chip nennt (PIT oder Intervall - Timer 8253). Er weist drei Zähler auf: 1. Zähler 0: Wird zum periodischen Nachstellen der Systemuhr benutzt und ist mit dem IRQ0 des PIC verbunden. Der hier ausgelöste Interrupt stellt die Uhr nach, die vom Befehl TIME oder DATE aufgerufen wird. 2. Zähler 1: Führt zusammen mit dem DMA - Chip die Auffrischung des Speichers aus. 3. Zähler 2: Erzeugt die Frequenz für den Beeper im Rechner. 4. Die Tastatur ist über ein programmierbares Peripherie - Interface (PPI) 8255 mit dem Systembus verbunden. Der gleiche Chip kann auch Informationen über das System ans BIOS schicken, die er über die DIP - Schalter bekommt. Als Hardware - Komponenten werden alle Support - Chips über Ports im I/O Adressbereich angesprochen. Alle Streckkartenkomponenten werden ebenfalls über Port - Adressen angesprochen. Der I/O Adressbereich ist auf die Busslots herausgeführt, so dass interne und externe Hardware auf dem gleichen I/O Adressraum arbeitet. (UART von COM1 und COM2 dürfen nicht die gleiche I/O Adresse besitzen. DMA - Architektur Neben Prozessor kann auch der DMA - Chip 8237 A Speicher - und I/O - Zugriffe tätigen. Er dient in erster Linie dazu, Daten zwischen dem Hauptspeicher und den I/O Einheiten (z.B. dem Diskettenkontroller) zu transportieren. Im Gegensatz zum Prozessor, kann er aber keine Daten verarbeiten. Er weist vier getrennt programmierbare Kanäle auf. 1. Kanal 0 dient der Speicherauffrischung und wird vom PIT 8253 A periodisch aktiviert, um einen Blindzugriff auf den Speicher auszuüben (dadurch auffrischen). 2. Kanal 1 bis 3 stehen zur Datenübertragung zur Verfügung. Hat der Festplattencontroller einen Sektor eingelesen, so wird Kanal 3 des 8237A aktiviert und überlässt ihm die Datenübertragung ohne Eingriff der CPU. Der 8237A stellt also einen weiteren von der CPU unabhängigen Chip dar, der zur Ausführung von Buszyklen kommt. Der DMA - Chip benutzt ein Übertragungsprotokoll. Der DMA - Chip ist ein Busmaster, er kann nämlich selbständig Buszyklen ausführen. Alle Busmaster befinden sich beim PC/XT auf den Board und nicht auf Slotkarten. Alle Slotkarten müssen einen Hardwareinterrupt auslösen, um damit den Bedarf an Daten vorzubringen und werden nicht automatisch mit Daten versorgt wie ein Busmaster. 8-Bit-Kanäle Der 8237A z.B. nützt im wesentlichen der Datenübertragung zwischen dem Hauptspeicher und dem I/O - Gerät in einem Slot. Da der PC/XT nur 8 - Bit breite Slots besitzt, findet auch nur eine Datenübertragung auf Basis der 8 - Bit - DMA - Kanäle statt. Der PC besitzt einen 8 - Bit breiten Datenbus und einen 20 - Bit breiten Adressbus. Der 20 - Bit - Adressraum ergibt sich aus den 8 Adressbits, den 8 Adress - Bits vom Adress - Latch und den vier Bits vom Page - Register. Durch den 8 - Bit breiten Datenbus sind nur 8 - Bit DMA - Kanäle möglich, wobei der 8237A ein 8 - Bit Chip ist. Soll etwas gelesen werden, so gibt der 8237A die Speicheradresse aus und aktiviert das Signal MEMR, damit ein Datenbyte (8 Bit) aus dem Speicher auf den Datenbus gelesen werden. Hiernach wird Signal IOW aktiviert, um das Datenbyte dem Peripheriegerät zu übergeben. Beim XT handelt es sich aber um ein 16 - Bit - Datenbus. Da aber der DMA - Chip nur 8 - Bit verarbeiten kann und nur zu 8 - Bit Peripheriegeräten kompatibel ist, wird es etwas umständlicher. Die Peripheriegeräte sind ebenfalls an die 8 - Bit breiten Slots angeschlossen. Da aber der Datenbus 16 - Bit breit ist, ist auch der Hauptspeicher in 16 - Bit Breite organisiert. Das heißt konkret, dass auf dem niederwertigen Byte (D0 bis D7) des Datenbusses nur Datenbytes mit gerader Adresse und auf dem höherwertigen Byte die Datenbytes mit ungerader Adresse auftauchen. Liest der 8237A jetzt Daten aus dem Speicher, so erschienen die Datenbytes entweder auf dem höher oder niederwertigen Byte des Datenbusses. Damit z.B. ein Peripheriegerät mit gerader I/O - Adresse die Daten empfangen kann, muss eine Logik dafür sorgen, dass das Datenbyte im höherwertigen Teil des Datenbusses in den niederwertigen gelangt. Ein analoges Problem tritt beim XT ebenfalls auf. Er löst dies so, dass er mit dem Signal BHE und dem niederwertigsten Adressbit A0 je nach Fall eine Hälfte des Datenbusses stilllegt. Speicherauffrischung: Der DMA - Kanal 0 ist für die Speicherauffrischung reserviert. Diese wird über einen DMA Zyklus ausgeführt. Dazu wird im PIT 8253 (im Modus 3) der erste Zähler mit einem Zählwert von 18 (12h) betrieben. Nur das niederwertige Zählerbyte wird geladen (RW1=0, RW0=1). Dann löst er ein Rechtecksignal aus, was mit einer Frequenz von 66,288 Hz arbeitet. Alle 15 Mikrosekunden wird ein Signal gesandt, wobei der DMA - Chip im Lesemodus ist. Durch diese Blindübertragung werden Daten vom DMA - Chip kurzfristig aus dem Speicher gelesen. Durch diesen Eingriff aktivieren sich automatisch Adresspuffer, Adressdekoder und Leseverstärker. Da aber keine Einheit mit dem DREQ0 die Daten angefordert hat, werden sie auch nicht weiterverarbeitet (sie können dadurch auch nicht mit einem DACK0, MEMR oder IOW reagieren). Damit verschwinden die gelesenen Daten beim nächsten Zyklus von Datenbus. Der PIT liefert das periodische Rechtecksignal und damit den Auffrischungszeitpunkt, wobei der DMA - Chip die Refresh - Adresse und das Steuersignal zum Lesen erzeugt. Das BIOS spielt dabei auch eine Rolle. Bei jedem Booten stellt das BIOS das Zählregister auf einen geeigneten Wert und Kanal 0 wird auf Einzelübertragung und Autoinitialisierung. Jede Anforderung über den Kanal 1 löst genau eine Übertragung aus und inkrementiert die Refresh - Adresse. Gleichzeitig wird das Zählregister erniedrigt bis es den Wert ffffh erreicht hat. Danach tritt ein TC auf, der Kanal 0 des DMA initialisiert sich wieder automatisch und der Refresh beginnt wieder von vorn. 2.2 Die 16 - Bit Architektur des 80286 Die Komponenten und ihr Zusammenwirken Die Chips, die im Schema dargestellt sind, müssen längst nicht so auf dem realen Motherboard vorkommen, da heute viele Chips in einem integriert werden. Dieser 80286 Prozessor besitzt 24 Adressleitungen, also kann er 16 Mbyte RAM ansprechen. Der Protected Mode ist hier auch schon möglich (z.B. für OS/2). Die Adressleitung A20 kann vom Tastaturkontroller 8042 gesteuert und kann im jeweiligen Fall abgeschaltet werden. Der 80286 kann einen zusätzlichen Coprozessor 80287 erhalten. Auf dem Board steht ein Sockel für diesen zumindest zur Verfügung. Der Taktgenerator 82284 ist neu und sorgt für den Systemtakt. Die CPU adressiert den Speicher durch einen 24 - Bit breiten Adressbus. Die Datenübertragung wird vom Steuerbus geregelt und der Datenbus ist 16 Bit breit. Die Steuersignale kommen vom Buscontroller 82288. Man unterscheidet verschiedene Adressbusse: Lokaler Adressbus: 24 Adresssignale. Getrennt vom übrigen Adressbus durch Externe Adresspuffer und Adress - Latches. Systemadressbus: Der wesentliche Adressbus. Die gelatchte Version der Bits A0 A19 des lokalen Adressbusses. Also 20 - Bit breit. Das Signal zur Verriegelung der Adresssignale auf dem lokalen Adressbus ist ALE. Der Bus ist in den externen Slots herausgeführt. Speicheradressbus: Nur auf dem Motherboard vorhanden. Gemultiplexte Version des Systemadressbusses. Über ihn werden nacheinander die Zeilen - und Spaltenadressen an die DRAM - Chips übergeben. X - Adressbus: Über Puffer und Treiber vom Systembus abgetrennt und dient der Adressierung der I/O - Einheiten und des ROM - BIOS auf dem Board (z.B. die Register des Interrupt - Controllers, des Timers oder eines On - Board Diskettenkontrollers). I/O - Ports und ROM - BIOS auf Erweiterungskarten werden über den Systemadressbus angesprochen. L - Adressbus: Dieser Adressbus besteht aus den sieben (A17 bis A23) höherwertigen (und nicht gelatchten) Bits des lokalen Adressbusses. Er wird als AL17 bis LA23 in die AT - Slots herausgeführt. Man unterscheidet verschiedene Datenbusse: Lokaler Datenbus: Umfasst die 16 Datensignale vom Prozessor. Eine Buslogik ist notwendig, damit Byte - und Wordzugriffe unterschieden werden. Externe Datenpuffer und Daten - Latches trennen diesen Bus vom Übrigen Systemdatenbus. Systemdatenbus: Die gelatchte Version des lokalen Datenbusses. 16 - Bit - Breite. In die Slots herausgeführt. Speicherdatenbus: Dieser Datenbus ist nur auf den Board vorhanden. Verbindung zwischen Hauptspeicher und Systemdatenbus. X - Datenbus: Über Puffer und Treiber vom Systemdatenbus abgetrennt. Spricht I/O Einheiten und ROM - BIOS auf dem Board an, I/O - Ports und Zusatz - BIOS auf Steckarten werden vom Systemdatenbus versorgt. Neben dem Hauptspeicher sind Zugriffe von der CPU auch auf Steckarten in den Slots möglich. Hier wird der Datenbus mit einer Breite von 16 Bit auf die Slots herausgeführt, also mit der vollen Breite. Dadurch gibt es einen neuen Slotabschnitt, der mehr Kontakte enthält. Alte Steckkarten können auch im neuen Slot weiterbetrieben werden, was die Buslogik erst möglich macht. Damit wird eine 16 - Bit von einer 8 - Bit Steckkarte automatisch unterschieden. Ein 8/16 Wandler sorgt dafür, dass 16 - Bit - Werte in zwei 8 - Bit - Werte zerlegt werden. Auch hier dürfen Busmaster nur interner Struktur sein, Slotkarten dürfen nicht als Busmaster fungieren. Die besseren AT's laufen mit 16 MHz oder mehr Taktfrequenz, was dazu führte, dass die Busslots nicht mit der Hälfte der Frequenz zurechtkamen, was ihre tatsächliche Taktfrequenz war. Aus diesem Grund wurde ein Standardwert festgesetzt, mit dem alle ISA - Slotkarten höchstens laufen dürfen, nämlich mit 8,33 MHz. ISA ist die Bezeichnung für die Gruppe der 16 - Bit - AT - Slots. Der Hauptspeicher hingegen läuft mit der vollen Frequenz des Prozessors. Nur die CPU sendet Wartezyklen aus, wenn der Speicher zu langsam ist und nicht mitkommt. Deshalb sollte dem Einbau von On - Board - RAM der Vorrang gelten. Beim AT gibt es einen Adressmultiplexer, der zusammen mit dem Speicherpuffer den Speicher anspricht. Die Logik zur Überprüfung der Parität löst einen NMI aus, wenn das Paritätsbit nicht mit den gesandten Daten übereinstimmt. Beim AT wird der Zeitpunkt für die Speicherauffrischung über den Kanal 1 des Timer - Chips festgelegt. Dann wird eine spezielle Refresh - Logik vom Timer 1 angesteuert. Also ist Kanal 0 normalerweise frei. Der AT besitzt ebenfalls ein ROM, worin alle beim Boot notwendigen Daten gespeichert sind. Der AT kann im Protected Mode laufen, was aber das BIOS nicht schafft, da dieser Modus völlig inkompatibel zum Real - Modus ist. Auch der AT weist mehrere Support - Chips auf. Für den alten Interrupt - Controller gibt es jetzt zwei davon, einen Master - PIC und einen Slave - PIC, die ebenfalls zusammen unter der Bezeichnung PIC 8259A auftauchen. Die beiden PIC's sind kaskadiert (miteinander verschachtelt verbunden). Deshalb stehen statt 8 jetzt 15 IRQ - Ebenen zur Verfügung. Der NMI ist ebenfalls als Interrupt aufgeführt, wobei der Interrupt - Controller für diesen nicht zuständig ist. Ein programmierbarer Intervall - Timer (PIT) 8253/8254 ist ebenfalls vorhanden. Er hat drei programmierbare Zähler: Zähler 0: wird zum Nachstellen der Systemuhr benutzt. (Befehl TIME in DOS). Kanal 0 ist mit dem IRQ 0 des Master - PIC verbunden. Kanal 1 ist zur Speicherauffrischung gut und Kanal 2 erzeugt die Tonfrequenz im PC - Speaker. Die AT - Tastatur kann programmiert werden. Das geschieht über ein programmierbares Peripherie - Interface (PPI) 8255. Der AT verfügt über ein CMOS - RAM, was vieles leichter gestaltet. Dieser speichert die Systemkonfiguration und gibt sie beim Booten an das BIOS weiter, was das lästige umstellen von Jumpern überflüssig macht. Er behält seine Einstellungen auch dann bei, wenn der Rechner ausgeschaltet wird. Die Support - Chips werden über I/O - Ports im Adressbereich angesprochen. Der AT verwendet ebenso eine I/O - Mapped Ein -/Ausgabe Bei höheren Prozessoren, wie dem 80486 unterscheiden sich oft nur die internen Adress und Datenbusse vom 80286, von ein Paar Feinheiten und Verbesserungen abgesehen. Der AT oder ISA - Bus besteht dort immer noch aus 16 Bit Datenbreite. Die Umlegung der verschieden breiten Busse erfolgt über spezielle Swapper und Puffer. DMA - Architektur Für Speicher und I/O - Zugriffe unter Umgehung der CPU weist der AT zwei DMA - Chips auf, die kaskadiert sind und damit insgesamt sieben Kanäle besitzen. Die vier ersten Kanäle des Slave - Chips bedienen acht - Bit - Peripheriegeräte, wobei die drei freien Kanäle fünf bis sieben für 16 - Bit Einheiten gedacht sind. Kanal Null ist für Speicherauffrischung reserviert, obwohl die meisten ATs eine eigene Refresh - Logik aufweisen. Die DMA - Chips arbeiten mit einer sehr niedrigen Taktfrequenz (üblich: 5 MHz). Deshalb übergeben die meisten Festplattenkontroller ihre Daten nicht über DMA sonder über eigen programmierte I/O, weil der Prozessor viel schneller als seine DMA - Chips arbeitet. Der AT besitzt wegen seines großen Adressraums von 16 MB schon ein 8 - Bit Pageregister. Damit kann er jetzt mit den zwei 8 - Bit - Adressen vom 8237 und dem DMA Adress - Latch eine 24 - Bit - Adresse erzeugen. 2.3.1 Der Triton II Chipsatz Zu dieser Familie gehören die HV und VX Chipsätze von Intel. Die interne Bezeichnung lautet 82430HX und 82430VX. Sie haben die Triton – Familie abgelöst. Diese Motherboards weisen eine 64 – Bit breiten Datenbus auf. Diese Motherboards können mit DRAM Speicherbausteinen des Typs FPM (Fast Page Mode), EDO (Extended Data Output) oder SDRAM (Synchronous Dynamic RAM) ausgerüstet werden. Bei allen Triton II Boards ist aber immer noch der TAG RAM für die Hauptspeicherausrüstung von herausragender Wichtigkeit. Dieser ist für die maximal cachebaren Hauptspeicher zuständig. Dessen Größe bestimmt nämlich die Größe des maximal cachebaren Hauptspeichers. In den meisten Boards wurden 8 x 8Kbyte Tag RAM eingebaut, wes zu einer maximal cachebaren Hauptspeichergröße von 64 Mbyte führt. Wer seinen Rechner mit mehr als 64 Mbyte RAM ausrüstet, muss mit erheblichen Geschwindigkeitseinbußen rechnen. Die üblichen Boards, die mit höchstens 66 MHz Systembustakt laufen, brauchen nur 8 ns schnellen Cache – Speicher. Für die Boards, die mit 75 MHz Bustakt laufen, sind schon mal 6 ns angesagt. Dann werden die Cache – Module auch ihre volle Leistung zur Geltung kommen lassen. Alle Boards mit Triton II Chipsatz werden serienmäßig mit einem I/O – Controller (früher ISA Steckkarte) ausgestattet, der für die Schnittstellen verantwortlich ist. Außerdem ist noch der PS/2 Anschluss hinzugekommen. Dieser befindet sich auf einer Steckkartenblende und wird mit dem Board verbunden. Man kann sich durch den Anschluss einer PS/2 – Maus die seriellen Schnittstellen für andere Geräte freihalten. Alle auf den Triton und Triton II basierenden Motherboards ist ein I/O – Schnittstellen FIFO – Chip 16550, der hohe Übertragungsraten ermöglicht. Mit den Triton II kam auch ein neuer Standard für PCI – Geräte auf – der PCI 2.1. Jetzt sind fünf busmasterfähige Geräte anschließbar, wobei eines davon der auf den Board schon integrierte PIIX3 – Chip ist. Dieser Chip stellt das PCI to DRAM Interface dar und zeichnet sich durch größere Datenübertragungsraten aus. Er kann bis zu 112 Mbyte/s beim Lesen und bis zu 121 Mbyte/s beim Schrieben an Daten übertragen. Der PCI to DRAM Buffer wurde im Vergleich zum Vorgänger Triton I vergrößert. Bei jedem Triton II Board ist auch ein PCI I/O Xcelerator PIIX3 Chip (82371SB) dabei, der folgende Aufgaben löst: PCI zu ISA – Verbindung: Er stellt die Brücke zwischen ISA und PCI her. Bis zu fünf ISA Geräte mit einer maximalen Taktfrequenz von 8,33 werden unterstützt. Fast – IDE – Support: Der PIIX3 ist ein vollständiger Enhanced – IDE – Controller, Neben den von vorn hinein Funktionen unterstützt er auch die neuen Zugriffsverfahren PIO Mode 4 (bis zu 16,6 Mbyte/s)und DMA Mode 2 (bis zu 22,2 Mbyte/s). USB – Controller: Universal Standard Bus ist eine neuartige Technologie, die das Verwalten und Organisieren von Peripheriegeräten standardisieren soll. (Erklärung später) 2.3.1.1 Der 82430HX Chipsatz Schema eines Motherboards mit Intel HX – Chipsatz: Dieser Chipsatz, wie auch der VX, aus der Triton II Familie unterstützt die P54C und P55C Prozessoren bis 200 MHz Taktfrequenz. Einige beherrschen auch höhere Tektraten, es sind aber sehr wenige. Der zentrale Punkt ist der System – Controller (TXC) 82439HX. Dieser stellt die Single Chip PCI to Host Bridge. Dieser Chip kann zwei Prozessoren gleichzeitig bedienen. Das HX Board kann auch bis zu 512 Kbyte Second – Level – Cache aufnehmen und verwalten. Das HX kann bis zu 512 MByte Hauptspeicher adressieren. Das HX – Board stellt ein weites Feature zur Verfügung, wonach FPM Module mit einem Paritybit benutzt werden können. Diese Speicherbausteine könne dann das Feature ECC ausnutzen. ECC bedeutet Error Correction Code, womit umgekippte Bits automatisch korrigiert werden können. Das vermindert die Absturzgefahr eines Rechners, geht aber nur in Kombination eines HX Boards mit den FPM DRAMs mit Parity – Bit. Eine weiter Funktion des ECC ist das Virtual Swappable Bank Support, womit fehlerhafte Speicherbänke nicht zum Betrieb zugelassen werden. Eine Speicherbank ergibt sich aus je zwei SIM – Speichermodulen. Ist das Board mit 2 x 16 Kbyte x 8 Tag RAM ausgestattet, so könne 512 Mbyte RAM ohne Einbußen angesprochen werden. 2.3.1.2 Der 82430VX Chipsatz Dieser Typ von Motherboard ist eher für Multimedia – Anwendungen konzipiert. Den System – Controller stellt der 82437VX dar. Als Bindeglied zwischen CPU, Speicher und Cache werden zusätzlich zwei weitere Chips eingesetzt, die 82438VS Data Path Units (TDX). Jeder von diesen arbeitet mit 32 Bit Datenbus. Diese Chips bilden eine CPU to Host Bridge und unterstützen nur eine System – CPU. Da diese CPU to Host Bridge besitzt nur acht Steuerleitungen (TIO 0 bis 7). Dadurch sind nur die ersten 64 Mbyte des Arbeitsspeichers über den Cache adressierbar. Auf den Arbeitsspeicher wird über die beiden Chips zugegriffen. D.h. jeder Chip ist für 32 Bit zuständig. Es wird also insgesamt mit 64 Bit zugegriffen. Der VX Chipsatz kann maximal (wie auch schon der Triton I Chipsatz) 128 Mbyte Hauptspeicher adressieren. Dieser Chipsatz erlaubt keine Fehlerkorrektur wie z.B. die ECC. Dafür bietet das VX Board ein anderes Feature an - Es kann nämlich SDRAMs (Synchronous DRAMs) als Hauptspeicherbausteine aufnehmen. Diese Speicherbausteine haben eine 64 – Bit Architektur und erscheinen als 16 bis 128 Mbyte Module auf dem Markt. Man muss also das Motherboard mit immer einem Paar von 32 Bit breiten DRAMs oder mit je einem 64 Bit breiten SDRAM bestücken, weil der Speicherzugriff 64 –bittig ist. Eine weitere wichtige Erweiterung ist das SMBA (Shared Memory Buffer Architecture). Das ist eine Funktion, die ausgewählten Grafik – Controllern den direkten Speicherzugriff ermöglicht. Der Grafik – Controller und die CPU to Host Bridge sind mit einer Zweidraht – Handshake – Leitung verbunden. Das soll Motherboard – Herstellern ermöglichen, Boards mit integrierten Grafikkarten billig zu produzieren. 2.3.2 Der Triton III Chipsatz Dies ist eine neue Chipsatz - Generation von Intel, dessen interne Bezeichnung 82430TX lautet. Im wesentlichen handelt es sich um einen Chip, der als Speicher- und Cache Controller aber auch als CPU - Bridge und PCI – Steuerungseinheit fungiert. Er beherrscht dafür kein ECC, was auf die hohe Integrationsdichte zurückzuführen ist. Der neue Chip beherrscht auch DPMA (Dynamic Power Management Architecture). Dadurch soll der Rechner, der nicht mehr ausgeschaltet wird, Wirklichkeit werden. Das ACPI (Advanced Configuration and Power Interface) schaltet nur die Geräte aus, von denen es weiß, dass sie in nächster Zeit nicht gebraucht werden. Dadurch wäre ein Rechner machbar, der den ganzen Tag vor sich hindämmert, dann vollautomatisch ein Fax empfängt und anschließend wieder in den Schlaf verfällt. Der neue Chipsatz erlaubt auch die Nutzung von SDRAMs, die zwar 12 Nanosekunden Zugriffszeit aufweisen, aber ihre volle Leistung durch die Begrenzung des Bustaktes auf 66 MHz (von Intel) wahrscheinlich nicht voll zum Tragen kommt. Intel hat den Chipsatz so konzipiert, dass man ohne Second – Level –Cache arbeiten kann, weil ja ohnehin mit SDRAMs arbeiten sollte. Dieser Speicher arbeitet mit einem Burst von 5-1-1-1. Das ist immer noch bis zu sechs Mal langsamer als der Second – Level – Cache des Boards, der mit einem Burst von bis 1-1-1-1 arbeitet. Eine neue PCI – to – ISA Bridge erschien mit dem TX – Chipsatz, derer interne Bezeichnung PIIX4 lautet. Dieser beinhaltet auch noch den USB – Controller und den PCI EIDE – Controller mit zwei Anschlüssen. Der PIIX4 hat den EIDE – Überwachungsmodus PIO Mode 0 bis 4 und das Multi – Word DMA 0 bis 2 implementiert bekommen. Weiterhin unterstützt der PIIX4 Ultra - DMA. Das ist ein neues Protokoll für die IDE - Geräte, das Transferraten von bis zu 33 MByte pro Sekunde ermöglichen soll. Eine andere Funktion des PIIX4 übernimmt der 82371AB Power Management Controller die Aufgabe der Steuerzentrale. Mit diesem können alle Lüfter und sämtliche Spannungen auf dem Board kontrolliert werden und er kann sogar bei Unregelmäßigkeiten einen entsprechenden Warnton ausgeben. Aber auch Nachteile hat der neue Chipsatz vererbt bekommen. Er kann nämlich wie der VX Chipsatz nur 64 MByte maximal cachen, was sich durch den 8 – Bit breiten Tag – RAM ergibt. Der maximale Hauptspeicher beläuft sich auf 256 Mbyte RAM. Das ist natürlich ein Handikap für denjenigen, der ein Rechner für die Zukunft kauft. Außerdem beherrscht dieser Chipsatz nicht die AGP - Schnittstelle. AGP (Accelerated Graphics Port) ist ein neuer Port, der speziell für Grafikanwendungen entwickelt wurde. Aber Intel argumentiert hier damit, dass man sich für den Profibereich eher einen Pentium II kaufen sollte, dessen Board diese Nachteile nicht mehr mit sich bringt. Es ist also ein künstlich entstandener Mangel, der den Käufer auf die Pentium II - Bahn bringen soll. Der Multi I/O – Controller 82371SB wurde von 82371AB abgelöst und verspricht höhere Übertragungsraten. 2.3.3 Natoma – Chipsatz 82440FX für Pentium Pro Alle, die sich einen Pentium Pro gekauft haben, sollten auf jeden Fall ein Board mit Natoma – Chipsatz einbauen, weil dieses einen Standard für diese Systeme darstellt. Der Natoma – Chipsatz kommt wieder von Intel und unterstützt wieder die vollautomatische ECC mit Parity – DRAM – Modulen. Hinzu kommt noch, dass der 440FX bis zu1 Gbyte an Arbeitsspeicher verwalten kann. Da der Pentium Pro. Den Second –Level – Cache im Prozessor trägt, wird kein Second – Level –Cache mehr auf dem Mainboard benötigt. 2.3.4 Intel – Natoma - Mainboard mit 440 FX und 440LX Chipsatz und Intel – Orion – Mainboard mit 440KX Chipsatz Ein Pentium II/300 MHz Motherboard gegen ein Pentium MMX/200 Motherboard im Vergleich. Das sind die aktuellen Mainboard – Chipsätze für Pentium II Systeme. Der Orion Chipsatz ist mit Hinsicht auf Multiprozessorsysteme und Server gebaut worden, was ihn natürlich extrem teuer macht. Alle diese Boards beherrschen das ECC, so dass die Rechner bei Ein – Bit – Fehlern einfach weiterlaufen, da solch vollautomatisch korrigiert werden. Bei mehr als einem Bit – Fehler wird ein NMI ausgelöst. Die Pentium II hat auch noch einen weiteren sehr wichtigen Vorteil. Alle Pentium – Boards mussten sich den gemeinsamen Second – Level – Cache teilen, was zu äußert komplizierten Verwaltungsalgorithmen führte. Die Pentium II Prozessoren haben ihren eigenen Second – Level – Cache, was die Sache erheblich beschleunigt und vereinfacht, da jeder Prozessor nur auf seinen Cache zugreift. Wissenswert ist auch noch, dass die 440FX – Chipsätze kein AGP unterstützten, was sie für den Endkunden uninteressant macht. Da sollte man schon zum neueren 440LX – Board greifen, denn AGP wird sich wohl durchsetzten können, wie es aussieht. Nicht jeder wird sich gleich einen Pentium II kaufen wollen, nur weil der 430 TX so wenig Hauptspeicher aufnehmen kann. Da kann man zu Apollos VP3 – Mainboard greifen, das auch noch den AGP beherrscht. Da aber Intel mit starken Preissenkungen beim Pentium II den Markt für sich gewinnen will, ist abzuwarten, was in nächster Zeit passieren wird. 3. Die wichtigsten Elemente eines Motherboards – Die Support - Chips Die Gesamtheit von Prozessor und Support - Chips nennt man Chipsatz. Diese Chips können den Prozessor entlasten oder ihn sogar bei kleineren Aufgeben ersetzen. 3.1 Die Hardware - Interrupts und der Interrupt - Controller (PIC) 8259A Wie man weiß, sollte jeder Rechner eine serielle Schnittstelle haben. Dort kommen Daten asynchron an, d.h. sie kommen nacheinander und nicht gleichzeitig (synchron) an. Man stelle sich jetzt vor, dass der Prozessor ein Programm abarbeitet. Dabei kommen Daten von der seriellen Schnittstelle. So können diese vom UART aufgenommen und vorerst gesammelt werden, ohne den Prozessor bei seiner Arbeit zu stören. UART bedeutet Universal Asynchronous Receiver and Transmitter, der einen intelligenten Chip für die serielle Schnittstelle darstellt. Er kann parallele Daten serialisieren und umgekehrt und er kann Start -, Paritäts- und Stoppbits abtrennen oder anfügen, also alles um die Aufgaben einer Schnittstelle abzudecken. Worin besteht der Unterschied zwischen Polling und Interrupt - getriebener Kommunikation? Wenn Daten von der seriellen Schnittstelle kommen, gibt es zwei Möglichkeiten, um diese zu bearbeiten: Die serielle Schnittstelle wird ständig nach neuen Daten abgetastet Die serielle Schnittstelle meldet sich dann zu Wort, wenn sie ein vollständiges Zeichen empfangen hat. Wie man auf den ersten Blick sieht, ist die erste Methode eher nicht optimal. Dieses Verfahren bezeichnet man als Polling. Der Prozessor ist dabei allzu sehr damit beschäftigt, die Daten abzufragen, so dass das primär zu bearbeitende Programm langsamer läuft. Zwei Daten laufen direkt hintereinander ein, und der Prozessor kann nur in bestimmten Zeitabständen abfragen, so geht das zweite Paket verloren. Die zweite Methode wird mit Hilfe von Hardware - Interrupts realisiert, woher der Name der Interrupt - getriebenen Kommunikation herrührt. In unserem Fall aktiviert die serielle Schnittstelle ein IRQ - Signal, wenn ein vollständiges Zeichen gelesen wurde. Damit weiß der Prozessor, wenn Daten wieder eingelaufen sind. Die Übertragung des IRQ - Signals übernimmt hier der Support - Chip PIC 8259A. Damit entfällt die ständige Prüfung und das Zeichen oder mehrere können gelesen werden, z.B. dann, wenn die Auslastung des Prozessors gering ist. Daneben können noch andere Geräte mit dieser Methode arbeiten: Die parallele Schnittstelle Der Disketten -/ Festplattencontroller Netzwerkadapter Die Tastatur Der Prozessor hat nur ein Interrupt - Eingang, aber es gibt viele Geräte, die einen Interrupt an den Prozessor auslösen können. Der PIC 8259A hat auch die Aufgabe, diese Interrupts zu verwalten. Dieser Chip ist zwischen dem Interrupt - auslösenden Geräten und dem Prozessor geschaltet. Interner Aufbau des 8259A Ein Peripheriegerät will ein Interrupt auslösen. Damit muss zuerst im IRR - Register das entsprechende Bit gesetzt werden. Jedes Peripheriegerät hat sein eigenes Bit. Im IRR sind also alle Geräte festgehalten, die gerade ein Interrupt ausgelöst haben. Da auch mehrere Bits gleichzeitig gesetzt sein können, muss das Bit mit der höchsten Priorität weitergeleitet werden. Dafür sorgt der Prioritätsgeber. Der PIC aktiviert dann den Ausgang INT, um dem Prozessor eine Interrupt - Anforderung mitzuteilen. Die sogenannte Interrupt - Acknowledge Sequenz beginnt. Ist das IE - Flag im Prozessor gesetzt, so reagiert er mit der Ausgabe eines ersten INTA - Impulses an den INTA - Eingang des 8259A. Der Prioritätsgeber überträgt das Bit mit der höchsten Priorität an das In- Service - Register (ISR) und löscht das betreffende Bit im IRR. Das gesetzte Bit im ISR gibt an, welche Interrupt - Anforderung gerade bedient wird ( In - Service ist). Der Prozessor gibt einen zweiten Impuls, damit die 8 Bit - Nummer des auszuführenden Interrupt - Handlers auf den Datenbus D7 - D0 gelegt wird. 3.2 Der programmierbare Intervall - Timer (PIT) 8253/8254 Jeder, der schon mal professioneller programmiert hat, kennt das Problem, dass man absichtlich Warteschleifen einbauen muss, damit ein Programm an bestimmten Stellen langsamer läuft oder wartet. Solche Dummy - Schleifen laufen auf verschieden schnellen Rechnern verschieden schnell. Das ist ein Problem, wenn man Sequenzen gleicher Länge erzeugen will. DOS versieht jede Datei mit Datum und Uhrzeit der letzten Änderung, und auch die Ansteuerung der Motoren des Diskettenlaufwerks verlangt exakte Zeitintervalle. Deshalb hat der PC auch einen oder mehrere programmierbare Intervall - Timer (PIT)s spendiert bekommen. Aufbau und Funktionsweise der PITs Der PIT erzeugt von der CPU unabhängige Zeitintervalle aus einem externen Taktsignal von einem Oszillator. Der PIT kennt mehrere Betriebsmodi. Er hat drei voneinander unabhängige Zähler 0 bis 2, die mit je einer Breite von 16 Bit vorkommen. Jeder Zähler bekommt ein eigenes Taktsignal (CLK0 bis CLK2). Somit hat jeder Zähler eine eigene Zeitbasis. Jeder PC besitzt einen Oszillator, der den PIT mit einer Frequenz von 1,19318 MHz versorgt. Im PC arbeitet also jeder Zähler mit derselben Zeitbasis von 0,838 Mikrosekunden. Jeder der Zähler bekommt ein Eingangssignal GATE0 bis GATE2 und jeder hat je einen Ausgang AOT0 bis OUT2. Diese Signale und ihre Bedeutung hängen vom Modi des Zählers ab, und haben unterschiedliche Auswirkungen. Der Datenbuspuffer und die Schreib-/Leselogik erlauben das lesen bzw. schreiben von Daten in bzw. aus dem PIT. Das Steuerregister lädt die Zähler und steuert deren Betriebsmodi. Systemuhr: Betriebssysteme benutzen die Systemuhr zur internen Verwaltung von Uhrzeit und Datum. Dadurch können letzte Änderungen von Dateien festgehalten werden. Neben dieser Systemuhr haben viele PCs auch noch eine Echtzeituhr, die auch dann noch weiter läuft, wenn der Rechner aus ist oder der PIT nicht mehr arbeitet. Der PC kann dadurch die Uhr beim Booten abfragen und die aktuelle Zeit ins zugewiesene CMOS - RAM schreiben. Die Systemuhr wird durch den ersten Zähler des PIT 8253/8254, den PIC 8259A und die Handler - Routinen für die Interrupts 08h und 1ch gesteuert. Speicher - Refresh: Der PIT wird auch zur Speicherauffrischung verwendet. Der Zähler 1 ist dabei reserviert, der alle 18 CLK - Zyklen einen DMA - Chip anweist, eine Blindübertragung durchzuführen. Die Daten werden nach außen auf den Datenbus gelegt und die Leseverstärker, Adresspuffer und Adressdekoder in den Speicherchips aktiviert. Lautsprecher: Hierzu wird der Zähler 2 des PIT gebraucht. Er kann einen bestimmten Ton auf dem Systemlautsprecher (Beeper) erzeugen. Fail - Safe - Timer: Viele Rechner haben einen zweiten PIT, einen 8254, der nur einen Zähler, den Zähler 0 besitzt. Der Ausgang des Zählers ist mit dem NMI - Eingang des Prozessors verbunden. Ein niedrig - hoch Signal am OUT0 erzeugt einen NMI (unmaskierten Interrupt). Das ist immer dann brauchbar, wenn der Rechner sich aufgehängt hat, oder wenn er sich in einer Schleife befindet. Dann kann man nur durch einen Hardware - Reset des Rechners dieser Vorgang sofort abgebrochen werden. Das kann dann passieren, wenn ein Programmfehler alle Hardware - Interrupts mir CLI oder durch Maskierung in den PICs gesperrt worden hat. Der Rechner reagiert zu dieser Zeit auf keine Tastendrücke. Der Handler für den NMI (Interrupt 2) kann aber auch unterscheiden, ob die Quelle der PIT 8254 oder ein Paritätsfehler beim Lesen eines Speicherchips war. Im letzteren Fall handelt es sich um einen groben Hardware - Fehler. 3.3 Der DMA - Chip 8237A Neben der CPU kann ein anderer Chip selbständig auf den Speicher und die Peripheriegeräte zugreifen, der DMA - Chip 8237A. Was heißt DMA.: Direkter Speicherzugriff: (direct memory access) (Eine Adresse im I/O - Adressraum des Prozessors ist ein Port. Über dieses Port wird ein Register in einer Peripherieeinheit angesprochen. Den Hauptbaustein zwischen Hauptspeicher und Peripherie stellt die CPU dar. Einen weiteren stellt aber der DMA - Chip dar. Damit wird der direkte Speicherzugriff konkret ausgeführt. Ist die CPU mit zeitaufwendigen Aufgaben beschäftigt, so kann der DMA - Chip diese entlasten. Die Übertragung durch die CPU findet durch eines seiner Register statt. Das kann natürlich bei einer großen Datenmenge ziemlich lange dauern. Einen Datenpfad zwischen Peripherie und Speicher stellt auch der DMA - Chip her. Die Datenübertragung läuft aber nicht mehr durch diesen hindurch. Der 8237A gibt nur die Adress - und Steuersignale aus. Die Datenübertragung findet über den Datenbus statt und wird vom DMA - Chip kontrolliert. Damit kann ein Peripheriegerät direkt auf den Speicher schreiben und die CPU ist von dieser Aufgabe völlig entlastet. Normalerweise ist den Peripherieeinheiten ein spezieller DMA - Kanal zugewiesen. Das Peripheriegerät kann über ein DREQ (DMA Request - Signal) diesen Kanal aktivieren. Bsp. Diskettenlaufwerk: Die CPU initialisiert die DMA - Steuerung und löst den FDC - Befehl aus. Der Diskettenkontroller spricht das Laufwerk an und positioniert den Lesekopf. Der Lesekopf wird aktiviert, sowie die DMA - Steuerung. Die Daten von Laufwerk werden direkt in einen Puffer im Hauptspeicher geschrieben, den der DMA - Chip eingerichtet hat. Der FD Controller kann anschließend über einen Hardware - Interrupt auf die gelesenen Daten im Hauptspeicher hinweisen. In der Zwischenzeit hat der Prozessor andere Aufgaben erledigt und kann sich jetzt um die Daten vom Laufwerk kümmern. Andere Peripheriechips und -komponenten Der Lautsprecher: Dieser kann Töne verschiedener Frequenz und Länge ausgeben. Der wesentliche Punkt beim Lautsprecher ist der Zähler 2 des PIT 8253/8254. Dabei spielt noch das Bit 0 und 1 des Ports B des PPI - Chips eine Rolle. Der Ausgang OUT des Zählers 2 ist mit einem Gatter und anschließend mit einem Verstärker verbunden. Es gibt zwei Möglichkeiten, den Speaker anzusprechen: Die erste ist über direkte Aktivierung des Lautsprechers über den Zähler 2 im PIT. Die zweite ist das periodische Aktivieren des Verstärkers über den Prozessor. Die erste ist wesentlich besser, da sie ohne Zuhilfenahme des Prozessors und direkt abläuft. PPI 8255 - das programmierbare Peripherie - Interface: Dieser Chip ist nur im PC/XT verwendet worden, weswegen ich nicht auf diesen eingehen werde. CMOS - RAM und Echtzeituhr: Die früheren Rechner mussten über sogenannte DIP - Schalter eingestellt werden. Diese waren fest auf dem Board eingestellt und konnten nur mit Mühe geändert werden. Das ergab Probleme, wenn mehrere Benutzter an einem Rechner arbeiteten, weil dann es vorkam, dass man verschiedene Einstellungen tätigen müsste. Da dies aber schwierig war, hat man es meist gelassen. Außerdem fehlte eine Echtzeituhr, die auch dann noch funktionieren würde, wenn der Rechner nicht im Betrieb ist. Dadurch war es auch früher notwendig, dass man bei jedem Start noch das aktuelle Datum und die aktuelle Zeit eintippen musste. Das ist mittlerweile Vergangenheit. Die Echtzeituhr und der CMOS -RAM werden von einem Akku mit Strom versorgt, was auch nach dem Ausschalten des Rechners nicht zum Datenverlust führt. Der CMOS - RAM wird auch NVR genannt, also ein Non - Volatile - RAM, ein nicht - flüchtiger - Speicher. Die Uhr läuft also ständig im Hintergrund mit. Beim Boot werden beide vom ROM - BIOS gelesen. Die Uhr und der CMOS - RAM sind in einem gemeinsamen Chip. Der CMOS - RAM, der auch Informationen über die Uhrzeit und das Datum enthält, wird ständig von der Echtzeituhr aktualisiert. Leistungsfähigkeiten des Prozessors Registerbreite: Die Bitzahl der Register bestimmt den Umfang des Befehlssatzes des Prozessors, z.B. 8, 16, 32 oder 64 Bit. Taktfrequenz: Die Taktfrequenz bestimmt die Schnelligkeit des Prozessors, z.B. 33, 66, 133 oder 200MHz (Mega-Hertz). Taktfrequenz / Instruktionsrate Die Instruktionsrate gibt die Anzahl der Instruktionen (Befehle ) an, die pro Sekunde erledigt werden können. Gemessen wird die Instruktionsrate in MIPS, d.h. million instructions per second. Die Instruktionsrate ergibt sich, durch Division der Taktfrequenz durch die Anzahl Takte, die für eine Instruktion benötigt werden. Instruktionsrate Beispiel (80386): - Taktfrequenz = 16 MHz = 16.000.000 Takte/Sekunde - 4 Takte/Befehl Instrukt.- Rate = 16.000.000 Takte/Sek. : 4 Takte/Instruktion = 4.000.000 Instruktionen/Sekunde = 4 MIPS Beispiel (80486): - Taktfrequenz = 50 MHz = 50.000.000 Takte/Sekunde 1 Takt/Befehl Instrukt.- Rate = 50.000.000 Takte/Sek. : 1 Takte/Instruktion = 50 MIPS Aufgaben des Prozessors Aufgaben des Leitwerks - Steuerung der Befehlsbearbeitung - Decodierung der Befehle - Ausgabe der für die Befehlsbearbeitung notwendigen Steuersignale Aufgaben des Rechenwerks - Operanden aus dem Arbeitsspeicher holen - Verknüpfung der Operanden - Transfer der Ergebnisse in den Arbeitsspeicher Generationen von Mikroprozessoren Generationen 1. 2. RegisterBreite 4 Bit 8 Bit 3. 16 Bit 4. 32 Bit 5. 64 Bit ProzessorFabrikat INTEL 4000, 4004 Intel 8080, Motorola 6800, Zilog Z80 INTEL 8086, 8088, 80286, Motorola 68000, Zilog Z8000 INTEL 80386, 80486, Pentium, Motorola 68020, 68030, Zilog Z80000 DEC Alpha