Sp1_k15_09_Hauptspeicher

Werbung

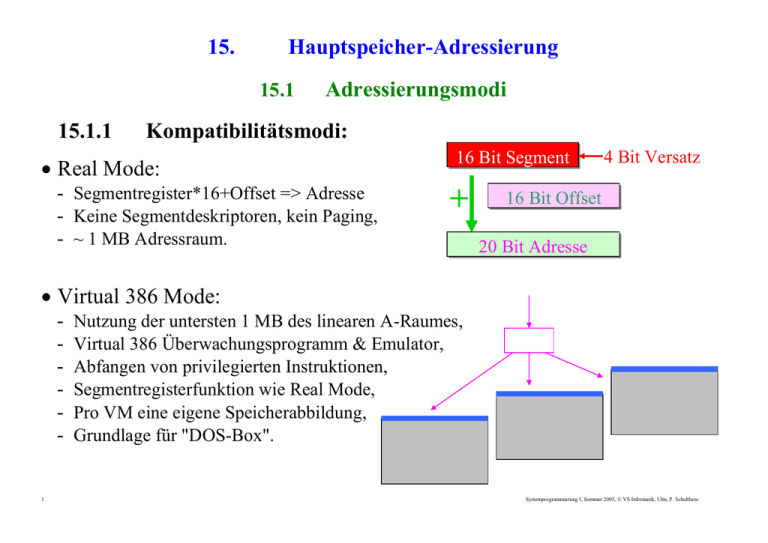

15. Hauptspeicher-Adressierung 15.1 15.1.1 Adressierungsmodi Kompatibilitätsmodi: Real Mode: - Segmentregister*16+Offset => Adresse - Keine Segmentdeskriptoren, kein Paging, - ~ 1 MB Adressraum. 16 Bit Segment + 4 Bit Versatz 16 Bit Offset 20 Bit Adresse Virtual 386 Mode: - 1 Nutzung der untersten 1 MB des linearen A-Raumes, Virtual 386 Überwachungsprogramm & Emulator, Abfangen von privilegierten Instruktionen, Segmentregisterfunktion wie Real Mode, Pro VM eine eigene Speicherabbildung, Grundlage für "DOS-Box". Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.1.2 Protected Mode: Segmentregister sind nun Segmentselektoren. Deskriptoren für Speichersegmente. 16 verschiedene Segmenttypen. Segmentselektor Paging ab Intel/386 möglich. 64 Terabyte Adressraum. Segmentdeskriptoren 4 Privilegierungsebenen. 32 Bit Adresse Segment-Basis + 32 Bit Adresse 2 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.1.3 Long Mode für Athlon 64 Prozessoren Zusätzliche Stufen der Adressübersetzung Einfachere Speichersegmentierung. Erweiterung auf 64 Bit. Erweiterung des Registersatzes: - General Purpose Register, - SSE/XMM Register. - Instruction Pointer, 3 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.1.4 Adressierung im Protected Mode Segmentierung und Paging kombinierbar: GDTR LDTR Segmentselektor Lokale Deskriptortabelle Segment-Basis Globale Deskriptortabelle Page Directory CR3 4 Virtuelle 32 Bit Adresse + Lineare Adresse Page DeskriptorDeskriptorPage tabelle Deskriptortabelle Tables tabelle + Physikalische Adresse ! Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.2 15.2.1 Register ab i386 Sichtbare Register Für Anwendungsprogramme zugänglich. Arbeitsregister: - Mit Segmentregister verbunden, - aber umsteuerbar mit einem Präfix. Funktionsbezogene Register: - Flags (mit IO-Privilege Level), - Daten, Extra-Daten, - Stack, Code. Spätere Register (nicht 386): - SSE – Streaming SIMD Extension, - MMX - Multimedia Extension, - Gleitkomma Operationen. 5 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.2.2 Unsichtbare Register Zweck: - Caching der Deskriptoren, Erweiterte Adresse im Protected Mode, Zugriffsschutz & Prozessorsteuerung, Betriebssystemaufruf. Kontrollregister CR0..CR3/4. Weitere Register: - Debug & Test Register, - Boundary Scan .... Modellspezifische Register MSR: - Monitoring & Profiling, - Memory Type Range Register, - Page Attribute Table… 15.2.3 6 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.2.3 Evolution vs. Komplikation Die Segmentregister arbeiten im Protected Mode als 16 Bit Segmentselektoren: Im Segmentselektor liegt ein Index in die globale oder die lokale Deskkriptortabelle. Gleichzeitig mit dem Segmentregister wird implizit der Segmentdeskriptorcache geladen. Dabei geschehen unter Umständen mehrere Hauptspeicherzugriffe. Auch für das aktuelle Task-State Segment und die lokale Deskriptortabelle werden Deskriptoren gepuffert (cached). Selektorregister TSSX und LDTX können gelesen werden. 7 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.2.4 4(5) Kontrollregister: Maschinenkonfigurierung, Maschineneigenschaften, Seitentabellen. CR0 PG CR0: - Paging, Taskswitch, Coprocessor, Protected Mode. 15.3 8 CR1 ...... TS, EM, MP, PE reserviert PageFault Adresse CR3 PageDirectory Adresse CPU Erweiterungen CR4 CR2 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.3 15.3.1 Segmentdeskriptoren Datenstrukturen Originaldeskriptoren liegen in lokaler oder globaler Deskriptortabelle. Segmentdeskriptor-Caches unsichtbar in der CPU vorhanden. Potential für einen segmentierten virtuellen Speicher ohne Seiteneinteilung: - evtl. Segment-Deskriptoren ein- & auslagern und Selektoren ergänzen. gleichzeitig jeweils 8000 lokale und 8000 globale Deskriptoren, anstatt eines Zeigers nur ein Segment-Selektor, für jedes Objekt einen Segmentdeskriptor, Evtl. LDT-Register umsetzen. Schutzfunktion bei Segmentierung: - Protection Level ( 0 ... 3)=(privileged ... non-priv.) - Zugriffsmodus (exec, read, write ), - Feldlänge im Deskriptor. 9 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.3.2 Deskriptor für Applikationssegmente: Intel 286 "Historium". Granularität der Länge: - 1 Byte / 4K. 32-Bit oder 16-Bit Instruktionen & Adressen. Beim Zugriff auf ein ausgelagertes Segment erfolgt ein Interrupt an das OS. Applikation-Deskriptoren haben DT=true. Nur Deskriptoren mit gleicher oder schlechterer Sicherheitsstufe dürfen „einfach selektiert“ werden (CS). 10 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.3.3 Kennung für Applikationssegemente Bit#11=true (EXE-Bit): Code - Codesegment, darf ausgeführt werden, - darf auch gelesen werden, falls Bit#9=true (W/R), - falls Bit#10=true (conforming), ausführbar durch unterprivilegiertes Segment. Bit#11=false (EXE-Bit): Data - Datensegment, nicht ausfühbar, - schreiben, falls Bit#9=true (W/R), - falls Bit#10=true (abwärts), erstreckt sich das Segment von der Basisadresse nach unten (Stack). Bit#8=true (Access-Bit): - dieses Segment wurde benützt, - nützlich für die Speicherauslagerungsstrategie. 11 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.3.4 Intel386 System-Segmente Haben das DT-Bit gelöscht (286er Segmente weggelassen). Call-Gate Deskriptor (Typ = 12): - 12 beschreibt den Einsprung in eine geschützte Routine, normalerweise in einem anderen Segment (far call), referenziert einen weiteres Segmentdeskriptor, ändert kurzzeitig die Privilegierungsebene, übernimmt bis zu 124 Parameterbytes: Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess Interrupt-Deskriptoren (Typ = 14): - Beschreibt den Einsprung in eine Interruptroutine, - 8 Byte Einträge in der Interrupt-Deskriptortabelle, - IDT-Basis/Limit geladen über LIDT-Instruktion, Trap-Gate Deskriptoren (Typ = 15) arbeiten ähnlich wie Interruptdeskriptoren, jedoch ohne die Interrupts zu maskieren: LDT Segmentdeskriptor (Typ = 2): 13 kann nur in der Globalen Deskriptortabelle liegen, wird durch eine LLDT-Instruktion geladen, beschreibt eine Lokale Deskriptortabelle, Format wie Applikationsdeskriptor. Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess Task-Gate Deskriptor (Typ = 5): - referenziert ein Task-State Segment (TSS), - evtl. mehrere Task-Gates für ein TSS, - enthält Privilegierungsstufe: Ein Task-Switch erfolgt falls: - laden von Selektor für Task-Gate oder TSS, i.e. Call- oder Jump-Instruktion, Interrupt oder Exception, IRET v. nested Task. 14 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess Task-State Segment Deskriptor (Typ = 9/11): - Enthält aktuellen/geretteten Prozessorzustand (TSS), - Segmentselektor für lokale - Deskriptortabelle, Basisadresse für Seitentabellendirectory, Stacks der Privilegierungstufen 0,1,2, aktuell sichttbare Prozessorregister, Zugriffsmaske für die E/A-Ports, Link zum vorherigen Tasksegm., aktives TSS mit Typ=11, Nested-Task Flag. 15.3.5 15 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.3.5 Zugriffsschutz-Mechanismen Schutzverletzung falls ein besser privilegierter Deskriptor geladen wird. Zugang zu besserer Privilegierung über Gate-Deskriptoren: - Inanspruchnahme von Betriebssystemdienste und dergleichen, - Call, Trap, Interrupt, Task (TSS) - Ausnahme: Conforming Deskriptors* Vier Privilegierungsebenen: 3: 2: 1: 0: Anwendungsprogramme, Laufzeitumgebungen, GUI ... Gerätetreiber, Kernel. 0 1 2 3 Privilegierungscode: - CPL im aktuellen Codesegment, RPL im Selektorargument, DPL im Deskriptor, IOPL in Flags. * greifen auf geschützte Daten im Auftrag einer Applikation zu. 16 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.4 Paging und MMU Für ausgelagerte Seiten (Pages) wird beim Zugriff eine Exception erzeugt & die Seite wird vom OS eingelagert (ähnlich wie bei ausg. Segmenten). Die Memory Management Unit (MMU) besorgt die Adressübersetzung: - Adressübersetzung für jeweils eine Speicherseite mit 4 KB fester Länge (z.B.), Übernimmt eine sog. lineare Adresse 32-Bit von der Segmentierung, Liefert eine 32-Bit physikalische Adresse, zweistufige Übersetzungstabelle, Paging Segmentierung. TLB: - 17 Translation look-aside Buffer, Enthalten die letzten Mappings, beispielsweise 100 Einträge, evtl. explizit „flushen“, hier nicht gezeigt. Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.4.1 Seitentabelleneintrag (Intel Pentium) : Kacheladresse nur gültig, wenn die Seite im Hauptspeicher vorhanden ist. Page Frame/Kachel-Adresse 20 Im Falle eines Seitenfehlers (Page fault) holt das OS die Seite vom Sekundärspeicher. Caching Strategie und Schreibrechte. 18 Avail Avail 12 Nutzbar für Betriebssystem 00 12 dirty accessed PCD PWT U/S W/R P beschrieben Use-Bit Seite hat Cache Disabled Cache durchschreiben User Seite, nicht Supervisor Seite beschreibbar Präsenz Bit, Seite vorhanden Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.5 Adressübersetzung im Long-Mode (Athlon 64) Erweiterung der MMU auf 4 Stufen: - 3. Stufe Page Directory Pointer Table, - PageMap4L als vierte Stufe, - Tabelleneinträge 64 Bits. Derzeitige Implementierung: Nur noch rudimentäre Segmentierung: - Basisadresse >0 for FS, GS, - Attribute für CS, DS. - Logische Adresse erst bis 48 Bits, - Physikalische Adresse bis 40 Bits, - obere Bits reserviert. 19 Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess 15.6 Grafik-Adressübersetzungstabelle abgekürzt "GART": - greifen als Busmaster in den Hauptspeicher hinein, - arbeiten auf logischen Koordinaten & Strukturen. Physikalische Buszugriffe: 20 für normale PCI-Geräte, über den PCI Bus, über Hostbus, zum Cache. AGP Grafikadapter (3D) Logische Adressen 3D-Grafikadapter: CPU: (Treiber/SW) MMU Physikal. Adressen - findet sich in AGP-fähigen Host-Bridges, - übersetzt logische Speicherzugriffe in physikalische, - Grafiktreiber setzt explizit die Tabelleneinträge. GART Host-Brücke (PCI/AGP) Hauptspeicher Systemprogrammierung I, Sommer 2005, © VS Informatik, Ulm, P. Schulthess