F.1. Einordnung

Werbung

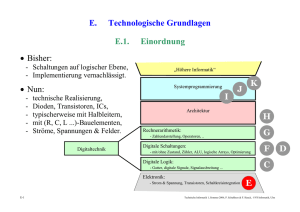

F. Programmierbare Logik F.1. Einordnung Bisher: - wenige Schaltkreise pro Chip, - feste Verdrahtung. „Höhere Informatik“ Nun: - Systemprogrammierung Generischer Schaltkreis, Löschen & programmieren, Umfangreiche Funktionalität, Einstellbare Logikfunktionen, Einstellbare Verdrahtung, I J K Architektur H G Rechnerarithmetik: - Zahlendarstellung, Operatoren, .. Digitaltechnik Digitale Schaltungen: - mit/ohne Zustand, Zähler, ALU, logische Arrays, Optimierung C Digitale Logik: - Gatter, digitale Signale, Signalausbreitung ... Elektronik: - Strom & Spannung, Transistoren, Schaltkreisintegration E-1 F E Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm D F.2. Tri-State-Ausgabelogik F.2.1 Elektronische Bussysteme BUS: Gruppe von parallelen Leitungen zum Datenaustausch.. Bus im Rechenwerk => - Bidirektional, - z.B. 32 Bit Daten, - von & zum Register. ALU Register Register Register Register Bus Busysteme in einem Standard-PC: - versch. Geschwindigkeit & Breite, - Daten- & Adresse, - Arbitrierung. CPU FSB RAM RAM N-Bridge Device Device PCI - Bus IDE IDE S-Bridge Device Device ISA - Bus E-2 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.2.2 Ausgabepegel elektronischer Digitalschaltungen Bisher 2 Zustände: - Zustand „Logisch 0“: geringe Spannung, geringer Stromfluss - Zustand „Logisch 1“: hohe Spannung, hoher Stromfluss, - oder umgekehrt. Problem: zwei Ausgänge auf derselben Leitung - elektrischer Kurzschluss je nach Ausgabewert - bzw. Spannungen im verbotenen Bereich, - undefinierter logischer Zustand. => Zusätzlicher Zustand: - Ausgang soll sich gelegentlich elektrisch neutral verhalten, - Passt sich dem bestehenden Zustand auf dem Bus an, - Ähnlich „do not care“. E-3 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm Lösung: Tri-State-Puffer: E „Enable“ Signal, Y „evtl. hochohmiger Ausgang“, - oft mit invertiertem Enabler E, - Ausgabepegel „floatet“, falls enable, Open-Kollektor Schaltung als Alternative: - „Wired-OR, Wired-AND, E-4 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.2.3 Zugang zum Bus nur über Tri-State-Puffer Enable: - Das Schaltwerk legt seinen Ausgang auf den Bus, - Hoffentlich ist nur ein Sender am Bus „enabled“. Ein bestimmter Datenpfad kann gezielt ausgewählt werden: - Mehrere Empfänger möglich. E-5 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.3. SPLD - Simple Programmable Logic Devices Einfache programmierbare Logikbausteine: - Im wesentlichen keine Rechenfähigkeit, - Typischerweise Festwertspeicher. ROM - Read Only Memory: - Werte/Bitmuster bei Herstellung festgelegt, - Z.B. durch eine letzte Metallisierung. Dioden als Koppelelement: - Koppeln das Lesesignal auf die Ausgangsleitung. ? ? ! E-6 ! Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm PROM – Programmable Read Only Memory - einmalig durch Anwender programmierbar, - z.B. durchschmelzen von Sicherungen. E-7 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.3.1 Beispiel: 8 x 4 Bit PROM Funktionsweise - Adressleitungen selektieren Speicherzelle, - Inhalt an Ausgabeleitung abgreifbar: Koppelelement E-8 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.4. EPROM/EEPROM/Flash Erasable Programmable Read Only Memory (EPROM): - elektrisch programmierbar (durch Überspannungen). - durch UV-Bestrahlung löschbar, Electrically Erasable PROM (EEPROM, E2PROM): - Etwa zur Speicherung des BIOS eines PCs, - elektrisch programmierbar, - elektrisch löschbar. Flash-Speicher: - Etwa zur Speicherung von Photos in digitalen Kameras, - ähnlich EEPROM aber geringere Größe, - blockweise programmier- und löschbar. E-9 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.5. PROM als Schaltnetz Schematische Darstellung eines PROM - Programmierbare ODER-Matrix mit Koppelelementen, - Adressdekoder als feste UND-Matrix, - Minterme über Adressleitungen, PROM kann Schaltfunktionen implementieren: - E-10 pro Wertekombination der Eingänge wird ein Ergebnis direkt programmiert. 2m Worte à n Bit realisieren n Schaltfunktionen mit je m Eingängen, Wahrheitstabelle in Hardware abgebildet, keine Minimisierung üblich. Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.5.1 Beispiel: 2x2-Multiplizierer Werte in PROM „brennen“: - Adresse fest vordecodiert, - Wahrheitstabelle (C10.1): Mult 0x0=0 0x1=0 0x2=0 0x3=0 1x0=0 1x1=1 1x2=2 1x3=3 2x0=0 2x1=2 2x2=4 2x3=6 3x0=0 3x1=3 3x2=6 3x3=9 E-11 a 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 b 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 c 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 d 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 y3 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 y2 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 0 y1 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 y0 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.6. PAL - Programmable Array Logic Charakteristiken: - feste ODER-Matrix, - frei programmierbare UND-Matrix, - feste Anzahl UND-Gatter pro ODER-Gatter (hier 4). PAL kann jede minimisierte Schaltfunktion realisieren, falls Anzahl Produktterme pro Schaltfunktion klein genug: - Hier 4 Produktterme pro SF. E-12 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.6.1 Begriff PAL Eingetragenes Warenzeichen der Fa. AMD bzw. Lattice Technik - ursprünglich in TTL- später auch CMOS-Technik, - ursprünglich einmalig programmierbar, - heute auch löschbare Varianten. Varianten (siehe auch GAL) - E-13 Rückkopplung der Ausgänge als interne Eingänge, normaler oder invertierter Ausgang, getaktet / ungetaktete Flip-Flops, Flip-Flops an den Ausgängen, Tri-State-Ausgänge. Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.7. GAL - Generic Array Logic Funktionsweise wie PAL, jedoch flexiblere Ausgabelogik, anschliessend an PAL-Array (nicht gezeigt). Beispiel: Output Logic Macro Cell (OLMC): E-14 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm E-15 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm E-16 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm E-17 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm E-18 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm Rückkoppelung des Ausganges Ausschließlich CMOS Technik Markenzeichen der Fa. Lattice Reprogrammierbar durch E2CMOS-Technologie (ähnlich EEPROM) E-19 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.8. PLA - Programmable Logic Array (PLA) ODER-Matrix ebenso wie UNDMatrix frei programmierbar. Realisiert beliebige Schaltfunktionen, falls Anzahl der Produktterme ausreichend. E-20 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.9. CPLD - Complex Programmable Logic Device Alternativbezeichnungen (Markennamen): - EPLD, EEPLD, PEEL, MAX, SuperPAL, MegaPAL ... Zusammenfassung der Funktionalität bis zu etwa 100 GAL-Bausteine Makrozellen: - für Ausgabelogik (I/O-Blocks) - für Berechnung der Schaltfunktionen - „Borgen“ zusätzlicher UND-Glieder für Produktterme aus anderen Makrozellen. Verschaltung der internen GALs/Makrozellen: - mit einer programmierbaren Zuordnungsmatrix, - vollständige oder unvollständige Verschaltung. Programmierung wie EPROM, EEPROM oder Flash-ROM: - Anders als FPGA keine Startup- bzw. Ladeverzögerung. E-21 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.9.1 Blockschaltbild für Makrozellenorganisation: Verschiedene Makrozellen bilden einen Logik-Block: - GAL-Zellen, ALU-Zellen, Registerzellen, ... - Configurationspeicher ... GAL E-22 Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.10. FPGA - Field Programmable Gate Array Alternativbezeichnungen (Markenzeichen): - LCA, pASIC, FLEX, APEX, ORCA, SPGA ... Aufbau - bis zu mehreren 10.000 Makrozellen für Schaltfunktionen und Flip-Flops, - programmierbare Kommunikationsinfrastruktur zwischen den Zellen, - große oder kleine Logikzellen. Programmierung: - E-23 wie EPROM, EEPROM oder Flash-ROM, Programmierung mit flüchtigem Speicher (RAM), Hochfahren des FPGA durch externen Speicher (z.B. PROM), Umprogrammierung im laufenden Betrieb möglich. Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm F.10.1 E-24 FPGA Blockschaltbild Technische Informatik 1, Sommer 2006, P. Schulthess & F. Hauck, ©VS Informatik, Ulm