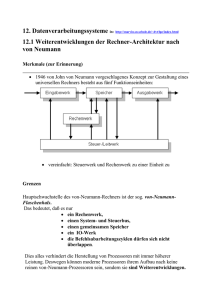

DOCX - Technische Universität Chemnitz

Werbung