Spicker-Seite-20047_de - Ewig Drohendes Versagen

Werbung

Best-Effort-Dienst: 1. Pakete können verloren gehen, 2. Pakete können in einer anderen

Reihenfolge empfangen werden, als sie gesendet wurden, 3. über die Dauer des Transports

eines Pakets bis zur Ankunft beim Empfänger wird keine Aussage gemacht, 4. es werden keine

Zusagen über die Bandbreite zwischen Sender und Empfänger gemacht, 5. es werden keine

Informationen bzgl. einer Überlastung des Netzwerks an den Sender oder Empfänger

weitergegeben.

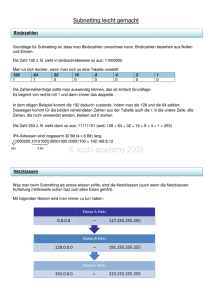

Cache Treffer

rw auf Cache=2ns inkl. Suche und Ablage = 10ns

Aufgabe: Reduzierung der durchsch. Zugriffszeit auf 4ns

Lösung: x*2ns+(1-x)*10ns=4ns -> x=0,75 -> 75%

IP Adressen: 32 Bit: 2^8.2^8.2^8.2^8 – IP Adresse + AND Operation – die Netzwerkmaske

identifiziert somit das Netzwerk. A0, B10, C110, D1110, E11110 Notation: a.b.c.d/xx (Bit).

Geschwindigkeit bps immer in 10^x

Verzögerungen:

Ausbreitungsverzögerung tprop: ist die Zeit welche ein einziges Bit benötigt um sich vollständig

auf der Leitung auszubreiten - gleich der Entfernung der Hosts A und B geteilt durch die

Ausbreitungsgeschwindigkeit, tprop=d/v in ms oder s

Übertragungsverzögerung ttrans: ist die Zeit, die für die Übertragung aller Paketbits (gesamte

Nachricht auf) auf der Verbindungsleitung erforderlich ist. Wenn die Paketgröße L Bit und die

Übertragungsrate R auf der Verbindungsleitung von Host A zum Host B sind, dann ist. ttrans=L/R

in ms oder s Zum Zeitpunkt ttrans werden alle Paketbits fertig auf die Verbindungsleitung

gebracht, also hat das letzte Bit des Pakets gerade den Host A verlassen.

Verbreitungsverzögerung: Die Zeit, die ein Router für die Feststellung benötigt, wohin das Paket

weiterzuleiten ist, ggfs. Auch die Zeit, um Bitfehler zu entdecken, die durch Störungen auf der

Leitung bei der Übertragung auftreten können.

Warteschlangenverzögerung: Die Zeit, die das Paket in einer Warteschlange eines Routers

verbringt, um auf die Übertragung auf einer ausgehenden Verbindungsleitung zu warten.

Ende-zu-Ende-Verzögerung: Wenn die Verarbeitungs- und Warteschlangenverzögerungen

ignoriert werden, dann ist die Ende-zu-Ende-Verzögerung des Pakets die Summe der

Ausbreitungs- und Übertragungsverzögerungen, also (d/v + L/R) in ms oder s

Zusammenhang trans und tprop:

Nachdem das erste Bit des Pakets zum Zeitpunkt t = 0 auf die Verbindungsleitung gebracht wird,

breitet es sich mit Geschwindigkeit v in die Richtung des Hosts B aus. Wenn die Entfernung d

zwischen Host A und B groß genug ist, dann hat das erste Bit die Entfernung zum Host A

(v*ttrans) hinter sich gelegt. D. h. wenn d <= v ⋅ L / R, oder d/v <= L / R, oder tprop <= ttrans ist,

dann befindet sich das erste Bit zum Zeitpunkt ttrans schon beim Host B.

Entfernung: Aus tprop=trans folgt d=v*(L/R)

Paging: jede Adresse adressiert ein WORT

Adresslänge: (logischer Speicher) / (Wortgröße) = 2^x Byte, = x Bit

Die Adressbusbreite entspricht der Anzahl der Binärstellen, die notwendig ist, um alle Worte

adressieren zu können. Bei 2^{x} Worten werde genau x Binärstellen benötigt.

max. Einträge in der Seitentabelle: (logischer Speicher) / (Seitengröße)

Anzahl Seitenrahmen: (phys. Speicher) / (Seitengröße) = 2^n Seitenrahmen

Größe eines Eintrags der Seitentabelle: n Bit

Seitengröße i.W.: Seitengröße in KB / Wortgröße (16KB/8B=2^14/2^3=2^11)

physische zu logischer Adresse: (phys. Adresse) / (Seitengröße i.W.) = A Rest B

log. Adresse = A-zu-Seitenrahmennummer * Seitengröße + B (Offset)

logische zu physischer Adresse: (log. Adresse) / (Seitengröße i.W.) = C Rest D

phy. Adresse = C-zu-Seitennummer * Seitengröße + D (Offset)

kleine Seitengrössen: Problem der internen Fragmentierung ist viel kleiner

-> lange Seitentabellen, wodurch die Effizienz der Speicherzugriffe sinkt.

grosse Seitengrössen: Seitentabellen der Prozesse werden kürzer

-> interne Fragmentierung steigt.

externe Fragmentierung: Menge der existierenden Prozesse ständig ändert, entstehen in den

Adressräumen der Prozesse im HS Lücken.

interne Fragmentierung: Bei der Seiteneinteilung wird der Speicher in Seiten mit fester Größe

eingeteilt. Sobald ein Programm Speicher beantragt (alloziert), werden so viele Seiten reserviert,

dass die Summe der reservierten Seiten größer oder gleich dem beantragten Speicher ist. Ist die

beantragte Menge kleiner als die Summe des Speichers der reservierten Seiten, so bezeichnet

man diese Differenz als interne Fragmentierung: dieser Verschnitt liegt innerhalb des

reservierten Bereiches, typischerweise am Ende. Zum Beispiel: Das Betriebssystem verwaltet

den Arbeitsspeicher in Seiten mit einer Größe von 4 Kilobyte. Ein Programm beantragt 5 kByte.

Daraufhin reserviert das Betriebssystem 2 Seiten (8 kByte). Die interne Fragmentierung beträgt

3 Kilobyte.

Dateisysteme: FAT: File Allocation Table:

Datenverzeichnis phys. Adr. [i] von Dateiblock 0 FAT[i] enthalt dann Eintrag zu FAT[j]

Verkettung der physischen Blockadresse in FAT-> [j]361->[k]24->[l]88->eof

(Partitionsgröße) / (Blockgröße) = 2^n Blöcke - Blockadresslänge = n bit,

FAT-Größe = Blöcke * Blockadresslänge (2^n * n) Bsp: (2^16bit * 2^4bit) -> [2^4=16]

FAT-Größe in Blöcken = (FAT-Größe) / (Blockgröße)

Ein Block kann (Blockgröße) / (Blockadresslänge) viele Adressen enthalten.

Ein inode kann maximal adressieren: 12 direkt, erster Bruch einfach, zweiter Bruch zweifach und

dritter Bruch dreifach indirekt: 12 + [(Blockgröße)/(Blockadresslänge)] +

[(Blockgröße)/(Blockadresslänge)]^2 + [(Blockgröße)/(Blockadresslänge)]^3

HTTP 1.0: nur nicht persistente Verbindungen, Verbindung wird nach Übertragung wieder

abgebaut. HTTP 1.1 auch persistente Verbindungen, Verbindung bleibt offen, kann durch

Benutzer oder Time-out-Intervall geschlossen werden.

Portnummern 0 bis 1023 - bekannte Anwendungsprotokolle. 16 Bit, bis 65.536

Prüfsumme: Alle Bit-Wörter des Segments werden zusammen addiert, Überläufe auch. Davon

wird das 1er Komplement gebildet (0 mit 1 und 1 mit 0 aus-tauschen). Bit Wörter + Prüfsumme =

1111...

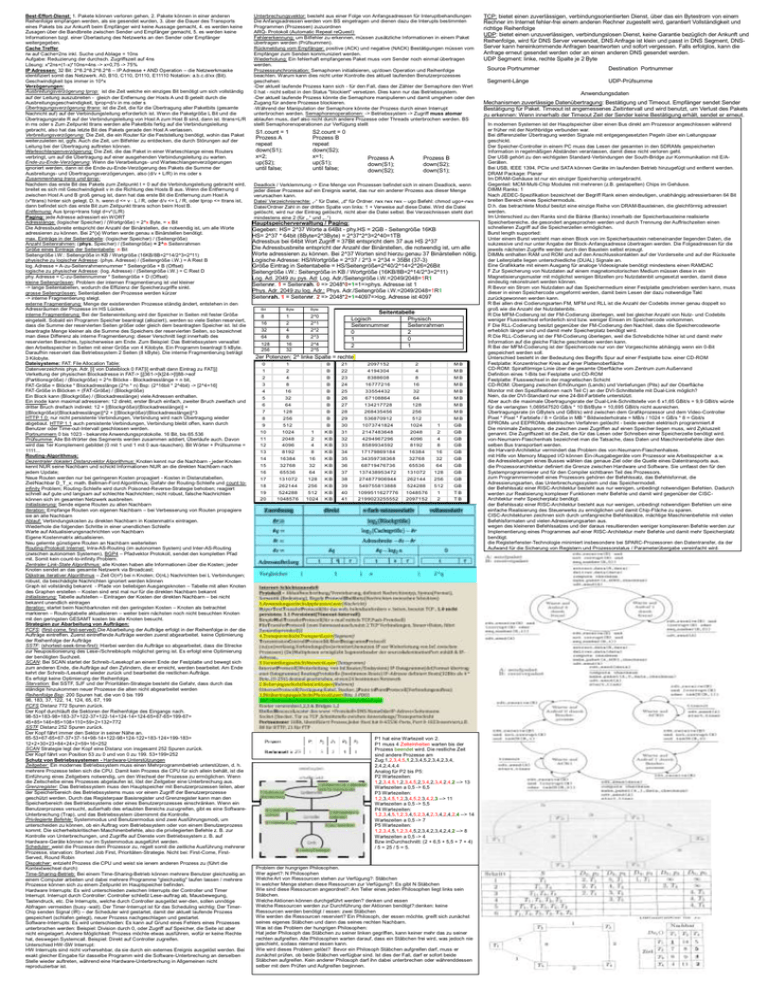

Routing-Algorithmus:

Dezentraler (lokaler) Distanzvektor Algorithmus: Knoten kennt nur die Nachbarn - jeder Knoten

kennt NUR seine Nachbarn und schickt Informationen NUR an die direkten Nachbarn nach

jedem Update;

Neue Routen werden nur bei geringeren Kosten propagiert - Kosten in Distanztabellen,

Ziel/Nachbar D_T_x; math. Bellman-Ford Algorithmus; Gefahr der Routing-Schleife und count toinfinity Problem; Routing-Schleife wird durch Poisoned-Reverse-Strategie behoben; reagiert

schnell auf gute und langsam auf schlechte Nachrichten; nicht robust, falsche Nachrichten

können sich im gesamten Netzwerk ausbreiten.

Initialisierung: Sende eigene Routen zu allen Nachbarn

Iteration: Empfange Routen von eigenen Nachbarn – bei Verbesserung von Routen propagiere

sie an alle Nachbarn

Ablauf: Verbindungskosten zu direkten Nachbarn in Kostenmatrix eintragen.

Wiederhole die folgenden Schritte in einer unendlichen Schleife

Warte auf Aktualisierungsnachrichten von Nachbarn

Eigene Kostenmatrix aktualisieren.

Neu gelernte günstigere Routen an Nachbarn weiterleiten

Routing-Protokoll Internet: Intra-AS-Routing (im autonomen System) und Inter-AS-Routing

(zwischen autonomen Systemen), BGP4 – Pfadvektor Protokoll, sendet den kompletten Pfad

mit. Somit kein count-to-infinity Problem.

Zentraler Link-State Algorithmus: alle Knoten haben alle Informationen über die Kosten; jeder

Knoten sendet an das gesamte Netzwerk via Broadcast;

Dijkstras iterativer Algorithmus – Zeit O(n²) bei n Knoten; O(nL) Nachrichten bei L Verbindungen;

robust, da beschädigte Nachrichten ignoriert werden können

Graph ist vollständig bekannt - Pfade von beliebigen Ausgangsknoten – Tabelle mit allen Knoten

des Graphen erstellen – Kosten sind erst mal nur für die direkten Nachbarn bekannt

Initialisierung: Tabelle aufstellen – Eintragen der Kosten der direkten Nachbarn – bei nicht

bekannt unendlich eintragen

Iteration: startet beim Nachbarknoten mit den geringsten Kosten – Knoten als betrachtet

markieren – Routingtabelle aktualisieren – weiter beim nächsten noch nicht besuchten Knoten

mit den geringsten GESAMT kosten bis alle Knoten besucht.

Strategien zur Abarbeitung von Aufträgen:

FCFS: (first-come, first-served) Die Abarbeitung der Aufträge erfolgt in der Reihenfolge in der die

Aufträge eintreffen. Zuerst eintreffende Aufträge werden zuerst abgearbeitet. keine Optimierung

der Reihenfolge der Aufträge

SSTF: (shortest-seek-time-first): Hierbei werden die Aufträge so abgearbeitet, dass die Strecke

zur Neupositionierung des Lese-/Schreibkopfs möglichst gering ist. Es erfolgt eine Optimierung

der benötigten Suchzeit.

SCAN: Bei SCAN startet der Schreib-/Lesekopf an einem Ende der Festplatte und bewegt sich

zum anderen Ende, die Aufträge auf den Zylindern, die er erreicht, werden bearbeitet. Am Ende

kehrt der Schreib-/Lesekopf wieder zurück und bearbeitet die restlichen Aufträge.

Es erfolgt keine Optimierung der Reihenfolge.

Starvation: Bei SSTF, SJF und der Prioritäten-Strategie besteht die Gefahr, dass durch das

ständige hinzukommen neuer Prozesse die alten nicht abgearbeitet werden

Reihenfolge Bsp: 200 Spuren hat, die von 0 bis 199

98, 183, 37, 122, 14, 124, 65, 67, 199

FCFS Distanz 772 Spuren zurück.

Der Kopf durchläuft die Sektoren der Reihenfolge des Eingangs nach.

98-53+183-98+183-37+122-37+122-14+124-14+124-65+67-65+199-67=

45+85+146+85+108+110+59+2+132=772

SSTF Distanz 252 Spuren zurück.

Der Kopf fährt immer den Sektor in seiner Nähe an.

65-53+67-65+67-37+37-14+98-14+122-98+124-122+183-124+199-183=

12+2+30+23+84+24+2+59+16=252

SCAN Strategie legt der Kopf eine Distanz von insgesamt 252 Spuren zurück.

Der Kopf fährt von Position 53 zu 0 und von 0 zu 199. 53+199=252

Schutz von Betriebssystemen - Hardware-Unterstützungen

Zeitgeber: Ein modernes Betriebssystem muss einen Mehrprogrammbetrieb unterstützen, d. h.

mehrere Prozesse teilen sich die CPU. Damit kein Prozess die CPU für sich allein behält, ist die

Einführung eines Zeitgebers notwendig, um den Wechsel der Prozesse zu ermöglichen. Wenn

die Zeitscheibe eines Prozesses abgelaufen ist, löst der Zeitgeber eine Unterbrechung aus.

Grenzregister: Das Betriebssystem muss den Hauptspeicher mit Benutzerprozessen teilen, aber

der Speicherbereich des Betriebssystems muss vor einem Zugriff der Benutzerprozesse

geschützt werden. Durch das Registerpaar Basisregister und Grenzregister kann man den

Speicherbereich des Betriebssystems oder eines Benutzerprozesses einschränken. Wenn ein

Benutzerprozess versucht, außerhalb des erlaubten Bereichs zuzugreifen, gibt es eine SoftwareUnterbrechung (Trap), und das Betriebssystem übernimmt die Kontrolle.

Privilegierte Befehle: Systemmodus und Benutzermodus sind zwei Ausführungsmodi, um

unterscheiden zu können, ob ein Auftrag vom Betriebssystem oder von einem Benutzerprozess

kommt. Die sicherheitskritischen Maschinenbefehle, also die privilegierten Befehle z. B. zur

Kontrolle von Unterbrechungen, und Zugriffe auf Dienste vom Betriebssystem z. B. auf

Hardware-Geräte können nur im Systemmodus ausgeführt werden.

Scheduler: weist die Prozesse dem Prozessor zu, regelt somit die zeitliche Ausführung mehrerer

Prozesse, starvation: Shortest Job First, Prioritäten-Strategie. Nicht bei: First-Come, FirstServed, Round Robin

Dispatcher: entzieht Prozess die CPU und weist sie ienem anderen Prozess zu (führt die

Kontextwechsel durch)

Time-Sharing-Betrieb: Bei einem Time-Sharing-Betrieb können mehrere Benutzer gleichzeitig an

einem Computer arbeiten und dabei mehrere Programme "gleichzeitig" laufen lassen / mehrere

Prozesse können sich zu einem Zeitpunkt im Hauptspeicher befinden.

Hardware Interrupts: Es wird unterschieden zwischen Interrupts der Controller und Timer

Interrupt. Interrupt durch Controller: Controller schließt Lese-auftrag ab, Mausbewegung,

Tastendruck, etc. Die Interrupts, welche durch Controller ausgelöst wer-den, sollen unnötige

Abfragen vermeiden (busy -wait). Der Timer-Interrupt ist für das Scheduling wichtig: Der TimerChip senden Signal (IR) – der Scheduler wird gestartet, damit der aktuell laufende Prozess

gespeichert (schlafen gelegt), neuer Prozess nachgeschlagen und gestartet.

Software-Interrupts: Es wird unterschieden: Es kann auf Grund eines Fehlers eines Prozesses

unterbrochen werden: Beispiel: Division durch 0, oder Zugriff auf Speicher, die Seite ist aber

nicht eingelagert. Andere Möglichkeit: Prozess möchte etwas ausführen, wofür er keine Rechte

hat, deswegen Systemcall. Beispiel: Direkt auf Controller zugreifen.

Unterschied HW-SW Interrupt:

HW Interrupts sind nicht vorhersehbar, da sie durch ein externes Ereignis ausgelöst werden. Bei

exakt gleicher Eingabe für dasselbe Programm wird die Software-Unterbrechung an derselben

Stelle wieder auftreten, während eine Hardware-Unterbrechung in Allgemeinen nicht

reproduzierbar ist.

Unterbrechungsvektor: besteht aus einer Folge von Anfangsadressen für Interuptbehandlungen

Die Anfangsadressen werden vom BS eingetragen und dienen dazu die Interupts bestimmten

Programmen (Prozessen) zuzuordnen

ARQ- Protokoll (Automatic Repeat reQuest):

Fehlererkennung: um Bitfehler zu erkennen, müssen zusätzliche Informationen in einem Paket

übertragen werden (Prüfsummen).

Rückmeldung vom Empfänger: positive (ACK) und negative (NACK) Bestätigungen müssen vom

Empfänger zum Senden kommuniziert werden.

Wiederholung: Ein fehlerhaft empfangenes Paket muss vom Sender noch einmal übertragen

werden.

Prozesssynchronisation: Semaphoren initialisieren, up/down Operation und Reihenfolge

beachten. Warum kann dies nicht unter Kontrolle des aktuell laufenden Benutzerprozesses

geschehen:

-Der aktuell laufende Prozess kann sich - für den Fall, dass der Zähler der Semaphore den Wert

0 hat - nicht selbst in den Status "blockiert" versetzen. Dies kann nur das Betriebssystem.

-Der aktuell laufende Prozess könnte die Semaphore manipulieren und damit umgehen oder den

Zugang für andere Prozesse blockieren.

-Während der Manipulation der Semaphore könnte der Prozess durch einen Interrupt

unterbrochen werden. Semaphorenoperationen: -> Betriebssystem -> Zugriff muss atomar

ablaufen muss, darf also nicht durch andere Prozesse oder Threads unterbrochen werden. BS

stellt Semaphorenoperationen zur Verfügung stellt

S1.count = 1

Prozess A

repeat

down(S1);

x=2;

up(S2);

until false;

S2.count = 0

Prozess B

repeat

down(S2);

x=1;

up(S1);

until false;

Prozess A

down(S1);

down(S2);

Prozess B

down(S2);

down(S1);

Deadlock / Verklemmung -> Eine Menge von Prozessen befindet sich in einem Deadlock, wenn

jeder dieser Prozesse auf ein Ereignis wartet, das nur ein anderer Prozess aus dieser Menge

verursachen kann.

Datei/ Verzeichnisrechte: „-“ für Datei, „d“ für Ordner. rwx rwx rwx – ugo Befehl: chmod ugo+-rwx

Datei/Ordner Zahl in der dritten Spalte von links: 1 + Verweise auf diese Datei. Wird die Datei

gelöscht, wird nur der Eintrag gelöscht, nicht aber die Datei selbst. Bei Verzeichnissen steht dort

mindestens eine 2 (für „.“ und „..“)

Hauptspeicherverwaltung / Paging:

Gegeben: HS= 2^37 Worte a 64Bit - phy.HS = 2GB - Seitengröße 16KB

HS= 2^37 * 64bit (8Byte=2^3Byte) = 2^37*2^3=2^40=1TB

Adressbus bei 64bit Wort Zugriff = 37Bit entspricht dem 37 aus HS 2^37

Die Adressbusbreite entspricht der Anzahl der Binärstellen, die notwendig ist, um alle

Worte adressieren zu können. Bei 2^37 Worten sind hierzu genau 37 Binärstellen nötig.

Logische Adresse: HS/Wortgröße = 2^37 / 2^3 = 2^34 = 35Bit (37-3)

Größe Eintrag in Seitentabelle = HS/Seitengröße=2^40/2^14=2^26=26Bit

Seitengröße i.W.: Seitengröße in KB / Wortgröße (16KB/8B=2^14/2^3=2^11)

Log. Ad. 2049 zu pys. Ad: Log. Adr./Seitengröße i.W.=2049/2048=1R1

Seitennr. 1 = Seitenrah. 0 => 2048*0+1=1=>phys. Adresse ist 1

Phys. Adr. 2049 zu log. Adr.: Phys. Adr./Seitengröße i.W.=2049/2048=1R1

Seitenrah. 1 = Seitennr. 2 => 2048*2+1=4097=>log. Adresse ist 4097

Bit

Byte

Byte

8

16

32

64

1

2

4

8

2^0

2^1

2^2

2^3

128

256

16

32

2^4

2^5

Seitentabelle

Logisch

Physisch

Seitennummer

Seitenrahmen

0

2

1

0

2

1

2er Potenzen: 2^ linke Spalte = rechte

0

1

B

21

2097152

2

MB

1

2

B

22

4194304

4

MB

2

4

B

23

8388608

8

MB

3

8

B

24

16777216

16

MB

4

16

B

25

33554432

32

MB

5

32

B

26

67108864

64

MB

6

64

B

27

134217728

128

MB

7

128

B

28

268435456

256

8

256

B

29

536870912

512

9

512

B

30

1073741824

1024

1

GB

10

1024

1

KB

31

2147483648

2048

2

GB

11

2048

2

KB

32

4294967296

4096

4

GB

12

4096

4

KB

33

8589934592

8192

8

GB

13

8192

8

KB

34

17179869184

16384

16

GB

14

16384

16

KB

35

34359738368

32768

32

GB

15

32768

32

KB

36

68719476736

65536

64

GB

16

65536

64

KB

37

137438953472

131072

128

GB

17

131072

128

KB

38

274877906944

262144

256

GB

18

262144

256

KB

39

549755813888

524288

512

GB

19

20

524288

1048576

512

1024

KB

KB

40

41

1099511627776

2199023255552

1048576

2097152

1

2

TB

TB

MB

MB

P1 hat eine Wartezeit von 2.

P1 muss 4 Zeiteinheiten warten bis der

Prozess beendet wird. Die restliche Zeit

sind andere Prozesse am

Zug:1,2,3,4,5,1,2,3,4,5,2,3,4,2,3,4,

2,4,2,4,4,4

Analog für P2 bis P5:

P2 Wartezeiten:

1,2,3,4,5,1,2,3,4,5,2,3,4,2,3,4,2,4,2 --> 13

Wartezeiten a 0,5 -> 6,5

P3 Wartezeiten:

1,2,3,4,5,1,2,3,4,5,2,3,4,2,3 --> 11

Wartezeiten a 0,5 -> 5,5

P4 Wartezeiten:

1,2,3,4,5,1,2,3,4,5,2,3,4,2,3,4,2,4,2,4 --> 14

Wartezeiten a 0,5 -> 7

P5 Wartezeiten:

1,2,3,4,5,1,2,3,4,5,2,3,4,2,3,4,2,4,2 --> 8

Wartezeiten a 0,5 -> 4

Bzw imDurchschnitt: (2 + 6,5 + 5,5 + 7 + 4)

/ 5 = 25 / 5 = 5.

Problem der hungrigen Philosophen.

Wer agiert?: N Philosophen

Welche Art von Ressourcen stehen zur Verfügung?: Stäbchen

In welcher Menge stehen diese Ressourcen zur Verfügung?: Es gibt N Stäbchen

Wie sind diese Ressourcen angeordnet?: Am Teller eines jeden Philosophen liegt links sein

Stäbchen.

Welche Aktionen können durchgeführt werden? denken und essen

Welche Ressourcen werden zur Durchführung der Aktionen benötigt?:denken: keine

Ressourcen werden benötigt / essen: zwei Stäbchen

Wie werden die Ressourcen reserviert? Ein Philosoph, der essen möchte, greift sich zunächst

seines eigenes Stäbchen und dann das seines rechten Nachbarn.

Was ist das Problem der hungrigen Philosophen:

Hat jeder Philosoph das Stäbchen zu seiner linken gegriffen, kann keiner mehr das zu seiner

rechten aufgreifen. Alle Philosophen warten darauf, dass ein Stäbchen frei wird, was jedoch nie

geschieht, sodass niemand essen kann.

Wie wird dieses Problem gelöst? Bevor ein Philosoph Stäbchen aufgreifen darf, muss er

zunächst prüfen, ob beide Stäbchen verfügbar sind. Ist dies der Fall, darf er sofort beide

Stäbchen aufgreifen. Kein anderer Philosoph darf ihn dabei unterbrechen oder währenddessen

selber mit dem Prüfen und Aufgreifen beginnen.

TCP: bietet einen zuverlässigen, verbindungsorientierten Dienst, über das ein Bytestrom von einem

Rechner im Internet fehler-frei einem anderen Rechner zugestellt wird, garantiert Vollständigkeit und

richtige Reihenfolge

UDP: bietet einen unzuverlässigen, verbindungslosen Dienst, keine Garantie bezüglich der Ankunft und

Reihenfolge, wird für DNS Server verwendet, DNS Anfrage ist klein und passt in DNS Segment, DNSServer kann hereinkommende Anfragen beantworten und sofort vergessen. Falls erfolglos, kann die

Anfrage erneut gesendet werden oder an einen anderen DNS gesendet werden.

UDP Segment: linke, rechte Spalte je 2 Byte

Source Portnummer

Segment-Länge

Destination Portnummer

UDP-Prüfsumme

Anwendungsdaten

Mechanismen zuverlässige Datenübertragung: Bestätigung und Timeout. Empfänger sendet Sender

Bestätigung für Paket. Timeout ist angemessenes Zeitintervall und wird benutzt, um Verlust des Pakets

zu erkennen: Wenn innerhalb der Timeout Zeit der Sender keine Bestätigung erhält, sendet er erneut.

In modernen Systemen ist der Hauptspeicher über einen Bus direkt am Prozessor angeschlossen während

er früher mit der Northbridge verbunden war.

Bei differenzieller Übertragung werden Signale mit entgegengesetzten Pegeln über ein Leitungspaar

geschickt.

Der Speicher-Controller in einem PC muss das Lesen der gesamten in den SDRAMs gespeicherten

Information in regelmäßigen Abständen veranlassen, damit diese nicht verloren geht.

Der USB gehört zu den wichtigsten Standard-Verbindungen der South-Bridge zur Kommunikation mit E/AGeräten.

Bei USB, IEEE 1394, PCIe und SATA können Geräte im laufenden Betrieb hinzugefügt und entfernt werden.

DRAM Package: Planar

Im DRAM-Gehäuse ist nur ein einziger Speicherchip untergebracht.

Gegenteil: MCM-Multi-Chip Modules mit mehreren (z.B. gestapelten) Chips im Gehäuse.

DIMM Ranks: 1

Nach JEDEC-Spezifikation bezeichnet der Begriff Rank einen eindeutigen, unabhängig adressierbaren 64 Bit

breiten Bereich eines Speichermoduls.

D.h. das betrachtete Modul besitzt eine einzige Reihe von DRAM-Bausteinen, die gleichförmig adressiert

werden.

Im Unterschied zu den Ranks sind die Bänke (Banks) innerhalb der Speicherbausteine realisierte

Speicherbereiche, die gesondert angesprochen werden und durch Trennung der Auffrischzeiten einen

schnelleren Zugriff auf die Speicherzellen ermöglichen.

Burst length supported:

Unter einem Burst versteht man einen Block von im Speicherbaustein nebeneinander liegenden Daten, die

sukzessive und nur unter Angabe der Block-Anfangsadresse übertragen werden. Die Folgeadressen für die

jeweils nächsten Zugriffe werden durch den Baustein selbst erzeugt.

DIMMs enthalten RAM und ROM und auf den Anschlusskontakten auf der Vorderseite und auf der Rückseite

der Leiterplatte liegen unterschiedliche (DUAL) Signale an.

Eine Grafikkarte mit einem Ausgang für analoge Videosignale benötigt mindestens einen RAMDAC

F Zur Speicherung von Nutzdaten auf einem magnetomotorischen Medium müssen diese in ein

Magnetisierungsmuster mit möglichst wenigen Bitzellen pro Nutzdatenbit umgesetzt werden, damit diese

eindeutig rekonstruiert werden können.

R Bevor ein Strom von Nutzdaten auf das Speichermedium einer Festplatte geschrieben werden kann, muss

dieser in einen Speichercode umgeformt werden, damit beim Lesen der dazu notwendige Takt

zurückgewonnen werden kann.

R Bei allen drei Codierungsarten FM, MFM und RLL ist die Anzahl der Codebits immer genau doppelt so

groß wie die Anzahl der Nutzdatenbits.

R Die MFM-Codierung ist der FM-Codierung überlegen, weil bei gleicher Anzahl von Nutz- und Codebits

weniger Flusswechsel erforderlich sind bzw. weniger Einsen im Speichercode vorkommen.

F Die RLL-Codierung besitzt gegenüber der FM-Codierung den Nachteil, dass die Speichercodeworte

erheblich länger sind und damit mehr Speicherplatz benötigt wird.

R Die RLL-Codierung ist der FM-Codierung überlegen, weil die Schreibdichte höher ist und damit mehr

Information auf die gleiche Fläche geschrieben werden kann.

R Bei der MFM-Codierung ist der Speichercode nur von der Vorgeschichte abhängig wenn ein 0-Bit

gespeichert werden soll.

Unterschied besteht in der Bedeutung des Begriffs Spur auf einer Festplatte bzw. einer CD-ROM

Festplatte: Konzentrischer Kreis auf einer Plattenoberfläche

CD-ROM: Spiralförmige Linie über die gesamte Oberfläche vom Zentrum zum Außenrand

Definition eines 1-Bits bei Festplatte und CD-ROM

Festplatte: Flusswechsel in der magnetischen Schicht

CD-ROM: Übergang zwischen Erhöhungen (Lands) und Vertiefungen (Pits) auf der Oberfläche

Monitor mit den Spezifikationen nach Teil C) an der DVI-Schnittstelle mit Dual-Link möglich?

Nein, da der DVI-Standard nur eine 24-Bit-Farbtiefe unterstützt.

Aber auch die maximale Übertragungsrate der Dual-Link-Schnittstelle von 6 x1,65 GBit/s = 9,9 GBit/s würde

für die verlangten 1,069547520 GB/s * 10 Bit/Byte = 10,695 GBit/s nicht ausreichen.

Übertragungsrate (in GByte/s und GBit/s) wird zwischen dem Grafikprozessor und dem Video-Controller

Pixel * Pixel * Farbtiefe / 8 = Größe in MB * Bildwiederholrate = MB/s / 1024 = GB/s * 8 = Gbit/s

EPROMs und EEPROMs elektrischen Verfahren gelöscht - beide werden elektrisch programmiert.#

Die minimale Zeitspanne, die zwischen zwei Zugriffen auf einen Speicher liegen muss, wird Zykluszeit

genannt. Die Zugriffszeit ist die Zeit, die für das Lesen oder Schreiben einer Speicherzelle benötigt wird.

von-Neumann-Flaschenhals bezeichnet man die Tatsache, dass Daten und Maschinenbefehle über den

selben Bus transportiert werden.

die Harvard-Architektur vermindert das Problem des von-Neumann-Flaschenhalses.

mit Hilfe von Memory Mapped I/O können Ein-/Ausgabegeräte vom Prozessor wie Arbeitsspeicher a.w.

die Adressleitungen eines Busses wählen das genaue Ziel oder die Quelle eines Datentransports aus.

die Prozessorarchitektur definiert die Grenze zwischen Hardware und Software. Sie umfasst den für den

Systemprogrammierer und für den Compiler sichtbaren Teil des Prozessors.

zum Programmiermodell eines Prozessors gehören der Befehlssatz, das Befehlsformat, die

Adressierungsarten, das Unterbrechungssystem und das Speichermodell.

der Befehlssatz einer RISC-Architektur besteht aus nur wenigen, unbedingt notwendigen Befehlen. Dadurch

werden zur Realisierung komplexer Funktionen mehr Befehle und damit wird gegenüber der CISCArchitektur mehr Speicherplatz benötigt.

der Befehlssatz einer RISC-Architektur besteht aus nur wenigen, unbedingt notwendigen Befehlen um eine

einfache Realisierung des Steuerwerks zu ermöglichen und damit Chip-Fläche zu sparen.

CISC-Architekturen zeichnen sich durch umfangreiche Befehlssätze, mächtige Maschinenbefehle mit vielen

Befehlsformaten und vielen Adressierungsarten aus.

wegen des kleineren Befehlssatzes und der daraus resultierenden weniger komplexeren Befehle werden zur

Implementierung eines Programmes auf einer RISC-Architektur mehr Befehle und damit mehr Speicherplatz

benötigt.

die Registerfenster-Technologie minimiert insbesondere bei SPARC-Prozessoren den Datentransfer, da der

Aufwand für die Sicherung von Registern und Prozessorstatus / Parameterübergabe vereinfacht wird.